## STMicroelectronics - <u>STM32F205VCT7TR Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| υ | e | τ | a | I | IS |

|---|---|---|---|---|----|

|   |   |   |   |   |    |

E·XF

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT       |

| Number of I/O              | 82                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 100K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205vct7tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.4 Embedded Flash memory

The STM32F20x devices embed a 128-bit wide Flash memory of 128 Kbytes, 256 Kbytes, 512 Kbytes, 768 Kbytes or 1 Mbyte available for storing programs and data.

The devices also feature 512 bytes of OTP memory that can be used to store critical user data such as Ethernet MAC addresses or cryptographic keys.

## 3.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 3.6 Embedded SRAM

All STM32F20x products embed:

- Up to 128 Kbytes of system SRAM accessed (read/write) at CPU clock speed with 0 wait states

- 4 Kbytes of backup SRAM.

The content of this area is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

## 3.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS) and the slaves (Flash memory, RAM, FSMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

The DMA can be used with the main peripherals:

- SPI and I<sup>2</sup>S

- I<sup>2</sup>C

- USART and UART

- General-purpose, basic and advanced-control timers TIMx

- DAC

- SDIO

- Camera interface (DCMI)

- ADC.

## **3.9** Flexible static memory controller (FSMC)

The FSMC is embedded in all STM32F20x devices. It has four Chip Select outputs supporting the following modes: PC Card/Compact Flash, SRAM, PSRAM, NOR Flash and NAND Flash.

Functionality overview:

- Write FIFO

- Code execution from external memory except for NAND Flash and PC Card

- Maximum frequency (f<sub>HCLK</sub>) for external access is 60 MHz

#### LCD parallel interface

The FSMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

## **3.10** Nested vectored interrupt controller (NVIC)

The STM32F20x devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 81 maskable interrupt channels plus the 16 interrupt lines of the Cortex<sup>®</sup>-M3.

The NVIC main features are the following:

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt latency.

DocID15818 Rev 13

There are three power modes configured by software when the regulator is ON:

- MR is used in the nominal regulation mode

- LPR is used in Stop modes

The LP regulator mode is configured by software when entering Stop mode.

• Power-down is used in Standby mode.

The Power-down mode is activated only when entering Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost).

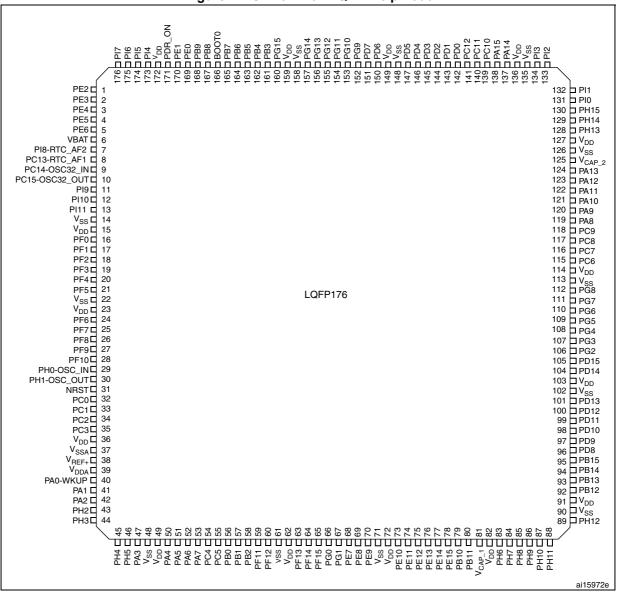

Two external ceramic capacitors should be connected on  $V_{CAP_1}$  and  $V_{CAP_2}$  pin. Refer to *Figure 19: Power supply scheme* and *Table 16: VCAP1/VCAP2 operating conditions*.

All packages have the regulator ON feature.

#### 3.16.2 Regulator OFF

This feature is available only on packages featuring the REGOFF pin. The regulator is disabled by holding REGOFF high. The regulator OFF mode allows to supply externally a V12 voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

The two 2.2 µF ceramic capacitors should be replaced by two 100 nF decoupling capacitors. Refer to *Figure 19: Power supply scheme*.

When the regulator is OFF, there is no more internal monitoring on V12. An external power supply supervisor should be used to monitor the V12 of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on V12 power domain.

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset the part of the 1.2 V logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used at power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection at reset or pre-reset is required.

#### Regulator OFF/internal reset ON

On WLCSP64+2 package, this mode is activated by connecting REGOFF pin to V<sub>DD</sub> and IRROFF pin to V<sub>SS</sub>. On UFBGA176 package, only REGOFF must be connected to V<sub>DD</sub> (IRROFF not available). In this mode,  $V_{DD}/V_{DDA}$  minimum value is 1.8 V.

The regulator OFF/internal reset ON mode allows to supply externally a 1.2 V voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins, in addition to V<sub>DD</sub>.

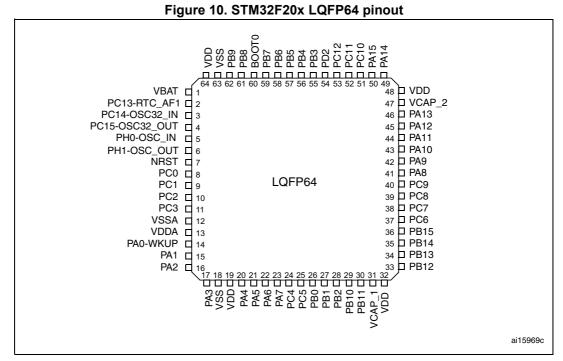

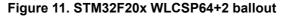

## 4 Pinouts and pin description

1. The above figure shows the package top view.

|   | 1    | 2      | 3      | 4   | 5   | 6     | 7      | 8      | 9                |

|---|------|--------|--------|-----|-----|-------|--------|--------|------------------|

| А | PA14 | PA15   | PC12   | PB3 | PB5 | PB7   | PB9    | VDD    | V <sub>BAT</sub> |

| В | VSS  | PA13   | PC10   | PB4 | PB6 | BOOT0 | PB8    | PC13   | PC14             |

| С | PA12 | VCAP_2 | PC11   |     |     |       | PD2    | IRROFF | PC15             |

| D | PC9  | PA11   | PA10   |     |     |       | PC2    | VSS    | VDD              |

| E | VDD  | PA8    | PA9    |     |     |       | PA0    | NRST   | PH0-<br>OSC_IN   |

| F | VSS  | PC7    | PC8    |     |     |       | VREF+  | PC1    | PH1-<br>OSC_OUT  |

| G | PB15 | PC6    | PC5    |     |     |       | PA3    | PC3    | PC0              |

| н | PB14 | PB13   | PB10   | PC4 | PA6 | PA5   | REGOFF | PA1    | VSS_5            |

| J | PB12 | PB11   | VCAP_1 | PB2 | PB1 | PB0   | PA7    | PA4    | PA2              |

|   |      |        |        |     |     |       |        |        |                  |

|   |      |        |        |     |     |       |        |        |                  |

1. The above figure shows the package top view.

#### Pinouts and pin description

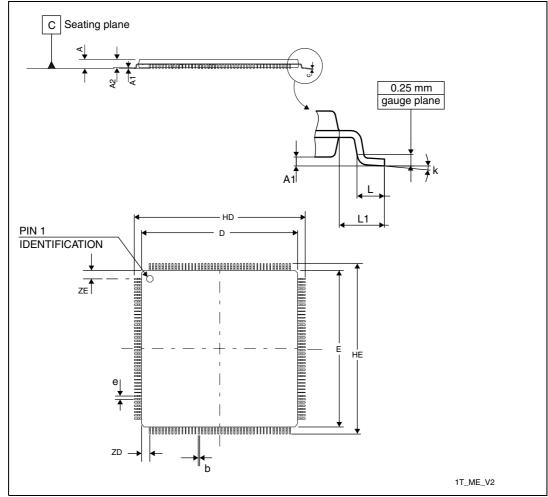

| Figure 14. | STM32F20x L | .QFP176 pi | nout |

|------------|-------------|------------|------|

|------------|-------------|------------|------|

1. RFU means "reserved for future use". This pin can be tied to  $V_{DD}$ ,  $V_{SS}$  or left unconnected.

2. The above figure shows the package top view.

|        |           | Pi      | ns      |         |          |                                                      |          |               |      |                                                                                                               |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                                                           | Additional<br>functions |

| 22     | H5        | 31      | 42      | 52      | P3       | PA6                                                  | I/O      | FT            | (4)  | SPI1_MISO, TIM8_BKIN,<br>TIM13_CH1, DCMI_PIXCLK,<br>TIM3_CH1, TIM1_BKIN,<br>EVENTOUT                          | ADC12_IN6               |

| 23     | J7        | 32      | 43      | 53      | R3       | PA7                                                  | I/O      | FT            | (4)  | SPI1_MOSI, TIM8_CH1N,<br>TIM14_CH1, TIM3_CH2,<br>ETH_MII_RX_DV,<br>TIM1_CH1N,<br>ETH_RMII_CRS_DV,<br>EVENTOUT | ADC12_IN7               |

| 24     | H4        | 33      | 44      | 54      | N5       | PC4                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD0,<br>ETH_MII_RXD0,<br>EVENTOUT                                                                   | ADC12_IN14              |

| 25     | G3        | 34      | 45      | 55      | P5       | PC5                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD1,<br>ETH_MII_RXD1,<br>EVENTOUT                                                                   | ADC12_IN15              |

| 26     | J6        | 35      | 46      | 56      | R5       | PB0                                                  | I/O      | FT            | (4)  | TIM3_CH3, TIM8_CH2N,<br>OTG_HS_ULPI_D1,<br>ETH_MII_RXD2,<br>TIM1_CH2N, EVENTOUT                               | ADC12_IN8               |

| 27     | J5        | 36      | 47      | 57      | R4       | PB1                                                  | I/O      | FT            | (4)  | TIM3_CH4, TIM8_CH3N,<br>OTG_HS_ULPI_D2,<br>ETH_MII_RXD3,<br>TIM1_CH3N, EVENTOUT                               | ADC12_IN9               |

| 28     | J4        | 37      | 48      | 58      | M6       | PB2/BOOT1 (PB2)                                      | I/O      | FT            | -    | EVENTOUT                                                                                                      | -                       |

| -      | -         | -       | 49      | 59      | R6       | PF11                                                 | I/O      | FT            | -    | DCMI_D12, EVENTOUT                                                                                            |                         |

| -      | -         | -       | 50      | 60      | P6       | PF12                                                 | I/O      | FT            | -    | FSMC_A6, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 51      | 61      | M8       | V <sub>SS</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 52      | 62      | N8       | V <sub>DD</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 53      | 63      | N6       | PF13                                                 | I/O      | FT            | -    | FSMC_A7, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 54      | 64      | R7       | PF14                                                 | I/O      | FT            | -    | FSMC_A8, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 55      | 65      | P7       | PF15                                                 | I/O      | FT            | -    | FSMC_A9, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 56      | 66      | N7       | PG0                                                  | I/O      | FT            | -    | FSMC_A10, EVENTOUT                                                                                            | -                       |

| -      | -         | -       | 57      | 67      | M7       | PG1                                                  | I/O      | FT            | -    | FSMC_A11, EVENTOUT                                                                                            | -                       |

|        |           | Pi      | ns      |         |          |                                                      |          |               |      |                                                                              |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                          | Additional<br>functions |

| -      | -         | -       | -       | 130     | D13      | PH15                                                 | I/O      | FT            | -    | TIM8_CH3N, DCMI_D11,<br>EVENTOUT                                             | -                       |

| -      | -         | -       | -       | 131     | E14      | PIO                                                  | I/O      | FT            | -    | TIM5_CH4, SPI2_NSS,<br>I2S2_WS, DCMI_D13,<br>EVENTOUT                        | -                       |

| -      | -         | -       | -       | 132     | D14      | PI1                                                  | I/O      | FT            | -    | SPI2_SCK, I2S2_SCK,<br>DCMI_D8, EVENTOUT                                     | -                       |

| -      | -         | -       | -       | 133     | C14      | PI2                                                  | I/O      | FT            | -    | TIM8_CH4 ,SPI2_MISO,<br>DCMI_D9, EVENTOUT                                    | -                       |

| -      | -         | -       | -       | 134     | C13      | PI3                                                  | I/O      | FT            | -    | TIM8_ETR, SPI2_MOSI,<br>I2S2_SD, DCMI_D10,<br>EVENTOUT                       | -                       |

| -      | -         | -       | -       | 135     | D9       | V <sub>SS</sub>                                      | S        | -             | -    | -                                                                            | -                       |

| -      | -         | -       | -       | 136     | C9       | V <sub>DD</sub>                                      | S        | -             | -    | -                                                                            | -                       |

| 49     | A1        | 76      | 109     | 137     | A14      | PA14<br>(JTCK-SWCLK)                                 | I/O      | FT            | -    | JTCK-SWCLK, EVENTOUT                                                         | -                       |

| 50     | A2        | 77      | 110     | 138     | A13      | PA15 (JTDI)                                          | I/O      | FT            | -    | JTDI, SPI3_NSS,<br>I2S3_WS,TIM2_CH1_ETR,<br>SPI1_NSS, EVENTOUT               | -                       |

| 51     | В3        | 78      | 111     | 139     | B14      | PC10                                                 | I/O      | FT            | -    | SPI3_SCK, I2S3_SCK,<br>UART4_TX, SDIO_D2,<br>DCMI_D8, USART3_TX,<br>EVENTOUT | -                       |

| 52     | C3        | 79      | 112     | 140     | B13      | PC11                                                 | I/O      | FT            | -    | UART4_RX, SPI3_MISO,<br>SDIO_D3,<br>DCMI_D4,USART3_RX,<br>EVENTOUT           | -                       |

| 53     | A3        | 80      | 113     | 141     | A12      | PC12                                                 | I/O      | FT            | -    | UART5_TX, SDIO_CK,<br>DCMI_D9, SPI3_MOSI,<br>I2S3_SD, USART3_CK,<br>EVENTOUT | -                       |

| -      | -         | 81      | 114     | 142     | B12      | PD0                                                  | I/O      | FT            | -    | FSMC_D2,CAN1_RX,<br>EVENTOUT                                                 | -                       |

| -      | -         | 82      | 115     | 143     | C12      | PD1                                                  | I/O      | FT            | -    | FSMC_D3, CAN1_TX,<br>EVENTOUT                                                | -                       |

Table 8. STM32F20x pin and ball definitions (continued)

#### 6.1.6 Power supply scheme

Figure 19. Power supply scheme

1. Each power supply pair must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

2. To connect REGOFF and IRROFF pins, refer to Section 3.16: Voltage regulator.

3. The two 2.2  $\mu F$  ceramic capacitors should be replaced by two 100 nF decoupling capacitors when the voltage regulator is OFF.

4. The 4.7  $\mu F$  ceramic capacitor must be connected to one of the  $V_{DD}$  pin.

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> ...) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB, to ensure good device operation. It is not recommended to remove filtering capacitors to reduce PCB size or cost. This might cause incorrect device operation.

DocID15818 Rev 13

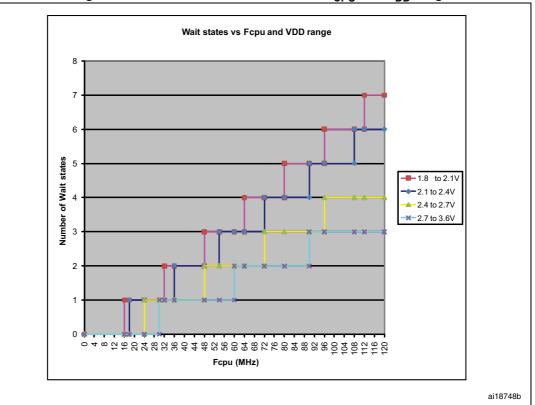

Figure 21. Number of wait states versus  $f_{\mbox{CPU}}$  and  $V_{\mbox{DD}}$  range

1. The supply voltage can drop to 1.7 V when the device operates in the 0 to 70  $^\circ\text{C}$  temperature range and IRROFF is set to V\_DD.

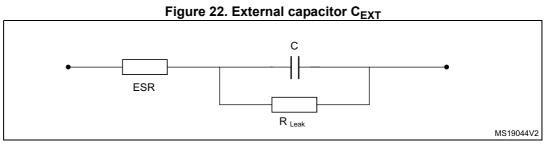

#### 6.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 16*.

1. Legend: ESR is the equivalent series resistance.

#### Table 16. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

| Symbol | Parameter                         | Conditions |

|--------|-----------------------------------|------------|

| CEXT   | Capacitance of external capacitor | 2.2 µF     |

| ESR    | ESR of external capacitor         | < 2 Ω      |

1. When bypassing the voltage regulator, the two 2.2  $\mu F$  V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 26*. The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog inputs by firmware.

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with one peripheral clocked on (with only the clock applied)

- The code is running from Flash memory and the Flash memory access time is equal to 3 wait states at 120 MHz

- Prefetch and Cache ON

- When the peripherals are enabled, HCLK = 120MHz,  $f_{PCLK1}$  =  $f_{HCLK}/4,$  and  $f_{PCLK2}$  =  $f_{HCLK}/2$

- The typical values are obtained for V<sub>DD</sub> = 3.3 V and T<sub>A</sub>= 25 °C, unless otherwise specified.

|      | Peripheral <sup>(1)</sup>                            | Typical consumption at 25 °C | Unit |

|------|------------------------------------------------------|------------------------------|------|

|      | GPIO A                                               | 0.45                         |      |

|      | GPIO B                                               | 0.43                         |      |

|      | GPIO C                                               | 0.46                         |      |

|      | GPIO D                                               | 0.44                         |      |

|      | GPIO E                                               | 0.44                         |      |

|      | GPIO F                                               | 0.42                         |      |

|      | GPIO G                                               | 0.44                         |      |

|      | GPIO H                                               | 0.42                         |      |

| AHB1 | GPIO I                                               | 0.43                         |      |

|      | OTG_HS + ULPI                                        | 3.64                         |      |

|      | CRC                                                  | 1.17                         | mA   |

|      | BKPSRAM                                              | 0.21                         |      |

|      | DMA1                                                 | 2.76                         |      |

|      | DMA2                                                 | 2.85                         |      |

|      | ETH_MAC +<br>ETH_MAC_TX<br>ETH_MAC_RX<br>ETH_MAC_PTP | 2.99                         |      |

| AHB2 | OTG_FS                                               | 3.16                         |      |

| АНВ2 | DCMI                                                 | 0.60                         |      |

| AHB3 | FSMC                                                 | 1.74                         |      |

Table 26. Peripheral current consumption

The test results are given in *Table 41*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                              | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 120 MHz, conforms<br>to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 120 MHz, conforms<br>to IEC 61000-4-2 | 4A              |

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **USB OTG FS characteristics**

The USB OTG interface is USB-IF certified (Full-Speed). This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol                              | Parameter                           | Мах | Unit |  |  |  |  |  |

|-------------------------------------|-------------------------------------|-----|------|--|--|--|--|--|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |  |  |  |  |  |

Table 56. USB OTG FS startup time

1. Guaranteed by design, not tested in production.

| Sym            | bol                                                                                                                        | Parameter                                  | Conditions                                                       | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup> | Unit |

|----------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------|---------------------|------|---------------------|------|

|                | $V_{DD}$                                                                                                                   | USB OTG FS operating<br>voltage            |                                                                  | 3.0 <sup>(2)</sup>  | -    | 3.6                 | V    |

| Input          | V <sub>DI</sub> <sup>(3)</sup>                                                                                             | Differential input sensitivity             | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                                 | 0.2                 | -    | -                   |      |

| levels         | V <sub>CM</sub> <sup>(3)</sup>                                                                                             | Differential common mode range             | Includes V <sub>DI</sub> range                                   | 0.8                 | -    | 2.5                 | V    |

|                | $V_{SE}^{(3)}$                                                                                                             | Single ended receiver threshold            |                                                                  | 1.3                 | -    | 2.0                 |      |

| Output         | V <sub>OL</sub>                                                                                                            | Static output level low                    | $\rm R_L$ of 1.5 k\Omega to 3.6 $\rm V^{(4)}$                    | -                   | -    | 0.3                 | V    |

| levels         | V <sub>OH</sub>                                                                                                            | Static output level high                   | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                 | -    | 3.6                 | v    |

| В              | R <sub>PD</sub><br>PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM)<br>PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS) |                                            | V <sub>IN</sub> = V <sub>DD</sub>                                | 17                  | 21   | 24                  |      |

|                |                                                                                                                            |                                            | VIN - VDD                                                        | 0.65                | 1.1  | 2.0                 | kΩ   |

|                |                                                                                                                            | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP)       | V <sub>IN</sub> = V <sub>SS</sub>                                | 1.5                 | 1.8  | 2.1                 |      |

| R <sub>P</sub> | יט                                                                                                                         | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS) | V <sub>IN</sub> = V <sub>SS</sub>                                | 0.25                | 0.37 | 0.55                |      |

#### Table 57. USB OTG FS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The STM32F205xx and STM32F207xx USB OTG FS functionality is ensured down to 2.7 V but not the full USB OTG FS electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

3. Guaranteed by design, not tested in production.

4. R<sub>L</sub> is the load connected on the USB OTG FS drivers

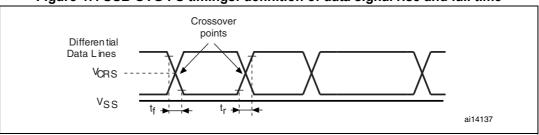

#### Figure 47. USB OTG FS timings: definition of data signal rise and fall time

#### Table 58. USB OTG FS electrical characteristics<sup>(1)</sup>

|                  | Driver o                        | characteristics                |     |     |      |

|------------------|---------------------------------|--------------------------------|-----|-----|------|

| Symbol           | Parameter                       | Conditions                     | Min | Max | Unit |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |

| t <sub>rfm</sub> | Rise/fall time matching         | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |

| V <sub>CRS</sub> | Output signal crossover voltage | -                              | 1.3 | 2.0 | V    |

1. Guaranteed by design, not tested in production.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

#### **USB HS characteristics**

Table 59 shows the USB HS operating voltage.

#### Table 59. USB HS DC electrical characteristics

| Symb        | ol       | Parameter                    | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

|-------------|----------|------------------------------|---------------------|---------------------|------|

| Input level | $V_{DD}$ | USB OTG HS operating voltage | 2.7                 | 3.6                 | V    |

1. All the voltages are measured from the local ground potential.

#### Table 60. Clock timing parameters

| Parameter <sup>(1)</sup>                                           |                  | Symbol                  | Min    | Nominal | Max    | Unit |  |

|--------------------------------------------------------------------|------------------|-------------------------|--------|---------|--------|------|--|

| Frequency (first transition)                                       | 8-bit ±10%       | F <sub>START_8BIT</sub> | 54     | 60      | 66     | MHz  |  |

| Frequency (steady state) ±500                                      | ppm              | F <sub>STEADY</sub>     | 59.97  | 60      | 60.03  | MHz  |  |

| Duty cycle (first transition)                                      | 8-bit ±10%       | D <sub>START_8BIT</sub> | 40     | 50      | 60     | %    |  |

| Duty cycle (steady state) ±500 ppm                                 |                  | D <sub>STEADY</sub>     | 49.975 | 50      | 50.025 | %    |  |

| Time to reach the steady state duty cycle after the first transiti |                  | T <sub>STEADY</sub>     | -      | -       | 1.4    | ms   |  |

| Clock startup time after the                                       | Peripheral       | T <sub>START_DEV</sub>  | -      | -       | 5.6    | me   |  |

| de-assertion of SuspendM                                           | Host             | T <sub>START_HOST</sub> | -      | -       | -      | ms   |  |

| PHY preparation time after the<br>of the input clock               | first transition | T <sub>PREP</sub>       | -      | -       | -      | μs   |  |

1. Guaranteed by design, not tested in production.

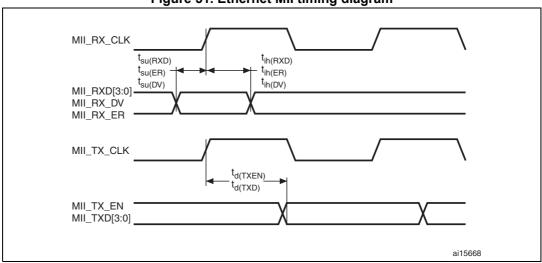

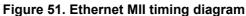

*Table 65* gives the list of Ethernet MAC signals for MII and *Figure 50* shows the corresponding timing diagram.

| Table 65, Dy | namics char | acteristics:  | Ethernet | MAC sid | unals for M   | 111 |

|--------------|-------------|---------------|----------|---------|---------------|-----|

|              |             | uotor 15t105. | Ethornot | MIAO 31 | jiiuis ioi ii |     |

| Symbol               | Rating                           | Min | Тур | Мах | Unit |

|----------------------|----------------------------------|-----|-----|-----|------|

| t <sub>su(RXD)</sub> | Receive data setup time          | 7.5 | -   | -   | ns   |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 1   | -   | -   | ns   |

| t <sub>su(DV)</sub>  | Data valid setup time            | 4   | -   | -   | ns   |

| t <sub>ih(DV)</sub>  | Data valid hold time             | 0   | -   | -   | ns   |

| t <sub>su(ER)</sub>  | Error setup time                 | 3.5 | -   | -   | ns   |

| t <sub>ih(ER)</sub>  | Error hold time                  | 0   | -   | -   | ns   |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | -   | 11  | 14  | ns   |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | -   | 11  | 14  | ns   |

#### CAN (controller area network) interface

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CANTX and CANRX).

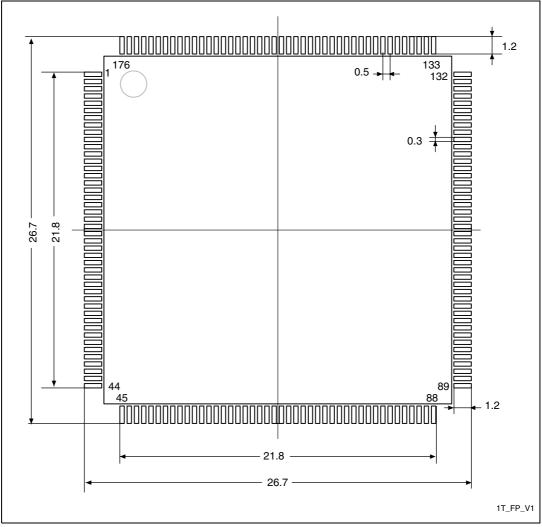

Figure 61. Synchronous multiplexed NOR/PSRAM read timings

| able 76. Synchronous multiplexed NOR/PSRAM read timings <sup>(1)(2)</sup> | minas <sup>(1)(2)</sup> |

|---------------------------------------------------------------------------|-------------------------|

| able 10. Synchronous multiplexed NON/FSIXAW read unnings                  | migs                    |

| Symbol                     | Parameter                                | Min                | Мах | Unit |

|----------------------------|------------------------------------------|--------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                          | 2T <sub>HCLK</sub> | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)      | -                  | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)    | 1                  | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low            | -                  | 1.5 | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high           | 2.5                | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)   | -                  | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625) | 0                  | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>  | FSMC_CLK high to FSMC_NOE low            | -                  | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>  | FSMC_CLK low to FSMC_NOE high            | 1                  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>   | FSMC_CLK low to FSMC_AD[15:0] valid      | -                  | 3   | ns   |

| t <sub>d(CLKL-ADIV)</sub>  | FSMC_CLK low to FSMC_AD[15:0] invalid    | 0                  | -   | ns   |

| 0k.e.l |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|--------|--------|-------------|--------|--------|-----------------------|--------|

| Symbol | Min    | Тур         | Мах    | Min    | Тур                   | Max    |

| А      | -      | -           | 1.600  | -      | -                     | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |

| D      | 21.800 | 22.000      | 22.200 | 0.8583 | 0.8661                | 0.8740 |

| D1     | 19.800 | 20.000      | 20.200 | 0.7795 | 0.7874                | 0.7953 |

| D3     | -      | 17.500      | -      | -      | 0.6890                | -      |

| Е      | 21.800 | 22.000      | 22.200 | 0.8583 | 0.8661                | 0.8740 |

| E1     | 19.800 | 20.000      | 20.200 | 0.7795 | 0.7874                | 0.7953 |

| E3     | -      | 17.500      | -      | -      | 0.6890                | -      |

| е      | -      | 0.500       | -      | -      | 0.0197                | -      |

| L      | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236                | 0.0295 |

| L1     | -      | 1.000       | -      | -      | 0.0394                | -      |

| k      | 0°     | 3.5°        | 7°     | 0°     | 3.5°                  | 7°     |

| CCC    | -      | -           | 0.080  | -      | -                     | 0.0031 |

# Table 91. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat packagemechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

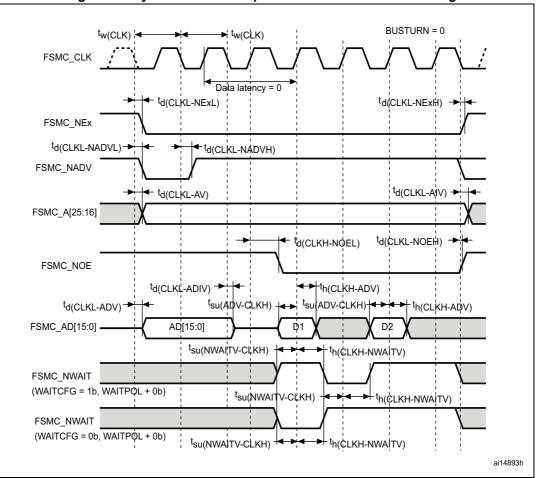

## 7.5 LQFP176 package information

Figure 87. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline

1. Drawing is not to scale.

| Table 92. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

|        |        |             | Dimer  | nsions |                       |        |

|--------|--------|-------------|--------|--------|-----------------------|--------|

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|        | Min.   | Тур.        | Max.   | Min.   | Тур.                  | Max.   |

| А      | -      | -           | 1.600  | -      | -                     | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |

| A2     | 1.350  | -           | 1.450  | 0.0531 | -                     | 0.0571 |

| b      | 0.170  | -           | 0.270  | 0.0067 | -                     | 0.0106 |

| с      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |

| D      | 23.900 | -           | 24.100 | 0.9409 | -                     | 0.9488 |

DocID15818 Rev 13

# Figure 88. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

| Date |

|------|

| Date |

| Table 97. Document revision history (continued) |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date                                            | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 20-Dec-2011                                     | 8<br>(continued) | Added maximum power consumption at $T_A=25$ °C in Table 23: Typical<br>and maximum current consumptions in Stop mode.<br>Updated md minimum value in Table 36: SSCG parameters constraint.<br>Added examples in Section 6.3.11: PLL spread spectrum clock<br>generation (SSCG) characteristics.<br>Updated Table 54: SPI characteristics and Table 55: I2S characteristics.<br>Updated Table 54: SPI characteristics and Table 51: ULPI timing.<br>Updated Table 63: Dynamics characteristics: Ethernet MAC signals for<br>SMI, Table 64: Dynamics characteristics: Ethernet MAC signals for<br>RMII, and Table 65: Dynamics characteristics: Ethernet MAC signals for<br>RMII, and Table 65: Dynamics characteristics: Ethernet MAC signals for<br>MII.<br>Section 6.3.25: FSMC characteristics: updated Table 72 to Table 83,<br>changed C <sub>L</sub> value to 30 pF, and modified FSMC configuration for<br>asynchronous timings and waveforms. Updated Figure 62:<br>Synchronous multiplexed PSRAM write timings.<br>Updated Table 92: UFBGA176+25 - ultra thin fine pitch ball grid array 10<br>× 10 × 0.6 mm mechanical data.<br>Updated Table 96: Ordering information scheme.<br>Appendix A.2: USB OTG full speed (FS) interface solutions: updated<br>Figure 87: USB OTG FS (full speed) host-only connection and added<br>Note 2, updated Figure 88: OTG FS (full speed) connection dual-role<br>with internal PHY and added Note 3 and Note 4, modified Figure 89:<br>OTG HS (high speed) device connection, host and dual-role in high-<br>speed mode with external PHY and added Note 2.<br>Appendix A.3: USB OTG HS device-only connection in FS mode and<br>USB OTG HS host-only connection in FS mode, updated Figure 89:<br>OTG HS (high speed) device connection, host and dual-role in high-<br>speed mode with external PHY.<br>Added Appendix A.4: Ethernet interface solutions.<br>Updated disclaimer on last page. |

| 24-Apr-2012                                     | 9                | Updated V <sub>DD</sub> minimum value in <i>Section 2: Description</i> .<br>Updated number of USB OTG HS and FS, modified packages for<br>STM32F207Ix part numbers, added <i>Note 1</i> related to FSMC and <i>Note 2</i><br>related to SPI/I2S, and updated <i>Note 3</i> in <i>Table 2: STM32F205xx</i><br><i>features and peripheral counts</i> and <i>Table 3: STM32F207xx features and</i><br><i>peripheral counts</i> .<br>Added <i>Note 2</i> and update TIM5 in <i>Figure 4: STM32F20x block diagram</i> .<br>Updated maximum number of maskable interrupts in <i>Section 3.10:</i><br><i>Nested vectored interrupt controller (NVIC)</i> .<br>Updated V <sub>DD</sub> minimum value in <i>Section 3.14: Power supply schemes</i> .<br>Updated <i>Note a</i> in <i>Section 3.16.1: Regulator ON</i> .<br>Removed STM32F205xx in <i>Section 3.28: Universal serial bus on-the-go</i><br><i>full-speed (OTG_FS)</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |