# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 120MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 82                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 132K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205vet6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 84. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline      | 158 |

|------------|--------------------------------------------------------------------------|-----|

| Figure 85. | LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package               |     |

|            | recommended footprint                                                    | 160 |

| Figure 86. | LQFP144 marking (package top view)                                       | 161 |

|            | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline      |     |

| Figure 88. | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package              |     |

| U          | recommended footprint                                                    | 164 |

| Figure 89. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch,                       |     |

| U          | ultra fine pitch ball grid array package outline                         | 165 |

| Figure 90. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball |     |

| U          | grid array package recommended footprint                                 | 166 |

## 3 Functional overview

# 3.1 **ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with embedded Flash and SRAM**

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

With its embedded  $\text{ARM}^{\text{®}}$  core, the STM32F20x family is compatible with all  $\text{ARM}^{\text{®}}$  tools and software.

Figure 4 shows the general block diagram of the STM32F20x family.

## 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M3 processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher operating frequencies.

To release the processor full 150 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 120 MHz.

## 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

The interface allows data transfer at up to 48 MHz in 8-bit mode, and is compliant with the SD Memory Card Specification Version 2.0.

The SDIO Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDIO/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

In addition to SD/SDIO/MMC, this interface is fully compliant with the CE-ATA digital protocol Rev1.1.

# 3.26 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

Peripheral available only on the STM32F207xx devices.

The STM32F207xx devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard mediumindependent interface (MII) or a reduced medium-independent interface (RMII). The STM32F207xx requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). the PHY is connected to the STM32F207xx MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) or 50 MHz (RMII) output from the STM32F207xx.

The STM32F207xx includes the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors (see the STM32F20x and STM32F21x reference manual for details)

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes, that is 4 Kbytes in total

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

## 3.27 Controller area network (CAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one

DocID15818 Rev 13

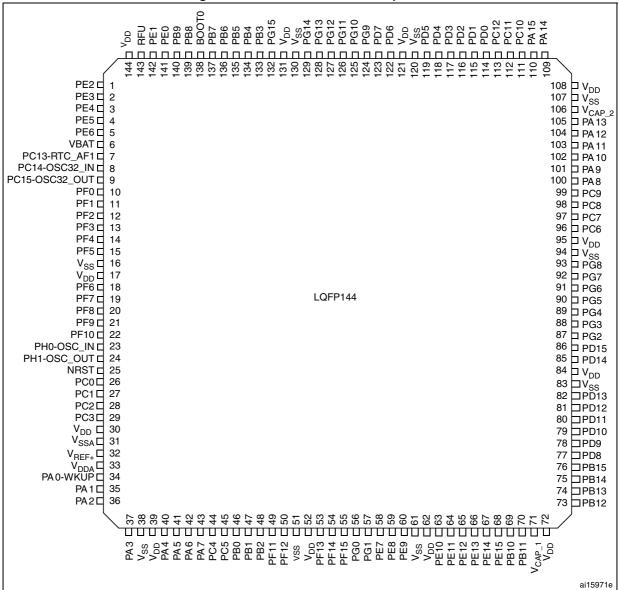

Figure 13. STM32F20x LQFP144 pinout

1. RFU means "reserved for future use". This pin can be tied to  $V_{DD}$ ,  $V_{SS}$  or left unconnected.

2. The above figure shows the package top view.

|   | 1                  | 2             | 3            | 4      | 5   | 6     | 7    | 8    | 9    | 10     | 11   | 12   | 13     | 14   | 15   |

|---|--------------------|---------------|--------------|--------|-----|-------|------|------|------|--------|------|------|--------|------|------|

| А | PE3                | PE2           | PE1          | PE0    | PB8 | PB5   | PG14 | PG13 | PB4  | PB3    | PD7  | PC12 | PA15   | PA14 | PA13 |

| в | PE4                | PE5           | PE6          | PB9    | PB7 | PB6   | PG15 | PG12 | PG11 | PG10   | PD6  | PD0  | PC11   | PC10 | PA12 |

| С | VBAT               | PI7           | PI6          | PI5    | VDD | RFU   | VDD  | VDD  | VDD  | PG9    | PD5  | PD1  | PI3    | Pl2  | PA11 |

| D | PC13-<br>TAMP1     | PI8-<br>TAMP2 | PI9          | PI4    | VSS | BOOT0 | VSS  | VSS  | VSS  | PD4    | PD3  | PD2  | PH15   | PI1  | PA10 |

| Е | PC14-<br>OSC32_IN  | PF0           | PI10         | PI11   |     |       |      |      |      |        |      | PH13 | PH14   | P10  | PA9  |

| F | PC15-<br>OSC32_OUT | VSS           | VDD          | PH2    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VSS  | VCAP_2 | PC9  | PA8  |

| G | PH0-<br>OSC_IN     | VSS           | VDD          | PH3    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PC8  | PC7  |

| н | PH1-<br>OSC_OUT    | PF2           | PF1          | PH4    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PG8  | PC6  |

| J | NRST               | PF3           | PF4          | PH5    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VDD  | VDD    | PG7  | PG6  |

| к | PF7                | PF6           | PF5          | VDD    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | PH12 | PG5    | PG4  | PG3  |

| L | PF10               | PF9           | PF8          | REGOFF |     |       |      |      |      |        |      | PH11 | PH10   | PD15 | PG2  |

| м | VSSA               | PC0           | PC1          | PC2    | PC3 | PB2   | PG1  | VSS  | VSS  | VCAP_1 | PH6  | PH8  | PH9    | PD14 | PD13 |

| N | VREF-              | PA1           | PA0-<br>WKUP | PA4    | PC4 | PF13  | PG0  | VDD  | VDD  | VDD    | PE13 | PH7  | PD12   | PD11 | PD10 |

| Ρ | VREF+              | PA2           | PA6          | PA5    | PC5 | PF12  | PF15 | PE8  | PE9  | PE11   | PE14 | PB12 | PB13   | PD9  | PD8  |

| R | VDDA               | PA3           | PA7          | PB1    | PB0 | PF11  | PF14 | PE7  | PE10 | PE12   | PE15 | PB10 | PB11   | PB14 | PB15 |

Figure 15. STM32F20x UFBGA176 ballout

1. RFU means "reserved for future use". This pin can be tied to  $V_{\text{DD}}, V_{\text{SS}}$  or left unconnected.

2. The above figure shows the package top view.

|  | Table 7. Legend/abbreviations used in the p | inout table |

|--|---------------------------------------------|-------------|

|--|---------------------------------------------|-------------|

| Name                   | Abbreviation                                                                                                                          | Definition                                                                      |  |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|

| Pin name               | Unless otherwise specified in brackets below the pin name, the pin function during and after reset is the same as the actual pin name |                                                                                 |  |  |  |  |

|                        | S                                                                                                                                     | Supply pin                                                                      |  |  |  |  |

| Pin type               | I                                                                                                                                     | Input only pin                                                                  |  |  |  |  |

|                        | I/O                                                                                                                                   | Input/ output pin                                                               |  |  |  |  |

|                        | FT                                                                                                                                    | 5 V tolerant I/O                                                                |  |  |  |  |

| I/O structure          | TTa 3.3 V tolerant I/O                                                                                                                |                                                                                 |  |  |  |  |

| NO structure           | В                                                                                                                                     | B Dedicated BOOT0 pin                                                           |  |  |  |  |

|                        | RST                                                                                                                                   | RST Bidirectional reset pin with embedded weak pull-up resistor                 |  |  |  |  |

| Notes                  | Unless otherwise                                                                                                                      | specified by a note, all I/Os are set as floating inputs during and after reset |  |  |  |  |

| Alternate<br>functions | Functions selected                                                                                                                    | d through GPIOx_AFR registers                                                   |  |  |  |  |

| Additional functions   | Functions directly                                                                                                                    | selected/enabled through peripheral registers                                   |  |  |  |  |

|        |           | Pi      | ns      |         |          |                                                      |          |    |     | ennitions (continued)                                                  |                        |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|----|-----|------------------------------------------------------------------------|------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | 21 |     | Additional<br>functions                                                |                        |

| -      | -         | -       | 14      | 20      | J3       | PF4                                                  | I/O      | FT | (4) | FSMC_A4, EVENTOUT                                                      | ADC3_IN14              |

| -      | -         | -       | 15      | 21      | K3       | PF5                                                  | I/O      | FT | (4) | FSMC_A5, EVENTOUT                                                      | ADC3_IN15              |

| -      | H9        | 10      | 16      | 22      | G2       | V <sub>SS</sub>                                      | S        | -  | -   | -                                                                      | -                      |

| -      | -         | 11      | 17      | 23      | G3       | V <sub>DD</sub>                                      | S        | -  | -   | -                                                                      | -                      |

| -      | -         | -       | 18      | 24      | K2       | PF6                                                  | I/O      | FT | (4) | TIM10_CH1, FSMC_NIORD,<br>EVENTOUT                                     | ADC3_IN4               |

| -      | -         | -       | 19      | 25      | K1       | PF7                                                  | I/O      | FT | (4) | TIM11_CH1,FSMC_NREG,<br>EVENTOUT                                       | ADC3_IN5               |

| -      | -         | -       | 20      | 26      | L3       | PF8                                                  | I/O      | FT | (4) | TIM13_CH1,<br>FSMC_NIOWR, EVENTOUT                                     | ADC3_IN6               |

| -      | -         | -       | 21      | 27      | L2       | PF9                                                  | I/O      | FT | (4) | TIM14_CH1, FSMC_CD,<br>EVENTOUT                                        | ADC3_IN7               |

| -      | -         | -       | 22      | 28      | L1       | PF10                                                 | I/O      | FT | (4) | FSMC_INTR, EVENTOUT                                                    | ADC3_IN8               |

| 5      | E9        | 12      | 23      | 29      | G1       | PH0/OSC_IN<br>(PH0)                                  | I/O      | FT | -   | EVENTOUT                                                               | OSC_IN <sup>(4)</sup>  |

| 6      | F9        | 13      | 24      | 30      | H1       | PH1/OSC_OUT<br>(PH1)                                 | I/O      | FT | -   | EVENTOUT                                                               | OSC_OUT <sup>(4)</sup> |

| 7      | E8        | 14      | 25      | 31      | J1       | NRST                                                 | I/O      |    | I   | -                                                                      | -                      |

| 8      | G9        | 15      | 26      | 32      | M2       | PC0                                                  | I/O      | FT | (4) | OTG_HS_ULPI_STP,<br>EVENTOUT                                           | ADC123_<br>IN10        |

| 9      | F8        | 16      | 27      | 33      | М3       | PC1                                                  | I/O      | FT | (4) | ETH_MDC, EVENTOUT                                                      | ADC123_<br>IN11        |

| 10     | D7        | 17      | 28      | 34      | M4       | PC2                                                  | I/O      | FT | (4) | SPI2_MISO,<br>OTG_HS_ULPI_DIR,<br>ETH_MII_TXD2, EVENTOUT               | ADC123_<br>IN12        |

| 11     | G8        | 18      | 29      | 35      | M5       | PC3                                                  | I/O      | FT | (4) | SPI2_MOSI, I2S2_SD,<br>OTG_HS_ULPI_NXT,<br>ETH_MII_TX_CLK,<br>EVENTOUT | ADC123_<br>IN13        |

| -      | -         | 19      | 30      | 36      | -        | V <sub>DD</sub>                                      | S        | -  | -   | -                                                                      | -                      |

| 12     | -         | 20      | 31      | 37      | M1       | V <sub>SSA</sub>                                     | S        | -  | -   | -                                                                      | -                      |

| -      | -         | -       | -       | -       | N1       | V <sub>REF-</sub>                                    | S        | -  | -   | -                                                                      | -                      |

| -      | F7        | 21      | 32      | 38      | P1       | V <sub>REF+</sub>                                    | S        | -  | -   | -                                                                      | -                      |

|        |           | Pi      | ns      |         |          |                                                      |          |               |                     |                                                                      |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|---------------------|----------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Alternate functions |                                                                      | Additional<br>functions |

| 54     | C7        | 83      | 116     | 144     | D12      | PD2                                                  | I/O      | FT            | -                   | TIM3_ETR,UART5_RX,<br>SDIO_CMD, DCMI_D11,<br>EVENTOUT                | -                       |

| -      | -         | 84      | 117     | 145     | D11      | PD3                                                  | I/O      | FT            | -                   | FSMC_CLK,USART2_CTS,<br>EVENTOUT                                     | -                       |

| -      | -         | 85      | 118     | 146     | D10      | PD4                                                  | I/O      | FT            | -                   | FSMC_NOE, USART2_RTS,<br>EVENTOUT                                    | -                       |

| -      | -         | 86      | 119     | 147     | C11      | PD5                                                  | I/O      | FT            | -                   | FSMC_NWE,USART2_TX,<br>EVENTOUT                                      | -                       |

| -      | -         | -       | 120     | 148     | D8       | V <sub>SS</sub>                                      | S        | -             | -                   | -                                                                    | -                       |

| -      | -         | -       | 121     | 149     | C8       | V <sub>DD</sub>                                      | S        | -             | -                   | -                                                                    | -                       |

| -      | -         | 87      | 122     | 150     | B11      | PD6                                                  | I/O      | FT            | -                   | FSMC_NWAIT,<br>USART2_RX, EVENTOUT                                   | -                       |

| -      | -         | 88      | 123     | 151     | A11      | PD7                                                  | I/O      | FT            | -                   | USART2_CK,FSMC_NE1,<br>FSMC_NCE2, EVENTOUT                           | -                       |

| -      | -         | -       | 124     | 152     | C10      | PG9                                                  | I/O      | FT            | -                   | USART6_RX,<br>FSMC_NE2,FSMC_NCE3,<br>EVENTOUT                        | -                       |

| -      | -         | -       | 125     | 153     | B10      | PG10                                                 | I/O      | FT            | -                   | FSMC_NCE4_1,<br>FSMC_NE3, EVENTOUT                                   | -                       |

| -      | -         | -       | 126     | 154     | В9       | PG11                                                 | I/O      | FT            | -                   | FSMC_NCE4_2,<br>ETH_MII_TX_EN,<br>ETH_RMII_TX_EN,<br>EVENTOUT        | -                       |

| -      | -         | -       | 127     | 155     | B8       | PG12                                                 | I/O      | FT            | -                   | FSMC_NE4, USART6_RTS,<br>EVENTOUT                                    | -                       |

| -      | -         | -       | 128     | 156     | A8       | PG13                                                 | I/O      | FT            | -                   | FSMC_A24, USART6_CTS,<br>ETH_MII_TXD0,<br>ETH_RMII_TXD0,<br>EVENTOUT | -                       |

| -      | -         | -       | 129     | 157     | A7       | PG14                                                 | I/O      | FT            | -                   | FSMC_A25, USART6_TX,<br>ETH_MII_TXD1,<br>ETH_RMII_TXD1,<br>EVENTOUT  | -                       |

| -      | -         | -       | 130     | 158     | D7       | V <sub>SS</sub>                                      | S        | -             | -                   | -                                                                    | -                       |

Table 8. STM32F20x pin and ball definitions (continued)

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3 V (for the 1.8 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

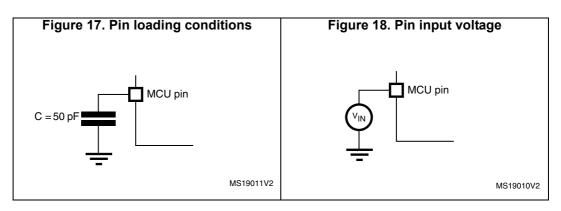

## 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 17*.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 18*.

|        |                                       |                                                                                                                                                  | Тур                       |                           | Max                       |                            |            |

|--------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------------|

| Symbol | Parameter                             | Conditions                                                                                                                                       | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit       |

|        | Supply current<br>in Stop mode        | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.55                      | 1.2                       | 11.00                     | 20.00                      |            |

|        | with main<br>regulator in<br>Run mode | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.50                      | 1.2                       | 11.00                     | 20.00                      | <b>m</b> 4 |

|        |                                       | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.35                      | 1.1                       | 8.00                      | 15.00                      | mA         |

|        | regulator in<br>Low-power<br>mode     | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.30                      | 1.1                       | 8.00                      | 15.00                      |            |

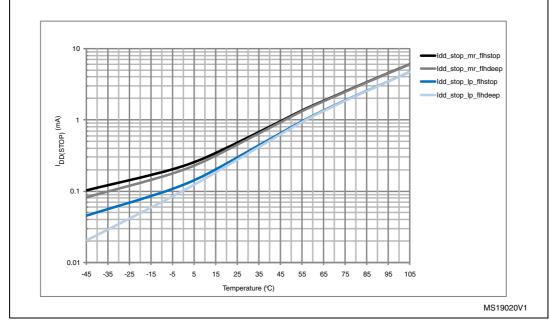

Table 23. Typical and maximum current consumptions in Stop mode

Figure 29. Typical current consumption vs. temperature in Stop mode

All typical and maximum values from table 18 and figure 26 will be reduced over time by up to 50% as part

of ST continuous improvement of test procedures. New versions of the datasheet will be released to reflect

these changes

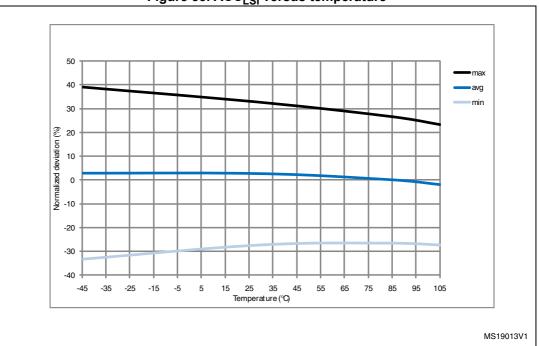

Figure 35. ACC<sub>LSI</sub> versus temperature

## 6.3.10 PLL characteristics

The parameters given in *Table 34* and *Table 35* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                  | Parameter                             | Conditions         | Min                 | Тур | Max                 | Unit |  |

|-------------------------|---------------------------------------|--------------------|---------------------|-----|---------------------|------|--|

| f <sub>PLL_IN</sub>     | PLL input clock <sup>(1)</sup>        | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 <sup>(2)</sup> | MHz  |  |

| f <sub>PLL_OUT</sub>    | PLL multiplier output clock           | -                  | 24                  | -   | 120                 | MHz  |  |

| f <sub>PLL48_</sub> OUT | 48 MHz PLL multiplier output<br>clock | -                  | -                   | -   | 48                  | MHz  |  |

| f <sub>VCO_OUT</sub>    | PLL VCO output                        | -                  | 192                 | -   | 432                 | MHz  |  |

|                         | PLL lock time                         | VCO freq = 192 MHz | 75                  | -   | 200                 | 116  |  |

| t <sub>LOCK</sub>       |                                       | VCO freq = 432 MHz | 100                 | -   | 300                 | μs   |  |

Table 34. Main PLL characteristics

| Symbol          | Parameter      | Conditions                                           | Min | Тур | Max | Unit |

|-----------------|----------------|------------------------------------------------------|-----|-----|-----|------|

| I <sub>DD</sub> |                | Write / Erase 8-bit mode<br>V <sub>DD</sub> = 1.8 V  | -   | 5   | -   |      |

|                 | Supply current | Write / Erase 16-bit mode<br>V <sub>DD</sub> = 2.1 V | -   | 8   | -   | mA   |

|                 |                | Write / Erase 32-bit mode<br>V <sub>DD</sub> = 3.3 V | -   | 12  | -   |      |

Table 37. Flash memory characteristics

#### Table 38. Flash memory programming

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | S    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 16   | 32                 |      |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 11   | 22                 | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 8    | 16                 |      |

|                         |                            | 32-bit program operation                         | 2.7                | -    | 3.6                | V    |

| V <sub>prog</sub>       | Programming voltage        | 16-bit program operation                         | 2.1                | -    | 3.6                | V    |

|                         |                            | 8-bit program operation                          | 1.8                | -    | 3.6                | V    |

1. Guaranteed by characterization results, not tested in production.

2. The maximum programming time is measured after 100K erase operations.

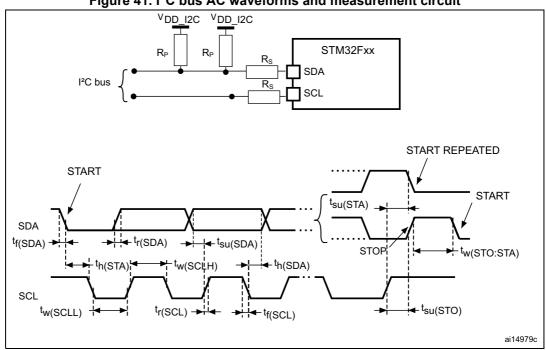

Figure 41. I<sup>2</sup>C bus AC waveforms and measurement circuit

- 1.  $R_S$ = series protection resistor.

- 2. R<sub>P</sub> = external pull-up resistor.

- 3.  $V_{DD_{12C}}$  is the I<sup>2</sup>C bus power supply.

| f (kU-)                | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x8019                  |

| 300                    | 0x8021                  |

| 200                    | 0x8032                  |

| 100                    | 0x0096                  |

| 50                     | 0x012C                  |

| 20                     | 0x02EE                  |

## Table 53. SCL frequency (f<sub>PCLK1</sub>= 30 MHz., V<sub>DD</sub> = 3.3 V)<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  = I<sup>2</sup>C speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

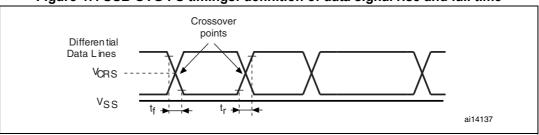

#### Figure 47. USB OTG FS timings: definition of data signal rise and fall time

#### Table 58. USB OTG FS electrical characteristics<sup>(1)</sup>

|                  | Driver o                        | characteristics                |     |     |      |

|------------------|---------------------------------|--------------------------------|-----|-----|------|

| Symbol           | Parameter                       | Conditions                     | Min | Max | Unit |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |

| t <sub>rfm</sub> | Rise/fall time matching         | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |

| V <sub>CRS</sub> | Output signal crossover voltage | -                              | 1.3 | 2.0 | V    |

1. Guaranteed by design, not tested in production.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

#### **USB HS characteristics**

Table 59 shows the USB HS operating voltage.

#### Table 59. USB HS DC electrical characteristics

| Symb        | ol       | Parameter                    | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

|-------------|----------|------------------------------|---------------------|---------------------|------|

| Input level | $V_{DD}$ | USB OTG HS operating voltage | 2.7                 | 3.6                 | V    |

1. All the voltages are measured from the local ground potential.

#### Table 60. Clock timing parameters

| Parameter <sup>(1)</sup>                                           |                  | Symbol                  | Min    | Nominal | Max    | Unit |

|--------------------------------------------------------------------|------------------|-------------------------|--------|---------|--------|------|

| Frequency (first transition)                                       | 8-bit ±10%       | F <sub>START_8BIT</sub> | 54     | 60      | 66     | MHz  |

| Frequency (steady state) ±500                                      | ppm              | F <sub>STEADY</sub>     | 59.97  | 60      | 60.03  | MHz  |

| Duty cycle (first transition)                                      | 8-bit ±10%       | D <sub>START_8BIT</sub> | 40     | 50      | 60     | %    |

| Duty cycle (steady state) ±500                                     | ppm              | D <sub>STEADY</sub>     | 49.975 | 50      | 50.025 | %    |

| Time to reach the steady state duty cycle after the first transiti |                  | T <sub>STEADY</sub>     | -      | -       | 1.4    | ms   |

| Clock startup time after the                                       | Peripheral       | T <sub>START_DEV</sub>  | -      | -       | 5.6    | ms   |

| de-assertion of SuspendM                                           | Host             | T <sub>START_HOST</sub> | -      | -       | -      | 1115 |

| PHY preparation time after the<br>of the input clock               | first transition | T <sub>PREP</sub>       | -      | -       | -      | μs   |

1. Guaranteed by design, not tested in production.

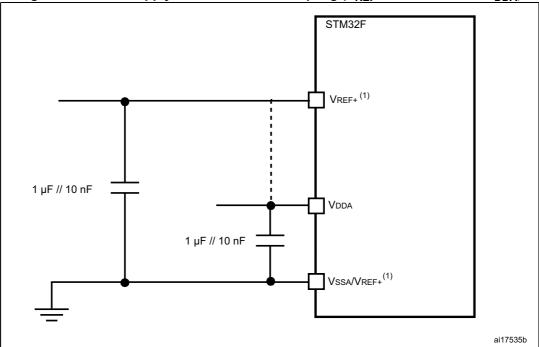

## General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 54* or *Figure 55*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

V<sub>REF+</sub> and V<sub>REF</sub> inputs are both available on UFBGA176 package. V<sub>REF+</sub> is also available on all packages except for LQFP64. When V<sub>REF+</sub> and V<sub>REF</sub> are not available, they are internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

| Symbol                     | Parameter                                    | Min | Max | Unit |

|----------------------------|----------------------------------------------|-----|-----|------|

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high               | 4   | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)       | -   | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625)     | 3   | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>  | FSMC_CLK high to FSMC_NOE low                | -   | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>  | FSMC_CLK low to FSMC_NOE high                | 1.5 | -   | ns   |

| t <sub>su(DV-CLKH)</sub>   | FSMC_D[15:0] valid data before FSMC_CLK high | 8   | -   | ns   |

| t <sub>h(CLKH-DV)</sub>    | FSMC_D[15:0] valid data after FSMC_CLK high  | 0   | -   | ns   |

## Table 78. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

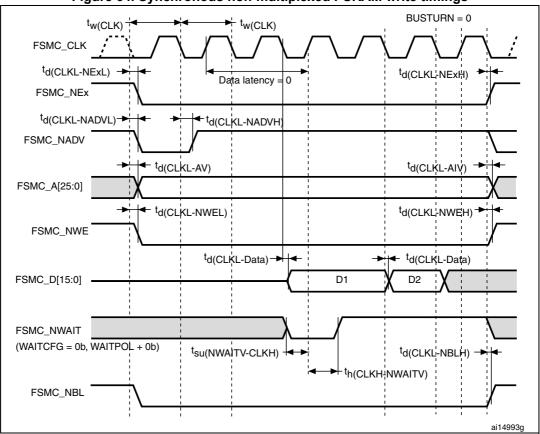

## Figure 64. Synchronous non-multiplexed PSRAM write timings

## Table 79. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                             | Min                    | Max | Unit |

|---------------------------|---------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>       | FSMC_CLK period                       | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub> | FSMC_CLK low to FSMC_NEx low (x=02)   | -                      | 1   | ns   |

| t <sub>d(CLKL-NExH)</sub> | FSMC_CLK low to FSMC_NEx high (x= 02) | 1                      | -   | ns   |

| Symbol              | Parameter                                  | Conditions              | Min | Max | Unit |

|---------------------|--------------------------------------------|-------------------------|-----|-----|------|

| f <sub>PP</sub>     | Clock frequency in data transfer mode      | $C_L \le 30 \text{ pF}$ | 0   | 48  | MHz  |

| -                   | SDIO_CK/f <sub>PCLK2</sub> frequency ratio | -                       | -   | 8/3 | -    |

| t <sub>W(CKL)</sub> | Clock low time, $f_{PP}$ = 16 MHz          | $C_L \le 30 \text{ pF}$ | 32  | -   |      |

| t <sub>W(CKH)</sub> | Clock high time, f <sub>PP</sub> = 16 MHz  | $C_L \le 30 \text{ pF}$ | 31  | -   |      |

| t <sub>r</sub>      | Clock rise time                            | $C_L \le 30 \text{ pF}$ | -   | 3.5 | ns   |

| t <sub>f</sub>      | Clock fall time                            | $C_L \le 30 \text{ pF}$ | -   | 5   |      |

| CMD, D inp          | outs (referenced to CK)                    |                         |     |     | •    |

| t <sub>ISU</sub>    | Input setup time                           | $C_L \le 30 \text{ pF}$ | 2   | -   | ne   |

| t <sub>IH</sub>     | Input hold time                            | $C_L \le 30 \text{ pF}$ | 0   | -   | ns   |

| CMD, D out          | tputs (referenced to CK) in MMC and        | SD HS mode              |     |     | •    |

| t <sub>OV</sub>     | Output valid time                          | $C_L \le 30 \text{ pF}$ | -   | 6   | 20   |

| t <sub>OH</sub>     | Output hold time                           | $C_L \le 30 \text{ pF}$ | 0.3 | -   | ns   |

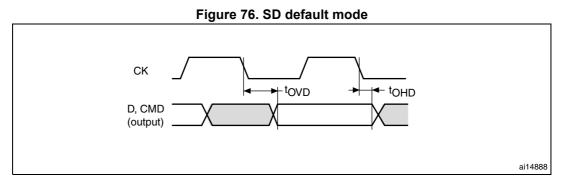

| CMD, D out          | tputs (referenced to CK) in SD defau       | ılt mode <sup>(1)</sup> |     |     |      |

| t <sub>OVD</sub>    | Output valid default time                  | $C_L \le 30 \text{ pF}$ | -   | 7   |      |

| t <sub>OHD</sub>    | Output hold default time                   | $C_L \le 30 \text{ pF}$ | 0.5 | -   | ns   |

#### Table 85. SD/MMC characteristics

1. Refer to SDIO\_CLKCR, the SDI clock control register to control the CK output.

## 6.3.28 RTC characteristics

## Table 86. RTC characteristics

| Symbol | Parameter                                  | Conditions                                       | Min | Max |

|--------|--------------------------------------------|--------------------------------------------------|-----|-----|

| -      | f <sub>PCLK1</sub> /RTCCLK frequency ratio | Any read/write operation from/to an RTC register | 4   | -   |

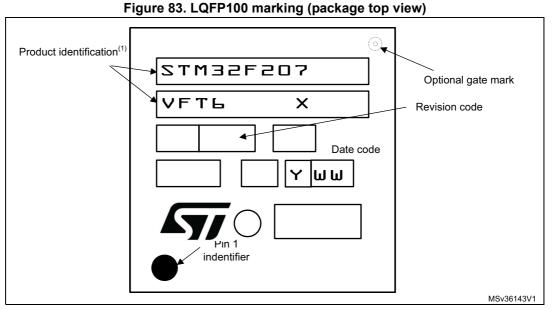

## **Device marking**

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

## 7.7 Thermal characteristics

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                  | Value | Unit |

|---------------|----------------------------------------------------------------------------|-------|------|

|               | Thermal resistance junction-ambient<br>LQFP 64 - 10 × 10 mm / 0.5 mm pitch | 45    |      |

|               | Thermal resistance junction-ambient<br>WLCSP64+2 - 0.400 mm pitch          | 51    |      |

| 0             | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch | 46    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm / 0.5 mm pitch | 40    | 0/11 |

|               | Thermal resistance junction-ambient<br>LQFP176 - 24 × 24 mm / 0.5 mm pitch | 38    |      |

|               | Thermal resistance junction-ambient<br>UFBGA176 - 10× 10 mm / 0.5 mm pitch | 39    |      |

#### **Reference document**

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

| Data   |

|--------|

|        |

| Date R |

| Table 97. Document revision history (continued) |  |  |

|-------------------------------------------------|--|--|

| Date                                            |  |  |

| Date                                            |  |  |