# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| υ | e | τ | a | I | I | s |

|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 120MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 82                                                                    |

| Program Memory Size        | 768KB (768K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 132K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205vft6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

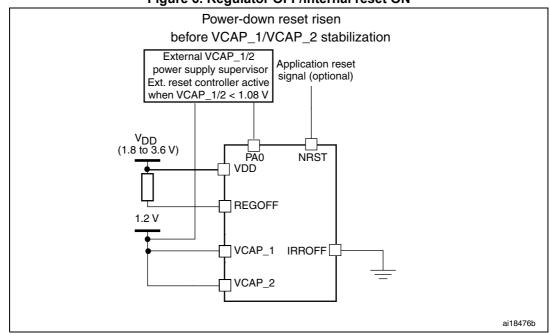

Figure 6. Regulator OFF/internal reset ON

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach 1.08 V is faster than the time for  $V_{DD}$  to reach 1.8 V, then PA0 should be kept low to cover both conditions: until  $V_{CAP_1}$  and  $V_{CAP_2}$  reach 1.08 V and until  $V_{DD}$  reaches 1.8 V (see *Figure 8*).

- Otherwise, If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach 1.08 V is slower than the time for V<sub>DD</sub> to reach 1.8 V, then PA0 should be asserted low externally (see *Figure 9*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below 1.08 V and V<sub>DD</sub> is higher than 1.8 V, then a reset must be asserted on PA0 pin.

#### **Regulator OFF/internal reset OFF**

On WLCSP64+2 package, this mode activated by connecting REGOFF to V<sub>SS</sub> and IRROFF to V<sub>DD</sub>. IRROFF cannot be activated in conjunction with REGOFF. This mode is available only on the WLCSP64+2 package. It allows to supply externally a 1.2 V voltage source through V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> pins. In this mode, the integrated power-on reset (POR)/ power-down reset (PDR) circuitry is disabled.

An external power supply supervisor should monitor both the external 1.2 V and the external  $V_{DD}$  supply voltage, and should maintain the device in reset mode as long as they remain below a specified threshold. The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.8 V. This supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range. A comprehensive set of power-saving modes allows to design low-power applications.

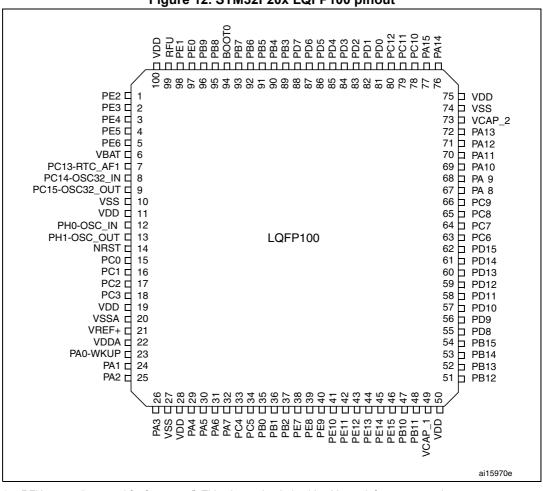

1. RFU means "reserved for future use". This pin can be tied to  $V_{\text{DD}}, V_{\text{SS}}$  or left unconnected.

2. The above figure shows the package top view.

|      |        |                | SMC           | ,           |         |

|------|--------|----------------|---------------|-------------|---------|

| Pins | CF     | NOR/PSRAM/SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100 |

| PD13 | -      | A18            | A18           | -           | Yes     |

| PD14 | D0     | D0             | DA0           | D0          | Yes     |

| PD15 | D1     | D1             | DA1           | D1          | Yes     |

| PG2  | -      | A12            | -             | -           | -       |

| PG3  | -      | A13            | -             | -           | -       |

| PG4  | -      | A14            | -             | -           | -       |

| PG5  | -      | A15            | -             | -           | -       |

| PG6  | -      | -              | -             | INT2        | -       |

| PG7  | -      | -              | -             | INT3        | -       |

| PD0  | D2     | D2             | DA2           | D2          | Yes     |

| PD1  | D3     | D3             | DA3           | D3          | Yes     |

| PD3  | -      | CLK            | CLK           | -           | Yes     |

| PD4  | NOE    | NOE            | NOE           | NOE         | Yes     |

| PD5  | NWE    | NWE            | NWE           | NWE         | Yes     |

| PD6  | NWAIT  | NWAIT          | NWAIT         | NWAIT       | Yes     |

| PD7  | -      | NE1            | NE1           | NCE2        | Yes     |

| PG9  | -      | NE2            | NE2           | NCE3        | -       |

| PG10 | NCE4_1 | NE3            | NE3           | -           | -       |

| PG11 | NCE4_2 | -              | -             | -           | -       |

| PG12 | -      | NE4            | NE4           | -           | -       |

| PG13 | -      | A24            | A24           | -           | -       |

| PG14 | -      | A25            | A25           | -           | -       |

| PB7  | -      | NADV           | NADV          | -           | Yes     |

| PE0  | -      | NBL0           | NBL0          | -           | Yes     |

| PE1  | -      | NBL1           | NBL1          | -           | Yes     |

Table 9. FSMC pin definition (continued)

| S  |  |

|----|--|

| -  |  |

| S  |  |

| 22 |  |

|    |  |

| 8  |  |

| ŏ  |  |

| 2  |  |

Pinouts and pin description

|        |      | AF0      | AF1       | AF2      | AF3          | AF4            | AF5            | AF6       | AF7        | AF8                | AF9                       | AF10           | AF11         | AF12                   | AF13     |       |         |

|--------|------|----------|-----------|----------|--------------|----------------|----------------|-----------|------------|--------------------|---------------------------|----------------|--------------|------------------------|----------|-------|---------|

|        | Port | SYS      | TIM1/2    | TIM3/4/5 | TIM8/9/10/11 | 12C1/12C2/12C3 | SPI1/SPI2/I2S2 | SPI3/I2S3 | USART1/2/3 | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 | OTG_FS/ OTG_HS | ETH          | FSMC/SDIO/<br>OTG_HS   | DCMI     | AF014 | AF15    |

|        | PD0  | -        | -         | -        | -            | -              | -              | -         | -          | -                  | CAN1_RX                   | -              | -            | FSMC_D2                | -        | -     | EVENTO  |

|        | PD1  | -        | -         | -        | -            | -              | -              | -         | -          | -                  | CAN1_TX                   | -              | -            | FSMC_D3                | -        | -     | EVENTOL |

|        | PD2  | -        | -         | TIM3_ETR | -            | -              | -              | -         | -          | UART5_RX           | -                         | -              | -            | SDIO_CMD               | DCMI_D11 | -     | EVENTO  |

|        | PD3  | -        | -         | -        | -            | -              | -              | -         | USART2_CTS | -                  | -                         | -              | -            | FSMC_CLK               | -        | -     | EVENTO  |

|        | PD4  | -        | -         | -        | -            | -              | -              | -         | USART2_RTS | -                  | -                         | -              | -            | FSMC_NOE               | -        | -     | EVENTO  |

|        | PD5  | -        | -         | -        | -            | -              | -              | -         | USART2_TX  | -                  | -                         | -              | -            | FSMC_NWE               | -        | -     | EVENTO  |

|        | PD6  | -        | -         | -        | -            | -              | -              | -         | USART2_RX  | -                  | -                         | -              | -            | FSMC_NWAIT             | -        | -     | EVENTO  |

| D. I D | PD7  | -        | -         | -        | -            | -              | -              | -         | USART2_CK  | -                  | -                         | -              | -            | FSMC_NE1/<br>FSMC_NCE2 | -        | -     | EVENTO  |

| Port D | PD8  | -        | -         | -        | -            | -              | -              | -         | USART3_TX  | -                  | -                         | -              | -            | FSMC_D13               | -        | -     | EVENTO  |

|        | PD9  | -        | -         | -        | -            | -              | -              | -         | USART3_RX  | -                  | -                         | -              | -            | FSMC_D14               | -        | -     | EVENTO  |

|        | PD10 | -        | -         | -        | -            | -              | -              | -         | USART3_CK  | -                  | -                         | -              | -            | FSMC_D15               | -        | -     | EVENTO  |

|        | PD11 | -        | -         | -        | -            | -              | -              | -         | USART3_CTS | -                  | -                         | -              | -            | FSMC_A16               | -        | -     | EVENTO  |

|        | PD12 | -        | -         | TIM4_CH1 | -            | -              | -              | -         | USART3_RTS | -                  | -                         | -              | -            | FSMC_A17               | -        | -     | EVENTO  |

|        | PD13 | -        | -         | TIM4_CH2 | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_A18               | -        | -     | EVENTO  |

|        | PD14 | -        | -         | TIM4_CH3 | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_D0                | -        | -     | EVENTO  |

|        | PD15 | -        | -         | TIM4_CH4 | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_D1                | -        | -     | EVENTO  |

|        | PE0  | -        | -         | TIM4_ETR | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_NBL0              | DCMI_D2  | -     | EVENTO  |

|        | PE1  | -        | -         | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_NBL1              | DCMI_D3  | -     | EVENTO  |

|        | PE2  | TRACECLK | -         | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | ETH_MII_TXD3 | FSMC_A23               | -        | -     | EVENTO  |

|        | PE3  | TRACED0  | -         | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_A19               | -        | -     | EVENTO  |

|        | PE4  | TRACED1  | -         | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_A20               | DCMI_D4  | -     | EVENTO  |

|        | PE5  | TRACED2  | -         | -        | TIM9_CH1     | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_A21               | DCMI_D6  | -     | EVENTO  |

|        | PE6  | TRACED3  | -         | -        | TIM9_CH2     | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_A22               | DCMI_D7  | -     | EVENTO  |

| Port E | PE7  | -        | TIM1_ETR  | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_D4                | -        | -     | EVENTO  |

| FUILE  | PE8  | -        | TIM1_CH1N | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_D5                | -        | -     | EVENTO  |

|        | PE9  | -        | TIM1_CH1  | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_D6                | -        | -     | EVENTO  |

|        | PE10 | -        | TIM1_CH2N | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_D7                | -        | -     | EVENTO  |

|        | PE11 | -        | TIM1_CH2  | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_D8                | -        | -     | EVENTO  |

|        | PE12 | -        | TIM1_CH3N | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_D9                | -        | -     | EVENTO  |

|        | PE13 | -        | TIM1_CH3  | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_D10               | -        | -     | EVENTO  |

|        | PE14 | -        | TIM1_CH4  | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_D11               | -        | -     | EVENTO  |

|        | PE15 | -        | TIM1_BKIN | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -            | FSMC_D12               | -        | -     | EVENTO  |

#### Table 10. Alternate function mapping (continued)

DocID15818 Rev 13

5

63/182

| Symbol                               | Ratings                                                                 | Max.  | Unit |

|--------------------------------------|-------------------------------------------------------------------------|-------|------|

| - <b>,</b>                           |                                                                         |       |      |

| I <sub>VDD</sub>                     | Total current into V <sub>DD</sub> power lines (source) <sup>(1)</sup>  | 120   |      |

| I <sub>VSS</sub>                     | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>        | 120   |      |

| I <sub>IO</sub>                      | Output current sunk by any I/O and control pin                          | 25    |      |

|                                      | Output current source by any I/Os and control pin                       | 25    | mA   |

| ı (2)                                | Injected current on five-volt tolerant I/O <sup>(3)</sup>               | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                        | ±5    |      |

| $\Sigma I_{\rm INJ(PIN)}^{(4)}$      | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ±25   |      |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See note in Section 6.3.20: 12-bit ADC characteristics.

3. Positive injection is not possible on these I/Os. A negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 11* for the values of the maximum allowed input voltage.

4. A positive injection is induced by  $V_{IN}$  >  $V_{DD}$  while a negative injection is induced by  $V_{IN}$  <  $V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 11* for the values of the maximum allowed input voltage.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 125         | °C   |

## 6.3 Operating conditions

## 6.3.1 General operating conditions

#### Table 14. General operating conditions

| Symbol             | Parameter                     | Conditions | Min | Max | Unit |

|--------------------|-------------------------------|------------|-----|-----|------|

| f <sub>HCLK</sub>  | Internal AHB clock frequency  | -          | 0   | 120 |      |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency | -          | 0   | 30  | MHz  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency | -          | 0   | 60  |      |

| Symbol                                 | Parameter                                                                                        | Conditions                                               | Min                | Max                  | Unit |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------|----------------------|------|--|

| V <sub>DD</sub>                        | Standard operating voltage                                                                       | -                                                        | 1.8 <sup>(1)</sup> | 3.6                  |      |  |

| V <sub>DDA</sub> <sup>(2)</sup>        | Analog operating voltage<br>(ADC limited to 1 M samples)                                         | Must be the same potential as $V_{DD}^{(3)}$             | 1.8 <sup>(1)</sup> | 3.6                  |      |  |

| VDDA` '                                | Analog operating voltage<br>(ADC limited to 2 M samples)                                         |                                                          | 2.4                | 3.6                  |      |  |

| V <sub>BAT</sub>                       | Backup operating voltage                                                                         | -                                                        | 1.65               | 3.6                  |      |  |

|                                        | Input voltage on RST and FT pins                                                                 | $2 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | -0.3               | 5.5                  | V    |  |

| V                                      | input voltage on KST and FT pins                                                                 | $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2 \text{ V}$ | -0.3               | 5.2                  |      |  |

| V <sub>IN</sub>                        | Input voltage on TTa pins                                                                        | -                                                        | -0.3               | V <sub>DD</sub> +0.3 |      |  |

|                                        | Input voltage on BOOT0 pin                                                                       | -                                                        | 0                  | 9                    |      |  |

| V <sub>CAP1</sub><br>V <sub>CAP2</sub> | Internal core voltage to be supplied externally in REGOFF mode                                   | -                                                        | 1.1                | 1.3                  |      |  |

|                                        |                                                                                                  | LQFP64                                                   | -                  | 444                  |      |  |

|                                        | Power dissipation at $T_A = 85$ °C for<br>suffix 6 or $T_A = 105$ °C for suffix 7 <sup>(4)</sup> | WLCSP64+2                                                | -                  | 392                  | mW   |  |

| Р                                      |                                                                                                  | LQFP100                                                  | -                  | 434                  |      |  |

| PD                                     |                                                                                                  | LQFP144                                                  | -                  | 500                  |      |  |

|                                        |                                                                                                  | LQFP176                                                  | -                  | 526                  |      |  |

|                                        |                                                                                                  | UFBGA176                                                 | -                  | 513                  |      |  |

|                                        | Ambient temperature for 6 suffix                                                                 | Maximum power dissipation                                | -40                | 85                   | °C   |  |

| Та                                     | version                                                                                          | Low-power dissipation <sup>(5)</sup>                     | -40                | 105                  |      |  |

| IA                                     | Ambient temperature for 7 suffix                                                                 | Maximum power dissipation                                | -40                | 105                  | °C   |  |

|                                        | version                                                                                          | Low-power dissipation <sup>(5)</sup>                     | -40                | 125                  | C    |  |

| TJ                                     | Junction temperature range                                                                       | 6 suffix version                                         | -40                | 105                  | °C   |  |

| IJ                                     | Sunction temperature range                                                                       | 7 suffix version                                         | -40                | 125                  |      |  |

Table 14. General operating conditions (continued)

On devices in WLCSP64+2 package, if IRROFF is set to V<sub>DD</sub>, the supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

2. When the ADC is used, refer to *Table 66: ADC characteristics*.

3. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and power-down operation.

4. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

5. In low-power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$ .

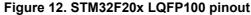

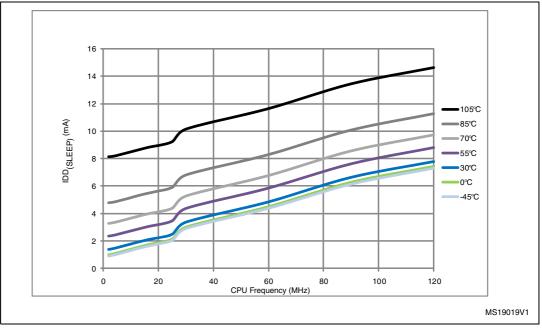

Figure 27. Typical current consumption vs. temperature in Sleep mode, peripherals ON

Figure 28. Typical current consumption vs. temperature in Sleep mode, peripherals OFF

| Per  | ripheral <sup>(1)</sup> | Typical consumption at 25 °C | Unit |

|------|-------------------------|------------------------------|------|

|      | SDIO                    | 0.69                         |      |

|      | TIM1                    | 1.06                         |      |

|      | TIM8                    | 1.03                         |      |

|      | TIM9                    | 0.58                         |      |

|      | TIM10                   | 0.37                         |      |

| APB2 | TIM11                   | 0.39                         | mA   |

| AFBZ | ADC1 <sup>(4)</sup>     | 2.13                         | ША   |

|      | ADC2 <sup>(4)</sup>     | 2.04                         |      |

|      | ADC3 <sup>(4)</sup>     | 2.12                         |      |

|      | SPI1                    | 1.20                         |      |

|      | USART1                  | 0.38                         |      |

|      | USART6                  | 0.37                         |      |

|  | Table 26. Peri | pheral current | consumption | (continued) |

|--|----------------|----------------|-------------|-------------|

|--|----------------|----------------|-------------|-------------|

1. External clock is 25 MHz (HSE oscillator with 25 MHz crystal) and PLL is on.

2. EN1 bit is set in DAC\_CR register.

3. EN2 bit is set in DAC\_CR register.

4.  $f_{ADC} = f_{PCLK2}/2$ , ADON bit set in ADC\_CR2 register.

## 6.3.7 Wakeup time from low-power mode

The wakeup times given in *Table 27* is measured on a wakeup phase with a 16 MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                                 | Parameter                                                                                    | Min <sup>(1)</sup> | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit |

|----------------------------------------|----------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>    | Wakeup from Sleep mode                                                                       | -                  | 1                  | -                  | μs   |

|                                        | Wakeup from Stop mode (regulator in Run mode)                                                | -                  | 13                 | -                  |      |

| t <sub>WUSTOP</sub> <sup>(2)</sup>     | Wakeup from Stop mode (regulator in low-power mode)                                          | -                  | 17                 | 40                 | us   |

|                                        | Wakeup from Stop mode (regulator in low-power mode and Flash memory in Deep power down mode) | -                  | 110                | -                  | F -  |

| t <sub>WUSTDBY</sub> <sup>(2)(3)</sup> | Wakeup from Standby mode                                                                     | 260                | 375                | 480                | μs   |

1. Guaranteed by characterization results, not tested in production.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3.  $t_{WUSTDBY}$  minimum and maximum values are given at 105 °C and -45 °C, respectively.

## 6.3.11 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 42: EMI characteristics*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|-----------------------|------|-----|--------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                 | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                  | %    |

| MODEPER * INCSTEP | -                     | -    | -   | 2 <sup>15</sup> –1 | -    |

| Table 36. | SSCG | parameters | constraint |

|-----------|------|------------|------------|

1. Guaranteed by design, not tested in production.

#### Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

```

MODEPER = round[f_{PLL \ IN}/ \ (4 \times f_{Mod})]

```

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round

$$[10^{6}/(4 \times 10^{3})] = 250$$

#### **Equation 2**

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[

$$((2^{15} - 1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

f<sub>VCO OUT</sub> must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/ ((2<sup>15</sup> - 1) × PLLN)

As a result:

$$md_{quantized} \% = (250 \times 126 \times 100 \times 5) / ((2^{15} - 1) \times 240) = 2.0002\%$$

(peak)

DocID15818 Rev 13

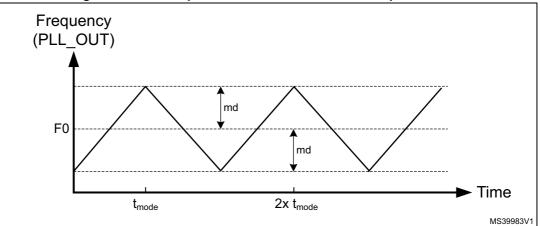

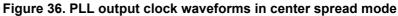

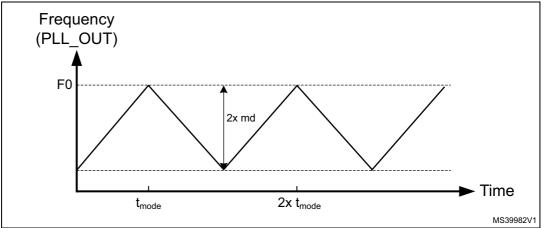

*Figure 36* and *Figure 37* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is f<sub>PLL\_OUT</sub> nominal.

T<sub>mode</sub> is the modulation period.

md is the modulation depth.

Figure 37. PLL output clock waveforms in down spread mode

## 6.3.12 Memory characteristics

### Flash memory

The characteristics are given at  $T_{\text{A}}$  = –40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

| Symbol                            | Parameter                                                                                             | Conditions                          | Min                  | Max | Unit |

|-----------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(2)</sup>    | tput low level voltage for an I/O pin<br>nen 8 pins are sunk at same time<br>$I_{IO} = +8 \text{ mA}$ |                                     | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time                         | $2.7 V < V_{DD} < 3.6 V$            | V <sub>DD</sub> 0.4  | -   | v    |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time                             | TTL ports<br>I <sub>IO</sub> =+ 8mA | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time                         | $2.7 V < V_{DD} < 3.6 V$            | 2.4                  | -   | v    |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time                             | I <sub>IO</sub> = +20 mA            | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time                         | 2.7 V < V <sub>DD</sub> < 3.6 V     | V <sub>DD</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time                             | I <sub>IO</sub> = +6 mA             | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time                         | 2 V < V <sub>DD</sub> < 2.7 V       | V <sub>DD</sub> -0.4 | -   | v    |

PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. to drive an LED).

- 2. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

- 3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 12 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

- 4. Guaranteed by characterization results, not tested in production.

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 39* and *Table 48*, respectively.

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                  | Min | Тур | Max | Unit |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

|                                               |                                                  |                                                                                 | $C_L$ = 50 pF, $V_{DD}$ > 2.70 V                            | -   | -   | 4   |      |

|                                               | f                                                | Maximum frequency <sup>(2)</sup>                                                | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 2   | MHz  |

|                                               | Imax(IO)out                                      |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 8   |      |

| 00                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 4   |      |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.8 V to<br>3.6 V | -   | -   | 100 | ns   |

| Table 4 | 48. | I/O | AC | characteristics <sup>(1)</sup> |

|---------|-----|-----|----|--------------------------------|

|---------|-----|-----|----|--------------------------------|

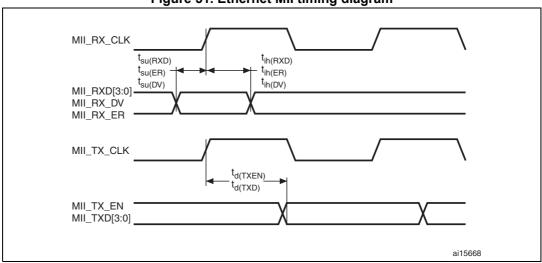

*Table 65* gives the list of Ethernet MAC signals for MII and *Figure 50* shows the corresponding timing diagram.

| Table 65, Dy | namics char | acteristics:  | Ethernet | MAC sid | anals for M   | 111 |

|--------------|-------------|---------------|----------|---------|---------------|-----|

|              |             | uotor 15t105. | Ethornot | MIAO 31 | jiiuis ioi ii |     |

| Symbol               | Rating                           | Min | Тур | Мах | Unit |

|----------------------|----------------------------------|-----|-----|-----|------|

| t <sub>su(RXD)</sub> | Receive data setup time          | 7.5 | -   | -   | ns   |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 1   | -   | -   | ns   |

| t <sub>su(DV)</sub>  | Data valid setup time            | 4   | -   | -   | ns   |

| t <sub>ih(DV)</sub>  | Data valid hold time             | 0   | -   | -   | ns   |

| t <sub>su(ER)</sub>  | Error setup time                 | 3.5 | -   | -   | ns   |

| t <sub>ih(ER)</sub>  | Error hold time                  | 0   | -   | -   | ns   |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | -   | 11  | 14  | ns   |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | -   | 11  | 14  | ns   |

### CAN (controller area network) interface

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CANTX and CANRX).

## 6.3.23 V<sub>BAT</sub> monitoring characteristics

Table 70. V<sub>BAT</sub> monitoring characteristics

| Symbol                                | Parameter                                                           | Min | Тур | Max | Unit |

|---------------------------------------|---------------------------------------------------------------------|-----|-----|-----|------|

| R                                     | Resistor bridge for V <sub>BAT</sub>                                | -   | 50  | -   | KΩ   |

| Q                                     | Ratio on V <sub>BAT</sub> measurement                               | -   | 2   | -   |      |

| Er <sup>(1)</sup>                     | Error on Q                                                          | –1  | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(2)(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub> (1 mV accuracy) | 5   | -   | -   | μs   |

1. Guaranteed by design, not tested in production.

2. Shortest sampling time can be determined in the application by multiple iterations.

## 6.3.24 Embedded reference voltage

The parameters given in *Table 71* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

|                                       | g-                                                                 |                                   |      |      |      |        |

|---------------------------------------|--------------------------------------------------------------------|-----------------------------------|------|------|------|--------|

| Symbol                                | Parameter                                                          | Conditions                        | Min  | Тур  | Мах  | Unit   |

| V <sub>REFINT</sub>                   | Internal reference voltage                                         | –40 °C < T <sub>A</sub> < +105 °C | 1.18 | 1.21 | 1.24 | V      |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the internal reference voltage      | -                                 | 10   | -    | -    | μs     |

| V <sub>RERINT_s</sub>                 | Internal reference voltage<br>spread over the temperature<br>range | V <sub>DD</sub> = 3 V             | -    | 3    | 5    | mV     |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                            | -                                 | -    | 30   | 50   | ppm/°C |

| t <sub>START</sub> <sup>(2)</sup>     | Startup time                                                       | -                                 | -    | 6    | 10   | μs     |

Table 71. Embedded internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design, not tested in production.

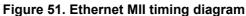

## 6.3.25 FSMC characteristics

### Asynchronous waveforms and timings

*Figure 57* through *Figure 60* represent asynchronous waveforms and *Table 72* through *Table 75* provide the corresponding timings. The results shown in these tables are obtained with the following FSMC configuration:

- AddressSetupTime = 1

- AddressHoldTime = 1

- DataSetupTime = 1

- BusTurnAroundDuration = 0x0

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

| Symbol                     | Parameter                                    | Min | Max | Unit |

|----------------------------|----------------------------------------------|-----|-----|------|

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high               | 4   | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)       | -   | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625)     | 3   | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>  | FSMC_CLK high to FSMC_NOE low                | -   | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>  | FSMC_CLK low to FSMC_NOE high                | 1.5 | -   | ns   |

| t <sub>su(DV-CLKH)</sub>   | FSMC_D[15:0] valid data before FSMC_CLK high | 8   | -   | ns   |

| t <sub>h(CLKH-DV)</sub>    | FSMC_D[15:0] valid data after FSMC_CLK high  | 0   | -   | ns   |

## Table 78. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

#### Figure 64. Synchronous non-multiplexed PSRAM write timings

#### Table 79. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                               | Min                    | Max | Unit |

|---------------------------|-----------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>       | FSMC_CLK period                         | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub> | FSMC_CLK low to FSMC_NEx low (x=02)     | -                      | 1   | ns   |

| t <sub>d(CLKL-NExH)</sub> | FSMC_CLK low to FSMC_NEx high (x= 02) 1 |                        | -   | ns   |

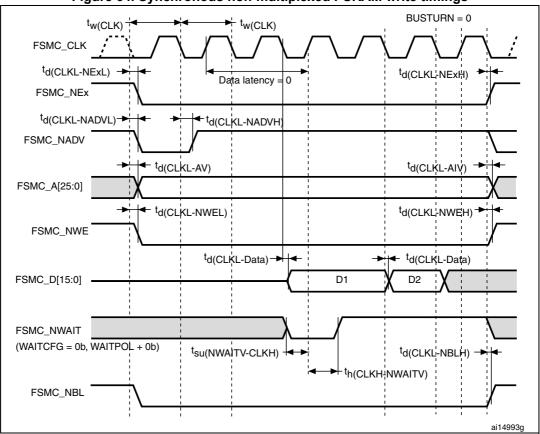

Figure 70. PC Card/CompactFlash controller waveforms for I/O space write access

# Table 80. Switching characteristics for PC Card/CF read and write cycles in attribute/common space<sup>(1)(2)</sup>

| Symbol                    | Parameter                                    | Min                      | Max                    | Unit |

|---------------------------|----------------------------------------------|--------------------------|------------------------|------|

| t <sub>v(NCEx-A)</sub>    | FSMC_Ncex low to FSMC_Ay valid               | -                        | 0                      | ns   |

| t <sub>h(NCEx_AI)</sub>   | FSMC_NCEx high to FSMC_Ax invalid            | 4                        | -                      | ns   |

| t <sub>d(NREG-NCEx)</sub> | FSMC_NCEx low to FSMC_NREG valid             | -                        | 3.5                    | ns   |

| t <sub>h(NCEx-NREG)</sub> | FSMC_NCEx high to FSMC_NREG invalid          | T <sub>HCLK</sub> + 4    | -                      | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                        | 5T <sub>HCLK</sub> + 1 | ns   |

| t <sub>d(NCEx-NOE)</sub>  | FSMC_NCEx low to FSMC_NOE low                | -                        | 5T <sub>HCLK</sub>     | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low width                           | 8T <sub>HCLK</sub> - 0.5 | 8T <sub>HCLK</sub> + 1 | ns   |

| t <sub>d(NOE_NCEx)</sub>  | FSMC_NOE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> + 2.5 | -                      | ns   |

| t <sub>su (D-NOE)</sub>   | FSMC_D[15:0] valid data before FSMC_NOE high | 4                        | -                      | ns   |

| t <sub>h (N0E-D)</sub>    | FSMC_N0E high to FSMC_D[15:0] invalid        | 2                        | -                      | ns   |

| t <sub>w(NWE)</sub>       | FSMC_NWE low width                           | 8T <sub>HCLK</sub> - 1   | 8T <sub>HCLK</sub> + 4 | ns   |

| t <sub>d(NWE_NCEx</sub> ) | FSMC_NWE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> + 1.5 | -                      | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                        | 5HCLK+ 1               | ns   |

| t <sub>v (NWE-D)</sub>    | FSMC_NWE low to FSMC_D[15:0] valid           | -                        | 0                      | ns   |

| t <sub>h (NWE-D)</sub>    | FSMC_NWE high to FSMC_D[15:0] invalid        | 8T <sub>HCLK</sub>       | -                      | ns   |

| t <sub>d (D-NWE)</sub>    | FSMC_D[15:0] valid before FSMC_NWE high      | 13T <sub>HCLK</sub>      | -                      | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

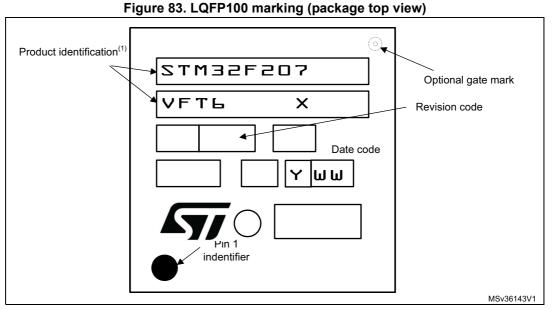

### **Device marking**

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 7.5 LQFP176 package information

Figure 87. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline

1. Drawing is not to scale.

| Table 92. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

|        | Dimensions  |      |        |                       |      |        |

|--------|-------------|------|--------|-----------------------|------|--------|

| Symbol | millimeters |      |        | inches <sup>(1)</sup> |      |        |

|        | Min.        | Тур. | Max.   | Min.                  | Тур. | Max.   |

| А      | -           | -    | 1.600  | -                     | -    | 0.0630 |

| A1     | 0.050       | -    | 0.150  | 0.0020                | -    | 0.0059 |

| A2     | 1.350       | -    | 1.450  | 0.0531                | -    | 0.0571 |

| b      | 0.170       | -    | 0.270  | 0.0067                | -    | 0.0106 |

| с      | 0.090       | -    | 0.200  | 0.0035                | -    | 0.0079 |

| D      | 23.900      | -    | 24.100 | 0.9409                | -    | 0.9488 |

DocID15818 Rev 13

| Table 97. Document revision history (continued)       Date     Revision       Changes |  |  |  |  |

|---------------------------------------------------------------------------------------|--|--|--|--|

| Date R                                                                                |  |  |  |  |

| Date       R         13-Jul-2010       (cc                                            |  |  |  |  |

| Data        | Table 97. Document revision history (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date        | Revision                                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|             |                                                 | Updated <i>Typical and maximum current consumption</i> conditions, as well<br>as <i>Table 21: Typical and maximum current consumption in Run mode,</i><br><i>code with data processing running from Flash memory (ART<br/>accelerator disabled)</i> and <i>Table 20: Typical and maximum current</i><br><i>consumption in Run mode, code with data processing running from</i><br><i>Flash memory (ART accelerator enabled) or RAM.</i> Added Figure 23,<br><i>Figure 24, Figure 25, and Figure 26.</i><br>Updated <i>Table 22: Typical and maximum current consumption in Sleep</i> |  |  |  |

| 1           |                                                 | mode, and added Figure 27 and Figure 28.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|             |                                                 | Updated Table 23: Typical and maximum current consumptions in Stop mode. Added Figure 29: Typical current consumption vs. temperature in Stop mode.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|             |                                                 | Updated Table 24: Typical and maximum current consumptions in<br>Standby mode and Table 25: Typical and maximum current<br>consumptions in VBAT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|             |                                                 | Updated On-chip peripheral current consumption conditions and Table 26: Peripheral current consumption.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|             |                                                 | Updated t <sub>WUSTDBY</sub> and t <sub>WUSTOP</sub> , and added <i>Note 3</i> in <i>Table 27: Low-power mode wakeup timings</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|             |                                                 | Maximum f <sub>HSE_ext</sub> and minimum t <sub>w(HSE)</sub> values updated in <i>Table 28: High-speed external user clock characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|             |                                                 | Updated C and $g_m$ in <i>Table 30: HSE 4-26 MHz oscillator characteristics</i> .<br>Updated $R_F$ , $I_2$ , $g_m$ , and $t_{su(LSE)}$ in <i>Table 31: LSE oscillator characteristics (fLSE = 32.768 kHz)</i> .                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 22-Apr-2011 | 6<br>(continued)                                | Added <i>Note 1</i> and updated ACC <sub>HSI</sub> , IDD <sub>(HSI</sub> , and t <sub>su(HSI)</sub> in <i>Table 32:</i><br><i>HSI oscillator characteristics</i> . Added <i>Figure 34: ACCHSI versus</i><br><i>temperature</i> .                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|             |                                                 | Updated f <sub>LSI</sub> , t <sub>su(LSI)</sub> and IDD <sub>(LSI)</sub> in <i>Table 33: LSI oscillator</i> characteristics. Added Figure 35: ACCLSI versus temperature                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|             |                                                 | <i>Table 34: Main PLL characteristics</i> : removed note 1, updated $t_{LOCK}$ , jitter, IDD <sub>(PLL)</sub> and IDD <sub>A(PLL)</sub> , added <i>Note 2</i> for $f_{PLL_IN}$ minimum and maximum values.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|             |                                                 | Table 35: PLLI2S (audio PLL) characteristics: removed note 1, updated $t_{LOCK}$ , jitter, IDD $(PLLI2S)$ and IDD $(PLLI2S)$ , added Note 2 for f $PLLI2S_{IN}$ minimum and maximum values.                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|             |                                                 | Added Note 1 in Table 36: SSCG parameters constraint.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|             |                                                 | Updated <i>Table 37: Flash memory characteristics</i> . Modified <i>Table 38:</i><br><i>Flash memory programming</i> and added <i>Note 2</i> for t <sub>prog</sub> . Updated t <sub>prog</sub><br>and added <i>Note 1</i> in <i>Table 39: Flash memory programming with VPP</i> .                                                                                                                                                                                                                                                                                                    |  |  |  |

|             |                                                 | Modified Figure 40: Recommended NRST pin protection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|             |                                                 | Updated Table 42: EMI characteristics and EMI monitoring conditions in<br>Section : Electromagnetic Interference (EMI). Added Note 2 related to                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|             |                                                 | V <sub>ESD(HBM)</sub> in <i>Table 43: ESD absolute maximum ratings</i> .<br>Updated <i>Table 48: I/O AC characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|             |                                                 | Added Section 6.3.15: I/O current injection characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|             |                                                 | Modified maximum frequency values and conditions in <i>Table 48: I/O AC characteristics</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|             |                                                 | Updated $t_{res(TIM)}$ in Table 50: Characteristics of TIMx connected to the APB1 domain. Modified $t_{res(TIM)}$ and $f_{EXT}$ Table 51: Characteristics of TIMx connected to the APB2 domain.                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

Table 97. Document revision history (continued)

| Table 97. Document revision history (continued) |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                            | Revision          | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

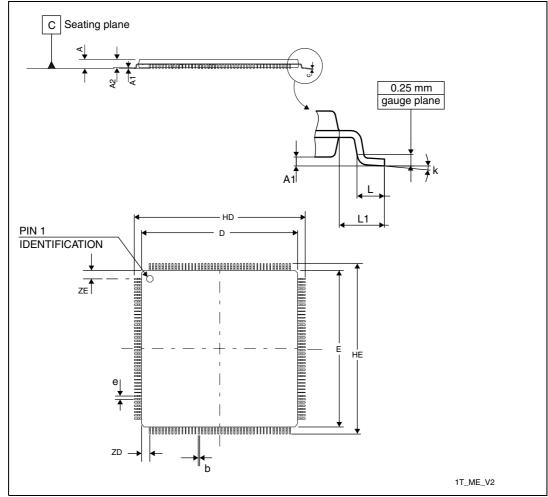

| 04-Nov-2013                                     | 11<br>(continued) | Removed Appendix A Application block diagrams.<br>Updated Figure 77: LQFP64 – 10 x 10 mm 64 pin low-profile quad flat<br>package outline and Table 87: LQFP64 – 10 x 10 mm 64 pin low-profile<br>quad flat package mechanical data. Updated Figure 80: LQFP100, 14 x<br>14 mm 100-pin low-profile quad flat package outline, Figure 83:<br>LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline,<br>Figure 86: LQFP176 - Low profile quad flat package 24 × 24 × 1.4 mm,<br>package outline. Updated Figure 88: UFBGA176+25 - ultra thin fine<br>pitch ball grid array 10 × 10 × 0.6 mm, package outline and Figure 88:<br>UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm,<br>package outline.                                                                                                                                                                      |  |  |

| 27-Oct-2014                                     | 12                | Updated V <sub>BAT</sub> voltage range in <i>Figure 19: Power supply scheme</i> . Added caution note in <i>Section 6.1.6: Power supply scheme</i> .<br>Updated V <sub>IN</sub> in <i>Table 14: General operating conditions</i> .<br>Removed note 1 in <i>Table 23: Typical and maximum current consumptions in Stop mode</i> .<br>Updated <i>Table 45: I/O current injection susceptibility</i> , <i>Section 6.3.16: I/O port characteristics</i> and <i>Section 6.3.17: NRST pin characteristics</i> .<br>Removed note 3 in <i>Table 69: Temperature sensor characteristics</i> .<br>Updated <i>Figure 79: WLCSP64+2 - 0.400 mm pitch wafer level chip size package outline</i> and <i>Table 88: WLCSP64+2 - 0.400 mm pitch wafer level chip size package mechanical data</i> . Added <i>Figure 83: LQFP100 marking (package top view)</i> and <i>Figure 86: LQFP144 marking (package top view)</i> . |  |  |

| 2-Feb-2016                                      | 13                | Updated Section 1: Introduction.<br>Updated Table 32: HSI oscillator characteristics and its footnotes.<br>Updated Figure 36: PLL output clock waveforms in center spread mode,<br>Figure 37: PLL output clock waveforms in down spread mode,<br>Figure 54: Power supply and reference decoupling (VREF+ not<br>connected to VDDA) and Figure 55: Power supply and reference<br>decoupling (VREF+ connected to VDDA).<br>Updated Section 7: Package information and its subsections.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

Table 97. Document revision history (continued)