# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| D | e | t | а | I | l | s |

|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 120MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 82                                                                    |

| Program Memory Size        | 1MB (1M × 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 132K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205vgt6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

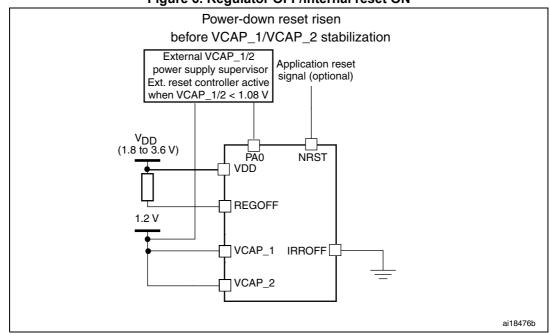

Figure 6. Regulator OFF/internal reset ON

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach 1.08 V is faster than the time for  $V_{DD}$  to reach 1.8 V, then PA0 should be kept low to cover both conditions: until  $V_{CAP_1}$  and  $V_{CAP_2}$  reach 1.08 V and until  $V_{DD}$  reaches 1.8 V (see *Figure 8*).

- Otherwise, If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach 1.08 V is slower than the time for V<sub>DD</sub> to reach 1.8 V, then PA0 should be asserted low externally (see *Figure 9*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below 1.08 V and V<sub>DD</sub> is higher than 1.8 V, then a reset must be asserted on PA0 pin.

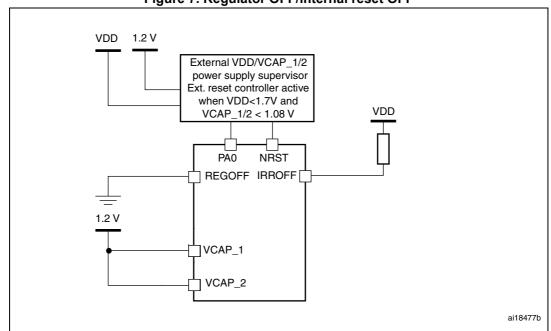

#### **Regulator OFF/internal reset OFF**

On WLCSP64+2 package, this mode activated by connecting REGOFF to V<sub>SS</sub> and IRROFF to V<sub>DD</sub>. IRROFF cannot be activated in conjunction with REGOFF. This mode is available only on the WLCSP64+2 package. It allows to supply externally a 1.2 V voltage source through V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> pins. In this mode, the integrated power-on reset (POR)/ power-down reset (PDR) circuitry is disabled.

An external power supply supervisor should monitor both the external 1.2 V and the external  $V_{DD}$  supply voltage, and should maintain the device in reset mode as long as they remain below a specified threshold. The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.8 V. This supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range. A comprehensive set of power-saving modes allows to design low-power applications.

Figure 7. Regulator OFF/internal reset OFF

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains (see *Figure 8*).

- PA0 should be kept low to cover both conditions: until  $V_{CAP_1}$  and  $V_{CAP_2}$  reach 1.08 V, and until  $V_{DD}$  reaches 1.7 V.

- NRST should be controlled by an external reset controller to keep the device under reset when V<sub>DD</sub> is below 1.7 V (see *Figure 9*).

In this mode, when the internal reset is OFF, the following integrated features are no more supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled.

- The brownout reset (BOR) circuitry is disabled.

- The embedded programmable voltage detector (PVD) is disabled.

- V<sub>BAT</sub> functionality is no more available and V<sub>BAT</sub> pin should be connected to VDD.

## 3.20 Timers and watchdogs

The STM32F20x devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

*Table 5* compares the features of the advanced-control, general-purpose and basic timers.

| Timer type           | Timer           | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>output | Max<br>interface<br>clock | Max<br>timer<br>clock |

|----------------------|-----------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---------------------------------|-------------------------|---------------------------|-----------------------|

| Advanced-<br>control | TIM1,<br>TIM8   | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                     | 60<br>MHz                 | 120<br>MHz            |

| General              | TIM2,<br>TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                      | 30<br>MHz                 | 60<br>MHz             |

| purpose              | TIM3,<br>TIM4   | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                      | 30<br>MHz                 | 60<br>MHz             |

| Basic                | TIM6,<br>TIM7   | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                      | 30<br>MHz                 | 60<br>MHz             |

|                      | TIM9            | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                      | 60<br>MHz                 | 120<br>MHz            |

| General              | TIM10,<br>TIM11 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                      | 60<br>MHz                 | 120<br>MHz            |

| purpose              | TIM12           | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                      | 30<br>MHz                 | 60<br>MHz             |

|                      | TIM13,<br>TIM14 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                      | 30<br>MHz                 | 60<br>MHz             |

Table 5. Timer feature comparison

## 3.20.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

CAN is used). The 256 bytes of SRAM which are allocated for each CAN are not shared with any other peripheral.

## 3.28 Universal serial bus on-the-go full-speed (OTG\_FS)

The devices embed an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- Combined Rx and Tx FIFO size of 320 × 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 4 bidirectional endpoints

- 8 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

- Internal FS OTG PHY support

### 3.29 Universal serial bus on-the-go high-speed (OTG\_HS)

The STM32F20x devices embed a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- Combined Rx and Tx FIFO size of 1024× 35 bits with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 6 bidirectional endpoints

- 12 host channels with periodic OUT support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode. The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

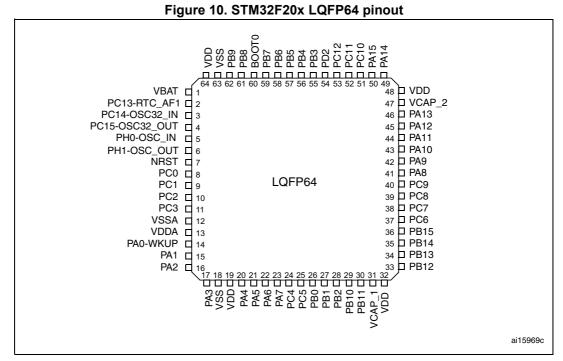

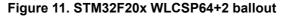

## 4 Pinouts and pin description

1. The above figure shows the package top view.

|   | 1    | 2      | 3      | 4   | 5   | 6     | 7      | 8      | 9                |

|---|------|--------|--------|-----|-----|-------|--------|--------|------------------|

| А | PA14 | PA15   | PC12   | PB3 | PB5 | PB7   | PB9    | VDD    | V <sub>BAT</sub> |

| В | VSS  | PA13   | PC10   | PB4 | PB6 | BOOT0 | PB8    | PC13   | PC14             |

| С | PA12 | VCAP_2 | PC11   |     |     |       | PD2    | IRROFF | PC15             |

| D | PC9  | PA11   | PA10   |     |     |       | PC2    | VSS    | VDD              |

| E | VDD  | PA8    | PA9    |     |     |       | PA0    | NRST   | PH0-<br>OSC_IN   |

| F | VSS  | PC7    | PC8    |     |     |       | VREF+  | PC1    | PH1-<br>OSC_OUT  |

| G | PB15 | PC6    | PC5    |     |     |       | PA3    | PC3    | PC0              |

| н | PB14 | PB13   | PB10   | PC4 | PA6 | PA5   | REGOFF | PA1    | VSS_5            |

| J | PB12 | PB11   | VCAP_1 | PB2 | PB1 | PB0   | PA7    | PA4    | PA2              |

|   |      |        |        |     |     |       |        |        |                  |

|   |      |        |        |     |     |       |        |        |                  |

1. The above figure shows the package top view.

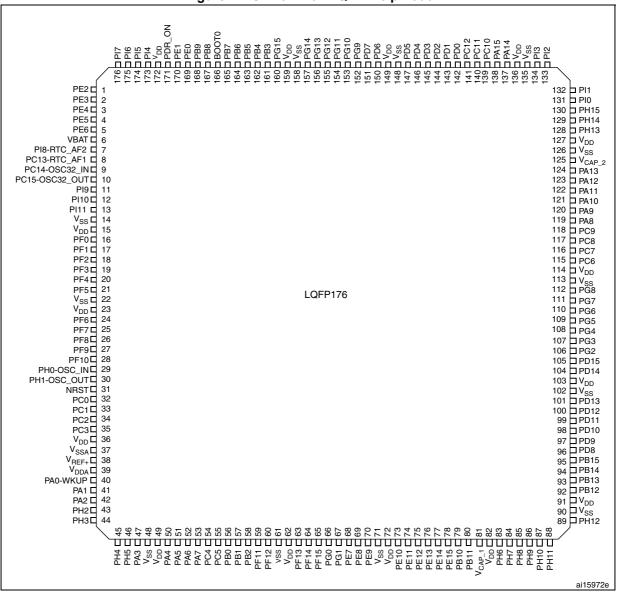

#### Pinouts and pin description

| Figure 14. | STM32F20x L | .QFP176 pi | nout |

|------------|-------------|------------|------|

|------------|-------------|------------|------|

1. RFU means "reserved for future use". This pin can be tied to  $V_{DD}$ ,  $V_{SS}$  or left unconnected.

2. The above figure shows the package top view.

|        |           | Pi      | ns      |         |          |                                                      |          |               |      |                                                                                                      |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                                                  | Additional<br>functions |

| -      | -         | 38      | 58      | 68      | R8       | PE7                                                  | I/O      | FT            | -    | FSMC_D4,TIM1_ETR,<br>EVENTOUT                                                                        | -                       |

| -      | -         | 39      | 59      | 69      | P8       | PE8                                                  | I/O      | FT            | -    | FSMC_D5,TIM1_CH1N,<br>EVENTOUT                                                                       | -                       |

| -      | -         | 40      | 60      | 70      | P9       | PE9                                                  | I/O      | FT            | -    | FSMC_D6,TIM1_CH1,<br>EVENTOUT                                                                        | -                       |

| -      | -         | -       | 61      | 71      | M9       | V <sub>SS</sub>                                      | S        |               | -    | -                                                                                                    | -                       |

| -      | -         | -       | 62      | 72      | N9       | V <sub>DD</sub>                                      | S        |               | -    | -                                                                                                    | -                       |

| -      | -         | 41      | 63      | 73      | R9       | PE10                                                 | I/O      | FT            | -    | FSMC_D7,TIM1_CH2N,<br>EVENTOUT                                                                       | -                       |

| -      | -         | 42      | 64      | 74      | P10      | PE11                                                 | I/O      | FT            | -    | FSMC_D8,TIM1_CH2,<br>EVENTOUT                                                                        | -                       |

| -      | -         | 43      | 65      | 75      | R10      | PE12                                                 | I/O      | FT            | -    | FSMC_D9,TIM1_CH3N,<br>EVENTOUT                                                                       | -                       |

| -      | -         | 44      | 66      | 76      | N11      | PE13                                                 | I/O      | FT            | -    | FSMC_D10,TIM1_CH3,<br>EVENTOUT                                                                       | -                       |

| -      | -         | 45      | 67      | 77      | P11      | PE14                                                 | I/O      | FT            | -    | FSMC_D11,TIM1_CH4,<br>EVENTOUT                                                                       | -                       |

| -      | -         | 46      | 68      | 78      | R11      | PE15                                                 | I/O      | FT            | -    | FSMC_D12,TIM1_BKIN,<br>EVENTOUT                                                                      | -                       |

| 29     | H3        | 47      | 69      | 79      | R12      | PB10                                                 | I/O      | FT            | -    | SPI2_SCK, I2S2_SCK,<br>I2C2_SCL,USART3_TX,OT<br>G_HS_ULPI_D3,ETH_MII_R<br>X_ER,TIM2_CH3,<br>EVENTOUT | -                       |

| 30     | J2        | 48      | 70      | 80      | R13      | PB11                                                 | I/O      | FT            | -    | I2C2_SDA, USART3_RX,<br>OTG_HS_ULPI_D4,<br>ETH_RMII_TX_EN,<br>ETH_MII_TX_EN,<br>TIM2_CH4, EVENTOUT   | -                       |

| 31     | J3        | 49      | 71      | 81      | M10      | V <sub>CAP_1</sub>                                   | S        |               | -    | -                                                                                                    | -                       |

| 32     | -         | 50      | 72      | 82      | N10      | V <sub>DD</sub>                                      | S        |               | -    | -                                                                                                    | -                       |

| -      | -         | -       | -       | 83      | M11      | PH6                                                  | I/O      | FT            | -    | I2C2_SMBA, TIM12_CH1,<br>ETH_MII_RXD2,<br>EVENTOUT                                                   | -                       |

| Table 8. STM32F20x pin and ball definitions (continue | d) |

|-------------------------------------------------------|----|

|                                                       | ,  |

|                 |                   |                                                                           |                   | Тур                       | Ma                        | x <sup>(1)</sup>           |      |

|-----------------|-------------------|---------------------------------------------------------------------------|-------------------|---------------------------|---------------------------|----------------------------|------|

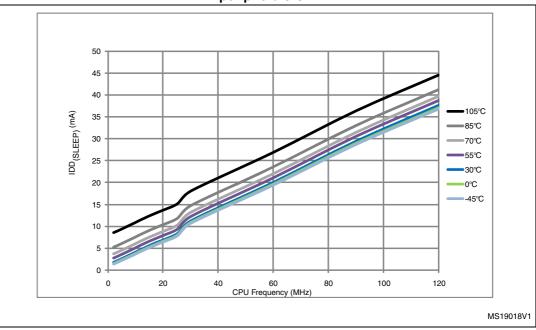

| Symbol          | Parameter         | Conditions                                                                | f <sub>HCLK</sub> | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                   |                                                                           | 120 MHz           | 38                        | 51                        | 61                         |      |

|                 |                   |                                                                           | 90 MHz            | 30                        | 43                        | 53                         |      |

|                 |                   |                                                                           | 60 MHz            | 20                        | 33                        | 43                         |      |

|                 |                   | <b>-</b> (2)                                                              | 30 MHz            | 11                        | 25                        | 35                         |      |

|                 |                   | External clock <sup>(2)</sup> ,<br>all peripherals enabled <sup>(3)</sup> | 25 MHz            | 8                         | 21                        | 31                         |      |

|                 | Supply current in |                                                                           | 16 MHz            | 6                         | 19                        | 29                         | mA   |

|                 |                   |                                                                           | 8 MHz             | 3.6                       | 17.0                      | 27.0                       |      |

|                 |                   |                                                                           | 4 MHz             | 2.4                       | 15.4                      | 25.3                       |      |

|                 |                   |                                                                           | 2 MHz             | 1.9                       | 14.9                      | 24.7                       |      |

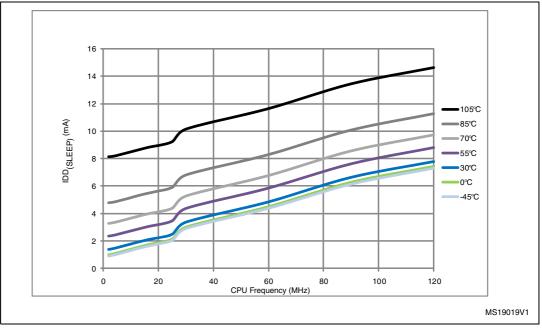

| I <sub>DD</sub> | Sleep mode        |                                                                           | 120 MHz           | 8                         | 21                        | 31                         | mA   |

|                 |                   |                                                                           | 90 MHz            | 7                         | 20                        | 30                         |      |

|                 |                   |                                                                           | 60 MHz            | 5                         | 18                        | 28                         |      |

|                 |                   |                                                                           | 30 MHz            | 3.5                       | 16.0                      | 26.0                       |      |

|                 |                   | External clock <sup>(2)</sup> , all peripherals disabled                  | 25 MHz            | 2.5                       | 16.0                      | 25.0                       |      |

|                 |                   |                                                                           | 16 MHz            | 2.1                       | 15.1                      | 25.0                       |      |

|                 |                   |                                                                           | 8 MHz             | 1.7                       | 15.0                      | 25.0                       |      |

|                 |                   |                                                                           | 4 MHz             | 1.5                       | 14.6                      | 24.6                       |      |

|                 |                   |                                                                           | 2 MHz             | 1.4                       | 14.2                      | 24.3                       |      |

| Table 22. Typical and maximum current | consumption in Sleep mode |

|---------------------------------------|---------------------------|

|---------------------------------------|---------------------------|

1. Guaranteed by characterization results, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 4 MHz and PLL is on when  $\rm f_{HCLK}$  > 25 MHz.

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

Figure 27. Typical current consumption vs. temperature in Sleep mode, peripherals ON

Figure 28. Typical current consumption vs. temperature in Sleep mode, peripherals OFF

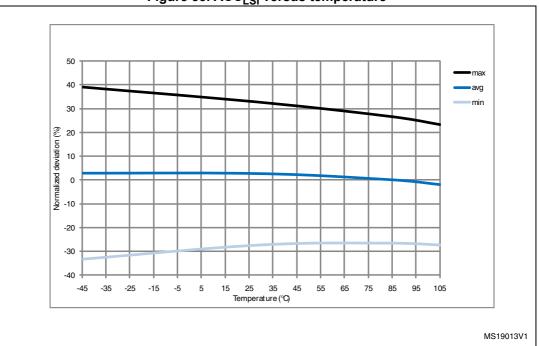

Figure 35. ACC<sub>LSI</sub> versus temperature

### 6.3.10 PLL characteristics

The parameters given in *Table 34* and *Table 35* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                  | Parameter                             | Conditions         | Min                 | Тур | Max                 | Unit |  |

|-------------------------|---------------------------------------|--------------------|---------------------|-----|---------------------|------|--|

| f <sub>PLL_IN</sub>     | PLL input clock <sup>(1)</sup>        | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 <sup>(2)</sup> | MHz  |  |

| f <sub>PLL_OUT</sub>    | PLL multiplier output clock           | -                  | 24                  | -   | 120                 | MHz  |  |

| f <sub>PLL48_</sub> OUT | 48 MHz PLL multiplier output<br>clock | -                  | -                   | -   | 48                  | MHz  |  |

| f <sub>VCO_OUT</sub>    | PLL VCO output                        | -                  | 192                 | -   | 432                 | MHz  |  |

| t                       | PLL lock time                         | VCO freq = 192 MHz | 75                  | -   | 200                 | 116  |  |

| t <sub>LOCK</sub>       |                                       | VCO freq = 432 MHz | 100                 | -   | 300                 | μs   |  |

Table 34. Main PLL characteristics

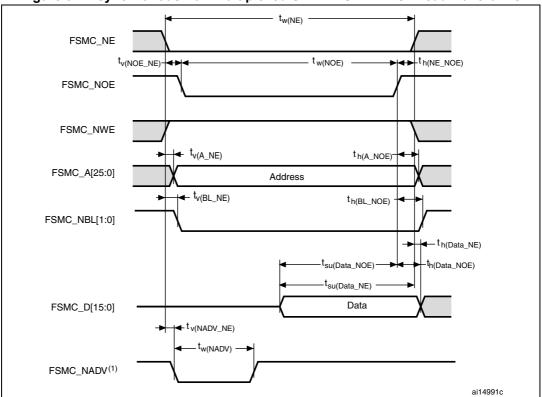

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

| Table 72. Asynchronous non-multi | plexed SRAM/PSRAM/NOR read timings <sup>(1)(2)</sup> |

|----------------------------------|------------------------------------------------------|

| Symbol                    | Parameter                               | Min                      | Мах                      | Unit |

|---------------------------|-----------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                        | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low            | 0.5                      | 2.5                      | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                       | 2T <sub>HCLK</sub> - 1   | 2T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time | 0                        | -                        | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid            | -                        | 4                        | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high   | 0                        | -                        | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid           | -                        | 0.5                      | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high   | 0                        | -                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time        | T <sub>HCLK</sub> + 0.5  | -                        | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOEx high setup time       | T <sub>HCLK</sub> + 2.5  | -                        | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high      | 0                        | -                        | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high      | 0                        | -                        | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low           | -                        | 2.5                      | ns   |

| t <sub>w(NADV</sub> )     | FSMC_NADV low time                      | -                        | T <sub>HCLK</sub> – 0.5  | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

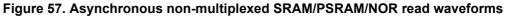

Figure 59. Asynchronous multiplexed PSRAM/NOR read waveforms

Table 74. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                                                | Min                     | Max                     | Unit |

|---------------------------|----------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                         | 3T <sub>HCLK</sub> -1   | 3T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                             | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                        | T <sub>HCLK</sub> -1    | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time                  | 0                       | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                             | -                       | 2                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                            | 1                       | 2.5                     | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                       | T <sub>HCLK</sub> – 1.5 | T <sub>HCLK</sub>       | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD(adress) valid hold time after<br>FSMC_NADV high) | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high                    | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL time after FSMC_NOE high                         | 0                       | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                            | -                       | 1                       | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time                         | T <sub>HCLK</sub> + 2   | -                       | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time                         | T <sub>HCLK</sub> + 3   | -                       | ns   |

| Symbol                   | Parameter                          | Min | Max | Unit |

|--------------------------|------------------------------------|-----|-----|------|

| t <sub>h(Data_NE)</sub>  | Data hold time after FSMC_NEx high | 0   | -   | ns   |

| t <sub>h(Data_NOE)</sub> | Data hold time after FSMC_NOE high | 0   | -   | ns   |

## Table 74. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

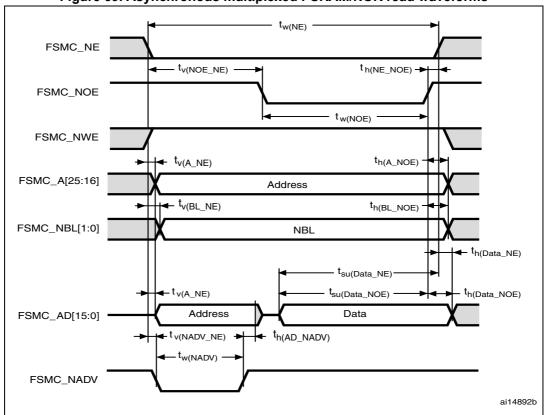

#### Figure 60. Asynchronous multiplexed PSRAM/NOR write waveforms

| Table 75. Asynchronous multiplexed PSRAM/NOR write | e timings <sup>(1)(2)</sup> |

|----------------------------------------------------|-----------------------------|

|----------------------------------------------------|-----------------------------|

|                         |                                                          |                                                      | -                     |      |

|-------------------------|----------------------------------------------------------|------------------------------------------------------|-----------------------|------|

| Symbol                  | Parameter                                                | Min                                                  | Мах                   | Unit |

| t <sub>w(NE)</sub>      | FSMC_NE low time                                         | 4T <sub>HCLK</sub> -1                                | 4T <sub>HCLK</sub> +1 | ns   |

| t <sub>v(NWE_NE)</sub>  | FSMC_NEx low to FSMC_NWE low                             | T <sub>HCLK</sub> - 1                                | T <sub>HCLK</sub>     | ns   |

| t <sub>w(NWE)</sub>     | FSMC_NWE low tim e                                       | C_NWE low tim e 2T <sub>HCLK</sub>                   |                       | ns   |

| t <sub>h(NE_NWE)</sub>  | FSMC_NWE high to FSMC_NE high hold time                  | high to FSMC_NE high hold time T <sub>HCLK</sub> - 1 |                       | ns   |

| t <sub>v(A_NE)</sub>    | FSMC_NEx low to FSMC_A valid                             | -                                                    | 0                     | ns   |

| t <sub>v(NADV_NE)</sub> | FSMC_NEx low to FSMC_NADV low                            | 1                                                    | 2                     | ns   |

| t <sub>w(NADV)</sub>    | FSMC_NADV low time                                       | T <sub>HCLK</sub> – 2                                | T <sub>HCLK</sub> + 2 | ns   |

| t <sub>h(AD_NADV)</sub> | FSMC_AD(adress) valid hold time after<br>FSMC_NADV high) | T <sub>HCLK</sub>                                    | -                     | ns   |

|                           | (00110110                                      |     |     |      |

|---------------------------|------------------------------------------------|-----|-----|------|

| Symbol                    | Parameter                                      | Min | Мах | Unit |

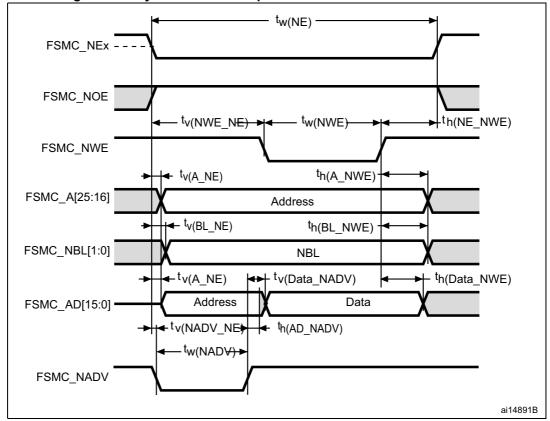

| t <sub>su(ADV-CLKH)</sub> | FSMC_A/D[15:0] valid data before FSMC_CLK high | 5   | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>  | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0   | -   | ns   |

#### Table 76. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

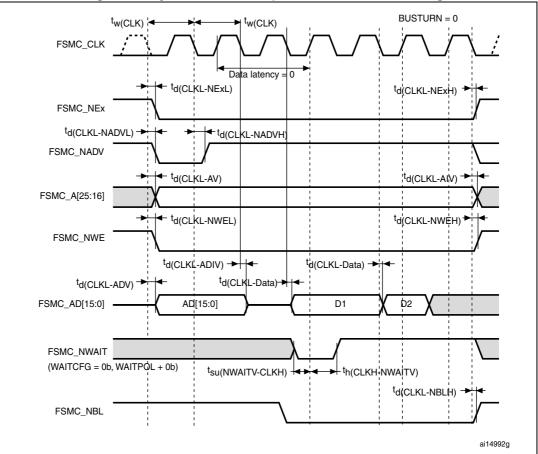

#### Figure 62. Synchronous multiplexed PSRAM write timings

Table 77. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                     | Parameter                                | Min                    | Max | Unit |

|----------------------------|------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                          | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)      | -                      | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)    | 2                      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low            | -                      | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high           | 3                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)   | -                      | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625) | 7                      | _   | ns   |

DocID15818 Rev 13

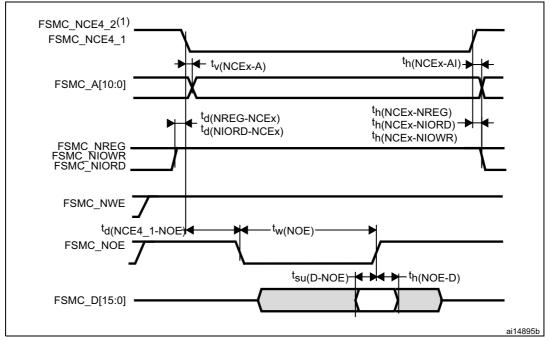

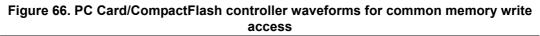

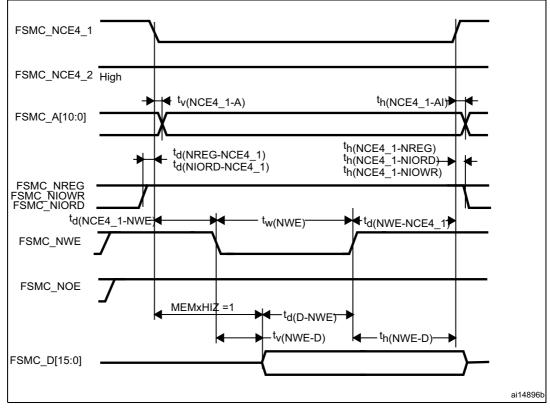

Figure 65. PC Card/CompactFlash controller waveforms for common memory read access

1. FSMC\_NCE4\_2 remains high (inactive during 8-bit access.

## Table 88. WLCSP64+2 - 66-ball, 4.539 x 4.911 mm, 0.4 mm pitch wafer level chip scale package mechanical data (continued)

| Symbol |     | millimeters |       | inches <sup>(1)</sup> |        |        |

|--------|-----|-------------|-------|-----------------------|--------|--------|

| Symbol | Min | Тур         | Max   | Min                   | Тур    | Max    |

| F      | -   | 0.220       | -     | -                     | 0.0087 | -      |

| G      | -   | 0.386       | -     | -                     | 0.0152 | -      |

| ааа    | -   | -           | 0.100 | -                     | -      | 0.0039 |

| bbb    | -   | -           | 0.100 | -                     | -      | 0.0039 |

| CCC    | -   | -           | 0.100 | -                     | -      | 0.0039 |

| ddd    | -   | -           | 0.050 | -                     | -      | 0.0020 |

| eee    | -   | -           | 0.050 | -                     | -      | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

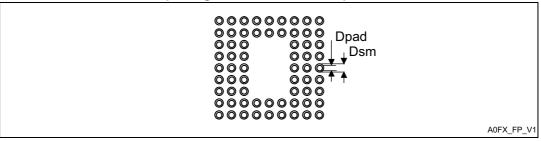

## Figure 80. WLCSP64+2 - 66-ball, 4.539 x 4.911 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

#### Table 89. WLCSP64 recommended PCB design rules (0.4 mm pitch)

| Dimension         | Recommended values                                               |  |

|-------------------|------------------------------------------------------------------|--|

| Pitch             | 0.4                                                              |  |

| Dpad              | 0.225 mm                                                         |  |

| Dsm               | 0.290 mm typ. (depends on the soldermask registration tolerance) |  |

| Stencil opening   | 0.250 mm                                                         |  |

| Stencil thickness | 0.100 mm                                                         |  |

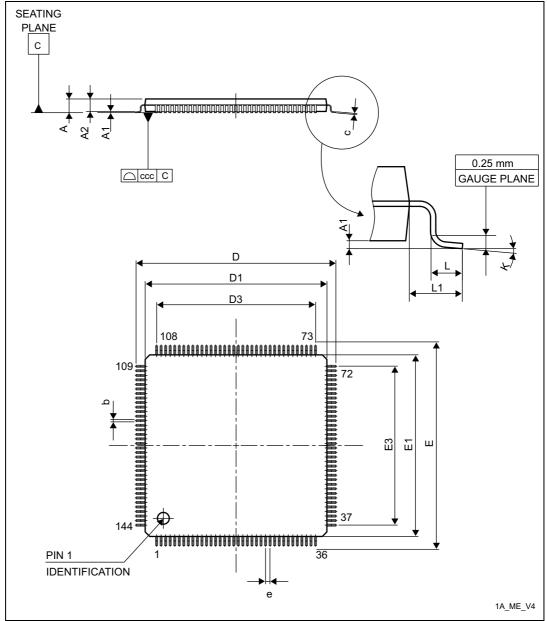

## 7.4 LQFP144 package information

Figure 84. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline

1. Drawing is not to scale.

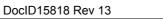

## 7.5 LQFP176 package information

Figure 87. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline

1. Drawing is not to scale.

| Table 92. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

|        |                    |      | Dimer  | isions                |      |        |

|--------|--------------------|------|--------|-----------------------|------|--------|

| Symbol | Symbol millimeters |      |        | inches <sup>(1)</sup> |      |        |

|        | Min.               | Тур. | Max.   | Min.                  | Тур. | Max.   |

| А      | -                  | -    | 1.600  | -                     | -    | 0.0630 |

| A1     | 0.050              | -    | 0.150  | 0.0020                | -    | 0.0059 |

| A2     | 1.350              | -    | 1.450  | 0.0531                | -    | 0.0571 |

| b      | 0.170              | -    | 0.270  | 0.0067                | -    | 0.0106 |

| с      | 0.090              | -    | 0.200  | 0.0035                | -    | 0.0079 |

| D      | 23.900             | -    | 24.100 | 0.9409                | -    | 0.9488 |

DocID15818 Rev 13

|             | Table 97. Document revision history (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date        | Revision                                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 14-Jun-2011 | 7                                               | Added SDIO in <i>Table 2: STM32F205xx features and peripheral counts.</i><br>Updated V <sub>IN</sub> for 5V tolerant pins in <i>Table 11: Voltage characteristics.</i><br>Updated jitter parameters description in <i>Table 34: Main PLL characteristics.</i><br>Remove jitter values for system clock in <i>Table 35: PLLI2S (audio PLL) characteristics.</i><br>Updated <i>Table 42: EMI characteristics.</i><br>Updated <i>Table 42: EMI characteristics.</i><br>Updated <i>Note 2</i> in <i>Table 52: I2C characteristics.</i><br>Updated Avg_Slope typical value and $T_{S\_temp}$ minimum value in <i>Table 69: Temperature sensor characteristics.</i><br>Updated $T_{S\_vbat}$ minimum value in <i>Table 70: VBAT monitoring characteristics.</i><br>Updated $T_{S\_vrefint}$ minimum value in <i>Table 71: Embedded internal reference voltage.</i><br>Added Software option in <i>Section 8: Part numbering.</i><br>In <i>Table 101: Main applications versus package for STM32F2xxx microcontrollers,</i> renamed USB1 and USB2, USB OTG FS and USB OTG HS, respectively; and removed USB OTG HS on 64-pin package; added <i>Note 1</i> and <i>Note 2.</i>                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 20-Dec-2011 | 8                                               | Updated SDIO register addresses in <i>Figure 16: Memory map</i> .<br>Updated <i>Figure 3: Compatible board design between STM32F10xx and</i><br><i>STM32F2xx for LQFP144 package, Figure 2: Compatible board design</i><br><i>between STM32F10xx and STM32F2xx for LQFP100 package,</i><br><i>Figure 1: Compatible board design between STM32F10xx and</i><br><i>STM32F2xx for LQFP64 package,</i> and added <i>Figure 4: Compatible</i><br><i>board design between STM32F10xx and STM32F2xx for LQFP176</i><br><i>package.</i><br>Updated <i>Section 3.3: Memory protection unit.</i><br>Updated <i>Section 3.6: Embedded SRAM.</i><br>Updated <i>Section 3.6: Embedded SRAM.</i><br>Updated <i>Section 3.28: Universal serial bus on-the-go full-speed</i><br>( <i>OTG_FS</i> ) to remove external FS OTG PHY support.<br>In <i>Table 8: STM32F20x pin and ball definitions:</i> changed SPI2_MCK<br>and SPI3_MCK to I2S2_MCK and I2S3_MCK, respectively. Added ETH<br>_RMII_TX_EN attlernate function to PG11. Added EVENTOUT in the<br>list of alternate functions for I/O pin/balls. Removed OTG_FS_SDA,<br>OTG_FS_SCL and OTG_FS_INTN alternate functions.<br>In <i>Table 10: Alternate function mapping:</i> changed I2S3_SCK to<br>I2S3_MCK for PC7/AF6, added FSMC_NCE3 for PG9, FSMC_NE3 for<br>PG10, and FSMC_NCE2 for PD7. Removed OTG_FS_SDA,<br>OTG_FS_SCL and OTG_FS_INTN alternate functions. Changed<br>I2S3_SCK into I2S3_MCK for PC7/AF6. Updated peripherals<br>corresponding to AF12.<br>Removed CEXT and ESR from <i>Table 14: General operating conditions</i> . |  |  |  |

Table 97. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID15818 Rev 13