Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

|                            | Obselvts                                                               |

| Product Status             | Obsolete                                                               |

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 120MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT      |

| Number of I/O              | 82                                                                     |

| Program Memory Size        | 1MB (1M x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 132K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 100-LQFP                                                               |

| Supplier Device Package    | 100-LQFP (14x14)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205vgt6j |

STM32F20xxx Description

## 2.1 Full compatibility throughout the family

The STM32F205xx and STM32F207xx constitute the STM32F20x family whose members are fully pin-to-pin, software and feature compatible, allowing the user to try different memory densities and peripherals for a greater degree of freedom during the development cycle.

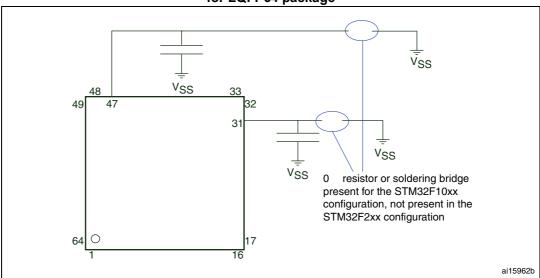

The STM32F205xx and STM32F207xx devices maintain a close compatibility with the whole STM32F10xxx family. All functional pins are pin-to-pin compatible. The STM32F205xx and STM32F207xx, however, are not drop-in replacements for the STM32F10xxx devices: the two families do not have the same power scheme, and so their power pins are different. Nonetheless, transition from the STM32F10xxx to the STM32F20x family remains simple as only a few pins are impacted.

Figure 1, Figure 2 and Figure 3 provide compatible board designs between the STM32F20x and the STM32F10xxx family.

Figure 1. Compatible board design between STM32F10xx and STM32F2xx for LQFP64 package

Functional overview STM32F20xxx

## 3 Functional overview

# 3.1 ARM® Cortex®-M3 core with embedded Flash and SRAM

The ARM® Cortex®-M3 processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM® Cortex®-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

With its embedded ARM<sup>®</sup> core, the STM32F20x family is compatible with all ARM<sup>®</sup> tools and software.

Figure 4 shows the general block diagram of the STM32F20x family.

## 3.2 Adaptive real-time memory accelerator (ART Accelerator™)

The ART Accelerator $^{\rm IM}$  is a memory accelerator which is optimized for STM32 industry-standard ARM $^{\rm I\!R}$  Cortex $^{\rm I\!R}$ -M3 processors. It balances the inherent performance advantage of the ARM $^{\rm I\!R}$  Cortex $^{\rm I\!R}$ -M3 over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher operating frequencies.

To release the processor full 150 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 120 MHz.

## 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

Functional overview STM32F20xxx

## 3.20 Timers and watchdogs

The STM32F20x devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

*Table 5* compares the features of the advanced-control, general-purpose and basic timers.

DMA Max Capture/ Max Complementary Counter Counter **Prescaler** Timer type **Timer** request compare interface timer resolution type factor output generation channels clock clock Up, Any integer Advanced-TIM1, 60 120 between 1 16-bit Down, Yes 4 Yes control TIM8 MHz MHz and 65536 Up/down Up, Any integer 60 TIM2, 30 32-bit Down, between 1 Yes 4 No TIM5 MHz MHz and 65536 Up/down General purpose Any integer Up, TIM3, 30 60 16-bit between 1 Down, Yes 4 Nο TIM4 MHz MHz Up/down and 65536 Any integer TIM6. 30 60 Basic 16-bit between 1 0 Up Yes No TIM7 MHz MHz and 65536 Any integer 60 120 TIM9 16-bit Up between 1 No 2 No MHz MHz and 65536 Any integer TIM10. 60 120 16-bit Up between 1 No 1 No TIM11 MHz MHz and 65536 General purpose Any integer 30 60 TIM12 16-bit Up between 1 No 2 No MHz MHz and 65536 Any integer TIM13, 30 60 16-bit Up between 1 No 1 No TIM14 MHz MHz and 65536

Table 5. Timer feature comparison

### 3.20.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

Functional overview STM32F20xxx

## 3.37 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

### 3.38 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F20x through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

#### Pinouts and pin description 4

PC13-RTC AF1 47 UCAP\_2 46 PA13 45 PA12 PC14-OSC32\_IN 🗖 3 PC15-OSC32\_OUT PH0-OSC\_IN 🗖 5 44 PA11 43 PA10 PH1-OSC\_OUT 42 PA9 NRST PC0 PA8 LQFP64 PC1 🗖 9 40 PC9 PC2 | 10 39 PC8 PC3 🗖 38 PC7 11 VSSA ☐ 12 37 PC6 VDDA 🗖 36 PB15 PA0-WKUP 35 PB14 34 🏻 PB13 PA1 15 PA2 33 PB12 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 ai15969c

Figure 10. STM32F20x LQFP64 pinout

1. The above figure shows the package top view.

8 9 PA14 PA15 PB3 PB5 PB7 PB9 VDD  $V_{BAT}$ PC12 VSS воото PC13 PA13 PB4 PB6 PB8 PC14 В PC10 С PA12 VCAP\_2 PD2 IRROFF PC15 PC11 PA11 D PA10 PA8 PA9 Ε OSC\_IN PH1-OSC\_OUT VSS PC7 VREF+ PC1 PC8 G PB15 PC6 PA3 PC3 PC0 PC5 PB14 PB13 PC4 PA6 PA5 REGOFF PA1 VSS\_5 Н PB10 PB11 VCAP 1 PA2 ai18470c

Figure 11. STM32F20x WLCSP64+2 ballout

1. The above figure shows the package top view.

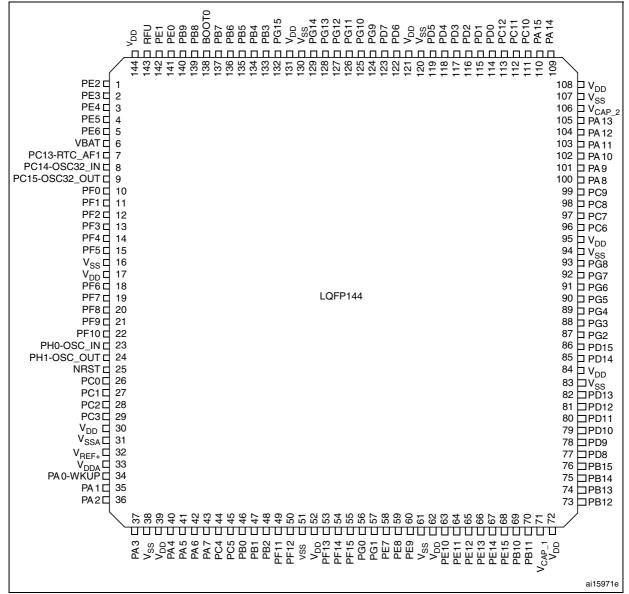

Figure 13. STM32F20x LQFP144 pinout

- 1. RFU means "reserved for future use". This pin can be tied to V<sub>DD</sub>,V<sub>SS</sub> or left unconnected.

- 2. The above figure shows the package top view.

2 9 11 12 13 14 15 PA13 PE3 PE2 PB8 PB5 PG14 PG13 PB4 PB3 PC12 PA15 PE1 PE0 PD7 PA14 PD6 PA12 В PE4 PE5 PE6 PB9 PB7 PB6 PG15 PG12 PG11 PG10 PD0 PC11 PC10 PI6 PI2 С VBAT PI7 PI5 VDD RFU VDD VDD VDD PG9 PD5 PD1 PI3 PA11 PC13-PI4 VSS D PI9 воото VSS VSS VSS PD4 PD2 PH15 PA10 PD3 PI1 TAMP2 PC14-PI10 PI11 PH13 PH14 PA9 Е PI0 PC15-osc32\_out vss VDD PH2 VSS VSS VSS VSS VSS VCAP\_2 PC9 PA8 VSS PH0-PC7 G VSS VDD РН3 VSS VSS VSS VSS VDD PC8 VSS VSS PH1-PF1 PH4 VSS VSS VSS VSS VSS VSS VDD PG8 PC6 OSC\_OUT NRST PF3 PF4 PH5 VSS VSS VDD PG7 PG6 VSS VSS VSS VDD PF7 PF5 VDD VSS VSS VSS VSS VSS PH12 PG5 PG4 PG3 REGOFF PH10 PD15 PF10 PF9 PF8 PG2 PH11 PB2 VSS VSS VCAP\_1 М VSSA PC0 PC1 PC2 PC3 PG1 PH6 PH8 PH9 PD14 PD13 PA0-WKUP PD12 VREF-PC4 PF13 PG0 VDD PE13 PD10 Ν PA1 PA4 VDD VDD PH7 PD11 PA6 VREF+ PA5 PC5 PF12 PF15 PB13 PD8 PA2 PE8 PE9 PE11 PE14 PB12 PD9 VDDA PA3 PA7 PB1 PB0 PF11 PF14 PE7 PE10 PE12 PE15 PB10 PB11 PB14 PB15 ai17293c

Figure 15. STM32F20x UFBGA176 ballout

- 1. RFU means "reserved for future use". This pin can be tied to  $V_{\text{DD}}$ ,  $V_{\text{SS}}$  or left unconnected.

- 2. The above figure shows the package top view.

Table 7. Legend/abbreviations used in the pinout table

| Name                                                                                  | Abbreviation       | Definition                                                                                         |  |  |  |  |

|---------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin name                                                                              |                    | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |

|                                                                                       | S                  | Supply pin                                                                                         |  |  |  |  |

| Pin type                                                                              | I                  | Input only pin                                                                                     |  |  |  |  |

|                                                                                       | I/O                | Input/ output pin                                                                                  |  |  |  |  |

|                                                                                       | FT                 | 5 V tolerant I/O                                                                                   |  |  |  |  |

| I/O structure                                                                         | TTa                | 3.3 V tolerant I/O                                                                                 |  |  |  |  |

| 1/O structure                                                                         | В                  | Dedicated BOOT0 pin                                                                                |  |  |  |  |

|                                                                                       | RST                | Bidirectional reset pin with embedded weak pull-up resistor                                        |  |  |  |  |

| Notes                                                                                 | Unless otherwise   | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |

| Alternate functions                                                                   | Functions selected | d through GPIOx_AFR registers                                                                      |  |  |  |  |

| Additional functions Functions directly selected/enabled through peripheral registers |                    |                                                                                                    |  |  |  |  |

Table 9. FSMC pin definition (continued)

|      |       |                | SMC           | ,           |         |

|------|-------|----------------|---------------|-------------|---------|

| Pins | CF    | NOR/PSRAM/SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100 |

| PE5  | -     | A21            | A21           | -           | Yes     |

| PE6  | -     | A22            | A22           | -           | Yes     |

| PF0  | A0    | A0             | -             | -           | -       |

| PF1  | A1    | A1             | -             | -           | -       |

| PF2  | A2    | A2             | -             | -           | -       |

| PF3  | A3    | A3             | -             | -           | -       |

| PF4  | A4    | A4             | -             | -           | -       |

| PF5  | A5    | A5             | -             | -           | -       |

| PF6  | NIORD | -              | -             | -           | -       |

| PF7  | NREG  | -              | -             | -           | -       |

| PF8  | NIOWR | -              | -             | -           | -       |

| PF9  | CD    | -              | -             | -           | -       |

| PF10 | INTR  | -              | -             | -           | -       |

| PF12 | A6    | A6             | -             | -           | -       |

| PF13 | A7    | A7             | -             | -           | -       |

| PF14 | A8    | A8             | -             | -           | -       |

| PF15 | A9    | A9             | -             | -           | -       |

| PG0  | A10   | A10            | -             | -           | -       |

| PG1  | -     | A11            | -             | -           | -       |

| PE7  | D4    | D4             | DA4           | D4          | Yes     |

| PE8  | D5    | D5             | DA5           | D5          | Yes     |

| PE9  | D6    | D6             | DA6           | D6          | Yes     |

| PE10 | D7    | D7             | DA7           | D7          | Yes     |

| PE11 | D8    | D8             | DA8           | D8          | Yes     |

| PE12 | D9    | D9             | DA9           | D9          | Yes     |

| PE13 | D10   | D10            | DA10          | D10         | Yes     |

| PE14 | D11   | D11            | DA11          | D11         | Yes     |

| PE15 | D12   | D12            | DA12          | D12         | Yes     |

| PD8  | D13   | D13            | DA13          | D13         | Yes     |

| PD9  | D14   | D14            | DA14          | D14         | Yes     |

| PD10 | D15   | D15            | DA15          | D15         | Yes     |

| PD11 | -     | A16            | A16           | CLE         | Yes     |

| PD12 | -     | A17            | A17           | ALE         | Yes     |

Pinouts and pin description

|        |                        | AF0  | AF1    | AF2      | AF3          | AF4            | AF5            | AF6                  | AF7        | AF8                | AF9                       | AF10                | AF11                          | AF12                 | AF13    |       |          |

|--------|------------------------|------|--------|----------|--------------|----------------|----------------|----------------------|------------|--------------------|---------------------------|---------------------|-------------------------------|----------------------|---------|-------|----------|

|        | Port                   | sys  | TIM1/2 | TIM3/4/5 | TIM8/9/10/11 | I2C1/I2C2/I2C3 | SPI1/SPI2/I2S2 | SPI3/I2S3            | USART1/2/3 | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 | OTG_FS/ OTG_HS      | ЕТН                           | FSMC/SDIO/<br>OTG_HS | DCMI    | AF014 | AF15     |

|        | PC0                    | =    | -      | -        | -            | -              | -              | -                    | -          | -                  | -                         | OTG_HS_ULPI_<br>STP | -                             | ÷                    | -       | -     | EVENTOUT |

|        | PC1                    | =    | -      | =        | =            | =              | =              | =                    | -          | =                  | =                         | -                   | ETH_MDC                       | =                    | =       | -     | EVENTOUT |

|        | PC2                    | -    | -      | -        | -            | -              | SPI2_MISO      | -                    | -          | -                  | -                         | OTG_HS_ULPI_<br>DIR | ETH_MII_TXD2                  | -                    | -       | -     | EVENTOUT |

|        | PC3                    | =-   | -      | -        | -            | -              | SPI2_MOSI      | -                    | -          | -                  | -                         | OTG_HS_ULPI_<br>NXT | ETH<br>_MII_TX_CLK            | =                    | -       | -     | EVENTOUT |

|        | PC4                    | =    | -      | =        | =            | -              | -              | -                    | -          | =                  | =                         | -                   | ETH_MII_RXD0<br>ETH_RMII_RXD0 | =                    | -       | -     | EVENTOUT |

|        | PC5                    | =    | -      | =        | -            | =              | -              | =                    | -          | =                  | =                         | -                   | ETH_MII_RXD1<br>ETH_RMII_RXD1 | =                    | =       | -     | EVENTOUT |

|        | PC6                    | -    | -      | TIM3_CH1 | TIM8_CH1     | -              | I2S2_MCK       | -                    | -          | USART6_TX          | -                         | -                   | -                             | SDIO_D6              | DCMI_D0 | -     | EVENTOUT |

|        | PC7                    | -    | -      | TIM3_CH2 | TIM8_CH2     | -              | -              | I2S3_MCK             | -          | USART6_RX          | -                         | -                   | -                             | SDIO_D7              | DCMI_D1 | -     | EVENTOUT |

| Port C | PC8                    | =    | -      | TIM3_CH3 | TIM8_CH3     | =              | =              | =                    | -          | USART6_CK          | =                         | -                   | =                             | SDIO_D0              | DCMI_D2 | -     | EVENTOUT |

|        | PC9                    | MCO2 | -      | TIM3_CH4 | TIM8_CH4     | I2C3_SDA       | I2S2_CKIN      | I2S3_CKIN            | -          | -                  | =                         | -                   | -                             | SDIO_D1              | DCMI_D3 | -     | EVENTOUT |

|        | PC10                   | =    | -      | -        | -            | -              | -              | SPI3_SCK<br>I2S3_SCK | USART3_TX  | UART4_TX           | -                         | -                   | -                             | SDIO_D2              | DCMI_D8 | -     | EVENTOUT |

|        | PC11                   | =    | -      | =        | -            | -              | -              | SPI3_MISO            | USART3_RX  | UART4_RX           | -                         | -                   | -                             | SDIO_D3              | DCMI_D4 | -     | EVENTOUT |

|        | PC12                   |      | -      | -        | -            | -              | -              | SPI3_MOSI<br>I2S3_SD | USART3_CK  | UART5_TX           | -                         | -                   | -                             | SDIO_CK              | DCMI_D9 | -     | EVENTOUT |

|        | PC13                   | -    | -      | -        | -            | -              | -              | -                    | -          | -                  | -                         | -                   | -                             | -                    | -       | -     | EVENTOUT |

|        | PC14-<br>OSC32_IN      | ≘'   | -      | -        | -            | -              | -              | -                    | -          | =                  | =                         | -                   | -                             | =                    | -       | -     | EVENTOUT |

|        | PC15-<br>OSC32_OU<br>T | =    | -      | -        | =            | -              | -              | -                    | -          | -                  | -                         | -                   | -                             | =                    | -       | -     | EVENTOUT |

### 6.1.6 Power supply scheme

$V_{BAT}$ Backup circuitry Power switch (OSC32K,RTC, 1.65-3.6V Wakeup logic Backup registers, backup RĂM) ΟUΤ shifter 10 GP I/Os Logic evel Kernel logic (CPU, digital 2 × 2.2 µF & RAM)  $V_{DD}$ Voltage 1/2/...14/15 regulator 15 × 100 nF  $+ 1 \times 4.7 \mu F$ **REGOFF** Flash memory **IRROFF**  $V_{DDA}$ VREF+ Analog 100 nl 100 nF + 1 μF **ADC** V<sub>REF</sub> RCs, PLI  $V_{SSA}$ ai17527f

Figure 19. Power supply scheme

- Each power supply pair must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be

placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality

of the device.

- 2. To connect REGOFF and IRROFF pins, refer to Section 3.16: Voltage regulator.

- The two 2.2 μF ceramic capacitors should be replaced by two 100 nF decoupling capacitors when the voltage regulator is OFF.

- 4. The 4.7  $\mu$ F ceramic capacitor must be connected to one of the  $V_{DD}$  pin.

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> ...) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB, to ensure good device operation. It is not recommended to remove filtering capacitors to reduce PCB size or cost. This might cause incorrect device operation.

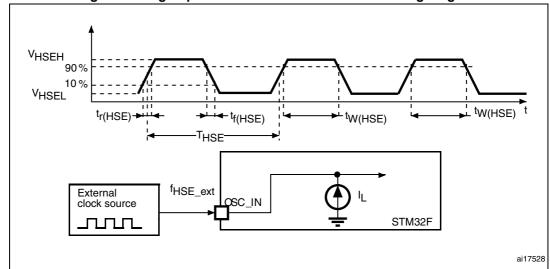

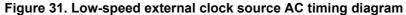

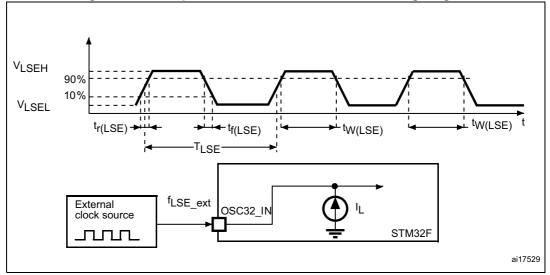

Figure 30. High-speed external clock source AC timing diagram

### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 30*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                   | Conditions                    | Min | Тур  | Max | Unit |

|-------------------------------------|-----------------------------|-------------------------------|-----|------|-----|------|

| R <sub>F</sub>                      | Feedback resistor           | -                             | -   | 18.4 | -   | МΩ   |

| I <sub>DD</sub>                     | LSE current consumption     | -                             | -   | -    | 1   | μΑ   |

| 9 <sub>m</sub>                      | Oscillator Transconductance | -                             | 2.8 | -    | -   | μA/V |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                | V <sub>DD</sub> is stabilized | -   | 2    | -   | S    |

Table 31. LSE oscillator characteristics ( $f_{LSE} = 32.768 \text{ kHz}$ ) (1)

Note: For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

Resonator with integrated capacitors fLSE Bias 32.768 kHz  $R_{\mathsf{F}}$ controlled resonator gain OSC32 OUT STM32F ai17531

Figure 33. Typical application with a 32.768 kHz crystal

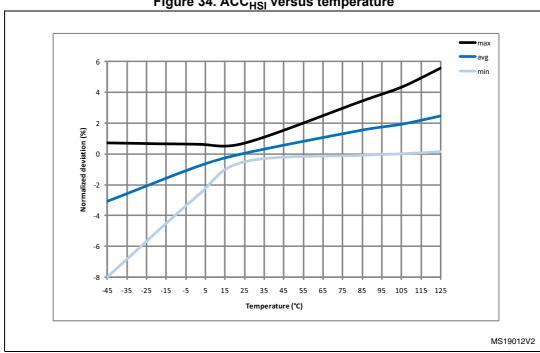

#### 6.3.9 Internal clock source characteristics

The parameters given in Table 32 and Table 33 are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 14*.

### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                             | Conditions                                         | Min        | Тур | Max | Unit |

|-------------------------------------|---------------------------------------|----------------------------------------------------|------------|-----|-----|------|

| f <sub>HSI</sub>                    | Frequency                             | -                                                  | -          | 16  | -   | MHz  |

|                                     | HSI user-trimming step <sup>(2)</sup> | -                                                  | -          | -   | 1   | %    |

| 400                                 | Accuracy of the<br>HSI oscillator     | $T_A = -40 \text{ to } 105 ^{\circ}\text{C}^{(3)}$ | -8         | -   | 4.5 | %    |

| ACC <sub>HSI</sub>                  |                                       | $T_A = -10 \text{ to } 85 ^{\circ}\text{C}^{(3)}$  | - 4        | -   | 4   | %    |

|                                     |                                       | T <sub>A</sub> = 25 °C <sup>(4)</sup>              | <b>–</b> 1 | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                                  | -          | 2.2 | 4.0 | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power consumption      | -                                                  | -          | 60  | 80  | μΑ   |

Table 32. HSI oscillator characteristics (1)

- 1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

- 2. Guaranteed by design, not tested in production.

- 3. Guaranteed by characterization results.

- 4. Factory calibrated, parts not soldered.

<sup>1.</sup> Guaranteed by design, not tested in production.

$t_{SU(LSE)}$  is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

Figure 34. ACC<sub>HSI</sub> versus temperature

## Low-speed internal (LSI) RC oscillator

Table 33. LSI oscillator characteristics (1)

| Symbol                              | Parameter                        | Min | Тур | Max | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> (3)            | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

- 1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

- 2. Guaranteed by characterization results, not tested in production.

- 3. Guaranteed by design, not tested in production.

Table 52. I<sup>2</sup>C characteristics

| 14516 02:1 0 0114140101151105 |                                                                    |                                          |                     |           |                                      |      |  |  |

|-------------------------------|--------------------------------------------------------------------|------------------------------------------|---------------------|-----------|--------------------------------------|------|--|--|

| Symbol                        | Parameter                                                          | Standaı<br>I <sup>2</sup> C <sup>(</sup> | rd mode<br>1)(2)    | Fast mode | e I <sup>2</sup> C <sup>(1)(2)</sup> | Unit |  |  |

| -                             |                                                                    | Min                                      | Max                 | Min       | Max                                  |      |  |  |

| t <sub>w(SCLL)</sub>          | SCL clock low time                                                 | 4.7                                      | -                   | 1.3       | -                                    | ш    |  |  |

| t <sub>w(SCLH)</sub>          | SCL clock high time                                                | 4.0                                      | -                   | 0.6       | -                                    | μs   |  |  |

| t <sub>su(SDA)</sub>          | SDA setup time                                                     | 250                                      | -                   | 100       | -                                    |      |  |  |

| t <sub>h(SDA)</sub>           | SDA data hold time                                                 | -                                        | 3450 <sup>(3)</sup> | -         | 900 <sup>(3)</sup>                   |      |  |  |

| t <sub>r(SDA)</sub>           | SDA and SCL rise time                                              | -                                        | 1000                | -         | 300                                  | ns   |  |  |

| t <sub>f(SDA)</sub>           | SDA and SCL fall time                                              | -                                        | 300                 | -         | 300                                  |      |  |  |

| t <sub>h(STA)</sub>           | Start condition hold time                                          | 4.0                                      | -                   | 0.6       | -                                    |      |  |  |

| t <sub>su(STA)</sub>          | Repeated Start condition setup time                                | 4.7                                      | -                   | 0.6       | -                                    | μs   |  |  |

| t <sub>su(STO)</sub>          | Stop condition setup time                                          | 4.0                                      | -                   | 0.6       | -                                    | μs   |  |  |

| t <sub>w(STO:STA)</sub>       | Stop to Start condition time (bus free)                            | 4.7                                      | -                   | 1.3       | -                                    | μs   |  |  |

| C <sub>b</sub>                | Capacitive load for each bus line                                  | -                                        | 400                 | -         | 400                                  | pF   |  |  |

| t <sub>SP</sub>               | Pulse width of the spikes that are suppressed by the analog filter | 0                                        | 50 <sup>(4)</sup>   | 0         | 50                                   | ns   |  |  |

<sup>1.</sup> Guaranteed by design, not tested in production.

<sup>2.</sup> f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies, and a multiple of 10 MHz to reach the 400 kHz maximum I<sup>2</sup>C fast mode clock

The maximum Data hold time has only to be met if the interface does not stretch the low period of the SCL signal.

<sup>4.</sup> The minimum width of the spikes filtered by the analog filter is above  $t_{SP(max)}$ .

### I<sup>2</sup>S - SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 54* for SPI or in *Table 55* for  $I^2S$  are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

Table 54. SPI characteristics

| Symbol                                           | Parameter                        | Conditions                                                | Min                  | Max                  | Unit    |

|--------------------------------------------------|----------------------------------|-----------------------------------------------------------|----------------------|----------------------|---------|

| f <sub>SCK</sub>                                 | SPI clock frequency              | SPI1 master/slave mode                                    | -                    | 30                   | MHz     |

| 1/t <sub>c(SCK)</sub>                            | SFT Clock frequency              | SPI2/SPI3 master/slave mode                               | -                    | 15                   | IVII IZ |

| t <sub>r(SCL)</sub>                              | SPI clock rise and fall time     | Capacitive load: C = 30 pF,<br>f <sub>PCLK</sub> = 30 MHz | -                    | 8                    | ns      |

| DuCy(SCK)                                        | SPI slave input clock duty cycle | Slave mode                                                | 30                   | 70                   | %       |

| t <sub>su(NSS)</sub> <sup>(1)</sup>              | NSS setup time                   | Slave mode                                                | 4t <sub>PCLK</sub>   | -                    |         |

| t <sub>h(NSS)</sub> <sup>(1)</sup>               | NSS hold time                    | Slave mode                                                | 2t <sub>PCLK</sub>   | -                    |         |

| $t_{w(SCLH)}^{(1)}_{(1)}$                        | SCK high and low time            | Master mode, f <sub>PCLK</sub> = 30 MHz,<br>presc = 2     | t <sub>PCLK</sub> -3 | t <sub>PCLK</sub> +3 |         |

|                                                  | Data input setup time            | Master mode                                               | 5                    | -                    |         |

| $t_{su(MI)}^{(1)}$                               | Data input setup time            | Slave mode                                                | 5                    | -                    |         |

| t <sub>h(MI)</sub> (1)<br>t <sub>h(SI)</sub> (1) | Data input hold time             | Master mode                                               | 5                    | -                    |         |

| t <sub>h(SI)</sub> (1)                           | Data input noid time             | Slave mode                                                | 4                    | -                    | ns      |

| t <sub>a(SO)</sub> (1)(2)                        | Data output access time          | Slave mode, f <sub>PCLK</sub> = 30 MHz                    | 0                    | 3t <sub>PCLK</sub>   |         |

| t <sub>dis(SO)</sub> (1)(3)                      | Data output disable time         | Slave mode                                                | 2                    | 10                   |         |

| t <sub>v(SO)</sub> (1)                           | Data output valid time           | Slave mode (after enable edge)                            | -                    | 25                   |         |

| t <sub>v(MO)</sub> <sup>(1)</sup>                | Data output valid time           | Master mode (after enable edge)                           | -                    | 5                    |         |

| t <sub>h(SO)</sub> <sup>(1)</sup>                | Data output hold time            | Slave mode (after enable edge)                            | 15                   | -                    |         |

| t <sub>h(MO)</sub> <sup>(1)</sup>                | Data output noid time            | Master mode (after enable edge)                           | 2                    | -                    |         |

<sup>1.</sup> Guaranteed by characterization results, not tested in production.

<sup>2.</sup> Min time is for the minimum time to drive the output and the max time is for the maximum time to validate the data.

<sup>3.</sup> Min time is for the minimum time to invalidate the output and the max time is for the maximum time to put the data in Hi-Z

#### **USB OTG FS characteristics**

The USB OTG interface is USB-IF certified (Full-Speed). This interface is present in both the USB OTG HS and USB OTG FS controllers.

Table 56. USB OTG FS startup time

| Symbol                              | Parameter                           | Max | Unit |

|-------------------------------------|-------------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |

<sup>1.</sup> Guaranteed by design, not tested in production.

Table 57. USB OTG FS DC electrical characteristics

| Sym            | bol                               | Parameter                                                 | Conditions                               | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup>            | Unit |

|----------------|-----------------------------------|-----------------------------------------------------------|------------------------------------------|---------------------|------|--------------------------------|------|

|                | $V_{DD}$                          | USB OTG FS operating voltage                              |                                          | 3.0 <sup>(2)</sup>  | -    | 3.6                            | ٧    |

| Input          | V <sub>DI</sub> <sup>(3)</sup>    | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)         | 0.2                 | -    | -                              |      |

| levels         | V <sub>CM</sub> <sup>(3)</sup>    | Differential common mode range                            | Includes V <sub>DI</sub> range           | 0.8                 | -    | 2.5                            | V    |

|                | V <sub>SE</sub> <sup>(3)</sup>    | Single ended receiver threshold                           |                                          | 1.3                 | -    | 2.0                            |      |

| Output         | V <sub>OL</sub>                   | Static output level low                                   | $R_L$ of 1.5 k $\Omega$ to 3.6 $V^{(4)}$ | -                   | -    | 0.3                            | V    |

| levels         | V <sub>OH</sub>                   | Static output level high                                  | $R_L$ of 15 k $\Omega$ to $V_{SS}^{(4)}$ | 2.8                 | -    | 3.6                            | V    |

| R <sub>F</sub> |                                   | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V <sub>IN</sub> = V <sub>DD</sub>        | 17                  | 21   | 24                             |      |

| 175            | PD                                | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | VIN - VDD                                | 0.65                | 1.1  | 2.5<br>2.0<br>0.3<br>3.6<br>24 | kΩ   |

|                | PA12, PB15 (USB_FS_DP, USB_HS_DP) |                                                           | V <sub>IN</sub> = V <sub>SS</sub>        | 1.5                 | 1.8  | 2.1                            |      |

| R <sub>F</sub> | PU                                | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>        | 0.25                | 0.37 | 0.55                           |      |

<sup>1.</sup> All the voltages are measured from the local ground potential.

<sup>2.</sup> The STM32F205xx and STM32F207xx USB OTG FS functionality is ensured down to 2.7 V but not the full USB OTG FS electrical characteristics which are degraded in the 2.7-to-3.0 V  $\rm V_{DD}$  voltage range.

<sup>3.</sup> Guaranteed by design, not tested in production.

<sup>4.</sup> R<sub>L</sub> is the load connected on the USB OTG FS drivers

Table 76. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

| Symbol                    | Parameter                                      | Min | Max | Unit |

|---------------------------|------------------------------------------------|-----|-----|------|

| t <sub>su(ADV-CLKH)</sub> | FSMC_A/D[15:0] valid data before FSMC_CLK high | 5   | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>  | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0   | -   | ns   |

<sup>1.</sup>  $C_L = 30 pF$ .

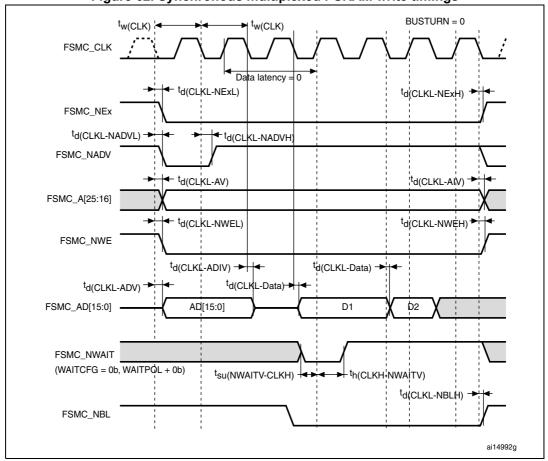

Figure 62. Synchronous multiplexed PSRAM write timings

Table 77. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                     | Parameter                                | Min                    | Max | Unit |

|----------------------------|------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                          | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)      | -                      | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)    | 2                      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low            | -                      | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high           | 3                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)   | -                      | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625) | 7                      | -   | ns   |

<sup>2.</sup> Guaranteed by characterization results, not tested in production.

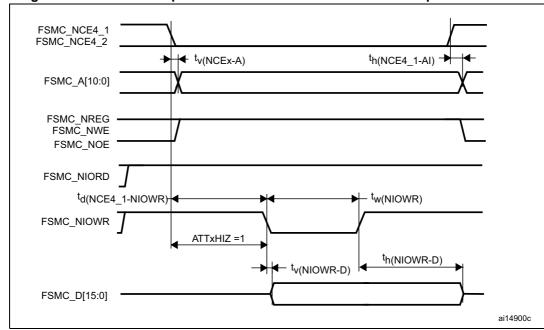

Figure 70. PC Card/CompactFlash controller waveforms for I/O space write access

Table 80. Switching characteristics for PC Card/CF read and write cycles in attribute/common space  $^{(1)(2)}$

| Symbol                    | Parameter                                    | Min                         | Max                    | Unit |

|---------------------------|----------------------------------------------|-----------------------------|------------------------|------|

| t <sub>v(NCEx-A)</sub>    | FSMC_Ncex low to FSMC_Ay valid               | -                           | 0                      | ns   |

| t <sub>h(NCEx_AI)</sub>   | FSMC_NCEx high to FSMC_Ax invalid            | 4                           | -                      | ns   |

| t <sub>d(NREG-NCEx)</sub> | FSMC_NCEx low to FSMC_NREG valid             | -                           | 3.5                    | ns   |

| t <sub>h(NCEx-NREG)</sub> | FSMC_NCEx high to FSMC_NREG invalid          | T <sub>HCLK</sub> + 4       | -                      | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | _NCEx low to FSMC_NWE low - |                        |      |

| t <sub>d(NCEx-NOE)</sub>  | FSMC_NCEx low to FSMC_NOE low                | -                           | 5T <sub>HCLK</sub>     | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low width                           | 8T <sub>HCLK</sub> - 0.5    | 8T <sub>HCLK</sub> + 1 | ns   |

| t <sub>d(NOE_NCEx)</sub>  | FSMC_NOE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> + 2.5    | -                      | ns   |

| t <sub>su (D-NOE)</sub>   | FSMC_D[15:0] valid data before FSMC_NOE high | 4                           | -                      | ns   |

| t <sub>h (N0E-D)</sub>    | FSMC_N0E high to FSMC_D[15:0] invalid        | 2                           | -                      | ns   |

| t <sub>w(NWE)</sub>       | FSMC_NWE low width                           | 8T <sub>HCLK</sub> - 1      | 8T <sub>HCLK</sub> + 4 | ns   |

| t <sub>d(NWE_NCEx</sub> ) | FSMC_NWE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> + 1.5    | -                      | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                           | 5HCLK+ 1               | ns   |

| t <sub>v (NWE-D)</sub>    | FSMC_NWE low to FSMC_D[15:0] valid           | -                           | 0                      | ns   |

| t <sub>h (NWE-D)</sub>    | FSMC_NWE high to FSMC_D[15:0] invalid        | 8T <sub>HCLK</sub> -        |                        | ns   |

| t <sub>d (D-NWE)</sub>    | FSMC_D[15:0] valid before FSMC_NWE high      | 13T <sub>HCLK</sub> -       |                        | ns   |

<sup>1.</sup>  $C_1 = 30 pF$ .

<sup>2.</sup> Guaranteed by characterization results, not tested in production.

#### 7.3 LQFP100 package information

SEATING PLANE С 0.25 mm GAUGE PLANE □ ccc C D D1 D3 의 교 PIN 1 **IDENTIFICATION** 1L\_ME\_V5

Figure 81. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

Table 90. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Max    | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600  | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150  | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С      | 0.090       | -      | 0.200  | 0.0035                | -      | 0.0079 |

| D      | 15.800      | 16.000 | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| D1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

STM32F20xxx Revision history

Table 97. Document revision history (continued)

| Date        | Revision         | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date        | Revision         | Changes  Removed support of I2C for OTG PHY in Section 3.29: Universal serial bus on-the-go high-speed (OTG_HS).  Removed OTG_HS_SCL, OTG_HS_SDA, OTG_FS_INTN in Table 8: STM32F20x pin and ball definitions and Table 10: Alternate function mapping.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 24-Apr-2012 | 9<br>(continued) | Renamed PH10 alternate function into TIM5_CH1 in Table 10: Alternate function mapping.  Added Table 9: FSMC pin definition.  Updated Note 1 in Table 14: General operating conditions, Note 2 in Table 15: Limitations depending on the operating power supply range, and Note 1 below Figure 21: Number of wait states versus fCPU and VDD range.  Updated VPOR/PDR in Table 19: Embedded reset and power control block characteristics.  Updated typical values in Table 24: Typical and maximum current consumptions in Standby mode and Table 25: Typical and maximum current consumptions in Nandby mode and Table 25: Typical and maximum current consumptions in VBAT mode.  Updated Table 30: HSE 4-26 MHz oscillator characteristics and Table 31: LSE oscillator characteristics (fLSE = 32.768 kHz).  Updated Table 37: Flash memory characteristics, Table 38: Flash memory programming, and Table 39: Flash memory programming with VPP.  Updated Section: Output driving current.  Updated Note 3 and removed note related to minimum hold time value in Table 52: I2C characteristics.  Updated Table 64: Dynamics characteristics: Ethernet MAC signals for RMII.  Updated Note 1, CADC, I <sub>VREF++</sub> , and I <sub>VDDA</sub> in Table 66: ADC characteristics.  Updated Note 3 and note concerning ADC accuracy vs. negative injection current in Table 67: ADC accuracy.  Updated Note 1 in Table 68: DAC characteristics.  Updated Section Figure 88: UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm, package outline.  Appendix A.1: Main applications versus package: removed number of address lines for FSMC/NAND in Table 101: Main applications versus package for STM32F2xxx microcontrollers.  Appendix A.4: Ethernet interface solutions: updated Figure 92: Complete audio player solution 1 and Figure 93: Complete audio player solution 2. |  |  |