### STMicroelectronics - STM32F205VGT7TR Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details |

|---------|

| Details |

E·XF

| 2012                       |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT       |

| Number of I/O              | 82                                                                      |

| Program Memory Size        | 1MB (1M x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 132K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205vgt7tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

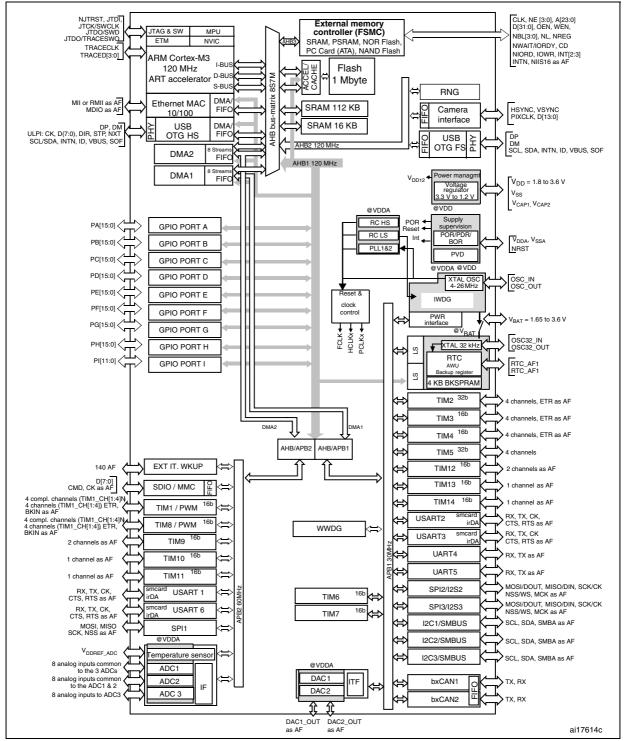

Figure 4. STM32F20x block diagram

1. The timers connected to APB2 are clocked from TIMxCLK up to 120 MHz, while the timers connected to APB1 are clocked from TIMxCLK up to 60 MHz.

2. The camera interface and Ethernet are available only in STM32F207xx devices.

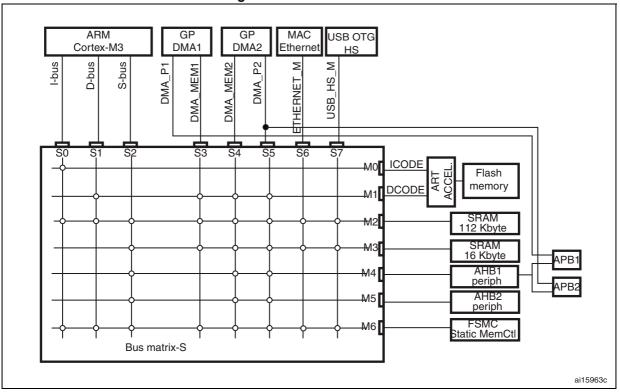

Figure 5. Multi-AHB matrix

# 3.8 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They share some centralized FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

# 3.11 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 23 edge-detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 140 GPIOs can be connected to the 16 external interrupt lines.

# 3.12 Clocks and startup

On reset the 16 MHz internal RC oscillator is selected as the default CPU clock. The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

The advanced clock controller clocks the core and all peripherals using a single crystal or oscillator. In particular, the ethernet and USB OTG FS peripherals can be clocked by the system clock.

Several prescalers and PLLs allow the configuration of the three AHB buses, the highspeed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the three AHB buses is 120 MHz and the maximum frequency the high-speed APB domains is 60 MHz. The maximum allowed frequency of the low-speed APB domain is 30 MHz.

The devices embed a dedicate PLL (PLLI2S) which allow to achieve audio class performance. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

# 3.13 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1 (PA9/PA10), USART3 (PC10/PC11 or PB10/PB11), CAN2 (PB5/PB13), USB OTG FS in Device mode (PA11/PA12) through DFU (device firmware upgrade).

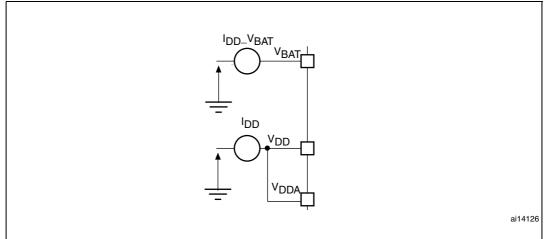

# 3.14 Power supply schemes

V<sub>DD</sub> = 1.8 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins. On devices in WLCSP64+2 package, if IRROFF is set to V<sub>DD</sub>, the supply voltage can drop to 1.7 V when the device operates

| FSMC FSMC pin definition (continued) |        |                |               |             |         |

|--------------------------------------|--------|----------------|---------------|-------------|---------|

| Pins                                 | CF     | NOR/PSRAM/SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100 |

| PD13                                 | -      | A18            | A18           | -           | Yes     |

| PD14                                 | D0     | D0             | DA0           | D0          | Yes     |

| PD15                                 | D1     | D1             | DA1           | D1          | Yes     |

| PG2                                  | -      | A12            | -             | -           | -       |

| PG3                                  | -      | A13            | -             | -           | -       |

| PG4                                  | -      | A14            | -             | -           | -       |

| PG5                                  | -      | A15            | -             | -           | -       |

| PG6                                  | -      | -              | -             | INT2        | -       |

| PG7                                  | -      | -              | -             | INT3        | -       |

| PD0                                  | D2     | D2             | DA2           | D2          | Yes     |

| PD1                                  | D3     | D3             | DA3           | D3          | Yes     |

| PD3                                  | -      | CLK            | CLK           | -           | Yes     |

| PD4                                  | NOE    | NOE            | NOE           | NOE         | Yes     |

| PD5                                  | NWE    | NWE            | NWE           | NWE         | Yes     |

| PD6                                  | NWAIT  | NWAIT          | NWAIT         | NWAIT       | Yes     |

| PD7                                  | -      | NE1            | NE1           | NCE2        | Yes     |

| PG9                                  | -      | NE2            | NE2           | NCE3        | -       |

| PG10                                 | NCE4_1 | NE3            | NE3           | -           | -       |

| PG11                                 | NCE4_2 | -              | -             | -           | -       |

| PG12                                 | -      | NE4            | NE4           | -           | -       |

| PG13                                 | -      | A24            | A24           | -           | -       |

| PG14                                 | -      | A25            | A25           | -           | -       |

| PB7                                  | -      | NADV           | NADV          | -           | Yes     |

| PE0                                  | -      | NBL0           | NBL0          | -           | Yes     |

| PE1                                  | -      | NBL1           | NBL1          | -           | Yes     |

Table 9. FSMC pin definition (continued)

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

# 6.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3 V (for the 1.8 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

# 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

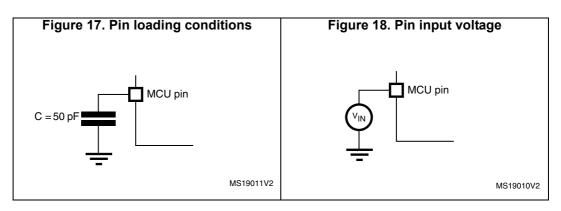

# 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 17*.

### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 18*.

# 6.1.7 Current consumption measurement

### Figure 20. Current consumption measurement scheme

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                       | Min                                                      | Max                 | Unit |

|-----------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------|---------------------|------|

| $V_{DD} - V_{SS}$                 | External main supply voltage (including $V_{DDA}$ , $V_{DD}$ ) <sup>(1)</sup> | -0.3                                                     | 4.0                 |      |

| V                                 | Input voltage on five-volt tolerant pin <sup>(2)</sup>                        | V <sub>SS</sub> -0.3                                     | V <sub>DD</sub> +4  | V    |

| V <sub>IN</sub>                   | Input voltage on any other pin                                                | V <sub>SS</sub> -0.3                                     | 4.0                 |      |

| $ \Delta V_{DDx} $                | Variations between different $V_{DD}$ power pins                              | -                                                        | 50                  | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins                              | -                                                        | 50                  | 1110 |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                            | see Sectio<br>Absolute n<br>ratings (ele<br>sensitivity) | naximum<br>ectrical | -    |

### Table 11. Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

V<sub>IN</sub> maximum value must always be respected. Refer to *Table 12* for the values of the maximum allowed injected current.

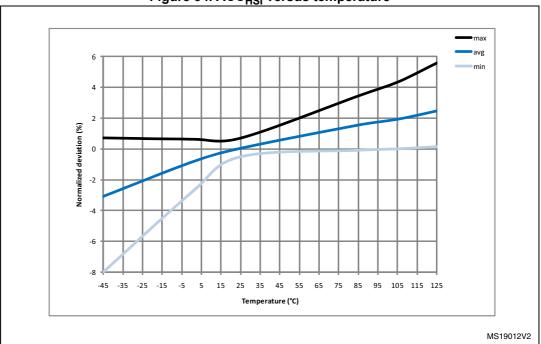

Figure 34. ACC<sub>HSI</sub> versus temperature

### Low-speed internal (LSI) RC oscillator

| Table 33. LS | l oscillator | characteristics <sup>(1)</sup> |

|--------------|--------------|--------------------------------|

|--------------|--------------|--------------------------------|

| Symbol                              | Parameter                        | Min | Тур | Мах | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by characterization results, not tested in production.

3. Guaranteed by design, not tested in production.

| Symbol                                  | Parameter                                    | Conditions                                                          |                    | Min          | Тур  | Мах          | Unit |

|-----------------------------------------|----------------------------------------------|---------------------------------------------------------------------|--------------------|--------------|------|--------------|------|

|                                         |                                              | Cycle to cycle at                                                   | RMS                | -            | 90   | -            |      |

|                                         | Master I2S clock jitter                      | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                        | peak<br>to<br>peak | -            | ±280 | -            | ps   |

| Jitter <sup>(3)</sup>                   |                                              | Average frequency of<br>12.288 MHz<br>N=432, R=5<br>on 1000 samples |                    | -            | 90   | -            | ps   |

|                                         | WS I2S clock jitter                          | Cycle to cycle at 48 I<br>on 1000 samples                           | КНz                | -            | 400  | -            | ps   |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$         | VCO freq = 192 MHz<br>VCO freq = 432 MHz                            |                    | 0.15<br>0.45 | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{\text{DDA}}$ | VCO freq = 192 MHz<br>VCO freq = 432 MHz                            |                    | 0.30<br>0.55 | _    | 0.40<br>0.85 | mA   |

| Table 35. | PLLI2S (audio | PLL) characterist | ics (continued) |

|-----------|---------------|-------------------|-----------------|

| 14810 001 |               |                   |                 |

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design, not tested in production.

3. Value given with main PLL running.

4. Guaranteed by characterization results, not tested in production.

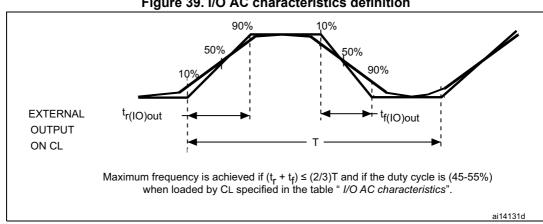

# 6.3.16 I/O port characteristics

### General input/output characteristics

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the conditions summarized in *Table 14: General operating conditions*.

All I/Os are CMOS and TTL compliant.

| Symbol           | Parameter                                   | Conditions                                                      | Min                                     | Тур | Мах                                      | Unit |  |

|------------------|---------------------------------------------|-----------------------------------------------------------------|-----------------------------------------|-----|------------------------------------------|------|--|

|                  | FT, TTa and NRST I/O                        | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                    | -                                       |     | 0.35V <sub>DD</sub> -0.04 <sup>(1)</sup> | -    |  |

| M                | input low level voltage                     | 1.75 V≤V <sub>DD</sub> ≤3.6 V,                                  |                                         |     | 0.3V <sub>DD</sub> <sup>(2)</sup>        |      |  |

| V <sub>IL</sub>  | BOOT0 I/O                                   | –40 °C≤T <sub>A</sub> ≤105 °C                                   | -                                       | -   | 0.1V <sub>DD</sub> +0.1 <sup>(1)</sup>   | V    |  |

|                  | input low level voltage                     | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C    | -                                       | -   |                                          |      |  |

|                  | FT, TTa and NRST I/O                        |                                                                 |                                         | _   | _                                        |      |  |

|                  | input high level voltage <sup>(5)</sup>     | 1.7 VSVDD <u>S</u> 0.0 V                                        | 0.7V <sub>DD</sub> <sup>(2)</sup>       | _   | _                                        | V    |  |

| $V_{\text{IH}}$  |                                             | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>–40 °C≤T <sub>A</sub> ≤105 °C | 0.17V <sub>DD</sub> +0.7 <sup>(1)</sup> |     | _                                        |      |  |

|                  | input high level voltage                    | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C    | 0.17 00010.7                            |     |                                          |      |  |

|                  | FT, TTa and NRST I/O<br>input hysteresis    | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                    | 0.45V <sub>DD</sub> +0.3 <sup>(1)</sup> | -   | -                                        | -    |  |

| $V_{\rm HYS}$    | BOOT0 I/O                                   | 1.75 V≤V <sub>DD</sub> ≤3.6 V,<br>–40 °C≤T <sub>A</sub> ≤105 °C | 10%V <sub>DDIO</sub> <sup>(1)(3)</sup>  | -   | -                                        | V    |  |

|                  | input hysteresis                            | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C    | 100 <sup>(1)</sup>                      | -   | -                                        |      |  |

| L.               | I/O input leakage current <sup>(4)</sup>    | $V_{SS} \leq V_{IN} \leq V_{DD}$                                | -                                       | -   | ±1                                       | μA   |  |

| I <sub>lkg</sub> | I/O FT input leakage current <sup>(5)</sup> | $V_{IN} = 5 V$                                                  | -                                       | -   | 3                                        | μΑ   |  |

| Table 46. I/O | static | characteristics |

|---------------|--------|-----------------|

|---------------|--------|-----------------|

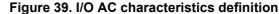

#### 6.3.17 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see Table 49).

Unless otherwise specified, the parameters given in Table 49 are derived from tests performed under the ambient temperature and  $V_{\text{DD}}$  supply voltage conditions summarized in Table 14.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       | -                       | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

#### Table 49. NRST pin characteristics

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series 1. resistance must be minimum (~10% order).

2. Guaranteed by design, not tested in production.

### Figure 40. Recommended NRST pin protection

- The reset network protects the device against parasitic resets. 1.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in 2. Table 49. Otherwise the reset is not taken into account by the device.

# 6.3.18 TIM timer characteristics

The parameters given in *Table 50* and *Table 51* are guaranteed by design.

Refer to Section 6.3.16: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                       | Conditions                                                     | Min    | Мах                     | Unit                 |

|------------------------|---------------------------------|----------------------------------------------------------------|--------|-------------------------|----------------------|

|                        |                                 | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time           | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>60 MHz | 16.7   | -                       | ns                   |

|                        |                                 | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                 | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 30 MHz                | 33.3   | 33.3 -                  |                      |

| f <sub>EXT</sub>       | Timer external clock            |                                                                | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| 'EXT                   | frequency on CH1 to CH4         |                                                                | 0      | 30                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                |                                                                | -      | 16/32                   | bit                  |

|                        | 16-bit counter clock period     |                                                                | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t                      | when internal clock is selected | f <sub>TIMxCLK</sub> = 60 MHz<br>APB1= 30 MHz                  | 0.0167 | 1092                    | μs                   |

| <sup>t</sup> COUNTER   | 32-bit counter clock period     |                                                                | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        | when internal clock is selected |                                                                | 0.0167 | 71582788                | μs                   |

| tury count             | Maximum possible count          |                                                                | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| t <sub>MAX_COUNT</sub> |                                 |                                                                | -      | 71.6                    | s                    |

| Table 50. Characteristics of TIMx connected to the APE | 31 domain <sup>(1)</sup> |

|--------------------------------------------------------|--------------------------|

|--------------------------------------------------------|--------------------------|

1. TIMx is used as a general term to refer to the TIM2, TIM3, TIM4, TIM5, TIM6, TIM7, and TIM12 timers.

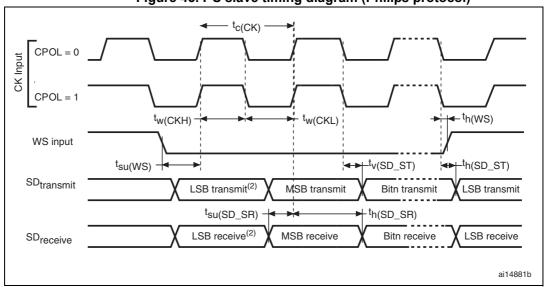

Figure 45. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

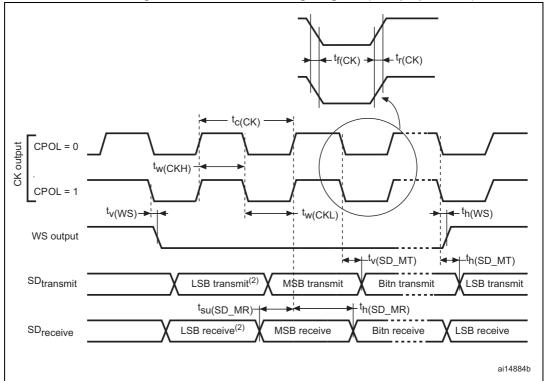

Figure 46. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. Guaranteed by characterization results, not tested in production.

2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

# 6.3.20 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 66* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 14*.

| Symbol                             | Parameter                                       | Conditions                                          | Min                                                         | Тур      | Мах               | Unit               |

|------------------------------------|-------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|----------|-------------------|--------------------|

| V <sub>DDA</sub>                   | Power supply                                    | -                                                   | 1.8 <sup>(1)</sup>                                          | -        | 3.6               | V                  |

| V <sub>REF+</sub>                  | Positive reference voltage                      | -                                                   | 1.8 <sup>(1)(2)</sup>                                       | -        | V <sub>DDA</sub>  | V                  |

| £                                  | ADC clock frequency                             | $V_{DDA}$ = 1.8 <sup>(1)</sup> to 2.4 V             | 0.6                                                         | -        | 15                | MHz                |

| f <sub>ADC</sub>                   | ADC Clock frequency                             | V <sub>DDA</sub> = 2.4 to 3.6 V                     | 0.6                                                         | -        | 30                | MHz                |

| f <sub>TRIG</sub> <sup>(3)</sup>   | External trigger frequency                      | f <sub>ADC</sub> = 30 MHz with<br>12-bit resolution | -                                                           | -        | 1764              | kHz                |

|                                    |                                                 | -                                                   | -                                                           | -        | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range <sup>(4)</sup>         | -                                                   | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -        | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(3)</sup>    | External input impedance                        | See <i>Equation 1</i> for details                   | -                                                           | -        | 50                | kΩ                 |

| R <sub>ADC</sub> <sup>(3)(5)</sup> | Sampling switch resistance                      | -                                                   | 1.5                                                         | -        | 6                 | kΩ                 |

| C <sub>ADC</sub> <sup>(3)</sup>    | Internal sample and hold capacitor              | -                                                   | -                                                           | 4        | -                 | pF                 |

| t <sub>lat</sub> (3)               | Injection trigger conversion<br>latency         | f <sub>ADC</sub> = 30 MHz                           | -                                                           | -        | 0.100             | μs                 |

| 'lat` ´                            |                                                 | -                                                   | -                                                           | -        | 3 <sup>(6)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (3)              | Regular trigger conversion latency              | f <sub>ADC</sub> = 30 MHz                           | -                                                           | -        | 0.067             | μs                 |

| 4atr` ´                            | Regular ingger conversion latency               | -                                                   | -                                                           | -        | 2 <sup>(6)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(3)</sup>      | Sampling time                                   | f <sub>ADC</sub> = 30 MHz                           | 0.100                                                       | -        | 16                | μs                 |

| LS(*)                              |                                                 | -                                                   | 3                                                           | -        | 480               | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(3)</sup>   | Power-up time                                   | -                                                   | -                                                           | 2        | 3                 | μs                 |

|                                    | Total conversion time (including sampling time) | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution      | 0.5                                                         | -        | 16.40             | μs                 |

|                                    |                                                 | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution      | 0.43                                                        | -        | 16.34             | μs                 |

|                                    |                                                 | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution       | 0.37                                                        | -        | 16.27             | μs                 |

|                                    |                                                 | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution       | 0.3                                                         | -        | 16.20             | μs                 |

|                                    |                                                 | 9 to 492 (t <sub>S</sub> for samplir approximation) | ng +n-bit resolutior                                        | for succ | cessive           | 1/f <sub>ADC</sub> |

| Table | 66. / | ADC | characteristics |

|-------|-------|-----|-----------------|

| Table |       |     | characteristics |

being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.16 does not affect the ADC accuracy.

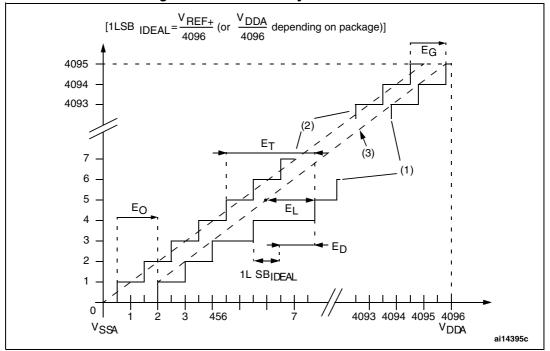

- Example of an actual transfer curve 1.

- 2. Ideal transfer curve

- End point correlation line. 3.

- $E_T$  = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. 4. EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one.

EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

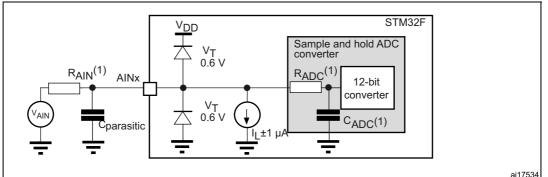

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2.

Refer to Table 66 for the values of  $\mathsf{R}_{AIN},\,\mathsf{R}_{ADC}$  and  $\mathsf{C}_{ADC}$ 1.

### General PCB design guidelines

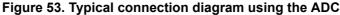

Power supply decoupling should be performed as shown in *Figure 54* or *Figure 55*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

V<sub>REF+</sub> and V<sub>REF</sub> inputs are both available on UFBGA176 package. V<sub>REF+</sub> is also available on all packages except for LQFP64. When V<sub>REF+</sub> and V<sub>REF</sub> are not available, they are internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

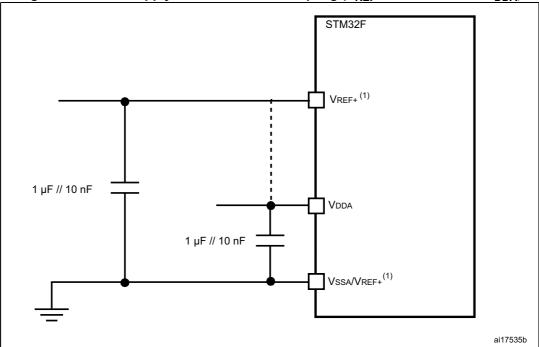

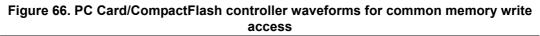

Figure 65. PC Card/CompactFlash controller waveforms for common memory read access

1. FSMC\_NCE4\_2 remains high (inactive during 8-bit access.

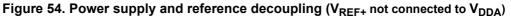

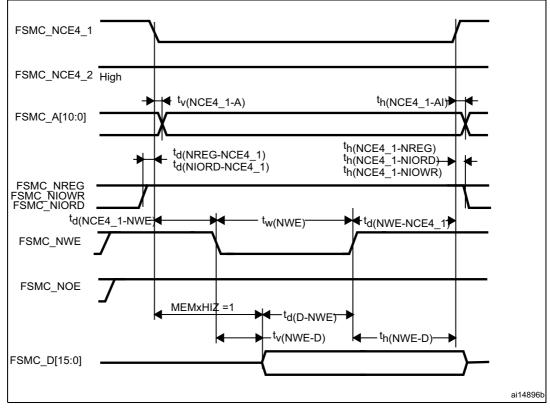

Figure 73. NAND controller waveforms for common memory read access

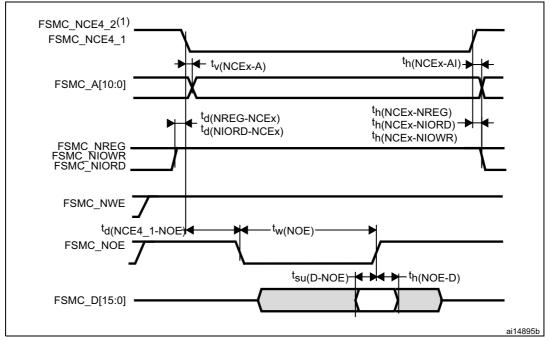

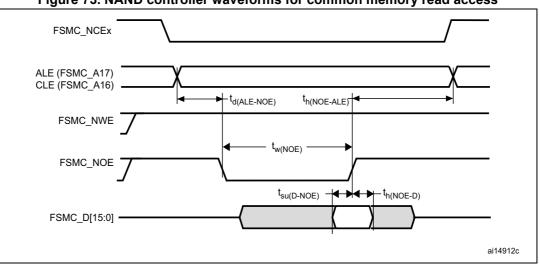

Figure 74. NAND controller waveforms for common memory write access

Table 82. Switching characteristics for NAND Flash read cycles<sup>(1)(2)</sup>

| Symbol                  | Parameter                                    | Min                    | Мах                    | Unit |

|-------------------------|----------------------------------------------|------------------------|------------------------|------|

| t <sub>w(N0E)</sub>     | FSMC_NOE low width                           | 4T <sub>HCLK</sub> - 1 | 4T <sub>HCLK</sub> + 2 | ns   |

| t <sub>su(D-NOE)</sub>  | FSMC_D[15-0] valid data before FSMC_NOE high | 9                      | -                      | ns   |

| t <sub>h(NOE-D</sub> )  | FSMC_D[15-0] valid data after FSMC_NOE high  | 3                      | -                      | ns   |

| t <sub>d(ALE-NOE)</sub> | FSMC_ALE valid before FSMC_NOE low           | -                      | 3T <sub>HCLK</sub>     | ns   |

| t <sub>h(NOE-ALE)</sub> | FSMC_NWE high to FSMC_ALE invalid            | 3T <sub>HCLK</sub> + 2 | -                      | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

| Symbol                  | Parameter                               | Min Max                |                        | Unit |

|-------------------------|-----------------------------------------|------------------------|------------------------|------|

| t <sub>w(NWE)</sub>     | FSMC_NWE low width                      | 4T <sub>HCLK</sub> - 1 | 4T <sub>HCLK</sub> + 3 | ns   |

| t <sub>v(NWE-D)</sub>   | FSMC_NWE low to FSMC_D[15-0] valid      | -                      | 0                      | ns   |

| t <sub>h(NWE-D)</sub>   | FSMC_NWE high to FSMC_D[15-0] invalid   | 3T <sub>HCLK</sub>     | -                      | ns   |

| t <sub>d(D-NWE)</sub>   | FSMC_D[15-0] valid before FSMC_NWE high | 5T <sub>HCLK</sub>     | -                      | ns   |

| t <sub>d(ALE-NWE)</sub> | FSMC_ALE valid before FSMC_NWE low      | -                      | 3T <sub>HCLK</sub> + 2 | ns   |

| t <sub>h(NWE-ALE)</sub> | FSMC_NWE high to FSMC_ALE invalid       | 3T <sub>HCLK</sub> - 2 | -                      | ns   |

Table 83. Switching characteristics for NAND Flash write cycles<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

# 6.3.26 Camera interface (DCMI) timing specifications

| Symbol | Parameter                                     | Conditions          | Min | Мах |

|--------|-----------------------------------------------|---------------------|-----|-----|

| -      | Frequency ratio DCMI_PIXCLK/f <sub>HCLK</sub> | DCMI_PIXCLK= 48 MHz | -   | 0.4 |

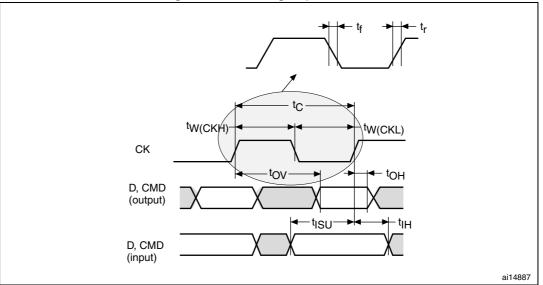

# 6.3.27 SD/SDIO MMC card host interface (SDIO) characteristics

Unless otherwise specified, the parameters given in *Table 85* are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (D[7:0], CMD, CK).

Figure 75. SDIO high-speed mode

| Table 97. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                            | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Date                                            |          | Changes           Changed minimum supply voltage from 1.65 to 1.8 V.           Updated number of AHB buses in Section 2: Description and<br>Section 3.12: Clocks and startup.           Removed Figure 4. Compatible board design between STM32F10xx<br>and STM32F2xx for LQFP176 package.           Updated Note 2 below Figure 4: STM32F20x block diagram.           Changed System memory to System memory + OTP in Figure 16:<br>Memory map.           Added Note 1 below Table 16: VCAP1/VCAP2 operating conditions.           Updated V <sub>DDA</sub> and V <sub>REF+</sub> decouping capacitor in Figure 19: Power<br>supply scheme and updated Note 3.           Changed simplex mode into half-duplex mode in Section 3.24: Inter-<br>integrated sound (I2S).           Replaced DAC1_OUT and DAC2_OUT by DAC_OUT1 and<br>DAC_OUT2, respectively.Changed TIM2_CH1/TIM2_ETR into<br>TIM2_CH1_ETR for PA0 and PA5 in Table 10: Alternate function<br>mapping.           Updated note applying to I <sub>DD</sub> (external clock and all peripheral disabled)<br>in Table 21: Typical and maximum current consumption in Run mode,<br>code with data processing running from Flash memory (ART<br>accelerator disabled). Updated Note 3 below Table 22: Typical and<br>maximum current consumption in Sleep mode.           Removed f <sub>HSE_ext</sub> typical value in Table 28: High-speed external user<br>clock characteristics.           Updated master 12S clock jitter conditions and vlaues in Table 35:<br>PLLI2S (audio PLL) characteristics.           Updated quations in Section 6.3.11: PLL spread spectrum clock<br>generation (SSCG) characteristics.           Updated TL and CMOS port conditions for V <sub>OL</sub> and V <sub>OH</sub> in Table 47:<br>Output voltage characteristics. |  |  |

|                                                 |          | Swapped TTL and CMOS port conditions for $V_{OL}$ and $V_{OH}$ in <i>Table 47:</i><br><i>Output voltage characteristics.</i><br>Updated $V_{IL(NRST)}$ and $V_{IH(NRST)}$ in <i>Table 49: NRST pin characteristics.</i><br>Updated <i>Table 54: SPI characteristics</i> and <i>Table 55: I2S characteristics.</i><br>Removed note 1 related to measurement points below <i>Figure 43: SPI timing diagram - slave mode and CPHA = 1, Figure 44: SPI timing diagram - master mode,</i> and <i>Figure 45: I2S slave timing diagram (Philips protocol)(1).</i><br>Updated t <sub>HC</sub> in <i>Table 61: ULPI timing.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|                                                 |          | Updated Figure 49: Ethernet SMI timing diagram, Table 63: Dynamics characteristics: Ethernet MAC signals for SMI and Table 65: Dynamics characteristics: Ethernet MAC signals for MII.<br>Update f <sub>TRIG</sub> in Table 66: ADC characteristics.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|                                                 |          | Updated I <sub>DDA</sub> description in <i>Table 68: DAC characteristics</i> .<br>Updated note below <i>Figure 54: Power supply and reference decoupling</i> ( <i>VREF+ not connected to VDDA</i> ) and <i>Figure 55: Power supply and reference decoupling</i> ( <i>VREF+ connected to VDDA</i> ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID15818 Rev 13