#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 120MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 114                                                                   |

| Program Memory Size        | 256KB (256K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 100K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 144-LQFP                                                              |

| Supplier Device Package    | 144-LQFP (20x20)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205zct6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.1 Full compatibility throughout the family

The STM32F205xx and STM32F207xx constitute the STM32F20x family whose members are fully pin-to-pin, software and feature compatible, allowing the user to try different memory densities and peripherals for a greater degree of freedom during the development cycle.

The STM32F205xx and STM32F207xx devices maintain a close compatibility with the whole STM32F10xxx family. All functional pins are pin-to-pin compatible. The STM32F205xx and STM32F207xx, however, are not drop-in replacements for the STM32F10xxx devices: the two families do not have the same power scheme, and so their power pins are different. Nonetheless, transition from the STM32F10xxx to the STM32F20x family remains simple as only a few pins are impacted.

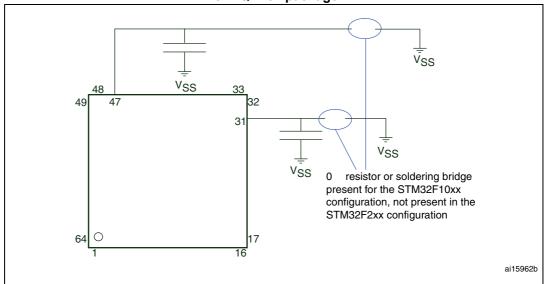

*Figure 1*, *Figure 2* and *Figure 3* provide compatible board designs between the STM32F20x and the STM32F10xxx family.

Figure 1. Compatible board design between STM32F10xx and STM32F2xx for LQFP64 package

## 3.34 ADCs (analog-to-digital converters)

Three 12-bit analog-to-digital converters are embedded and each ADC shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the timers TIM1, TIM2, TIM3, TIM4, TIM5 and TIM8 can be internally connected to the ADC start trigger and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

# 3.35 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

### 3.36 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.8 and 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

DocID15818 Rev 13

|   | 1                  | 2             | 3            | 4      | 5   | 6     | 7    | 8    | 9    | 10     | 11   | 12   | 13     | 14   | 15   |

|---|--------------------|---------------|--------------|--------|-----|-------|------|------|------|--------|------|------|--------|------|------|

| А | PE3                | PE2           | PE1          | PE0    | PB8 | PB5   | PG14 | PG13 | PB4  | PB3    | PD7  | PC12 | PA15   | PA14 | PA13 |

| в | PE4                | PE5           | PE6          | PB9    | PB7 | PB6   | PG15 | PG12 | PG11 | PG10   | PD6  | PD0  | PC11   | PC10 | PA12 |

| С | VBAT               | PI7           | PI6          | PI5    | VDD | RFU   | VDD  | VDD  | VDD  | PG9    | PD5  | PD1  | PI3    | Pl2  | PA11 |

| D | PC13-<br>TAMP1     | PI8-<br>TAMP2 | PI9          | PI4    | VSS | BOOT0 | VSS  | VSS  | VSS  | PD4    | PD3  | PD2  | PH15   | PI1  | PA10 |

| Е | PC14-<br>OSC32_IN  | PF0           | PI10         | PI11   |     |       |      |      |      |        |      | PH13 | PH14   | P10  | PA9  |

| F | PC15-<br>OSC32_OUT | VSS           | VDD          | PH2    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VSS  | VCAP_2 | PC9  | PA8  |

| G | PH0-<br>OSC_IN     | VSS           | VDD          | PH3    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PC8  | PC7  |

| н | PH1-<br>OSC_OUT    | PF2           | PF1          | PH4    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PG8  | PC6  |

| J | NRST               | PF3           | PF4          | PH5    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | VDD  | VDD    | PG7  | PG6  |

| к | PF7                | PF6           | PF5          | VDD    |     | VSS   | VSS  | VSS  | VSS  | VSS    |      | PH12 | PG5    | PG4  | PG3  |

| L | PF10               | PF9           | PF8          | REGOFF |     |       |      |      |      |        |      | PH11 | PH10   | PD15 | PG2  |

| м | VSSA               | PC0           | PC1          | PC2    | PC3 | PB2   | PG1  | VSS  | VSS  | VCAP_1 | PH6  | PH8  | PH9    | PD14 | PD13 |

| N | VREF-              | PA1           | PA0-<br>WKUP | PA4    | PC4 | PF13  | PG0  | VDD  | VDD  | VDD    | PE13 | PH7  | PD12   | PD11 | PD10 |

| Ρ | VREF+              | PA2           | PA6          | PA5    | PC5 | PF12  | PF15 | PE8  | PE9  | PE11   | PE14 | PB12 | PB13   | PD9  | PD8  |

| R | VDDA               | PA3           | PA7          | PB1    | PB0 | PF11  | PF14 | PE7  | PE10 | PE12   | PE15 | PB10 | PB11   | PB14 | PB15 |

Figure 15. STM32F20x UFBGA176 ballout

1. RFU means "reserved for future use". This pin can be tied to  $V_{\text{DD}}, V_{\text{SS}}$  or left unconnected.

2. The above figure shows the package top view.

|  | Table 7. Legend/abbreviations used in the p | inout table |

|--|---------------------------------------------|-------------|

|--|---------------------------------------------|-------------|

| Name                   | Abbreviation       | Definition                                                                                         |  |  |  |  |

|------------------------|--------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin name               |                    | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |

|                        | S                  | Supply pin                                                                                         |  |  |  |  |

| Pin type               | I                  | Input only pin                                                                                     |  |  |  |  |

|                        | I/O                | Input/ output pin                                                                                  |  |  |  |  |

|                        | FT                 | 5 V tolerant I/O                                                                                   |  |  |  |  |

| I/O structure          | TTa                | TTa 3.3 V tolerant I/O                                                                             |  |  |  |  |

| NO structure           | В                  | B Dedicated BOOT0 pin                                                                              |  |  |  |  |

|                        | RST                | Bidirectional reset pin with embedded weak pull-up resistor                                        |  |  |  |  |

| Notes                  | Unless otherwise   | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |

| Alternate<br>functions | Functions selected | d through GPIOx_AFR registers                                                                      |  |  |  |  |

| Additional functions   | Functions directly | selected/enabled through peripheral registers                                                      |  |  |  |  |

| 6 <u>4</u> |

|------------|

| 2          |

| 82         |

### Table 10 Alternate function mapping (continued)

|        |      | AF0 | AF1    | AF2      | AF3          | AF4            | AF5            | AF6       | AF7        | AF8                | AF9                       | AF10           | AF11                                 | AF12                     | AF13     |       |        |

|--------|------|-----|--------|----------|--------------|----------------|----------------|-----------|------------|--------------------|---------------------------|----------------|--------------------------------------|--------------------------|----------|-------|--------|

|        | Port | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10/11 | 12C1/12C2/12C3 | SPI1/SPI2/I2S2 | SPI3/I2S3 | USART1/2/3 | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 | OTG_FS/ OTG_HS | ЕТН                                  | FSMC/SDIO/<br>OTG_HS     | DCMI     | AF014 | AF15   |

|        | PF0  | -   | -      | -        | -            | I2C2_SDA       | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A0                  | -        | -     | EVENT  |

|        | PF1  | -   | -      | -        | -            | I2C2_SCL       |                | -         | -          | -                  | -                         | -              | -                                    | FSMC_A1                  | -        | -     | EVENTO |

|        | PF2  | -   | -      | -        | -            | I2C2_SMBA      | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A2                  | -        | -     | EVENT  |

|        | PF3  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A3                  | -        | -     | EVENT  |

|        | PF4  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A4                  | -        | -     | EVENT  |

|        | PF5  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A5                  | -        | -     | EVENT  |

|        | PF6  | -   | -      | -        | TIM10_CH1    | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_NIORD               | -        | -     | EVENT  |

| Port F | PF7  | -   | -      | -        | TIM11_CH1    | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_NREG                | -        | -     | EVENT  |

| FUILF  | PF8  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | TIM13_CH1                 | -              | -                                    | FSMC_NIOWR               | -        | -     | EVEN   |

|        | PF9  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | TIM14_CH1                 | -              | -                                    | FSMC_CD                  | -        | -     | EVEN   |

|        | PF10 | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_INTR                | -        | -     | EVEN.  |

|        | PF11 | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    |                          | DCMI_D12 | -     | EVEN   |

|        | PF12 | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A6                  | -        | -     | EVEN   |

|        | PF13 | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A7                  | -        | -     | EVEN   |

|        | PF14 | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A8                  | -        | -     | EVEN   |

|        | PF15 | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A9                  | -        | -     | EVEN   |

|        | PG0  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A10                 | -        | -     | EVEN   |

|        | PG1  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A11                 | -        | -     | EVEN   |

|        | PG2  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A12                 | -        | -     | EVEN   |

|        | PG3  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A13                 | -        | -     | EVEN   |

|        | PG4  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A14                 | -        | -     | EVEN   |

|        | PG5  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_A15                 | -        | -     | EVEN   |

|        | PG6  | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_INT2                | -        | -     | EVEN   |

|        | PG7  | -   | -      | -        | -            | -              | -              | -         | -          | USART6_CK          | -                         | -              | -                                    | FSMC_INT3                | -        | -     | EVEN.  |

| Port G | PG8  | -   | -      | -        | -            | -              | -              | -         | -          | USART6_RTS         | -                         | -              | ETH_PPS_OUT                          | -                        | -        | -     | EVEN   |

|        | PG9  | -   | -      | -        | -            | -              | -              | -         | -          | USART6_RX          | -                         | -              | -                                    | FSMC_NE2/<br>FSMC_NCE3   | -        | -     | EVENT  |

|        | PG10 | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | -                                    | FSMC_NCE4_1/<br>FSMC_NE3 | -        | -     | EVEN   |

|        | PG11 | -   | -      | -        | -            | -              | -              | -         | -          | -                  | -                         | -              | ETH _MII_TX_EN<br>ETH<br>_RMII_TX_EN | FSMC_NCE4_2              | -        | -     | EVENT  |

|        | PG12 | -   | -      | -        | -            | -              | -              | -         | -          | USART6_RTS         | -                         | -              | -                                    | FSMC_NE4                 | -        | -     | EVENT  |

|        | PG13 | -   | -      | -        | -            | -              | -              | -         | -          | UART6_CTS          | -                         | -              | ETH_MII_TXD0<br>ETH_RMII_TXD0        | FSMC_A24                 | -        | -     | EVEN   |

|        | PG14 | -   | -      | -        | -            | -              | -              | -         | -          | USART6_TX          | -                         | -              | ETH_MII_TXD1<br>ETH_RMII_TXD1        | FSMC_A25                 | -        | -     | EVEN   |

|        | PG15 | -   | -      | -        | -            | -              | -              | -         | -          | USART6_CTS         | -                         | -              | -                                    | -                        | DCMI_D13 | -     | EVENT  |

STM32F20xxx

# 5 Memory mapping

The memory map is shown in *Figure 16*.

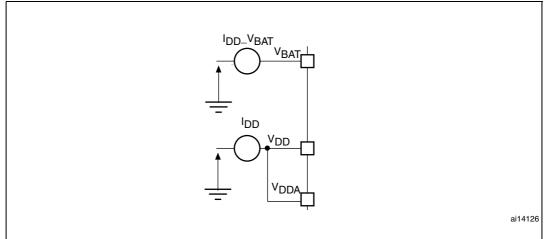

### 6.1.7 Current consumption measurement

### Figure 20. Current consumption measurement scheme

## 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                                       | Min                  | Max                                                                     | Unit |

|-----------------------------------|-------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------|------|

| $V_{DD} - V_{SS}$                 | External main supply voltage (including $V_{DDA}$ , $V_{DD}$ ) <sup>(1)</sup> | -0.3                 | 4.0                                                                     |      |

| V                                 | Input voltage on five-volt tolerant pin <sup>(2)</sup>                        | V <sub>SS</sub> -0.3 | 3 V <sub>DD</sub> +4<br>3 4.0<br>50<br>50<br>ction 6.3.14:<br>e maximum | V    |

| V <sub>IN</sub>                   | Input voltage on any other pin                                                | V <sub>SS</sub> -0.3 | 4.0                                                                     |      |

| $ \Delta V_{DDx} $                | Variations between different $V_{DD}$ power pins                              | -                    | 50                                                                      | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins                              | -                    | 50                                                                      | 1110 |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                            |                      | naximum<br>ectrical                                                     | -    |

#### Table 11. Voltage characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

V<sub>IN</sub> maximum value must always be respected. Refer to *Table 12* for the values of the maximum allowed injected current.

|          |                                   |                                                                                                                                                  | Тур                       |                           | Max                       |                            |      |

|----------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol I | Parameter                         | Conditions                                                                                                                                       | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

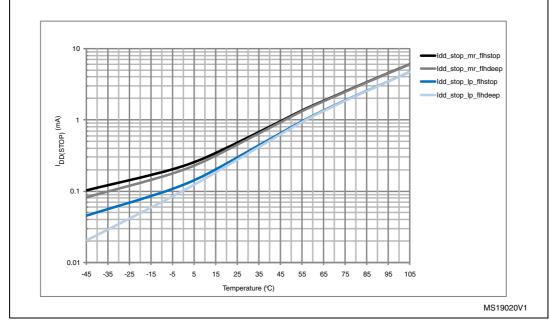

|          | Supply current<br>in Stop mode    | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.55                      | 1.2                       | 11.00                     | 20.00                      |      |

|          | Run mode                          | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.50                      | 1.2                       | 11.00                     | 20.00                      | mA   |

|          | Supply current                    | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.35                      | 1.1                       | 8.00                      | 15.00                      | IIIA |

|          | regulator in<br>Low-power<br>mode | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.30                      | 1.1                       | 8.00                      | 105 °C<br>20.00<br>20.00   |      |

Table 23. Typical and maximum current consumptions in Stop mode

Figure 29. Typical current consumption vs. temperature in Stop mode

All typical and maximum values from table 18 and figure 26 will be reduced over time by up to 50% as part

of ST continuous improvement of test procedures. New versions of the datasheet will be released to reflect

these changes

### 6.3.11 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 42: EMI characteristics*). It is available only on the main PLL.

| Symbol            |                       |      | Max <sup>(1)</sup> | Unit               |     |

|-------------------|-----------------------|------|--------------------|--------------------|-----|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -                  | 10                 | KHz |

| md                | Peak modulation depth | 0.25 | -                  | 2                  | %   |

| MODEPER * INCSTEP | -                     | -    | -                  | 2 <sup>15</sup> –1 | -   |

| Table 36. | SSCG | parameters | constraint |

|-----------|------|------------|------------|

1. Guaranteed by design, not tested in production.

#### Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

```

MODEPER = round[f_{PLL \ IN}/ \ (4 \times f_{Mod})]

```

$f_{\text{PLL}\ \text{IN}}$  and  $f_{\text{Mod}}$  must be expressed in Hz.

As an example:

If  $f_{PLL_IN} = 1$  MHz and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round

$$[10^{6}/(4 \times 10^{3})] = 250$$

### **Equation 2**

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[

$$((2^{15} - 1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

f<sub>VCO OUT</sub> must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/ ((2<sup>15</sup> - 1) × PLLN)

As a result:

$$md_{quantized} \% = (250 \times 126 \times 100 \times 5) / ((2^{15} - 1) \times 240) = 2.0002\%$$

(peak)

DocID15818 Rev 13

| Symbol                            | Parameter                                                                     | Conditions                                                | Min                  | Max | Unit |

|-----------------------------------|-------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | CMOS ports<br>I <sub>IO</sub> = +8 mA                     | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time | $2.7 V < V_{DD} < 3.6 V$                                  | V <sub>DD</sub> 0.4  | -   | v    |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | TTL ports                                                 | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time | I <sub>IO</sub> =+ 8mA<br>2.7 V < V <sub>DD</sub> < 3.6 V | 2.4                  | -   | v    |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +20 mA                                  | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2.7 V < V <sub>DD</sub> < 3.6 V                           | V <sub>DD</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +6 mA                                   | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2 V < V <sub>DD</sub> < 2.7 V                             | V <sub>DD</sub> -0.4 | -   | v    |

PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. to drive an LED).

- 2. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

- 3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 12 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

- 4. Guaranteed by characterization results, not tested in production.

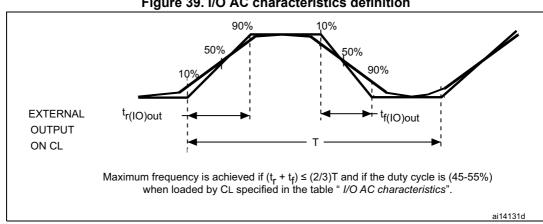

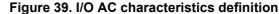

### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 39* and *Table 48*, respectively.

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                                                                                                                                                                                                                | Min                                                 | Тур | Max | Unit |     |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|------|-----|

|                                               |                                                  |                                                                                 | $C_L$ = 50 pF, $V_{DD}$ > 2.70 V                                                                                                                                                                                                                          | -                                                   | -   | 4   |      |     |

|                                               | f                                                | IX(IO)out Maximum frequency <sup>(2)</sup>                                      | $f_{max(IO)out} \text{ Maximum frequency}^{(2)} \qquad \frac{C_L = 50 \text{ pF}, \text{ V}_{DD} \text{ > } 1.8 \text{ V}}{C_L = 10 \text{ pF}, \text{ V}_{DD} \text{ > } 2.70 \text{ V}}$ $C_L = 10 \text{ pF}, \text{ V}_{DD} \text{ > } 1.8 \text{ V}$ | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 2    | MHz |

|                                               | Imax(IO)out                                      |                                                                                 |                                                                                                                                                                                                                                                           | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 8    |     |

| 00                                            |                                                  |                                                                                 |                                                                                                                                                                                                                                                           | -                                                   | -   | 4   |      |     |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.8 V to<br>3.6 V                                                                                                                                                                                               | -                                                   | -   | 100 | ns   |     |

| Table 4 | 48. | I/O | AC | characteristics <sup>(1)</sup> |

|---------|-----|-----|----|--------------------------------|

|---------|-----|-----|----|--------------------------------|

#### 6.3.17 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see Table 49).

Unless otherwise specified, the parameters given in Table 49 are derived from tests performed under the ambient temperature and  $V_{\text{DD}}$  supply voltage conditions summarized in Table 14.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       | -                       | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

#### Table 49. NRST pin characteristics

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series 1. resistance must be minimum (~10% order).

2. Guaranteed by design, not tested in production.

### Figure 40. Recommended NRST pin protection

- The reset network protects the device against parasitic resets. 1.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in 2. Table 49. Otherwise the reset is not taken into account by the device.

| Symbol                 | Parameter                       | Conditions                                                      | Min    | Max                     | Unit                 |

|------------------------|---------------------------------|-----------------------------------------------------------------|--------|-------------------------|----------------------|

|                        |                                 | AHB/APB2                                                        | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time           | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>120 MHz | 8.3    | -                       | ns                   |

|                        |                                 | AHB/APB2                                                        | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                 | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 60 MHz                 | 16.7   | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock            |                                                                 | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| 'EXT                   | frequency on CH1 to CH4         |                                                                 | 0      | 60                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                |                                                                 | -      | 16                      | bit                  |

| +                      | 16-bit counter clock period     | f <sub>TIMxCLK</sub> = 120 MHz<br>APB2 = 60 MHz                 | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| <sup>t</sup> COUNTER   | when internal clock is selected | APB2 = 60 MH2                                                   | 0.0083 | 546                     | μs                   |

| tury ocume             | Maximum possible count          |                                                                 | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT | Maximum possible count          |                                                                 | -      | 35.79                   | S                    |

Table 51. Characteristics of TIMx connected to the APB2 domain<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM1, TIM8, TIM9, TIM10, and TIM11 timers.

### 6.3.19 Communications interfaces

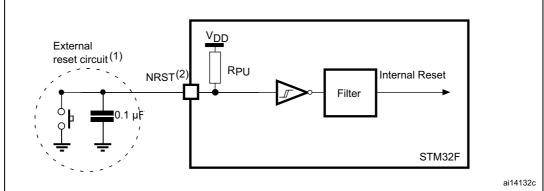

### I<sup>2</sup>C interface characteristics

STM32F205xx and STM32F207xx  $I^2$ C interface meets the requirements of the standard  $I^2$ C communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 52*. Refer also to *Section 6.3.16*: I/O port characteristics for more details on the input/output alternate function characteristics (SDA and SCL).

Figure 41. I<sup>2</sup>C bus AC waveforms and measurement circuit

- 1.  $R_S$ = series protection resistor.

- 2. R<sub>P</sub> = external pull-up resistor.

- 3.  $V_{DD_{12C}}$  is the I<sup>2</sup>C bus power supply.

| f (kU-)                | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x8019                  |

| 300                    | 0x8021                  |

| 200                    | 0x8032                  |

| 100                    | 0x0096                  |

| 50                     | 0x012C                  |

| 20                     | 0x02EE                  |

### Table 53. SCL frequency (f<sub>PCLK1</sub>= 30 MHz., V<sub>DD</sub> = 3.3 V)<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  = I<sup>2</sup>C speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

### 6.3.20 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 66* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 14*.

| Symbol                             | Parameter                                       | Conditions                                          | Min                                                         | Тур        | Мах               | Unit               |

|------------------------------------|-------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|------------|-------------------|--------------------|

| V <sub>DDA</sub>                   | Power supply                                    | -                                                   | 1.8 <sup>(1)</sup>                                          | -          | 3.6               | V                  |

| V <sub>REF+</sub>                  | Positive reference voltage                      | -                                                   | 1.8 <sup>(1)(2)</sup>                                       | -          | V <sub>DDA</sub>  | V                  |

| £                                  | ADC clock frequency                             | $V_{DDA}$ = 1.8 <sup>(1)</sup> to 2.4 V             | 0.6                                                         | -          | 15                | MHz                |

| f <sub>ADC</sub>                   | ADC Clock frequency                             | V <sub>DDA</sub> = 2.4 to 3.6 V                     | 0.6                                                         | -          | 30                | MHz                |

| f <sub>TRIG</sub> <sup>(3)</sup>   | External trigger frequency                      | f <sub>ADC</sub> = 30 MHz with<br>12-bit resolution | -                                                           | -          | 1764              | kHz                |

|                                    |                                                 | -                                                   | -                                                           | -          | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                   | Conversion voltage range <sup>(4)</sup>         | -                                                   | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -          | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(3)</sup>    | External input impedance                        | See <i>Equation 1</i> for details                   | -                                                           | -          | 50                | kΩ                 |

| R <sub>ADC</sub> <sup>(3)(5)</sup> | Sampling switch resistance                      | -                                                   | 1.5                                                         | -          | 6                 | kΩ                 |

| C <sub>ADC</sub> <sup>(3)</sup>    | Internal sample and hold capacitor              | -                                                   | -                                                           | 4          | -                 | pF                 |

| t <sub>lat</sub> (3)               | Injection trigger conversion<br>latency         | f <sub>ADC</sub> = 30 MHz                           | -                                                           | -          | 0.100             | μs                 |

| 'lat` ´                            |                                                 | -                                                   | -                                                           | -          | 3 <sup>(6)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (3)              | Regular trigger conversion latency              | f <sub>ADC</sub> = 30 MHz                           | -                                                           | -          | 0.067             | μs                 |

| 4atr` ´                            | Regular ingger conversion latency               | -                                                   | -                                                           | -          | 2 <sup>(6)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(3)</sup>      | Sampling time                                   | f <sub>ADC</sub> = 30 MHz                           | 0.100                                                       | -          | 16                | μs                 |

| LS(*)                              | Sampling une                                    | -                                                   | 3                                                           | -          | 480               | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(3)</sup>   | Power-up time                                   | -                                                   | -                                                           | 2          | 3                 | μs                 |

|                                    |                                                 | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution      | 0.5                                                         | -          | 16.40             | μs                 |

|                                    |                                                 | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution      | 0.43                                                        | -          | 16.34             | μs                 |

|                                    | Total conversion time (including sampling time) | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution       | 0.37                                                        | -          | 16.27             | μs                 |

|                                    |                                                 | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution       | 0.3                                                         | -          | 16.20             | μs                 |

|                                    |                                                 | 9 to 492 (t <sub>S</sub> for samplin approximation) | ng +n-bit resolutior                                        | n for succ | cessive           | 1/f <sub>ADC</sub> |

| Table | 66. / | ADC | characteristics |

|-------|-------|-----|-----------------|

| Table |       |     | characteristics |

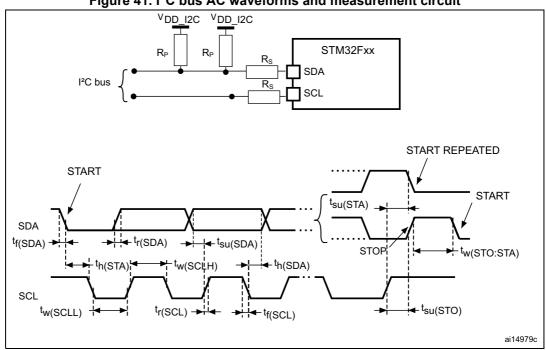

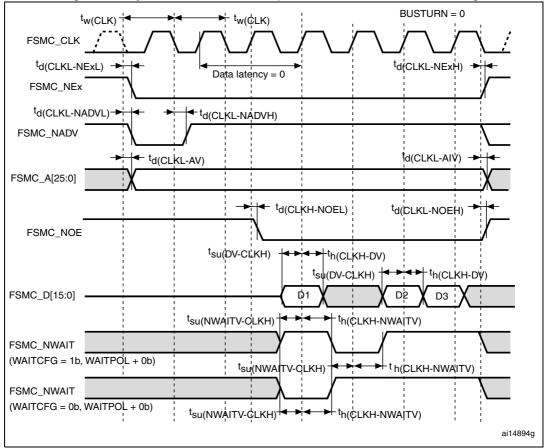

Figure 61. Synchronous multiplexed NOR/PSRAM read timings

| able 76. Synchronous multiplexed NOR/PSRAM read timings <sup>(1)(2)</sup> | minas <sup>(1)(2)</sup> |

|---------------------------------------------------------------------------|-------------------------|

| able 10. Synchronous multiplexed NON/FSIXAW read unnings                  | migs                    |

| Symbol                     | Parameter                                | Min                | Мах | Unit |

|----------------------------|------------------------------------------|--------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                          | 2T <sub>HCLK</sub> | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)      | -                  | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)    | 1                  | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low            | -                  | 1.5 | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high           | 2.5                | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)   | -                  | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625) | 0                  | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>  | FSMC_CLK high to FSMC_NOE low            | -                  | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>  | FSMC_CLK low to FSMC_NOE high            | 1                  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>   | FSMC_CLK low to FSMC_AD[15:0] valid      | -                  | 3   | ns   |

| t <sub>d(CLKL-ADIV)</sub>  | FSMC_CLK low to FSMC_AD[15:0] invalid    | 0                  | -   | ns   |

| Symbol                     | Parameter                                    | Min | Max | Unit |

|----------------------------|----------------------------------------------|-----|-----|------|

| t <sub>d(CLKL-NWEL)</sub>  | FSMC_CLK low to FSMC_NWE low                 | -   | 1   | ns   |

| t <sub>d(CLKL-NWEH)</sub>  | FSMC_CLK low to FSMC_NWE high                | 0   | -   | ns   |

| t <sub>d(CLKL-ADIV)</sub>  | FSMC_CLK low to FSMC_AD[15:0] invalid        | 0   | -   | ns   |

| t <sub>d(CLKL-DATA</sub> ) | FSMC_A/D[15:0] valid data after FSMC_CLK low | -   | 2   | ns   |

| t <sub>d(CLKL-NBLH)</sub>  | FSMC_CLK low to FSMC_NBL high                | 0.5 | -   | ns   |

Table 77. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

### Figure 63. Synchronous non-multiplexed NOR/PSRAM read timings

| able 78. Synchronous non-multiplexed NOR/PSRAM read timings <sup>(1)(2)</sup> | ) |

|-------------------------------------------------------------------------------|---|

| able ro. Synchronous non-multiplexed NORA SIXAM read timings                  |   |

| Symbol                     | Parameter                             | Min                | Max | Unit |

|----------------------------|---------------------------------------|--------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                       | 2T <sub>HCLK</sub> | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)   | -                  | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02) | 1                  | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low         | -                  | 2.5 | ns   |

# 8 Part numbering

| Table 96. Ordering information scheme              |     |   |     |     |      |

|----------------------------------------------------|-----|---|-----|-----|------|

| Example: STM32 F                                   | 205 | R | E ' | T 6 | Vxxx |

|                                                    |     |   |     |     |      |

| Device family                                      |     |   |     |     |      |

| STM32 = ARM-based 32-bit microcontroller           |     |   |     |     |      |

| Product type                                       |     |   |     |     |      |

| F = general-purpose                                |     |   |     |     |      |

| Device subfamily                                   |     |   |     |     |      |

| 205 = STM32F20x, connectivity                      |     |   |     |     |      |

| 207= STM32F20x, connectivity, camera interface,    |     |   |     |     |      |

| Ethernet                                           |     |   |     |     |      |

| Pin count                                          |     |   |     |     |      |

| R = 64 pins or 66 pins <sup>(1)</sup>              |     |   |     |     |      |

| V = 100 pins                                       |     |   |     |     |      |

| Z = 144 pins                                       |     |   |     |     |      |

| l = 176 pins                                       |     |   |     |     |      |

|                                                    |     |   |     |     |      |

| Flash memory size                                  |     |   |     |     |      |

| B = 128 Kbytes of Flash memory                     |     |   |     |     |      |

| C = 256 Kbytes of Flash memory                     |     |   |     |     |      |

| E = 512 Kbytes of Flash memory                     |     |   |     |     |      |

| F = 768 Kbytes of Flash memory                     |     |   |     |     |      |

| G = 1024 Kbytes of Flash memory                    |     |   |     |     |      |

| Package                                            |     |   |     |     |      |

| T = LQFP                                           |     |   |     |     |      |

| H = UFBGA                                          |     |   |     |     |      |

| Y = WLCSP                                          |     |   |     |     |      |

| Temperature range                                  |     |   |     |     |      |

| 6 = Industrial temperature range, -40 to 85 °C.    | _   |   |     |     |      |

| 7 = Industrial temperature range, $-40$ to 105 °C. |     |   |     |     |      |

| Software option                                    |     |   |     |     |      |

| Internal code or Blank                             |     |   |     |     |      |

| Options                                            |     |   |     |     |      |

xxx = programmed parts TR = tape and reel

1. The 66 pins is available on WLCSP package only.

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

| Data                                       |

|--------------------------------------------|

| Date R                                     |

| Date       R         13-Jul-2010       (cc |

|             | Table                                                                                                                                                                           | 97. Document revision history (continued)                                                                                                                                                                                                                                                          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision                                                                                                                                                                        | Changes                                                                                                                                                                                                                                                                                            |

|             |                                                                                                                                                                                 | Update I/Os in <i>Section : Features</i> .<br>Added WLCSP64+2 package. Added note 1 related to LQFP176 on                                                                                                                                                                                          |

|             |                                                                                                                                                                                 | cover page.                                                                                                                                                                                                                                                                                        |

|             |                                                                                                                                                                                 | Added trademark for ART accelerator. Updated Section 3.2: Adaptive real-time memory accelerator (ART Accelerator™).                                                                                                                                                                                |

|             |                                                                                                                                                                                 | Updated Figure 5: Multi-AHB matrix.                                                                                                                                                                                                                                                                |

|             |                                                                                                                                                                                 | Added case of BOR inactivation using IRROFF on WLCSP devices in <i>Section 3.15: Power supply supervisor</i> .                                                                                                                                                                                     |

|             |                                                                                                                                                                                 | Reworked <i>Section 3.16: Voltage regulator</i> to clarify regulator off modes.<br>Renamed PDROFF, IRROFF in the whole document.                                                                                                                                                                   |

|             |                                                                                                                                                                                 | Added Section 3.19: VBAT operation.                                                                                                                                                                                                                                                                |

|             |                                                                                                                                                                                 | Updated LIN and IrDA features for UART4/5 in Table 6: USART feature comparison.                                                                                                                                                                                                                    |

|             |                                                                                                                                                                                 | <i>Table 8: STM32F20x pin and ball definitions</i> : Modified V <sub>DD_3</sub> pin, and added note related to the FSMC_NL pin; renamed BYPASS-REG REGOFF, and add IRROFF pin; renamed USART4/5 UART4/5. USART4 pins renamed UART4.                                                                |

|             |                                                                                                                                                                                 | Changed $V_{SS}$ SA to $V_{SS}$ , and $V_{DD}$ SA pin reserved for future use.                                                                                                                                                                                                                     |

|             |                                                                                                                                                                                 | Updated maximum HSE crystal frequency to 26 MHz.                                                                                                                                                                                                                                                   |

|             |                                                                                                                                                                                 | Section 6.2: Absolute maximum ratings: Updated V <sub>IN</sub> minimum and maximum values and note related to five-volt tolerant inputs in <i>Table 11</i> . Voltage characteristics. Updated I <sub>INJ(PIN)</sub> maximum values and related notes in <i>Table 12: Current characteristics</i> . |

| 25-Nov-2010 | 5                                                                                                                                                                               | Updated V <sub>DDA</sub> minimum value in <i>Table 14: General operating conditions</i> .                                                                                                                                                                                                          |

|             |                                                                                                                                                                                 | Added Note 2 and updated Maximum CPU frequency in <i>Table 15:</i><br><i>Limitations depending on the operating power supply range</i> , and added<br><i>Figure 21: Number of wait states versus fCPU and VDD range</i> .                                                                          |

|             |                                                                                                                                                                                 | Added brownout level 1, 2, and 3 thresholds in <i>Table 19: Embedded</i> reset and power control block characteristics.                                                                                                                                                                            |

|             |                                                                                                                                                                                 | Changed f <sub>OSC_IN</sub> maximum value in <i>Table 30: HSE 4-26 MHz oscillator characteristics</i> .                                                                                                                                                                                            |

|             | Changed f <sub>PLL_IN</sub> maximum value in <i>Table 34: Main PLL characteristics</i> , and updated jitter parameters in <i>Table 35: PLLI2S (audio PLL) characteristics</i> . |                                                                                                                                                                                                                                                                                                    |

|             | Section 6.3.16: I/O port characteristics: updated V <sub>IH</sub> and V <sub>IL</sub> in Table 48. I/O AC characteristics.                                                      |                                                                                                                                                                                                                                                                                                    |

|             |                                                                                                                                                                                 | Added Note 1 below Table 47: Output voltage characteristics.                                                                                                                                                                                                                                       |

|             |                                                                                                                                                                                 | Updated R <sub>PD</sub> and R <sub>PU</sub> parameter description in <i>Table 57: USB OTG FS</i><br>DC electrical characteristics.                                                                                                                                                                 |

|             |                                                                                                                                                                                 | Updated V <sub>REF+</sub> minimum value in <i>Table 66: ADC characteristics</i> .                                                                                                                                                                                                                  |

|             |                                                                                                                                                                                 | Updated Table 71: Embedded internal reference voltage.                                                                                                                                                                                                                                             |

|             |                                                                                                                                                                                 | Removed Ethernet and USB2 for 64-pin devices in <i>Table 101: Main applications versus package for STM32F2xxx microcontrollers</i> .                                                                                                                                                               |

|             |                                                                                                                                                                                 | Added A.2: USB OTG full speed (FS) interface solutions, removed<br>"OTG FS connection with external PHY" figure, updated Figure 87,<br>Figure 88, and Figure 90 to add STULPI01B.                                                                                                                  |

Table 97. Document revision history (continued)

|             | Table 97. Document revision history (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date        | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 14-Jun-2011 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Added SDIO in <i>Table 2: STM32F205xx features and peripheral counts.</i><br>Updated V <sub>IN</sub> for 5V tolerant pins in <i>Table 11: Voltage characteristics.</i><br>Updated jitter parameters description in <i>Table 34: Main PLL characteristics.</i><br>Remove jitter values for system clock in <i>Table 35: PLLI2S (audio PLL) characteristics.</i><br>Updated <i>Table 42: EMI characteristics.</i><br>Updated <i>Table 42: EMI characteristics.</i><br>Updated <i>Note 2</i> in <i>Table 52: I2C characteristics.</i><br>Updated Avg_Slope typical value and $T_{S\_temp}$ minimum value in <i>Table 69: Temperature sensor characteristics.</i><br>Updated $T_{S\_vbat}$ minimum value in <i>Table 70: VBAT monitoring characteristics.</i><br>Updated $T_{S\_vrefint}$ minimum value in <i>Table 71: Embedded internal reference voltage.</i><br>Added Software option in <i>Section 8: Part numbering.</i><br>In <i>Table 101: Main applications versus package for STM32F2xxx microcontrollers,</i> renamed USB1 and USB2, USB OTG FS and USB<br>OTG HS, respectively; and removed USB OTG HS on 64-pin package; added <i>Note 1</i> and <i>Note 2.</i> |  |  |  |