#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 120MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT       |

| Number of I/O              | 114                                                                     |

| Program Memory Size        | 256КВ (256К х 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 100K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 144-LQFP                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205zct7tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

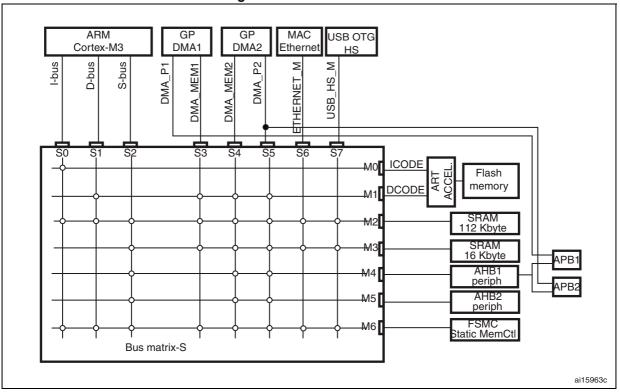

Figure 5. Multi-AHB matrix

# 3.8 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They share some centralized FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

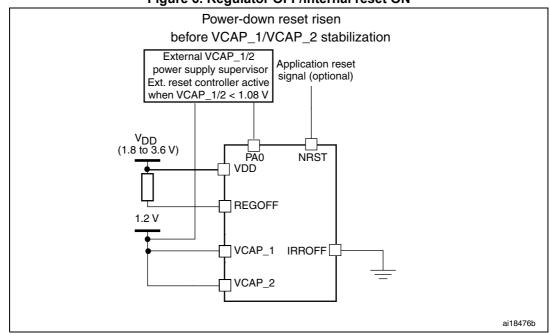

Figure 6. Regulator OFF/internal reset ON

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach 1.08 V is faster than the time for  $V_{DD}$  to reach 1.8 V, then PA0 should be kept low to cover both conditions: until  $V_{CAP_1}$  and  $V_{CAP_2}$  reach 1.08 V and until  $V_{DD}$  reaches 1.8 V (see *Figure 8*).

- Otherwise, If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach 1.08 V is slower than the time for V<sub>DD</sub> to reach 1.8 V, then PA0 should be asserted low externally (see *Figure 9*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below 1.08 V and V<sub>DD</sub> is higher than 1.8 V, then a reset must be asserted on PA0 pin.

# **Regulator OFF/internal reset OFF**

On WLCSP64+2 package, this mode activated by connecting REGOFF to V<sub>SS</sub> and IRROFF to V<sub>DD</sub>. IRROFF cannot be activated in conjunction with REGOFF. This mode is available only on the WLCSP64+2 package. It allows to supply externally a 1.2 V voltage source through V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> pins. In this mode, the integrated power-on reset (POR)/ power-down reset (PDR) circuitry is disabled.

An external power supply supervisor should monitor both the external 1.2 V and the external  $V_{DD}$  supply voltage, and should maintain the device in reset mode as long as they remain below a specified threshold. The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.8 V. This supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range. A comprehensive set of power-saving modes allows to design low-power applications.

# 3.16.3 Regulator ON/OFF and internal reset ON/OFF availability

| Table 4. R                              | Table 4. Regulator ON/OFF and Internal reset ON/OFF availability |                                                       |                                                                           |  |  |  |  |  |  |  |  |  |

|-----------------------------------------|------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Package                                 | Regulator ON/internal reset ON                                   | Regulator<br>OFF/internal reset ON                    | Regulator OFF/internal<br>reset OFF                                       |  |  |  |  |  |  |  |  |  |

| LQFP64<br>LQFP100<br>LQFP144<br>LQFP176 | Yes                                                              | No                                                    | No                                                                        |  |  |  |  |  |  |  |  |  |

| WLCSP 64+2                              | Yes<br>REGOFF and IRROFF<br>set to V <sub>SS</sub>               | Yes REGOFF set to $V_{DD}$ and IRROFF set to $V_{SS}$ | Yes<br>REGOFF set to V <sub>SS</sub> and<br>IRROFF set to V <sub>DD</sub> |  |  |  |  |  |  |  |  |  |

| UFBGA176                                | Yes<br>REGOFF set to V <sub>SS</sub>                             | Yes<br>REGOFF set to V <sub>DD</sub>                  | No                                                                        |  |  |  |  |  |  |  |  |  |

Table 4. Regulator ON/OFF and internal reset ON/OFF availability

# 3.17 Real-time clock (RTC), backup SRAM and backup registers

The backup domain of the STM32F20x devices includes:

- The real-time clock (RTC)

- 4 Kbytes of backup SRAM

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Its main features are the following:

- Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28, 29 (leap year), 30, and 31 day of the month.

- Programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes.

- It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal lowpower RC oscillator or the high-speed external clock divided by 128. The internal lowspeed RC has a typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation.

- Two alarm registers are used to generate an alarm at a specific time and calendar fields can be independently masked for alarm comparison. To generate a periodic interrupt, a 16-bit programmable binary auto-reload downcounter with programmable resolution is available and allows automatic wakeup and periodic alarms from every 120 µs to every 36 hours.

- A 20-bit prescaler is used for the time base clock. It is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

The 4-Kbyte backup SRAM is an EEPROM-like area. It can be used to store data which need to be retained in VBAT and standby mode. This memory area is disabled to minimize power consumption (see *Section 3.18: Low-power modes*). It can be enabled by software.

# 3.20 Timers and watchdogs

The STM32F20x devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

*Table 5* compares the features of the advanced-control, general-purpose and basic timers.

| Timer type           | Timer           | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>output | Max<br>interface<br>clock | Max<br>timer<br>clock |

|----------------------|-----------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---------------------------------|-------------------------|---------------------------|-----------------------|

| Advanced-<br>control | TIM1,<br>TIM8   | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                     | 60<br>MHz                 | 120<br>MHz            |

| General              | TIM2,<br>TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                      | 30<br>MHz                 | 60<br>MHz             |

| purpose              | TIM3,<br>TIM4   | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                      | 30<br>MHz                 | 60<br>MHz             |

| Basic                | TIM6,<br>TIM7   | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                      | 30<br>MHz                 | 60<br>MHz             |

|                      | TIM9            | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                      | 60<br>MHz                 | 120<br>MHz            |

| General              | TIM10,<br>TIM11 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                      | 60<br>MHz                 | 120<br>MHz            |

| purpose              | TIM12           | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 2                               | No                      | 30<br>MHz                 | 60<br>MHz             |

|                      | TIM13,<br>TIM14 | 16-bit                | Up                      | Any integer<br>between 1<br>and 65536 | No                           | 1                               | No                      | 30<br>MHz                 | 60<br>MHz             |

Table 5. Timer feature comparison

# 3.20.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The TIM1 and TIM8 counters can be frozen in debug mode. Many of the advanced-control timer features are shared with those of the standard TIMx timers which have the same architecture. The advanced-control timer can therefore work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

# 3.20.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F20x devices (see *Table 5* for differences).

# TIM2, TIM3, TIM4, TIM5

The STM32F20x include 4 full-featured general-purpose timers. TIM2 and TIM5 are 32-bit timers, and TIM3 and TIM4 are 16-bit timers. The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

The counters of TIM2, TIM3, TIM4, TIM5 can be frozen in debug mode. Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

# TIM10, TIM11 and TIM9

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10 and TIM11 feature one independent channel, whereas TIM9 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

# TIM12, TIM13 and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM13 and TIM14 feature one independent channel, whereas TIM12 has two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers.

They can also be used as simple time bases.

# 3.20.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

DocID15818 Rev 13

| Table 8. STM32 | F20> | c pin | and | ball definitions |

|----------------|------|-------|-----|------------------|

|                |      |       |     |                  |

|        |           | Pi      | ns      |         |          | Table 8. STM32                                       |                                                        |               |                                     |                                                      |                          |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|--------------------------------------------------------|---------------|-------------------------------------|------------------------------------------------------|--------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type                                               | I/O structure | Note                                | Alternate functions                                  | Additional<br>functions  |

| -      | -         | 1       | 1       | 1       | A2       | PE2                                                  | I/O FT - TRACECLK, FSMC_A23,<br>ETH_MII_TXD3, EVENTOUT |               | -                                   |                                                      |                          |

| -      | -         | 2       | 2       | 2       | A1       | PE3                                                  | I/O                                                    | FT            | -                                   | TRACED0,FSMC_A19,<br>EVENTOUT                        | -                        |

| -      | -         | 3       | 3       | 3       | B1       | PE4                                                  | I/O                                                    | FT            | -                                   | TRACED1,FSMC_A20,<br>DCMI_D4, EVENTOUT               | -                        |

| -      | -         | 4       | 4       | 4       | B2       | PE5                                                  | I/O                                                    | FT            | -                                   | TRACED2, FSMC_A21,<br>TIM9_CH1, DCMI_D6,<br>EVENTOUT | -                        |

| -      | -         | 5       | 5       | 5       | В3       | PE6                                                  | I/O                                                    | FT            | -                                   | TRACED3, FSMC_A22,<br>TIM9_CH2, DCMI_D7,<br>EVENTOUT | -                        |

| 1      | A9        | 6       | 6       | 6       | C1       | V <sub>BAT</sub>                                     | S                                                      |               | -                                   | -                                                    | -                        |

| -      | -         | -       | -       | 7       | D2       | PI8                                                  | I/O                                                    | FT            | (2)(3)                              | EVENTOUT                                             | RTC_AF2                  |

| 2      | B8        | 7       | 7       | 8       | D1       | PC13                                                 | I/O                                                    | FT            | (2)(3)                              | EVENTOUT                                             | RTC_AF1                  |

| 3      | В9        | 8       | 8       | 9       | E1       | PC14/OSC32_IN<br>(PC14)                              | I/O                                                    | FT            | (2)(3)                              | EVENTOUT                                             | OSC32_IN <sup>(4)</sup>  |

| 4      | C9        | 9       | 9       | 10      | F1       | PC15-OSC32_OUT<br>(PC15)                             | I/O                                                    | FT            | (2)(3)                              | EVENTOUT                                             | OSC32_OUT <sup>(4)</sup> |

| -      | -         | -       | -       | 11      | D3       | PI9                                                  | I/O                                                    | FT            | -                                   | CAN1_RX,EVENTOUT                                     | -                        |

| -      | -         | -       | -       | 12      | E3       | PI10                                                 | I/O                                                    | FT            | -                                   | ETH_MII_RX_ER,<br>EVENTOUT                           | -                        |

| -      | -         | -       | -       | 13      | E4       | PI11                                                 | I/O                                                    | FT            | -                                   | OTG_HS_ULPI_DIR,<br>EVENTOUT                         | -                        |

| -      | -         | -       | -       | 14      | F2       | V <sub>SS</sub>                                      | S                                                      |               | -                                   | -                                                    | -                        |

| -      | -         | -       | -       | 15      | F3       | V <sub>DD</sub>                                      | S                                                      |               | -                                   | -                                                    | -                        |

| -      | -         | -       | 10      | 16      | E2       | PF0                                                  | I/O                                                    | FT            | FT - FSMC_A0, I2C2_SDA,<br>EVENTOUT |                                                      | -                        |

| -      | -         | -       | 11      | 17      | H3       | PF1                                                  | I/O                                                    | FT            | -                                   | FSMC_A1, I2C2_SCL,<br>EVENTOUT                       | -                        |

| -      | -         | -       | 12      | 18      | H2       | PF2                                                  | I/O                                                    | FT            | -                                   | FSMC_A2, I2C2_SMBA,<br>EVENTOUT                      | -                        |

| -      | -         | -       | 13      | 19      | J2       | PF3                                                  | I/O                                                    | FT            | (4)                                 | FSMC_A3, EVENTOUT                                    | ADC3_IN9                 |

|        |           | Pi      | ns      |         |          |                                                                                                               |          |                                                                              |      |                                                                 |                         |

|--------|-----------|---------|---------|---------|----------|---------------------------------------------------------------------------------------------------------------|----------|------------------------------------------------------------------------------|------|-----------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup>                                                          | Pin type | I/O structure                                                                | Note | Alternate functions                                             | Additional<br>functions |

| 38     | F2        | 64      | 97      | 116     | G15      |                                                                                                               |          | I2S3_MCK, TIM8_CH2,<br>SDIO_D7, USART6_RX,<br>DCMI_D1, TIM3_CH2,<br>EVENTOUT | -    |                                                                 |                         |

| 39     | F3        | 65      | 98      | 117     | G14      | PC8 I/O FT - TIM8_CH3,SDIO_D0,<br>TIM3_CH3, USART6_CK,<br>DCMI_D2, EVENTOUT                                   |          | -                                                                            |      |                                                                 |                         |

| 40     | D1        | 66      | 99      | 118     | F14      | PC9 I/O FT - I2S2_CKIN, I2S3_CKIN,<br>MCO2, TIM8_CH4,<br>SDIO_D1, I2C3_SDA,<br>DCMI_D3, TIM3_CH4,<br>EVENTOUT |          | -                                                                            |      |                                                                 |                         |

| 41     | E2        | 67      | 100     | 119     | F15      | PA8                                                                                                           |          | FT                                                                           | -    | MCO1, USART1_CK,<br>TIM1_CH1, I2C3_SCL,<br>OTG_FS_SOF, EVENTOUT | -                       |

| 42     | E3        | 68      | 101     | 120     | E15      | PA9                                                                                                           | I/O      | FT                                                                           | -    | USART1_TX, TIM1_CH2,<br>I2C3_SMBA, DCMI_D0,<br>EVENTOUT         | OTG_FS_<br>VBUS         |

| 43     | D3        | 69      | 102     | 121     | D15      | PA10                                                                                                          | I/O      | FT                                                                           | -    | USART1_RX, TIM1_CH3,<br>OTG_FS_ID,DCMI_D1,<br>EVENTOUT          | -                       |

| 44     | D2        | 70      | 103     | 122     | C15      | PA11                                                                                                          | I/O      | FT                                                                           | -    | USART1_CTS, CAN1_RX,<br>TIM1_CH4,OTG_FS_DM,<br>EVENTOUT         | -                       |

| 45     | C1        | 71      | 104     | 123     | B15      | PA12                                                                                                          | I/O      | FT                                                                           | -    | USART1_RTS, CAN1_TX,<br>TIM1_ETR, OTG_FS_DP,<br>EVENTOUT        | -                       |

| 46     | B2        | 72      | 105     | 124     | A15      | PA13<br>(JTMS-SWDIO)                                                                                          | I/O      | FT                                                                           | -    | JTMS-SWDIO, EVENTOUT                                            | -                       |

| 47     | C2        | 73      | 106     | 125     | F13      | V <sub>CAP_2</sub>                                                                                            | S        |                                                                              | -    |                                                                 |                         |

| -      | B1        | 74      | 107     | 126     | F12      | V <sub>SS</sub>                                                                                               | S        |                                                                              |      | -                                                               | -                       |

| 48     | A8        | 75      | 108     | 127     | G13      | V <sub>DD</sub>                                                                                               | S        |                                                                              |      |                                                                 |                         |

| -      | -         | -       | -       | 128     | E12      |                                                                                                               |          | TIM8_CH1N, CAN1_TX,<br>EVENTOUT                                              | -    |                                                                 |                         |

| -      | -         | -       | -       | 129     | E13      | PH14                                                                                                          | I/O      | FT                                                                           | -    | TIM8_CH2N, DCMI_D4,<br>EVENTOUT                                 | -                       |

| Table 8. STM32F20x pin and ball definitions | (continued) |

|---------------------------------------------|-------------|

|                                             | (           |

|       |       |                | n definition (continu | ed)         |         |

|-------|-------|----------------|-----------------------|-------------|---------|

| Pins  |       | F              | SMC                   |             | LQFP100 |

| 1 113 | CF    | NOR/PSRAM/SRAM | NOR/PSRAM Mux         | NAND 16 bit | Lairio  |

| PE5   | -     | A21            | A21                   | -           | Yes     |

| PE6   | -     | A22            | A22                   | -           | Yes     |

| PF0   | A0    | A0             | -                     | -           | -       |

| PF1   | A1    | A1             | -                     | -           | -       |

| PF2   | A2    | A2             | -                     | -           | -       |

| PF3   | A3    | A3             | -                     | -           | -       |

| PF4   | A4    | A4             | -                     | -           | -       |

| PF5   | A5    | A5             | -                     | -           | -       |

| PF6   | NIORD | -              | -                     | -           | -       |

| PF7   | NREG  | -              | -                     | -           | -       |

| PF8   | NIOWR | -              | -                     | -           | -       |

| PF9   | CD    | -              | -                     | -           | -       |

| PF10  | INTR  | -              | -                     | -           | -       |

| PF12  | A6    | A6             | -                     | -           | -       |

| PF13  | A7    | A7             | -                     | -           | -       |

| PF14  | A8    | A8             | -                     | -           | -       |

| PF15  | A9    | A9             | -                     | -           | -       |

| PG0   | A10   | A10            | -                     | -           | -       |

| PG1   | -     | A11            | -                     | -           | -       |

| PE7   | D4    | D4             | DA4                   | D4          | Yes     |

| PE8   | D5    | D5             | DA5                   | D5          | Yes     |

| PE9   | D6    | D6             | DA6                   | D6          | Yes     |

| PE10  | D7    | D7             | DA7                   | D7          | Yes     |

| PE11  | D8    | D8             | DA8                   | D8          | Yes     |

| PE12  | D9    | D9             | DA9                   | D9          | Yes     |

| PE13  | D10   | D10            | DA10                  | D10         | Yes     |

| PE14  | D11   | D11            | DA11                  | D11         | Yes     |

| PE15  | D12   | D12            | DA12                  | D12         | Yes     |

| PD8   | D13   | D13            | DA13                  | D13         | Yes     |

| PD9   | D14   | D14            | DA14                  | D14         | Yes     |

| PD10  | D15   | D15            | DA15                  | D15         | Yes     |

| PD11  | -     | A16            | A16                   | CLE         | Yes     |

| PD12  | -     | A17            | A17                   | ALE         | Yes     |

|       | 1     |                |                       |             | 1       |

Table 9. FSMC pin definition (continued)

|        |      | AF0               | AF1       | AF2      | AF3          | AF4            | AF5                  | AF6                  | AF7        | AF8                | AF9                       | AF10           | AF11                                 | AF12                 | AF13       |       |          |

|--------|------|-------------------|-----------|----------|--------------|----------------|----------------------|----------------------|------------|--------------------|---------------------------|----------------|--------------------------------------|----------------------|------------|-------|----------|

|        | Port | SYS               | TIM1/2    | TIM3/4/5 | TIM8/9/10/11 | I2C1/I2C2/I2C3 | SPI1/SPI2/I2S2       | SPI3/I2S3            | USART1/2/3 | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 | OTG_FS/ OTG_HS | ETH                                  | FSMC/SDIO/<br>OTG_HS | DCMI       | AF014 | AF15     |

|        | PB0  | -                 | TIM1_CH2N | TIM3_CH3 | TIM8_CH2N    | -              | -                    | -                    | -          | -                  | -                         | OTG_HS_ULPI_D1 | ETH_MII_RXD2                         | -                    | -          | -     | EVENTOUT |

|        | PB1  | -                 | TIM1_CH3N | TIM3_CH4 | TIM8_CH3N    | -              | -                    | -                    | -          | -                  | -                         | OTG_HS_ULPI_D2 | ETH_MII_RXD3                         | -                    | -          | -     | EVENTOUT |

|        | PB2  | -                 | -         | -        | -            | -              | -                    | -                    | -          | -                  | -                         | -              | -                                    | -                    | -          | -     | EVENTOUT |

|        | PB3  | JTDO/<br>TRACESWO | TIM2_CH2  | -        | -            | -              | SPI1_SCK             | SPI3_SCK<br>I2S3_SCK | -          | -                  | -                         | -              | -                                    | -                    | -          | -     | EVENTOUT |

|        | PB4  | JTRST             | -         | TIM3_CH1 | -            | -              | SPI1_MISO            | SPI3_MISO            | -          | -                  | -                         | -              | -                                    | -                    | -          | -     | EVENTOUT |

|        | PB5  | -                 | -         | TIM3_CH2 | -            | I2C1_SMBA      | SPI1_MOSI            | SPI3_MOSI<br>I2S3_SD | -          | -                  | CAN2_RX                   | OTG_HS_ULPI_D7 | ETH _PPS_OUT                         | -                    | DCMI_D10   | -     | EVENTOUT |

|        | PB6  | -                 | -         | TIM4_CH1 | -            | I2C1_SCL       | -                    | -                    | USART1_TX  | -                  | CAN2_TX                   | -              | -                                    | -                    | DCMI_D5    | -     | EVENTOUT |

|        | PB7  | -                 | -         | TIM4_CH2 | -            | I2C1_SDA       | -                    | -                    | USART1_RX  | -                  | -                         | -              | -                                    | FSMC_NL              | DCMI_VSYNC | -     | EVENTOUT |

| Port B | PB8  | -                 | -         | TIM4_CH3 | TIM10_CH1    | I2C1_SCL       | -                    | -                    | -          | -                  | CAN1_RX                   | -              | ETH _MII_TXD3                        | SDIO_D4              | DCMI_D6    | -     | EVENTOUT |

|        | PB9  | -                 | -         | TIM4_CH4 | TIM11_CH1    | I2C1_SDA       | SPI2_NSS<br>I2S2_WS  | -                    | -          | -                  | CAN1_TX                   | -              | -                                    | SDIO_D5              | DCMI_D7    | -     | EVENTOUT |

|        | PB10 | -                 | TIM2_CH3  | -        | -            | I2C2_SCL       | SPI2_SCK<br>I2S2_SCK | -                    | USART3_TX  | -                  | -                         | OTG_HS_ULPI_D3 | ETH_MII_RX_ER                        | -                    | -          | -     | EVENTOUT |

|        | PB11 | -                 | TIM2_CH4  | -        | -            | I2C2_SDA       | -                    | -                    | USART3_RX  | -                  | -                         | OTG_HS_ULPI_D4 | ETH _MII_TX_EN<br>ETH<br>_RMII_TX_EN | -                    | -          | -     | EVENTOUT |

|        | PB12 | -                 | TIM1_BKIN | ÷        | -            | I2C2_SMBA      | SPI2_NSS<br>I2S2_WS  | -                    | USART3_CK  | -                  | CAN2_RX                   | OTG_HS_ULPI_D5 | ETH_MII_TXD0<br>ETH_RMII_TXD0        | OTG_HS_ID            | -          | -     | EVENTOUT |

|        | PB13 | -                 | TIM1_CH1N | -        | -            | -              | SPI2_SCK<br>I2S2_SCK | -                    | USART3_CTS | -                  | CAN2_TX                   | OTG_HS_ULPI_D6 | ETH_MII_TXD1<br>ETH_RMII_TXD1        | -                    | -          | -     | EVENTOUT |

|        | PB14 | -                 | TIM1_CH2N | -        | TIM8_CH2N    | -              | SPI2_MISO            | -                    | USART3_RTS | -                  | TIM12_CH1                 | -              | -                                    | OTG_HS_DM            | -          | -     | EVENTOUT |

|        | PB15 | RTC_50Hz          | TIM1_CH3N | -        | TIM8_CH3N    | -              | SPI2_MOSI<br>I2S2_SD | -                    | -          | -                  | TIM12_CH2                 | -              | -                                    | OTG_HS_DP            | -          | -     | EVENTOUT |

# Table 10. Alternate function mapping (continued)

DocID15818 Rev 13

577

|                 |                                 |                                                                           |                   | Тур                       | Ma                        | x <sup>(1)</sup>           |      |

|-----------------|---------------------------------|---------------------------------------------------------------------------|-------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter                       | Conditions                                                                | f <sub>HCLK</sub> | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                                 |                                                                           | 120 MHz           | 38                        | 51                        | 61                         |      |

|                 |                                 |                                                                           | 90 MHz            | 30                        | 43                        | 53                         |      |

|                 |                                 |                                                                           | 60 MHz            | 20                        | 33                        | 43                         |      |

|                 |                                 | <b>-</b> (2)                                                              | 30 MHz            | 11                        | 25                        | 35                         |      |

|                 |                                 | External clock <sup>(2)</sup> ,<br>all peripherals enabled <sup>(3)</sup> | 25 MHz            | 8                         | 21                        | 31                         |      |

|                 | Supply current in<br>Sleep mode |                                                                           | 16 MHz            | 6                         | 19                        | 29                         |      |

|                 |                                 |                                                                           | 8 MHz             | 3.6                       | 17.0                      | 27.0                       | mA   |

|                 |                                 |                                                                           | 4 MHz             | 2.4                       | 15.4                      | 25.3                       |      |

|                 |                                 |                                                                           | 2 MHz             | 1.9                       | 14.9                      | 24.7                       |      |

| I <sub>DD</sub> |                                 |                                                                           | 120 MHz           | 8                         | 21                        | 31                         | mA   |

|                 |                                 |                                                                           | 90 MHz            | 7                         | 20                        | 30                         | -    |

|                 |                                 |                                                                           | 60 MHz            | 5                         | 18                        | 28                         |      |

|                 |                                 |                                                                           | 30 MHz            | 3.5                       | 16.0                      | 26.0                       |      |

|                 |                                 | External clock <sup>(2)</sup> , all peripherals disabled                  | 25 MHz            | 2.5                       | 16.0                      | 25.0                       | -    |

|                 |                                 |                                                                           | 16 MHz            | 2.1                       | 15.1                      | 25.0                       |      |

|                 |                                 |                                                                           | 8 MHz             | 1.7                       | 15.0                      | 25.0                       |      |

|                 |                                 |                                                                           | 4 MHz             | 1.5                       | 14.6                      | 24.6                       |      |

|                 |                                 |                                                                           | 2 MHz             | 1.4                       | 14.2                      | 24.3                       |      |

| Table 22. Typical and maximum current | consumption in Sleep mode |

|---------------------------------------|---------------------------|

|---------------------------------------|---------------------------|

1. Guaranteed by characterization results, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 4 MHz and PLL is on when  $\rm f_{HCLK}$  > 25 MHz.

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

| Symbol                              | Parameter                   | Conditions                    |     | Тур  | Max | Unit |  |  |  |  |  |  |

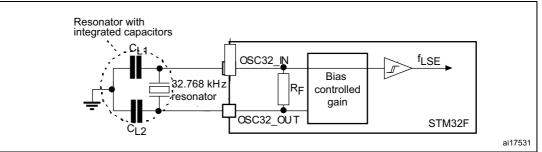

|-------------------------------------|-----------------------------|-------------------------------|-----|------|-----|------|--|--|--|--|--|--|

| R <sub>F</sub>                      | Feedback resistor           | -                             | -   | 18.4 | -   | MΩ   |  |  |  |  |  |  |

| I <sub>DD</sub>                     | LSE current consumption     | -                             | -   | -    | 1   | μA   |  |  |  |  |  |  |

| 9 <sub>m</sub>                      | Oscillator Transconductance | -                             | 2.8 | -    | -   | µA/V |  |  |  |  |  |  |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                | V <sub>DD</sub> is stabilized | -   | 2    | -   | s    |  |  |  |  |  |  |

Table 31. LSE oscillator characteristics ( $f_{LSE} = 32.768 \text{ kHz}$ )<sup>(1)</sup>

1. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

Note: For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 33. Typical application with a 32.768 kHz crystal

# 6.3.9 Internal clock source characteristics

The parameters given in *Table 32* and *Table 33* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

# High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                             | Conditions                           | Min | Тур | Max | Unit |

|-------------------------------------|---------------------------------------|--------------------------------------|-----|-----|-----|------|

| f <sub>HSI</sub>                    | Frequency                             | -                                    | -   | 16  | -   | MHz  |

|                                     | HSI user-trimming step <sup>(2)</sup> | -                                    | -   | -   | 1   | %    |

| ACC <sub>HSI</sub>                  | Accuracy of the<br>HSI oscillator     | $T_A = -40$ to 105 °C <sup>(3)</sup> | - 8 | -   | 4.5 | %    |

|                                     |                                       | $T_A = -10$ to 85 °C <sup>(3)</sup>  | - 4 | -   | 4   | %    |

|                                     |                                       | $T_A = 25 \ ^{\circ}C^{(4)}$         | – 1 | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                    | -   | 2.2 | 4.0 | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power consumption      | -                                    | -   | 60  | 80  | μA   |

Table 32. HSI oscillator characteristics <sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design, not tested in production.

- 3. Guaranteed by characterization results.

- 4. Factory calibrated, parts not soldered.

| Symbol                               | Parameter                                    | Conditions                               | Conditions         |              | Тур          | Max          | Unit |

|--------------------------------------|----------------------------------------------|------------------------------------------|--------------------|--------------|--------------|--------------|------|

|                                      |                                              |                                          | RMS                | -            | 25           | -            |      |

|                                      | Cycle-to-cycle jitter                        | System clock                             | peak<br>to<br>peak | -            | ±150         | -            |      |

|                                      |                                              | 120 MHz                                  | RMS                | -            | 15           | -            |      |

| Jitter <sup>(3)</sup>                | Period Jitter                                |                                          | peak<br>to<br>peak | -            | <u>+200</u>  | -            | ps   |

|                                      | Main clock output (MCO) for<br>RMII Ethernet | Cycle to cycle at 5<br>on 1000 samples   | -                  | 32           | -            |              |      |

|                                      | Main clock output (MCO) for MII<br>Ethernet  | Cycle to cycle at 25 MHz on 1000 samples |                    | -            | 40           | -            |      |

|                                      | Bit Time CAN jitter                          | Cycle to cycle at 1 MHz on 1000 samples  |                    | -            | 330          | -            |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD                 | VCO freq = 192 MHz<br>VCO freq = 432 MHz |                    | 0.15<br>0.45 | -            | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA                | VCO freq = 192 M<br>VCO freq = 432 M     | 0.30<br>0.55       | -            | 0.40<br>0.85 | mA           |      |

| Table 34. | Main PLL | characteristics | (continued) |

|-----------|----------|-----------------|-------------|

|-----------|----------|-----------------|-------------|

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design, not tested in production.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization results, not tested in production.

# Table 35. PLLI2S (audio PLL) characteristics

| Symbol                  | Parameter                         | Conditions         | Min                 | Тур | Мах                 | Unit |

|-------------------------|-----------------------------------|--------------------|---------------------|-----|---------------------|------|

| f <sub>PLLI2S_IN</sub>  | PLLI2S input clock <sup>(1)</sup> | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 <sup>(2)</sup> | MHz  |

| f <sub>PLLI2S_OUT</sub> | PLLI2S multiplier output clock    | -                  | -                   | -   | 216                 | MHz  |

| f <sub>VCO_OUT</sub>    | PLLI2S VCO output                 | -                  | 192                 | -   | 432                 | MHz  |

| t <sub>LOCK</sub>       | PLLI2S lock time                  | VCO freq = 192 MHz | 75                  | -   | 200                 |      |

|                         |                                   | VCO freq = 432 MHz | 100                 | -   | 300                 | μs   |

| Symbol                            | Parameter                                                                     | Conditions                                                 | Min                  | Max | Unit |

|-----------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | CMOS ports<br>I <sub>IO</sub> = +8 mA                      | -                    | 0.4 | v    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time | $1_{O} - 70 \text{ mA}$<br>2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -0.4 | -   | v    |

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | TTL ports<br>I <sub>IO</sub> =+ 8mA                        | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time | $2.7 V < V_{DD} < 3.6 V$                                   | 2.4                  | -   | v    |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | l <sub>IO</sub> = +20 mA                                   | -                    | 1.3 | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2.7 V < V <sub>DD</sub> < 3.6 V                            | V <sub>DD</sub> -1.3 | -   | v    |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +6 mA                                    | -                    | 0.4 | V    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2 V < V <sub>DD</sub> < 2.7 V                              | V <sub>DD</sub> -0.4 | -   |      |

PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. to drive an LED).

- 2. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

- 3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 12 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

- 4. Guaranteed by characterization results, not tested in production.

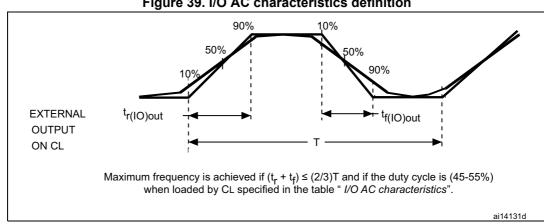

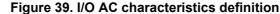

# Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 39* and *Table 48*, respectively.

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                                   | Parameter                                                                       | Conditions                                                  | Min | Тур | Max | Unit |

|-----------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|-----|------|

|                                               | f <sub>max(IO)out</sub> Maximum frequency <sup>(2)</sup> | $C_L$ = 50 pF, $V_{DD}$ > 2.70 V                                                | -                                                           | -   | 4   |     |      |

|                                               |                                                          | Maximum frequency <sup>(2)</sup>                                                | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 2   | MHz  |

|                                               |                                                          |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 8   |      |

| 00                                            |                                                          |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 4   |      |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub>         | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.8 V to<br>3.6 V | -   | -   | 100 | ns   |

| Table 4 | 48. | I/O | AC | characteristics <sup>(1)</sup> |

|---------|-----|-----|----|--------------------------------|

|---------|-----|-----|----|--------------------------------|

#### 6.3.17 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see Table 49).

Unless otherwise specified, the parameters given in Table 49 are derived from tests performed under the ambient temperature and  $V_{\text{DD}}$  supply voltage conditions summarized in Table 14.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       | -                       | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

#### Table 49. NRST pin characteristics

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series 1. resistance must be minimum (~10% order).

2. Guaranteed by design, not tested in production.

# Figure 40. Recommended NRST pin protection

- The reset network protects the device against parasitic resets. 1.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in 2. Table 49. Otherwise the reset is not taken into account by the device.

|                           | ge                                             | (00110110 |     |      |

|---------------------------|------------------------------------------------|-----------|-----|------|

| Symbol                    | Parameter                                      | Min       | Мах | Unit |

| t <sub>su(ADV-CLKH)</sub> | FSMC_A/D[15:0] valid data before FSMC_CLK high | 5         | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>  | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0         | -   | ns   |

# Table 76. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

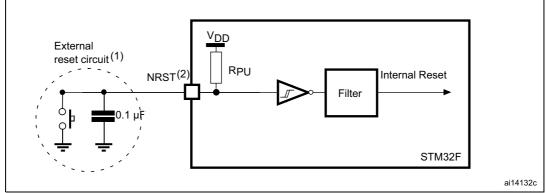

#### Figure 62. Synchronous multiplexed PSRAM write timings

Table 77. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                     | Parameter                                | Min                    | Max | Unit |

|----------------------------|------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                          | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)      | -                      | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)    | 2                      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low            | -                      | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high           | 3                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)   | -                      | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625) | 7                      | _   | ns   |

DocID15818 Rev 13

| Symbol                       | Parameter                                 | Min                      | Мах                      | Unit |

|------------------------------|-------------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NIOWR)</sub>        | FSMC_NIOWR low width                      | 8T <sub>HCLK</sub> - 0.5 | -                        | ns   |

| t <sub>v(NIOWR-D)</sub>      | FSMC_NIOWR low to FSMC_D[15:0] valid      | -                        | 5T <sub>HCLK</sub> - 1   | ns   |

| t <sub>h(NIOWR-D)</sub>      | FSMC_NIOWR high to FSMC_D[15:0] invalid   | 8T <sub>HCLK</sub> - 3   | -                        | ns   |

| t <sub>d(NCE4_1-NIOWR)</sub> | FSMC_NCE4_1 low to FSMC_NIOWR valid       | -                        | 5T <sub>HCLK</sub> + 1.5 | ns   |

| t <sub>h(NCEx-NIOWR)</sub>   | FSMC_NCEx high to FSMC_NIOWR invalid      | 5T <sub>HCLK</sub>       | -                        | ns   |

| t <sub>d(NIORD-NCEx)</sub>   | FSMC_NCEx low to FSMC_NIORD valid         | -                        | 5T <sub>HCLK</sub> + 1   | ns   |

| t <sub>h(NCEx-NIORD)</sub>   | FSMC_NCEx high to FSMC_NIORD) valid       | 5T <sub>HCLK</sub> – 0.5 | -                        | ns   |

| t <sub>w(NIORD)</sub>        | FSMC_NIORD low width                      | 8T <sub>HCLK</sub> + 1   | -                        | ns   |

| t <sub>su(D-NIORD)</sub>     | FSMC_D[15:0] valid before FSMC_NIORD high | 9.5                      | -                        | ns   |

| t <sub>d(NIORD-D)</sub>      | FSMC_D[15:0] valid after FSMC_NIORD high  | 0                        | -                        | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

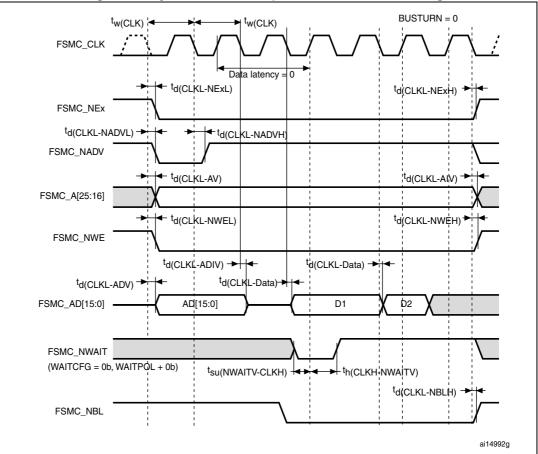

# NAND controller waveforms and timings

*Figure 71* through *Figure 74* represent synchronous waveforms, together with *Table 82* and *Table 83* provides the corresponding timings. The results shown in this table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x01;

- COM.FSMC\_WaitSetupTime = 0x03;

- COM.FSMC\_HoldSetupTime = 0x02;

- COM.FSMC\_HiZSetupTime = 0x01;

- ATT.FSMC SetupTime = 0x01;

- ATT.FSMC\_WaitSetupTime = 0x03;

- ATT.FSMC\_HoldSetupTime = 0x02;

- ATT.FSMC\_HiZSetupTime = 0x01;

- Bank = FSMC\_Bank\_NAND;

- MemoryDataWidth = FSMC\_MemoryDataWidth\_16b;

- ECC = FSMC\_ECC\_Enable;

- ECCPageSize = FSMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

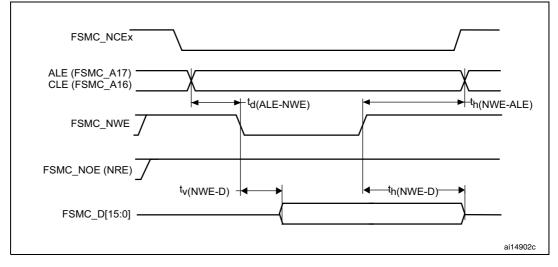

Figure 71. NAND controller waveforms for read access

Figure 72. NAND controller waveforms for write access

| Symbol                  | Parameter                               | Min                    | Мах                    | Unit |

|-------------------------|-----------------------------------------|------------------------|------------------------|------|

| t <sub>w(NWE)</sub>     | FSMC_NWE low width                      | 4T <sub>HCLK</sub> - 1 | 4T <sub>HCLK</sub> + 3 | ns   |

| t <sub>v(NWE-D)</sub>   | FSMC_NWE low to FSMC_D[15-0] valid      | -                      | 0                      | ns   |

| t <sub>h(NWE-D)</sub>   | FSMC_NWE high to FSMC_D[15-0] invalid   | 3T <sub>HCLK</sub>     | -                      | ns   |

| t <sub>d(D-NWE)</sub>   | FSMC_D[15-0] valid before FSMC_NWE high | 5T <sub>HCLK</sub>     | -                      | ns   |

| t <sub>d(ALE-NWE)</sub> | FSMC_ALE valid before FSMC_NWE low      | -                      | 3T <sub>HCLK</sub> + 2 | ns   |

| t <sub>h(NWE-ALE)</sub> | FSMC_NWE high to FSMC_ALE invalid       | 3T <sub>HCLK</sub> - 2 | -                      | ns   |

Table 83. Switching characteristics for NAND Flash write cycles<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

# 6.3.26 Camera interface (DCMI) timing specifications

| Symbol | Parameter                                     | Conditions          | Min | Мах |

|--------|-----------------------------------------------|---------------------|-----|-----|

| -      | Frequency ratio DCMI_PIXCLK/f <sub>HCLK</sub> | DCMI_PIXCLK= 48 MHz | -   | 0.4 |

# 6.3.27 SD/SDIO MMC card host interface (SDIO) characteristics

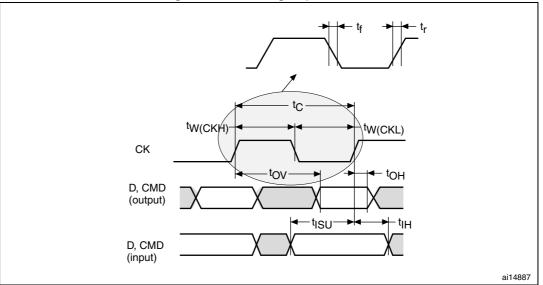

Unless otherwise specified, the parameters given in *Table 85* are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (D[7:0], CMD, CK).

Figure 75. SDIO high-speed mode

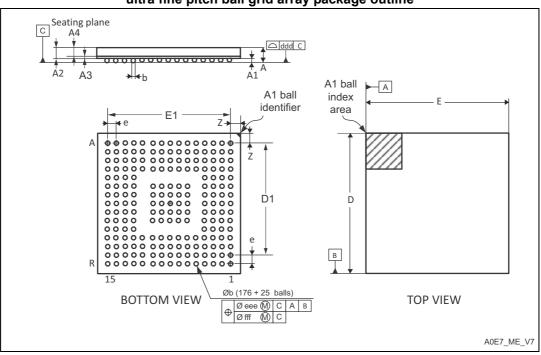

# 7.6 UFBGA176+25 package information

Figure 89. UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

# Table 93. UFBGA176+25, - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package mechanical data

| Cumhal | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

| Symbol | Min.        | Тур.   | Max.   | Min.                  | Тур.   | Max.   |

| Α      | -           | -      | 0.600  | -                     | -      | 0.0236 |

| A1     | -           | -      | 0.110  | -                     | -      | 0.0043 |

| A2     | -           | 0.450  | -      | -                     | 0.0177 | -      |

| A3     | -           | 0.130  | -      | -                     | 0.0051 | 0.0094 |

| A4     | -           | 0.320  | -      | -                     | 0.0126 | -      |

| b      | 0.240       | 0.290  | 0.340  | 0.0094                | 0.0114 | 0.0134 |

| D      | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |

| D1     | -           | 9.100  | -      | -                     | 0.3583 | -      |

| E      | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |

| E1     | -           | 9.100  | -      | -                     | 0.3583 | -      |

| е      | -           | 0.650  | -      | -                     | 0.0256 | -      |

| Z      | -           | 0.450  | -      | -                     | 0.0177 | -      |

| ddd    | -           | -      | 0.080  | -                     | -      | 0.0031 |

| Data                                       |

|--------------------------------------------|

| Date R                                     |

| Date       R         13-Jul-2010       (cc |