#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 120MHz                                                                |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT     |

| Number of I/O              | 114                                                                   |

| Program Memory Size        | 768KB (768K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 132K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                           |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 144-LQFP                                                              |

| Supplier Device Package    | 144-LQFP (20x20)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205zft6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 84. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline      | 158 |

|------------|--------------------------------------------------------------------------|-----|

| Figure 85. | LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package               |     |

|            | recommended footprint                                                    | 160 |

| Figure 86. | LQFP144 marking (package top view)                                       | 161 |

|            | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline      |     |

| Figure 88. | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package              |     |

| U          | recommended footprint                                                    | 164 |

| Figure 89. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch,                       |     |

| U          | ultra fine pitch ball grid array package outline                         | 165 |

| Figure 90. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball |     |

| U          | grid array package recommended footprint                                 | 166 |

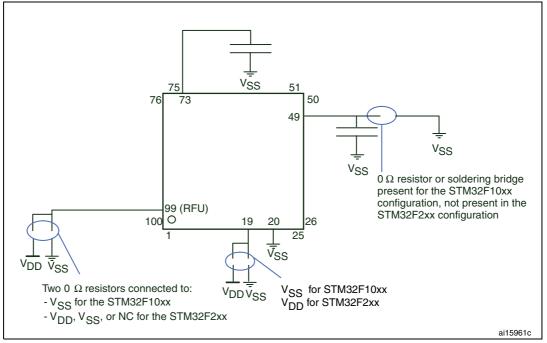

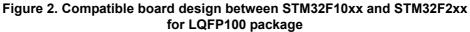

Figure 3. Compatible board design between STM32F10xx and STM32F2xx for LQFP144 package

1. RFU = reserved for future use.

DocID15818 Rev 13

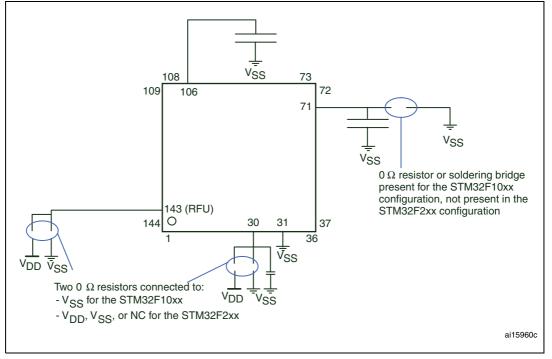

Figure 6. Regulator OFF/internal reset ON

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach 1.08 V is faster than the time for  $V_{DD}$  to reach 1.8 V, then PA0 should be kept low to cover both conditions: until  $V_{CAP_1}$  and  $V_{CAP_2}$  reach 1.08 V and until  $V_{DD}$  reaches 1.8 V (see *Figure 8*).

- Otherwise, If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach 1.08 V is slower than the time for V<sub>DD</sub> to reach 1.8 V, then PA0 should be asserted low externally (see *Figure 9*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below 1.08 V and V<sub>DD</sub> is higher than 1.8 V, then a reset must be asserted on PA0 pin.

#### **Regulator OFF/internal reset OFF**

On WLCSP64+2 package, this mode activated by connecting REGOFF to V<sub>SS</sub> and IRROFF to V<sub>DD</sub>. IRROFF cannot be activated in conjunction with REGOFF. This mode is available only on the WLCSP64+2 package. It allows to supply externally a 1.2 V voltage source through V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> pins. In this mode, the integrated power-on reset (POR)/ power-down reset (PDR) circuitry is disabled.

An external power supply supervisor should monitor both the external 1.2 V and the external  $V_{DD}$  supply voltage, and should maintain the device in reset mode as long as they remain below a specified threshold. The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.8 V. This supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range. A comprehensive set of power-saving modes allows to design low-power applications.

## 3.20.4 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

## 3.20.5 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

## 3.20.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source

## 3.21 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to three I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support the Standard- and Fast-modes. They support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

# 3.22 Universal synchronous/asynchronous receiver transmitters (UARTs/USARTs)

The STM32F20x devices embed four universal synchronous/asynchronous receiver transmitters (USART1, USART2, USART3 and USART6) and two universal asynchronous receiver transmitters (UART4 and UART5).

These six interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to communicate at speeds of up to 7.5 Mbit/s. The other available interfaces communicate at up to 3.75 Mbit/s.

USART1, USART2, USART3 and USART6 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

DocID15818 Rev 13

|        |           | Pi      | ns      |         |          |                                                      |                                              |               |      |                                                                                                                                                 |                         |  |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------------------------------------------|---------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type                                     | I/O structure | Note | Alternate functions                                                                                                                             | Additional<br>functions |  |

| -      | -         | -       | -       | 84      | N12      | PH7                                                  | I/O FT - I2C3_SCL, ETH_MII_RXD3,<br>EVENTOUT |               |      | -                                                                                                                                               |                         |  |

| -      | -         | -       | -       | 85      | M12      | PH8                                                  | I/O                                          | FT            | -    | I2C3_SDA, DCMI_HSYNC,<br>EVENTOUT                                                                                                               | -                       |  |

| -      | -         | -       | -       | 86      | M13      | PH9                                                  | I/O                                          | FT            | -    | I2C3_SMBA, TIM12_CH2,<br>DCMI_D0, EVENTOUT                                                                                                      | -                       |  |

| -      | -         | -       | -       | 87      | L13      | PH10                                                 | I/O                                          | FT            | -    | TIM5_CH1, DCMI_D1,<br>EVENTOUT                                                                                                                  | -                       |  |

| -      | -         | -       | -       | 88      | L12      | PH11                                                 | I/O                                          | FT            | -    | TIM5_CH2, DCMI_D2,<br>EVENTOUT                                                                                                                  | -                       |  |

| -      | -         | -       | -       | 89      | K12      | PH12                                                 | I/O                                          | FT            | -    | TIM5_CH3, DCMI_D3,<br>EVENTOUT                                                                                                                  | -                       |  |

| -      | -         | -       | -       | 90      | H12      | V <sub>SS</sub>                                      | S                                            | -             | -    | -                                                                                                                                               | -                       |  |

| -      | -         | -       | -       | 91      | J12      | V <sub>DD</sub>                                      | S                                            | -             | -    | -                                                                                                                                               | -                       |  |

| 33     | J1        | 51      | 73      | 92      | P12      | PB12                                                 | I/O                                          | FT            | -    | SPI2_NSS, I2S2_WS,<br>I2C2_SMBA, USART3_CK,<br>TIM1_BKIN, CAN2_RX,<br>OTG_HS_ULPI_D5,<br>ETH_RMII_TXD0,<br>ETH_MII_TXD0,<br>OTG_HS_ID, EVENTOUT | -                       |  |

| 34     | H2        | 52      | 74      | 93      | P13      | PB13                                                 | I/O                                          | FT            | -    | SPI2_SCK, I2S2_SCK,<br>USART3_CTS, TIM1_CH1N,<br>CAN2_TX,<br>OTG_HS_ULPI_D6,<br>ETH_RMII_TXD1,<br>ETH_MII_TXD1, EVENTOUT                        | OTG_HS_<br>VBUS         |  |

| 35     | H1        | 53      | 75      | 94      | R14      | PB14                                                 | I/O                                          | FT            | -    | SPI2_MISO, TIM1_CH2N,<br>TIM12_CH1, OTG_HS_DM<br>USART3_RTS, TIM8_CH2N,<br>EVENTOUT                                                             | -                       |  |

| 36     | G1        | 54      | 76      | 95      | R15      | PB15                                                 | I/O                                          | FT            | -    | SPI2_MOSI, I2S2_SD,<br>TIM1_CH3N, TIM8_CH3N,<br>TIM12_CH2, OTG_HS_DP,<br>RTC_50Hz, EVENTOUT                                                     | -                       |  |

| -      | -         | 55      | 77      | 96      | P15      | PD8                                                  | I/O                                          | FT            | -    | FSMC_D13, USART3_TX,<br>EVENTOUT                                                                                                                | -                       |  |

Table 8. STM32F20x pin and ball definitions (continued)

|        |           | Pi      | ns      |         |          |                                                      |          |               |      |                                                                      |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|----------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                  | Additional<br>functions |

| 54     | C7        | 83      | 116     | 144     | D12      | PD2                                                  | I/O      | FT            | -    | TIM3_ETR,UART5_RX,<br>SDIO_CMD, DCMI_D11,<br>EVENTOUT                | -                       |

| -      | -         | 84      | 117     | 145     | D11      | PD3                                                  | I/O      | FT            | -    | FSMC_CLK,USART2_CTS,<br>EVENTOUT                                     | -                       |

| -      | -         | 85      | 118     | 146     | D10      | PD4                                                  | I/O      | FT            | -    | FSMC_NOE, USART2_RTS,<br>EVENTOUT                                    | -                       |

| -      | -         | 86      | 119     | 147     | C11      | PD5                                                  | I/O      | FT            | -    | FSMC_NWE,USART2_TX,<br>EVENTOUT                                      | -                       |

| -      | -         | -       | 120     | 148     | D8       | V <sub>SS</sub>                                      | S        | -             | -    | -                                                                    | -                       |

| -      | -         | -       | 121     | 149     | C8       | V <sub>DD</sub>                                      | S        | -             | -    | -                                                                    | -                       |

| -      | -         | 87      | 122     | 150     | B11      | PD6                                                  | I/O      | FT            | -    | FSMC_NWAIT,<br>USART2_RX, EVENTOUT                                   | -                       |

| -      | -         | 88      | 123     | 151     | A11      | PD7                                                  | I/O      | FT            | -    | USART2_CK,FSMC_NE1,<br>FSMC_NCE2, EVENTOUT                           | -                       |

| -      | -         | -       | 124     | 152     | C10      | PG9                                                  | I/O      | FT            | -    | USART6_RX,<br>FSMC_NE2,FSMC_NCE3,<br>EVENTOUT                        | -                       |

| -      | -         | -       | 125     | 153     | B10      | PG10                                                 | I/O      | FT            | -    | FSMC_NCE4_1,<br>FSMC_NE3, EVENTOUT                                   | -                       |

| -      | -         | -       | 126     | 154     | В9       | PG11                                                 | I/O      | FT            | -    | FSMC_NCE4_2,<br>ETH_MII_TX_EN ,<br>ETH_RMII_TX_EN,<br>EVENTOUT       | -                       |

| -      | -         | -       | 127     | 155     | B8       | PG12                                                 | I/O      | FT            | -    | FSMC_NE4, USART6_RTS,<br>EVENTOUT                                    | -                       |

| -      | -         | -       | 128     | 156     | A8       | PG13                                                 | I/O      | FT            | -    | FSMC_A24, USART6_CTS,<br>ETH_MII_TXD0,<br>ETH_RMII_TXD0,<br>EVENTOUT | -                       |

| -      | -         | -       | 129     | 157     | A7       | PG14                                                 | I/O      | FT            | -    | FSMC_A25, USART6_TX,<br>ETH_MII_TXD1,<br>ETH_RMII_TXD1,<br>EVENTOUT  | -                       |

| -      | -         | -       | 130     | 158     | D7       | V <sub>SS</sub>                                      | S        | -             | -    | -                                                                    | -                       |

Table 8. STM32F20x pin and ball definitions (continued)

60/182

DocID15818 Rev 13

|        |          |                |                        |           |              | Та             | able 10. /     | Alternat            | te function | on map             | ping                      |                    |                                            |                      |            |       |          |

|--------|----------|----------------|------------------------|-----------|--------------|----------------|----------------|---------------------|-------------|--------------------|---------------------------|--------------------|--------------------------------------------|----------------------|------------|-------|----------|

|        |          | AF0            | AF1                    | AF2       | AF3          | AF4            | AF5            | AF6                 | AF7         | AF8                | AF9                       | AF10               | AF11                                       | AF12                 | AF13       |       |          |

|        | Port     | SYS            | TIM1/2                 | TIM3/4/5  | TIM8/9/10/11 | 12C1/12C2/12C3 | SPI1/SPI2/I2S2 | SPI3/I2S3           | USART1/2/3  | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 | OTG_FS/ OTG_HS     | ЕТН                                        | FSMC/SDIO/<br>OTG_HS | DCMI       | AF014 | AF15     |

|        | PA0-WKUP | -              | TIM2_CH1_ETR           | TIM 5_CH1 | TIM8_ETR     | -              | -              |                     | USART2_CTS  | UART4_TX           | -                         | -                  | ETH_MII_CRS                                | -                    | -          | -     | EVENTOUT |

|        | PA1      | -              | TIM2_CH2               | TIM5_CH2  | -            | -              | -              |                     | USART2_RTS  | UART4_RX           | -                         | -                  | ETH_MII<br>_RX_CLK<br>ETH_RMII<br>_REF_CLK | -                    | -          | -     | EVENTOUT |

|        | PA2      | -              | TIM2_CH3               | TIM5_CH3  | TIM9_CH1     | -              | -              |                     | USART2_TX   | -                  | -                         | -                  | ETH_MDIO                                   | -                    | -          | -     | EVENTOUT |

|        | PA3      | -              | TIM2_CH4               | TIM5_CH4  | TIM9_CH2     | -              | -              |                     | USART2_RX   | -                  | -                         | OTG_HS_ULPI_D0     | ETH _MII_COL                               | -                    | -          | -     | EVENTOUT |

|        | PA4      | -              | -                      | -         | -            | -              | SPI1_NSS       | SPI3_NSS<br>I2S3_WS | USART2_CK   | -                  | -                         |                    | -                                          | OTG_HS_SOF           | DCMI_HSYNC | -     | EVENTOUT |

|        | PA5      | -              | TIM2_CH1_ETR           | -         | TIM8_CH1N    | -              | SPI1_SCK       | -                   | -           | -                  | -                         | OTG_HS_ULPI_C<br>K | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA6      | -              | TIM1_BKIN              | TIM3_CH1  | TIM8_BKIN    | -              | SPI1_MISO      | -                   | -           | -                  | TIM13_CH1                 | -                  | -                                          | -                    | DCMI_PIXCK | -     | EVENTOUT |

| Port A | PA7      | -              | TIM1_CH1N              | TIM3_CH2  | TIM8_CH1N    | -              | SPI1_MOSI      | -                   | -           | -                  | TIM14_CH1                 | -                  | ETH_MII_RX_DV<br>ETH_RMII<br>_CRS_DV       | -                    | -          | -     | EVENTOUT |

|        | PA8      | MCO1           | TIM1_CH1               | -         | -            | I2C3_SCL       | -              | -                   | USART1_CK   | -                  | -                         | OTG_FS_SOF         | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA9      | -              | TIM1_CH2               | -         | -            | I2C3_SMBA      | -              | -                   | USART1_TX   | -                  | -                         |                    | -                                          | -                    | DCMI_D0    | -     | EVENTOUT |

|        | PA10     | -              | TIM1_CH3               | -         | -            | -              | -              | -                   | USART1_RX   | -                  | -                         | OTG_FS_ID          | -                                          | -                    | DCMI_D1    | -     | EVENTOUT |

|        | PA11     | -              | TIM1_CH4               | -         | -            | -              | -              | -                   | USART1_CTS  | -                  | CAN1_RX                   | OTG_FS_DM          | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA12     | -              | TIM1_ETR               | -         | -            | -              | -              | -                   | USART1_RTS  | -                  | CAN1_TX                   | OTG_FS_DP          | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA13     | JTMS-<br>SWDIO | -                      | -         | -            | -              | -              | -                   | -           | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA14     | JTCK-<br>SWCLK | -                      | -         | -            | -              | -              | -                   | -           | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA15     | JTDI           | TIM 2_CH1<br>TIM 2_ETR | -         | -            | -              | SPI1_NSS       | SPI3_NSS<br>I2S3_WS | -           | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

5

## 6.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for  $T_A$ .

| Symbol           | Parameter                      | Min | Max | Unit  |

|------------------|--------------------------------|-----|-----|-------|

| 1                | V <sub>DD</sub> rise time rate | 20  | 8   | us/V  |

| <sup>L</sup> VDD | V <sub>DD</sub> fall time rate | 20  | 8   | μ3/ ν |

## Table 17. Operating conditions at power-up / power-down (regulator ON)

## 6.3.4 Operating conditions at power-up / power-down (regulator OFF)

Subject to general operating conditions for  $T_A$ .

| Table 18. Operating conditions at power-up   | / power-down (regulator OFF) |

|----------------------------------------------|------------------------------|

| Table 10. Operating conditions at power-up / | power-down (regulator or r)  |

| Symbol            | Parameter                                    | Conditions | Min | Max | Unit |

|-------------------|----------------------------------------------|------------|-----|-----|------|

| t <sub>VDD</sub>  | V <sub>DD</sub> rise time rate               | Power-up   | 20  | 8   |      |

|                   | V <sub>DD</sub> fall time rate               | Power-down | 20  | 8   |      |

| t                 | $V_{CAP\_1}$ and $V_{CAP\_2}$ rise time rate | Power-up   | 20  | ∞   | µs/V |

| t <sub>VCAP</sub> | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | ∞   |      |

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog inputs by firmware.

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 30 MHz, 1 wait state from 30 to 60 MHz, 2 wait states from 60 to 90 MHz and 3 wait states from 90 to 120 MHz).

- When the peripherals are enabled HCLK is the system clock, f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2, except is explicitly mentioned.

- The maximum values are obtained for  $V_{DD}$  = 3.6 V and maximum ambient temperature (T<sub>A</sub>), and the typical values for T<sub>A</sub>= 25 °C and V<sub>DD</sub> = 3.3 V unless otherwise specified.

## Table 20. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM <sup>(1)</sup>

| Symbol          | Parameter      | Conditions                                                             | f                     | Тур                    | Ма                     | x <sup>(2)</sup>        | Unit |

|-----------------|----------------|------------------------------------------------------------------------|-----------------------|------------------------|------------------------|-------------------------|------|

| Symbol          | Farameter      |                                                                        | f <sub>HCLK</sub>     | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | •    |

|                 |                |                                                                        | 120 MHz               | 49                     | 63                     | 72                      |      |

|                 |                |                                                                        | 90 MHz                | 38                     | 51                     | 61                      |      |

|                 |                |                                                                        | 60 MHz                | 26                     | 39                     | 49                      |      |

|                 |                | (3)                                                                    | 30 MHz                | 14                     | 27                     | 37                      |      |

|                 |                | External clock <sup>(3)</sup> , all peripherals enabled <sup>(4)</sup> | 25 MHz                | 11                     | 24                     | 34                      |      |

|                 |                |                                                                        | 16 MHz <sup>(5)</sup> | 8                      | 21                     | 30                      |      |

|                 | Supply current |                                                                        | 8 MHz                 | 5                      | 17                     | 27                      |      |

|                 |                |                                                                        | 4 MHz                 | 3                      | 16                     | 26                      |      |

| 1               |                |                                                                        | 2 MHz                 | 2                      | 15                     | 25                      | m۸   |

| I <sub>DD</sub> | in Run mode    |                                                                        | 120 MHz               | 21                     | 34                     | 44                      | mA   |

|                 |                |                                                                        | 90 MHz                | 17                     | 30                     | 40                      |      |

|                 |                |                                                                        | 60 MHz                | 12                     | 25                     | 35                      |      |

|                 |                | (3)                                                                    | 30 MHz                | 7                      | 20                     | 30                      |      |

|                 |                | External clock <sup>(3)</sup> , all peripherals disabled               | 25 MHz                | 5                      | 18                     | 28                      |      |

|                 |                |                                                                        | 16 MHz <sup>(5)</sup> | 4.0                    | 17.0                   | 27.0                    |      |

|                 |                |                                                                        | 8 MHz                 | 2.5                    | 15.5                   | 25.5                    |      |

|                 |                |                                                                        | 4 MHz                 | 2.0                    | 14.7                   | 24.8                    |      |

|                 |                |                                                                        | 2 MHz                 | 1.6                    | 14.5                   | 24.6                    |      |

1. Code and data processing running from SRAM1 using boot pins.

2. Guaranteed by characterization, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

3. External clock is 4 MHz and PLL is on when  $f_{HCLK}$  > 25 MHz.

4. When the ADC is on (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

5. In this case HCLK = system clock/2.

|        |                           |                                                      |                            | Тур                        |                            | Ма                     |         |    |

|--------|---------------------------|------------------------------------------------------|----------------------------|----------------------------|----------------------------|------------------------|---------|----|

| Symbol | Parameter                 | Conditions                                           | Т                          | A = 25 °C                  | 0                          | T <sub>A</sub> = 85 °C | Unit    |    |

|        |                           |                                                      | V <sub>DD</sub> =<br>1.8 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> =      | = 3.6 V |    |

|        | Supply current in Standby | Backup SRAM ON, low-speed<br>oscillator and RTC ON   | 3.0                        | 3.4                        | 4.0                        | 15.1                   | 25.8    |    |

|        |                           | Backup SRAM OFF, low-<br>speed oscillator and RTC ON | 2.4                        | 2.7                        | 3.3                        | 12.4                   | 20.5    | μA |

|        | mode                      | Backup SRAM ON, RTC OFF                              | 2.4                        | 2.6                        | 3.0                        | 12.5                   | 24.8    |    |

|        |                           | Backup SRAM OFF, RTC<br>OFF                          | 1.7                        | 1.9                        | 2.2                        | 9.8                    | 19.2    |    |

### Table 24. Typical and maximum current consumptions in Standby mode

1. Guaranteed by characterization results, not tested in production.

## Table 25. Typical and maximum current consumptions in $\mathrm{V}_{\mathrm{BAT}}$ mode

|                      |           |                                                     |                            | Тур                        |                            | Ма                     |                               |    |  |

|----------------------|-----------|-----------------------------------------------------|----------------------------|----------------------------|----------------------------|------------------------|-------------------------------|----|--|

| Symbol               | Parameter | Conditions                                          | Т                          | A = 25 °                   | С                          | T <sub>A</sub> = 85 °C | 85 °C T <sub>A</sub> = 105 °C |    |  |

|                      |           |                                                     | V <sub>DD</sub> =<br>1.8 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> =      | = 3.6 V                       |    |  |

|                      |           | Backup SRAM ON, low-speed<br>oscillator and RTC ON  | 1.29                       | 1.42                       | 1.68                       | 12                     | 19                            |    |  |

| I <sub>DD_VBAT</sub> |           | Backup SRAM OFF, low-speed<br>oscillator and RTC ON | 0.62                       | 0.73                       | 0.96                       | 8                      | 10                            | μA |  |

|                      |           | Backup SRAM ON, RTC OFF                             | 0.79                       | 0.81                       | 0.86                       | 9                      | 16                            |    |  |

|                      |           | Backup SRAM OFF, RTC OFF                            | 0.10                       | 0.10                       | 0.10                       | 5                      | 7                             |    |  |

1. Guaranteed by characterization results, not tested in production.

## 6.3.8 External clock source characteristics

### High-speed external user clock generated from an external source

The characteristics given in *Table 28* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                           | Conditions                       | Min                | Тур | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|--------------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                       | External user clock source frequency <sup>(1)</sup> |                                  | 1                  | -   | 26                 | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                  | 0.7V <sub>DD</sub> | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  | -                                | $V_{SS}$           | -   | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              |                                  | 5                  | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                  | -                  | -   | 20                 | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             | -                                | -                  | 5   | -                  | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                          | -                                | 45                 | -   | 55                 | %    |

| ١L                                         | OSC_IN Input leakage current                        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -   | ±1                 | μA   |

Table 28. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

### Low-speed external user clock generated from an external source

The characteristics given in *Table 29* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                           | Conditions                       | Min                 | Тур    | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|---------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source frequency <sup>(1)</sup> |                                  | -                   | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage               |                                  | $0.7 V_{\text{DD}}$ | -      | $V_{DD}$           | v    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                |                                  | $V_{SS}$            | -      | $0.3V_{\text{DD}}$ |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>            | -                                | 450                 | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>           |                                  | -                   | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>           | -                                | -                   | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                          | -                                | 30                  | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                      | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                   | -      | ±1                 | μA   |

| Table 29. Low-speed external user clock char | acteristics |

|----------------------------------------------|-------------|

|----------------------------------------------|-------------|

1. Guaranteed by design, not tested in production.

| Symbol          | Parameter      | Conditions                                           | Min | Тур | Max | Unit |

|-----------------|----------------|------------------------------------------------------|-----|-----|-----|------|

| I <sub>DD</sub> |                | Write / Erase 8-bit mode<br>V <sub>DD</sub> = 1.8 V  | -   | 5   | -   |      |

|                 | Supply current | Write / Erase 16-bit mode<br>V <sub>DD</sub> = 2.1 V | -   | 8   | -   | mA   |

|                 |                | Write / Erase 32-bit mode<br>V <sub>DD</sub> = 3.3 V |     | 12  | -   |      |

Table 37. Flash memory characteristics

### Table 38. Flash memory programming

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |  |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|--|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 |                    | 16   | 100 <sup>(2)</sup> | μs   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |  |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |  |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |  |

| t <sub>ERASE128KB</sub> | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | s    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 16   | 32                 |      |  |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 11   | 22                 | s    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 8    | 16                 |      |  |

|                         |                            | 32-bit program operation                         | 2.7                | -    | 3.6                | V    |  |

| V <sub>prog</sub>       | Programming voltage        | 16-bit program operation                         | 2.1                | -    | 3.6 V              |      |  |

|                         |                            | 8-bit program operation                          | 1.8                | -    | 3.6                | V    |  |

1. Guaranteed by characterization results, not tested in production.

2. The maximum programming time is measured after 100K erase operations.

### **USB OTG FS characteristics**

The USB OTG interface is USB-IF certified (Full-Speed). This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol                              | Parameter                           | Мах | Unit |  |  |  |  |  |

|-------------------------------------|-------------------------------------|-----|------|--|--|--|--|--|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |  |  |  |  |  |

Table 56. USB OTG FS startup time

1. Guaranteed by design, not tested in production.

| Sym             | bol                            | Parameter                                                 | Conditions                                                       | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup> | Unit |

|-----------------|--------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|---------------------|------|---------------------|------|

| V <sub>DD</sub> |                                | USB OTG FS operating<br>voltage                           |                                                                  | 3.0 <sup>(2)</sup>  | -    | 3.6                 | V    |

| Input           | V <sub>DI</sub> <sup>(3)</sup> | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                                 | 0.2                 | -    | -                   |      |

| levels          | V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range                            | Includes V <sub>DI</sub> range                                   | 0.8                 | -    | 2.5                 | V    |

|                 | $V_{SE}^{(3)}$                 | Single ended receiver threshold                           |                                                                  | 1.3                 | -    | 2.0                 |      |

| Output          | V <sub>OL</sub>                | Static output level low                                   | $\rm R_L$ of 1.5 k\Omega to 3.6 $\rm V^{(4)}$                    | -                   | -    | 0.3                 | V    |

| levels          | V <sub>OH</sub>                | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                 | -    | 3.6                 | v    |

| R <sub>P</sub>  |                                | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V <sub>IN</sub> = V <sub>DD</sub>                                | 17                  | 21   | 24                  |      |

|                 | D                              | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | VIN - VDD                                                        | 0.65                | 1.1  | 2.0                 | kΩ   |

| R <sub>PU</sub> |                                | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP)                      | V <sub>IN</sub> = V <sub>SS</sub>                                | 1.5                 | 1.8  | 2.1                 |      |

|                 |                                | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>                                | 0.25                | 0.37 | 0.55                |      |

### Table 57. USB OTG FS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The STM32F205xx and STM32F207xx USB OTG FS functionality is ensured down to 2.7 V but not the full USB OTG FS electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

3. Guaranteed by design, not tested in production.

4. R<sub>L</sub> is the load connected on the USB OTG FS drivers

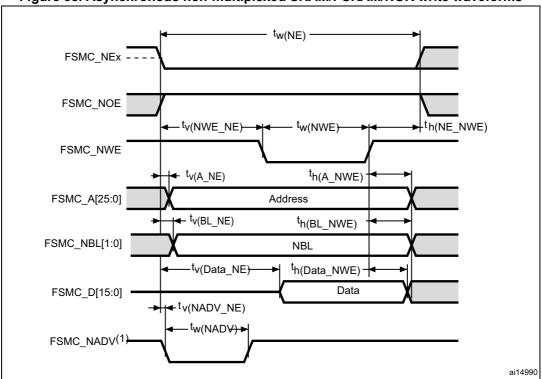

Figure 58. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

| Table 73. A | Asynchronous non-multiplexed SRAM | M/PSRAM/NO | R write timin | gs <sup>(1)(2)</sup> |

|-------------|-----------------------------------|------------|---------------|----------------------|

|             |                                   |            |               |                      |

| Symbol                   | Parameter                                | Min                     | Мах                     | Unit |

|--------------------------|------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>       | FSMC_NE low time                         | 3T <sub>HCLK</sub>      | 3T <sub>HCLK</sub> + 4  | ns   |

| t <sub>v(NWE_NE</sub> )  | FSMC_NEx low to FSMC_NWE low             | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>w(NWE)</sub>      | FSMC_NWE low time                        | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 3   | ns   |

| t <sub>h(NE_NWE)</sub>   | FSMC_NWE high to FSMC_NE high hold time  |                         |                         | ns   |

| t <sub>v(A_NE)</sub>     | FSMC_NEx low to FSMC_A valid             | -                       | 0                       | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FSMC_NWE high    | T <sub>HCLK</sub> - 3   | -                       | ns   |

| t <sub>v(BL_NE)</sub>    | FSMC_NEx low to FSMC_BL valid            | -                       | 0.5                     | ns   |

| t <sub>h(BL_NWE)</sub>   | FSMC_BL hold time after FSMC_NWE<br>high | T <sub>HCLK</sub> – 1   | -                       | ns   |

| t <sub>v(Data_NE)</sub>  | Data to FSMC_NEx low to Data valid       | -                       | T <sub>HCLK</sub> + 5   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FSMC_NWE high       | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(NADV_NE)</sub>  | FSMC_NEx low to FSMC_NADV low            | -                       | 2                       | ns   |

| t <sub>w(NADV)</sub>     | FSMC_NADV low time                       | -                       | T <sub>HCLK</sub> + 1.5 | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

| Symbol                         | Parameter                                  | Min         | Max | Unit |

|--------------------------------|--------------------------------------------|-------------|-----|------|

| t <sub>d(CLKL-</sub><br>NADVL) | FSMC_CLK low to FSMC_NADV low              | -           | 5   | ns   |

| t <sub>d(CLKL-</sub><br>NADVH) | FSMC_CLK low to FSMC_NADV high             | 6           | -   | ns   |

| t <sub>d(CLKL-AV)</sub>        | FSMC_CLK low to FSMC_Ax valid (x=1625)     | -           | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>       | FSMC_CLK low to FSMC_Ax invalid (x=1625)   | 8           | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>      | FSMC_CLK low to FSMC_NWE low               | -           | 1   | ns   |

| t <sub>d(CLKL-NWEH)</sub>      | (FSMC_CLK low to FSMC_NWE high 1           |             | -   | ns   |

| t <sub>d(CLKL-Data)</sub>      | FSMC_D[15:0] valid data after FSMC_CLK low | CLK low - 2 |     | ns   |

| t <sub>d(CLKL-NBLH)</sub>      | FSMC_CLK low to FSMC_NBL high              | 2           | -   | ns   |

Table 79. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

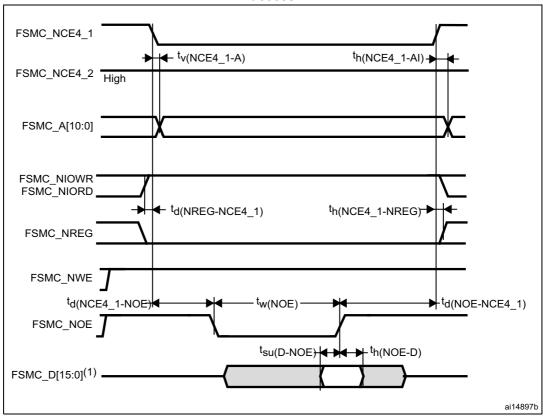

## PC Card/CompactFlash controller waveforms and timings

*Figure 65* through *Figure 70* represent synchronous waveforms, with *Table 80* and *Table 81* providing the corresponding timings. The results shown in these table are obtained with the following FSMC configuration:

- COM.FSMC\_SetupTime = 0x04;

- COM.FSMC\_WaitSetupTime = 0x07;

- COM.FSMC\_HoldSetupTime = 0x04;

- COM.FSMC\_HiZSetupTime = 0x00;

- ATT.FSMC\_SetupTime = 0x04;

- ATT.FSMC\_WaitSetupTime = 0x07;

- ATT.FSMC HoldSetupTime = 0x04;

- ATT.FSMC\_HiZSetupTime = 0x00;

- IO.FSMC\_SetupTime = 0x04;

- IO.FSMC\_WaitSetupTime = 0x07;

- IO.FSMC HoldSetupTime = 0x04;

- IO.FSMC HiZSetupTime = 0x00;

- TCLRSetupTime = 0;

- TARSetupTime = 0;

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period.

Figure 67. PC Card/CompactFlash controller waveforms for attribute memory read access

1. Only data bits 0...7 are read (bits 8...15 are disregarded).

## 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

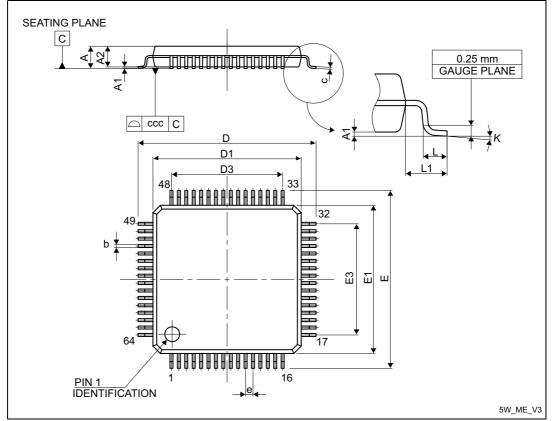

## 7.1 LQFP64 package information

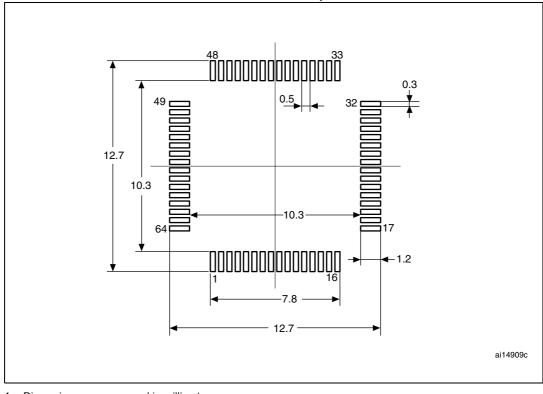

Figure 77. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

## Table 87. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|

|        | Min   | Тур         | Мах   | Min    | Тур                   | Мах    |  |

| С      | 0.090 | -           | 0.200 | 0.0035 | -                     | 0.0079 |  |

| D      | -     | 12.000      | -     | -      | 0.4724                | -      |  |

| D1     | -     | 10.000      | -     | -      | 0.3937                | -      |  |

| D3     | -     | 7.500       | -     | -      | 0.2953                | -      |  |

| Е      | -     | 12.000      | -     | -      | 0.4724                | -      |  |

| E1     | -     | 10.000      | -     | -      | 0.3937                | -      |  |

| E3     | -     | 7.500       | -     | -      | 0.2953                | -      |  |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |  |

| К      | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |  |

| L1     | -     | 1.000       | -     | -      | 0.0394                | -      |  |

| CCC    | -     | -           | 0.080 | -      | -                     | 0.0031 |  |

## Table 87. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

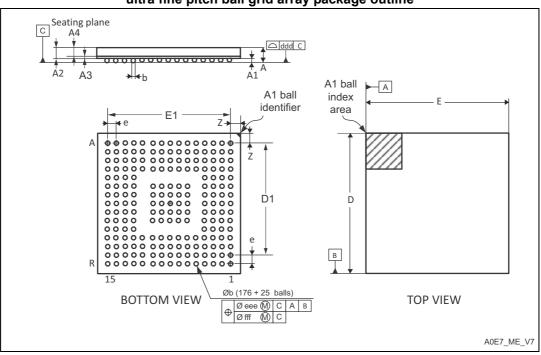

## 7.6 UFBGA176+25 package information

Figure 89. UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

## Table 93. UFBGA176+25, - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package mechanical data

| Cumhal | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

| Symbol | Min.        | Тур.   | Max.   | Min.                  | Тур.   | Max.   |

| А      | -           | -      | 0.600  | -                     | -      | 0.0236 |

| A1     | -           | -      | 0.110  | -                     | -      | 0.0043 |

| A2     | -           | 0.450  | -      | -                     | 0.0177 | -      |

| A3     | -           | 0.130  | -      | -                     | 0.0051 | 0.0094 |

| A4     | -           | 0.320  | -      | -                     | 0.0126 | -      |

| b      | 0.240       | 0.290  | 0.340  | 0.0094                | 0.0114 | 0.0134 |

| D      | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |

| D1     | -           | 9.100  | -      | -                     | 0.3583 | -      |

| E      | 9.850       | 10.000 | 10.150 | 0.3878                | 0.3937 | 0.3996 |

| E1     | -           | 9.100  | -      | -                     | 0.3583 | -      |

| е      | -           | 0.650  | -      | -                     | 0.0256 | -      |

| Z      | -           | 0.450  | -      | -                     | 0.0177 | -      |

| ddd    | -           | -      | 0.080  | -                     | -      | 0.0031 |

| Table 97. Document revision history (continued)       Date     Revision |  |  |

|-------------------------------------------------------------------------|--|--|

|                                                                         |  |  |

| Date       R         13-Jul-2010       (cc                              |  |  |