## STMicroelectronics - <u>STM32F205ZGT6W Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

E·XFI

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 120MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, MMC, SPI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT      |

| Number of I/O              | 114                                                                    |

| Program Memory Size        | 1MB (1M x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 132K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 144-LQFP                                                               |

| Supplier Device Package    | 144-LQFP (20x20)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f205zgt6w |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 93. | UFBGA176+25, - 201-ball, 10 x 10 mm, 0.65 mm pitch,          |     |

|-----------|--------------------------------------------------------------|-----|

|           | ultra fine pitch ball grid array package mechanical data     | 165 |

| Table 94. | UFBGA176+25 recommended PCB design rules (0.65 mm pitch BGA) | 166 |

| Table 95. | Package thermal characteristics                              | 167 |

| Table 96. | Ordering information scheme                                  | 168 |

| Table 97. | Document revision history                                    | 169 |

8/182

|                               |                         | Table                | 2. STM3 | 82F205    | xx feat | ures a | nd perip      | heral co                  | ounts | 5             |                    |               |        |      |      |

|-------------------------------|-------------------------|----------------------|---------|-----------|---------|--------|---------------|---------------------------|-------|---------------|--------------------|---------------|--------|------|------|

|                               | Peripherals             |                      | ST      | /132F205R | Rx      |        |               | STM32                     | F205V | x             |                    | S             | TM32F2 | 05Zx |      |

| Flash memory in               | n Kbytes                | 128                  | 256     | 512       | 768     | 1024   | 128           | 256                       | 512   | 768           | 1024               | 256           | 512    | 768  | 1024 |

| SRAM in Kbytes                | System<br>(SRAM1+SRAM2) | 64<br>(48+16)        |         |           |         |        | 64<br>(48+16) | 96<br>(80+16)             |       | 128<br>(112+1 | 6)                 | 96<br>(80+16) |        |      | 3)   |

|                               | Backup                  |                      | 4 4 4   |           |         |        |               |                           |       |               |                    |               |        |      |      |

| FSMC memory of                | controller              |                      |         | No        |         |        |               |                           |       |               | Yes <sup>(1)</sup> |               |        |      |      |

| Ethernet                      |                         |                      |         |           |         |        |               | No                        |       |               |                    |               |        |      |      |

|                               | General-purpose         |                      |         |           |         |        |               | 10                        |       |               |                    |               |        |      |      |

|                               | Advanced-control        |                      |         |           |         |        |               | 2                         |       |               |                    |               |        |      |      |

| Timers                        | Basic                   |                      |         |           |         |        |               | 2                         |       |               |                    |               |        |      |      |

|                               | IWDG                    |                      |         |           |         |        |               | Yes                       |       |               |                    |               |        |      |      |

|                               | WWDG                    |                      |         |           |         |        |               | Yes                       |       |               |                    |               |        |      |      |

| RTC                           |                         |                      |         |           |         |        |               | Yes                       |       |               |                    |               |        |      |      |

| Random numbei                 | r generator             | Yes                  |         |           |         |        |               |                           |       |               |                    |               |        |      |      |

|                               | SPI/(I <sup>2</sup> S)  | 3/(2) <sup>(2)</sup> |         |           |         |        |               |                           |       |               |                    |               |        |      |      |

|                               | l <sup>2</sup> C        |                      |         |           |         |        | 3             |                           |       |               |                    |               |        |      |      |

| Comm.<br>interfaces           | USART<br>UART           | 4<br>2               |         |           |         |        |               |                           |       |               |                    |               |        |      |      |

| interfaces                    | USB OTG FS              | Yes                  |         |           |         |        |               |                           |       |               |                    |               |        |      |      |

|                               | USB OTG HS              |                      | Yes     |           |         |        |               |                           |       |               |                    |               |        |      |      |

|                               | CAN                     |                      | 2       |           |         |        |               |                           |       |               |                    |               |        |      |      |

| Camera interface              | e                       |                      |         |           |         |        |               | No                        |       |               |                    |               |        |      |      |

| GPIOs                         |                         |                      |         | 51        |         |        |               | 8                         | 32    |               |                    |               | 114    |      |      |

| SDIO                          |                         |                      |         |           |         |        |               | Yes                       |       |               |                    |               |        |      |      |

| 12-bit ADC                    |                         |                      |         |           |         |        |               | 3                         |       |               |                    |               |        |      |      |

| Number of chan                | nels                    |                      |         | 16        |         |        |               | 1                         | 16    |               |                    |               | 24     |      |      |

| 12-bit DAC<br>Number of chanı | nels                    |                      |         |           |         |        |               | Yes<br>2                  |       |               |                    |               |        |      |      |

| Maximum CPU f                 | frequency               |                      |         |           |         |        | 1             | I20 MHz                   |       |               |                    |               |        |      |      |

| Operating voltag              | e                       |                      |         |           |         |        | 1.8           | V to 3.6 V <sup>(3)</sup> |       |               |                    |               |        |      |      |

5

14/182

# 3.34 ADCs (analog-to-digital converters)

Three 12-bit analog-to-digital converters are embedded and each ADC shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the timers TIM1, TIM2, TIM3, TIM4, TIM5 and TIM8 can be internally connected to the ADC start trigger and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

# 3.35 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

# 3.36 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.8 and 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

DocID15818 Rev 13

|        |           | Pi      | ns      |         |          |                                                      |          |               |      | ennitions (continued)                                                  |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                    | Additional<br>functions |

| -      | -         | -       | 14      | 20      | J3       | PF4                                                  | I/O      | FT            | (4)  | FSMC_A4, EVENTOUT                                                      | ADC3_IN14               |

| -      | -         | -       | 15      | 21      | K3       | PF5                                                  | I/O      | FT            | (4)  | FSMC_A5, EVENTOUT                                                      | ADC3_IN15               |

| -      | H9        | 10      | 16      | 22      | G2       | V <sub>SS</sub>                                      | S        | -             | -    | -                                                                      | -                       |

| -      | -         | 11      | 17      | 23      | G3       | V <sub>DD</sub>                                      | S        | -             | -    | -                                                                      | -                       |

| -      | -         | -       | 18      | 24      | K2       | PF6                                                  | I/O      | FT            | (4)  | TIM10_CH1, FSMC_NIORD,<br>EVENTOUT                                     | ADC3_IN4                |

| -      | -         | -       | 19      | 25      | K1       | PF7                                                  | I/O      | FT            | (4)  | TIM11_CH1,FSMC_NREG,<br>EVENTOUT                                       | ADC3_IN5                |

| -      | -         | -       | 20      | 26      | L3       | PF8                                                  | I/O      | FT            | (4)  | TIM13_CH1,<br>FSMC_NIOWR, EVENTOUT                                     | ADC3_IN6                |

| -      | -         | -       | 21      | 27      | L2       | PF9                                                  | I/O      | FT            | (4)  | TIM14_CH1, FSMC_CD,<br>EVENTOUT                                        | ADC3_IN7                |

| -      | -         | -       | 22      | 28      | L1       | PF10                                                 | I/O      | FT            | (4)  | FSMC_INTR, EVENTOUT                                                    | ADC3_IN8                |

| 5      | E9        | 12      | 23      | 29      | G1       | PH0/OSC_IN<br>(PH0)                                  | I/O      | FT            | -    | EVENTOUT                                                               | OSC_IN <sup>(4)</sup>   |

| 6      | F9        | 13      | 24      | 30      | H1       | PH1/OSC_OUT<br>(PH1)                                 | I/O      | FT            | -    | EVENTOUT                                                               | OSC_OUT <sup>(4)</sup>  |

| 7      | E8        | 14      | 25      | 31      | J1       | NRST                                                 | I/O      |               | I    | -                                                                      | -                       |

| 8      | G9        | 15      | 26      | 32      | M2       | PC0                                                  | I/O      | FT            | (4)  | OTG_HS_ULPI_STP,<br>EVENTOUT                                           | ADC123_<br>IN10         |

| 9      | F8        | 16      | 27      | 33      | М3       | PC1                                                  | I/O      | FT            | (4)  | ETH_MDC, EVENTOUT                                                      | ADC123_<br>IN11         |

| 10     | D7        | 17      | 28      | 34      | M4       | PC2                                                  | I/O      | FT            | (4)  | SPI2_MISO,<br>OTG_HS_ULPI_DIR,<br>ETH_MII_TXD2, EVENTOUT               | ADC123_<br>IN12         |

| 11     | G8        | 18      | 29      | 35      | M5       | PC3                                                  | I/O      | FT            | (4)  | SPI2_MOSI, I2S2_SD,<br>OTG_HS_ULPI_NXT,<br>ETH_MII_TX_CLK,<br>EVENTOUT | ADC123_<br>IN13         |

| -      | -         | 19      | 30      | 36      | -        | V <sub>DD</sub>                                      | S        | -             | -    | -                                                                      | -                       |

| 12     | -         | 20      | 31      | 37      | M1       | V <sub>SSA</sub>                                     | S        | -             | -    | -                                                                      | -                       |

| -      | -         | -       | -       | -       | N1       | V <sub>REF-</sub>                                    | S        | -             | -    | -                                                                      | -                       |

| -      | F7        | 21      | 32      | 38      | P1       | V <sub>REF+</sub>                                    | S        | -             | -    | -                                                                      | -                       |

|        |           | Pi      | ns      |         |          |                                                      |          |           |        |                                                                                                  |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|-----------|--------|--------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | Note Note |        | Alternate functions                                                                              | Additional<br>functions |

| 13     | -         | 22      | 33      | 39      | R1       | V <sub>DDA</sub>                                     | S        | -         | -      | -                                                                                                | -                       |

| 14     | E7        | 23      | 34      | 40      | N3       | PA0-WKUP<br>(PA0)                                    | I/O      | FT        | (4)(5) | USART2_CTS, UART4_TX,<br>ETH_MII_CRS,<br>TIM2_CH1_ETR,<br>TIM5_CH1, TIM8_ETR,<br>EVENTOUT        | ADC123_IN0,<br>WKUP     |

| 15     | H8        | 24      | 35      | 41      | N2       | PA1                                                  | I/O      | FT        | (4)    | USART2_RTS, UART4_RX,<br>ETH_RMII_REF_CLK,<br>ETH_MII_RX_CLK,<br>TIM5_CH2, TIM2_CH2,<br>EVENTOUT | ADC123_IN1              |

| 16     | J9        | 25      | 36      | 42      | P2       | PA2                                                  | I/O      | FT        | (4)    | USART2_TX,TIM5_CH3,<br>TIM9_CH1, TIM2_CH3,<br>ETH_MDIO, EVENTOUT                                 | ADC123_IN2              |

| -      | -         | -       | -       | 43      | F4       | PH2                                                  | I/O      | FT        | -      | ETH_MII_CRS, EVENTOUT                                                                            | -                       |

| -      | -         | -       | -       | 44      | G4       | PH3                                                  | I/O      | FT        | -      | ETH_MII_COL, EVENTOUT                                                                            | -                       |

| -      | -         | -       | -       | 45      | H4       | PH4                                                  | I/O      | FT        | -      | I2C2_SCL,<br>OTG_HS_ULPI_NXT,<br>EVENTOUT                                                        | -                       |

| -      | -         | -       | -       | 46      | J4       | PH5                                                  | I/O      | FT        | -      | I2C2_SDA, EVENTOUT                                                                               | -                       |

| 17     | G7        | 26      | 37      | 47      | R2       | PA3                                                  | I/O      | FT        | (4)    | USART2_RX, TIM5_CH4,<br>TIM9_CH2, TIM2_CH4,<br>OTG_HS_ULPI_D0,<br>ETH_MII_COL, EVENTOUT          | ADC123_IN3              |

| 18     | F1        | 27      | 38      | 48      | -        | V <sub>SS</sub>                                      | S        | -         | -      | -                                                                                                | -                       |

|        | H7        |         |         |         | L4       | REGOFF                                               | I/O      | -         | -      | -                                                                                                | -                       |

| 19     | E1        | 28      | 39      | 49      | K4       | V <sub>DD</sub>                                      | S        | -         | -      | -                                                                                                | -                       |

| 20     | J8        | 29      | 40      | 50      | N4       | PA4                                                  | I/O      | ТТа       | (4)    | SPI1_NSS, SPI3_NSS,<br>USART2_CK,<br>DCMI_HSYNC,<br>OTG_HS_SOF, I2S3_WS,<br>EVENTOUT             | ADC12_IN4,<br>DAC_OUT1  |

| 21     | H6        | 30      | 41      | 51      | P4       | PA5                                                  | I/O      | ТТа       | (4)    | SPI1_SCK,<br>OTG_HS_ULPI_CK,<br>TIM2_CH1_ETR,<br>TIM8_CH1N, EVENTOUT                             | ADC12_IN5,<br>DAC_OUT2  |

Table 8. STM32F20x pin and ball definitions (continued)

|        | Pins      |         |         |         |          |                                                      |          |               |      |                                                                                                               |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                                                           | Additional<br>functions |

| 22     | H5        | 31      | 42      | 52      | P3       | PA6                                                  | I/O      | FT            | (4)  | SPI1_MISO, TIM8_BKIN,<br>TIM13_CH1, DCMI_PIXCLK,<br>TIM3_CH1, TIM1_BKIN,<br>EVENTOUT                          | ADC12_IN6               |

| 23     | J7        | 32      | 43      | 53      | R3       | PA7                                                  | I/O      | FT            | (4)  | SPI1_MOSI, TIM8_CH1N,<br>TIM14_CH1, TIM3_CH2,<br>ETH_MII_RX_DV,<br>TIM1_CH1N,<br>ETH_RMII_CRS_DV,<br>EVENTOUT | ADC12_IN7               |

| 24     | H4        | 33      | 44      | 54      | N5       | PC4                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD0,<br>ETH_MII_RXD0,<br>EVENTOUT                                                                   | ADC12_IN14              |

| 25     | G3        | 34      | 45      | 55      | P5       | PC5                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD1,<br>ETH_MII_RXD1,<br>EVENTOUT                                                                   | ADC12_IN15              |

| 26     | J6        | 35      | 46      | 56      | R5       | PB0                                                  | I/O      | FT            | (4)  | TIM3_CH3, TIM8_CH2N,<br>OTG_HS_ULPI_D1,<br>ETH_MII_RXD2,<br>TIM1_CH2N, EVENTOUT                               | ADC12_IN8               |

| 27     | J5        | 36      | 47      | 57      | R4       | PB1                                                  | I/O      | FT            | (4)  | TIM3_CH4, TIM8_CH3N,<br>OTG_HS_ULPI_D2,<br>ETH_MII_RXD3,<br>TIM1_CH3N, EVENTOUT                               | ADC12_IN9               |

| 28     | J4        | 37      | 48      | 58      | M6       | PB2/BOOT1 (PB2)                                      | I/O      | FT            | -    | EVENTOUT                                                                                                      | -                       |

| -      | -         | -       | 49      | 59      | R6       | PF11                                                 | I/O      | FT            | -    | DCMI_D12, EVENTOUT                                                                                            |                         |

| -      | -         | -       | 50      | 60      | P6       | PF12                                                 | I/O      | FT            | -    | FSMC_A6, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 51      | 61      | M8       | V <sub>SS</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 52      | 62      | N8       | V <sub>DD</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 53      | 63      | N6       | PF13                                                 | I/O      | FT            | -    | FSMC_A7, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 54      | 64      | R7       | PF14                                                 | I/O      | FT            | -    | FSMC_A8, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 55      | 65      | P7       | PF15                                                 | I/O      | FT            | -    | FSMC_A9, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 56      | 66      | N7       | PG0                                                  | I/O      | FT            | -    | FSMC_A10, EVENTOUT                                                                                            | -                       |

| -      | -         | -       | 57      | 67      | M7       | PG1                                                  | I/O      | FT            | -    | FSMC_A11, EVENTOUT                                                                                            | -                       |

# 5 Memory mapping

The memory map is shown in *Figure 16*.

|                 |                   |                                                                           |                   | Тур                       | Ma                        |                            |                |  |

|-----------------|-------------------|---------------------------------------------------------------------------|-------------------|---------------------------|---------------------------|----------------------------|----------------|--|

| Symbol          | Parameter         | Conditions                                                                | f <sub>HCLK</sub> | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit           |  |

|                 |                   |                                                                           | 120 MHz           | 38                        | 51                        | 61                         |                |  |

|                 |                   |                                                                           | 90 MHz            | 30                        | 43                        | 53                         |                |  |

|                 |                   |                                                                           | 60 MHz            | 20                        | 33                        | 43                         |                |  |

|                 |                   | <b>-</b> (2)                                                              | 30 MHz            | 11                        | 25                        | 35                         |                |  |

|                 |                   | External clock <sup>(2)</sup> ,<br>all peripherals enabled <sup>(3)</sup> | 25 MHz            | 8                         | 21                        | 31                         |                |  |

|                 |                   |                                                                           | 16 MHz            | 6                         | 19                        | 29                         |                |  |

|                 |                   |                                                                           | 8 MHz             | 3.6                       | 17.0                      | 27.0                       | -<br>-<br>- mA |  |

|                 |                   |                                                                           | 4 MHz             | 2.4                       | 15.4                      | 25.3                       |                |  |

|                 | Supply current in |                                                                           | 2 MHz             | 1.9                       | 14.9                      | 24.7                       |                |  |

| I <sub>DD</sub> | Sleep mode        |                                                                           | 120 MHz           | 8                         | 21                        | 31                         | mA             |  |

|                 |                   |                                                                           | 90 MHz            | 7                         | 20                        | 30                         |                |  |

|                 |                   |                                                                           | 60 MHz            | 5                         | 18                        | 28                         |                |  |

|                 |                   |                                                                           | 30 MHz            | 3.5                       | 16.0                      | 26.0                       | -              |  |

|                 |                   | External clock <sup>(2)</sup> , all peripherals disabled                  | 25 MHz            | 2.5                       | 16.0                      | 25.0                       |                |  |

|                 |                   |                                                                           | 16 MHz            | 2.1                       | 15.1                      | 25.0                       |                |  |

|                 |                   |                                                                           | 8 MHz             | 1.7                       | 15.0                      | 25.0                       |                |  |

|                 |                   |                                                                           | 4 MHz             | 1.5                       | 14.6                      | 24.6                       |                |  |

|                 |                   |                                                                           | 2 MHz             | 1.4                       | 14.2                      | 24.3                       |                |  |

| Table 22. Typical and maximum current | consumption in Sleep mode |

|---------------------------------------|---------------------------|

|---------------------------------------|---------------------------|

1. Guaranteed by characterization results, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 4 MHz and PLL is on when  $\rm f_{HCLK}$  > 25 MHz.

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

|        |                           |                                                      |                            | Тур                        |                            | Ма                     |         |    |  |

|--------|---------------------------|------------------------------------------------------|----------------------------|----------------------------|----------------------------|------------------------|---------|----|--|

| Symbol | Parameter                 | Conditions                                           | Т                          | A = 25 °C                  | 0                          | T <sub>A</sub> = 85 °C | Unit    |    |  |

|        |                           |                                                      | V <sub>DD</sub> =<br>1.8 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> =      | = 3.6 V |    |  |

|        | Supply current in Standby | Backup SRAM ON, low-speed<br>oscillator and RTC ON   | 3.0                        | 3.4                        | 4.0                        | 15.1                   | 25.8    |    |  |

|        |                           | Backup SRAM OFF, low-<br>speed oscillator and RTC ON | 2.4                        | 2.7                        | 3.3                        | 12.4                   | 20.5    | μA |  |

|        | mode                      | Backup SRAM ON, RTC OFF                              | 2.4                        | 2.6                        | 3.0                        | 12.5                   | 24.8    |    |  |

|        |                           | Backup SRAM OFF, RTC<br>OFF                          | 1.7                        | 1.9                        | 2.2                        | 9.8                    | 19.2    |    |  |

## Table 24. Typical and maximum current consumptions in Standby mode

1. Guaranteed by characterization results, not tested in production.

# Table 25. Typical and maximum current consumptions in $\mathrm{V}_{\mathrm{BAT}}$ mode

| Symbol               |                                    | Parameter Conditions                                |                            | Тур                        |                            |                   | Max <sup>(1)</sup>      |      |  |

|----------------------|------------------------------------|-----------------------------------------------------|----------------------------|----------------------------|----------------------------|-------------------|-------------------------|------|--|

|                      | Parameter                          |                                                     |                            | T <sub>A</sub> = 25 °C     |                            |                   | T <sub>A</sub> = 105 °C | Unit |  |

|                      |                                    |                                                     | V <sub>DD</sub> =<br>1.8 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> = | = 3.6 V                 |      |  |

|                      | Backup<br>domain supply<br>current | Backup SRAM ON, low-speed oscillator and RTC ON     | 1.29                       | 1.42                       | 1.68                       | 12                | 19                      |      |  |

| I <sub>DD_VBAT</sub> |                                    | Backup SRAM OFF, low-speed<br>oscillator and RTC ON | 0.62                       | 0.73                       | 0.96                       | 8                 | 10                      | μA   |  |

|                      |                                    | Backup SRAM ON, RTC OFF                             | 0.79                       | 0.81                       | 0.86                       | 9                 | 16                      |      |  |

|                      |                                    | Backup SRAM OFF, RTC OFF                            | 0.10                       | 0.10                       | 0.10                       | 5                 | 7                       |      |  |

1. Guaranteed by characterization results, not tested in production.

| Symbol                              | Parameter                   | Conditions                    | Min | Тур  | Max | Unit |  |  |  |

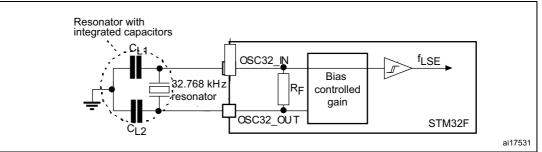

|-------------------------------------|-----------------------------|-------------------------------|-----|------|-----|------|--|--|--|

| R <sub>F</sub>                      | Feedback resistor           | -                             | -   | 18.4 | -   | MΩ   |  |  |  |

| I <sub>DD</sub>                     | LSE current consumption     | -                             | -   | -    | 1   | μA   |  |  |  |

| 9 <sub>m</sub>                      | Oscillator Transconductance | -                             | 2.8 | -    | -   | µA/V |  |  |  |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                | V <sub>DD</sub> is stabilized | -   | 2    | -   | S    |  |  |  |

Table 31. LSE oscillator characteristics ( $f_{LSE} = 32.768 \text{ kHz}$ )<sup>(1)</sup>

1. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

Note: For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Figure 33. Typical application with a 32.768 kHz crystal

# 6.3.9 Internal clock source characteristics

The parameters given in *Table 32* and *Table 33* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                             | Conditions                           | Min | Тур | Max | Unit |

|-------------------------------------|---------------------------------------|--------------------------------------|-----|-----|-----|------|

| f <sub>HSI</sub>                    | Frequency                             | -                                    | -   | 16  | -   | MHz  |

|                                     | HSI user-trimming step <sup>(2)</sup> | -                                    | -   | -   | 1   | %    |

|                                     |                                       | $T_A = -40$ to 105 °C <sup>(3)</sup> | - 8 | -   | 4.5 | %    |

| ACC <sub>HSI</sub>                  | Accuracy of the<br>HSI oscillator     | $T_A = -10$ to 85 °C <sup>(3)</sup>  | - 4 | -   | 4   | %    |

|                                     |                                       | $T_A = 25 \ ^{\circ}C^{(4)}$         | – 1 | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                    | -   | 2.2 | 4.0 | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power consumption      | -                                    | -   | 60  | 80  | μA   |

Table 32. HSI oscillator characteristics <sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design, not tested in production.

- 3. Guaranteed by characterization results.

- 4. Factory calibrated, parts not soldered.

The test results are given in *Table 41*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                              | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 120 MHz, conforms<br>to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 120 MHz, conforms<br>to IEC 61000-4-2 | 4A              |

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

# 6.3.18 TIM timer characteristics

The parameters given in *Table 50* and *Table 51* are guaranteed by design.

Refer to Section 6.3.16: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                       | Conditions                                                     | Min    | Мах                     | Unit                 |

|------------------------|---------------------------------|----------------------------------------------------------------|--------|-------------------------|----------------------|

|                        |                                 | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time           | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>60 MHz | 16.7   | -                       | ns                   |

|                        |                                 | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                 | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 30 MHz                | 33.3   | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock            |                                                                | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| 'EXT                   | frequency on CH1 to CH4         |                                                                | 0      | 30                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                |                                                                | -      | 16/32                   | bit                  |

|                        | 16-bit counter clock period     |                                                                | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t                      | when internal clock is selected | f <sub>TIMxCLK</sub> = 60 MHz<br>APB1= 30 MHz                  | 0.0167 | 1092                    | μs                   |

| <sup>t</sup> COUNTER   | 32-bit counter clock period     |                                                                | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        | when internal clock is selected |                                                                | 0.0167 | 71582788                | μs                   |

| tury count             | Maximum possible count          |                                                                | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT |                                 |                                                                | -      | 71.6                    | s                    |

| Table 50. Characteristics of TIMx connected to the APE | 31 domain <sup>(1)</sup> |

|--------------------------------------------------------|--------------------------|

|--------------------------------------------------------|--------------------------|

1. TIMx is used as a general term to refer to the TIM2, TIM3, TIM4, TIM5, TIM6, TIM7, and TIM12 timers.

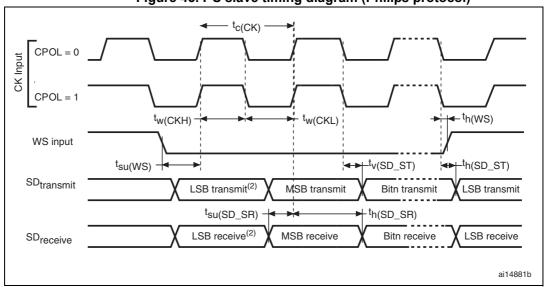

Figure 45. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

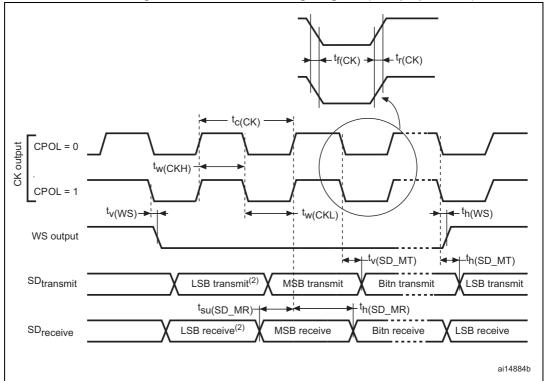

Figure 46. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. Guaranteed by characterization results, not tested in production.

2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

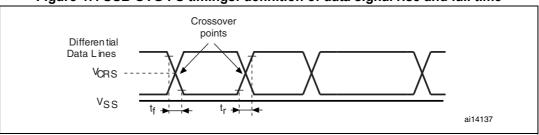

#### Figure 47. USB OTG FS timings: definition of data signal rise and fall time

### Table 58. USB OTG FS electrical characteristics<sup>(1)</sup>

| Driver characteristics |                                       |                                |     |     |    |  |  |  |

|------------------------|---------------------------------------|--------------------------------|-----|-----|----|--|--|--|

| Symbol                 | ymbol Parameter Conditions Min Max Un |                                |     |     |    |  |  |  |

| t <sub>r</sub>         | Rise time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |  |

| t <sub>f</sub>         | Fall time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |  |

| t <sub>rfm</sub>       | Rise/fall time matching               | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %  |  |  |  |

| V <sub>CRS</sub>       | Output signal crossover voltage       | -                              | 1.3 | 2.0 | V  |  |  |  |

1. Guaranteed by design, not tested in production.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

### **USB HS characteristics**

Table 59 shows the USB HS operating voltage.

#### Table 59. USB HS DC electrical characteristics

| Symbol                                                   |  | Parameter                    | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

|----------------------------------------------------------|--|------------------------------|---------------------|---------------------|------|

| Input level V <sub>DD</sub> USB OTG HS operating voltage |  | USB OTG HS operating voltage | 2.7                 | 3.6                 | V    |

1. All the voltages are measured from the local ground potential.

#### Table 60. Clock timing parameters

| Parameter <sup>(1)</sup>                                           | Symbol              | Min                     | Nominal | Max    | Unit |      |

|--------------------------------------------------------------------|---------------------|-------------------------|---------|--------|------|------|

| Frequency (first transition) 8-bit ±10%                            |                     | F <sub>START_8BIT</sub> | 54      | 60     | 66   | MHz  |

| Frequency (steady state) ±500                                      | F <sub>STEADY</sub> | 59.97                   | 60      | 60.03  | MHz  |      |

| Duty cycle (first transition) 8-bit ±10%                           |                     | D <sub>START_8BIT</sub> | 40      | 50     | 60   | %    |

| Duty cycle (steady state) ±500                                     | D <sub>STEADY</sub> | 49.975                  | 50      | 50.025 | %    |      |

| Time to reach the steady state duty cycle after the first transiti |                     | T <sub>STEADY</sub>     | -       | -      | 1.4  | ms   |

| Clock startup time after the                                       | Peripheral          | T <sub>START_DEV</sub>  | -       | -      | 5.6  | ms   |

| de-assertion of SuspendM                                           | Host                | T <sub>START_HOST</sub> | -       | -      | -    | 1115 |

| PHY preparation time after the<br>of the input clock               | T <sub>PREP</sub>   | -                       | -       | -      | μs   |      |

1. Guaranteed by design, not tested in production.

## General PCB design guidelines

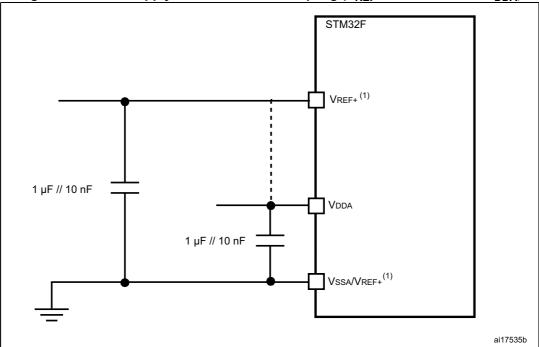

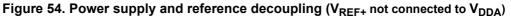

Power supply decoupling should be performed as shown in *Figure 54* or *Figure 55*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

V<sub>REF+</sub> and V<sub>REF</sub> inputs are both available on UFBGA176 package. V<sub>REF+</sub> is also available on all packages except for LQFP64. When V<sub>REF+</sub> and V<sub>REF</sub> are not available, they are internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

Figure 55. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

| Symbol Parameter                 |                                       | Min                | Тур | Мах                    | Unit | Comments                                                                                                                                       |  |  |  |

|----------------------------------|---------------------------------------|--------------------|-----|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>DDA</sub>                 | Analog supply voltage                 | 1.8 <sup>(1)</sup> | -   | 3.6                    | V    | -                                                                                                                                              |  |  |  |

| V <sub>REF+</sub>                | Reference supply voltage              | 1.8 <sup>(1)</sup> | -   | 3.6                    | V    | V <sub>REF+</sub> ≤V <sub>DDA</sub>                                                                                                            |  |  |  |

| V <sub>SSA</sub>                 | Ground                                | 0                  | -   | 0                      | V    | -                                                                                                                                              |  |  |  |

| R <sub>LOAD</sub> <sup>(2)</sup> | Resistive load with buffer<br>ON      | 5                  | -   | -                      | kΩ   | -                                                                                                                                              |  |  |  |

| R <sub>0</sub> <sup>(2)</sup>    | Impedance output with<br>buffer OFF   | -                  | -   | 15                     | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$                        |  |  |  |

| C <sub>LOAD</sub> <sup>(2)</sup> | Capacitive load                       | -                  | -   | 50                     | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                                |  |  |  |

| DAC_OUT<br>min <sup>(2)</sup>    | Lower DAC_OUT voltage with buffer ON  | 0.2                | -   | -                      | v    | It gives the maximum output excursion<br>of the DAC.<br>It corresponds to 12-bit input code<br>(0x0E0) to (0xF1C) at V <sub>REF+</sub> = 3.6 V |  |  |  |

| DAC_OUT<br>max <sup>(2)</sup>    | Higher DAC_OUT voltage with buffer ON | -                  | -   | V <sub>DDA</sub> – 0.2 | V    | and (0x1C7) to (0xE38) at $V_{REF+} = 3.0 \text{ V}$<br>1.8 V                                                                                  |  |  |  |

# 6.3.21 DAC electrical characteristics

Table 68. DAC characteristics

V<sub>REF+</sub> and V<sub>REF-</sub> inputs are both available on UFBGA176 package. V<sub>REF+</sub> is also available on all packages except for LQFP64. When V<sub>REF+</sub> and V<sub>REF-</sub> are not available, they are internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

| Symbol                     | Symbol Parameter                             |     |   |    |

|----------------------------|----------------------------------------------|-----|---|----|

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high               | 4   | - | ns |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)       | -   | 0 | ns |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625)     | 3   | - | ns |

| t <sub>d(CLKH-NOEL)</sub>  | FSMC_CLK high to FSMC_NOE low                | -   | 1 | ns |

| t <sub>d(CLKL-NOEH)</sub>  | FSMC_CLK low to FSMC_NOE high                | 1.5 | - | ns |

| t <sub>su(DV-CLKH)</sub>   | FSMC_D[15:0] valid data before FSMC_CLK high | 8   | - | ns |

| t <sub>h(CLKH-DV)</sub>    | FSMC_D[15:0] valid data after FSMC_CLK high  |     | - | ns |

# Table 78. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

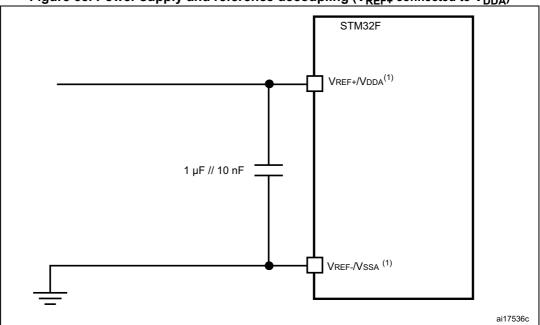

## Figure 64. Synchronous non-multiplexed PSRAM write timings

## Table 79. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                             | Min                    | Max | Unit |

|---------------------------|---------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>       | FSMC_CLK period                       | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub> | FSMC_CLK low to FSMC_NEx low (x=02)   | -                      | 1   | ns   |

| t <sub>d(CLKL-NExH)</sub> | FSMC_CLK low to FSMC_NEx high (x= 02) | 1                      | -   | ns   |

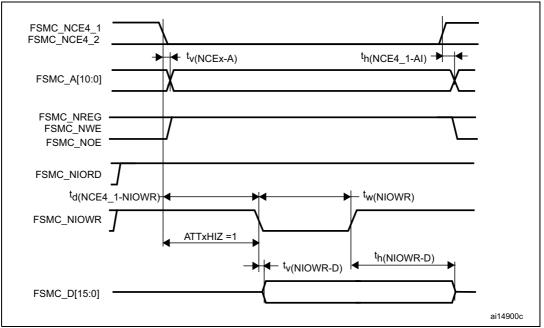

Figure 70. PC Card/CompactFlash controller waveforms for I/O space write access

# Table 80. Switching characteristics for PC Card/CF read and write cycles in attribute/common space<sup>(1)(2)</sup>

| Symbol                    | Parameter                                    | Min                      | Max                    | Unit |

|---------------------------|----------------------------------------------|--------------------------|------------------------|------|

| t <sub>v(NCEx-A)</sub>    | FSMC_Ncex low to FSMC_Ay valid               | -                        | 0                      | ns   |

| t <sub>h(NCEx_AI)</sub>   | FSMC_NCEx high to FSMC_Ax invalid            | 4                        | -                      | ns   |

| t <sub>d(NREG-NCEx)</sub> | FSMC_NCEx low to FSMC_NREG valid             | -                        | 3.5                    | ns   |

| t <sub>h(NCEx-NREG)</sub> | FSMC_NCEx high to FSMC_NREG invalid          | T <sub>HCLK</sub> + 4    | -                      | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                        | 5T <sub>HCLK</sub> + 1 | ns   |

| t <sub>d(NCEx-NOE)</sub>  | FSMC_NCEx low to FSMC_NOE low                | -                        | 5T <sub>HCLK</sub>     | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low width                           | 8T <sub>HCLK</sub> - 0.5 | 8T <sub>HCLK</sub> + 1 | ns   |

| t <sub>d(NOE_NCEx)</sub>  | FSMC_NOE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> + 2.5 | -                      | ns   |

| t <sub>su (D-NOE)</sub>   | FSMC_D[15:0] valid data before FSMC_NOE high | 4                        | -                      | ns   |

| t <sub>h (N0E-D)</sub>    | FSMC_N0E high to FSMC_D[15:0] invalid        | 2                        | -                      | ns   |

| t <sub>w(NWE)</sub>       | FSMC_NWE low width                           | 8T <sub>HCLK</sub> - 1   | 8T <sub>HCLK</sub> + 4 | ns   |

| t <sub>d(NWE_NCEx</sub> ) | FSMC_NWE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> + 1.5 | -                      | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                        | 5HCLK+ 1               | ns   |

| t <sub>v (NWE-D)</sub>    | FSMC_NWE low to FSMC_D[15:0] valid           | -                        | 0                      | ns   |

| t <sub>h (NWE-D)</sub>    | FSMC_NWE high to FSMC_D[15:0] invalid        | 8T <sub>HCLK</sub>       | -                      | ns   |

| t <sub>d (D-NWE)</sub>    | FSMC_D[15:0] valid before FSMC_NWE high      | 13T <sub>HCLK</sub>      | -                      | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

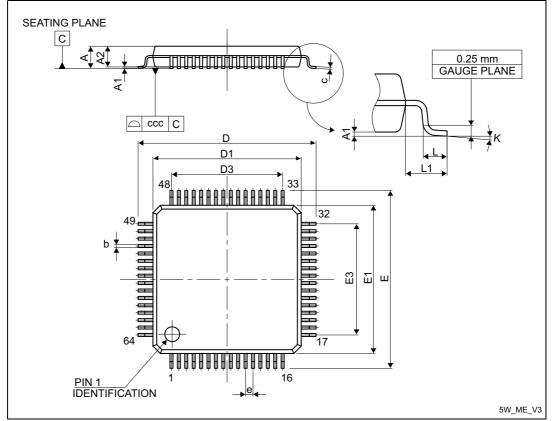

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 7.1 LQFP64 package information

Figure 77. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

# Table 87. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| А      | -           | -     | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| Table 97. Document revision history (continued) |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Date                                            | Revision          | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 04-Nov-2013                                     | 11<br>(continued) | Removed Appendix A Application block diagrams.<br>Updated Figure 77: LQFP64 – 10 x 10 mm 64 pin low-profile quad flat<br>package outline and Table 87: LQFP64 – 10 x 10 mm 64 pin low-profile<br>quad flat package mechanical data. Updated Figure 80: LQFP100, 14 x<br>14 mm 100-pin low-profile quad flat package outline, Figure 83:<br>LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline,<br>Figure 86: LQFP176 - Low profile quad flat package 24 × 24 × 1.4 mm,<br>package outline. Updated Figure 88: UFBGA176+25 - ultra thin fine<br>pitch ball grid array 10 × 10 × 0.6 mm, package outline and Figure 88:<br>UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm,<br>package outline.                                                                                                                                                                      |  |

| 27-Oct-2014                                     | 12                | Updated V <sub>BAT</sub> voltage range in <i>Figure 19: Power supply scheme</i> . Added caution note in <i>Section 6.1.6: Power supply scheme</i> .<br>Updated V <sub>IN</sub> in <i>Table 14: General operating conditions</i> .<br>Removed note 1 in <i>Table 23: Typical and maximum current consumptions in Stop mode</i> .<br>Updated <i>Table 45: I/O current injection susceptibility</i> , <i>Section 6.3.16: I/O port characteristics</i> and <i>Section 6.3.17: NRST pin characteristics</i> .<br>Removed note 3 in <i>Table 69: Temperature sensor characteristics</i> .<br>Updated <i>Figure 79: WLCSP64+2 - 0.400 mm pitch wafer level chip size package outline</i> and <i>Table 88: WLCSP64+2 - 0.400 mm pitch wafer level chip size package mechanical data</i> . Added <i>Figure 83: LQFP100 marking (package top view)</i> and <i>Figure 86: LQFP144 marking (package top view)</i> . |  |

| 2-Feb-2016                                      | 13                | <ul> <li>Updated Section 1: Introduction.</li> <li>Updated Table 32: HSI oscillator characteristics and its footnotes.</li> <li>Updated Figure 36: PLL output clock waveforms in center spread mode,<br/>Figure 37: PLL output clock waveforms in down spread mode,<br/>Figure 54: Power supply and reference decoupling (VREF+ not<br/>connected to VDDA) and Figure 55: Power supply and reference<br/>decoupling (VREF+ connected to VDDA).</li> <li>Updated Section 7: Package information and its subsections.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |  |

Table 97. Document revision history (continued)