Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>Details</b>            |                                                                                         |

|---------------------------|-----------------------------------------------------------------------------------------|

| roduct Status             | Active                                                                                  |

| Core Processor            | ARM® Cortex®-M3                                                                         |

| Core Size                 | 32-Bit Single-Core                                                                      |

| peed                      | 120MHz                                                                                  |

| onnectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, Memory Card, SPI, UART/USART, USB OTG |

| eripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                       |

| umber of I/O              | 140                                                                                     |

| rogram Memory Size        | 256KB (256K x 8)                                                                        |

| ogram Memory Type         | FLASH                                                                                   |

| EPROM Size                | -                                                                                       |

| AM Size                   | 132K x 8                                                                                |

| oltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                             |

| ata Converters            | A/D 24x12b; D/A 2x12b                                                                   |

| scillator Type            | Internal                                                                                |

| perating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| ounting Type              | Surface Mount                                                                           |

| ackage / Case             | 176-LQFP                                                                                |

| upplier Device Package    | 176-LQFP (24x24)                                                                        |

| ırchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f207ict6                   |

List of tables STM32F20xxx

# List of tables

| Table 1.  | Device summary                                                                 | 1     |

|-----------|--------------------------------------------------------------------------------|-------|

| Table 2.  | STM32F205xx features and peripheral counts                                     |       |

| Table 3.  | STM32F207xx features and peripheral counts                                     |       |

| Table 4.  | Regulator ON/OFF and internal reset ON/OFF availability                        |       |

| Table 5.  | Timer feature comparison                                                       |       |

| Table 6.  | USART feature comparison                                                       |       |

| Table 7.  | Legend/abbreviations used in the pinout table                                  |       |

| Table 8.  | STM32F20x pin and ball definitions                                             |       |

| Table 9.  | FSMC pin definition                                                            |       |

| Table 10. | Alternate function mapping                                                     |       |

| Table 11. | Voltage characteristics                                                        |       |

| Table 12. | Current characteristics                                                        |       |

| Table 13. | Thermal characteristics                                                        |       |

| Table 14. | General operating conditions                                                   |       |

| Table 15. | Limitations depending on the operating power supply range                      |       |

| Table 16. | VCAP1/VCAP2 operating conditions                                               |       |

| Table 17. | Operating conditions at power-up / power-down (regulator ON)                   |       |

| Table 18. | Operating conditions at power-up / power-down (regulator OFF)                  |       |

| Table 19. | Embedded reset and power control block characteristics                         |       |

| Table 20. | Typical and maximum current consumption in Run mode, code with data processing |       |

|           | running from Flash memory (ART accelerator enabled) or RAM                     | 78    |

| Table 21. | Typical and maximum current consumption in Run mode, code with data processing |       |

|           | running from Flash memory (ART accelerator disabled)                           | 79    |

| Table 22. | Typical and maximum current consumption in Sleep mode                          |       |

| Table 23. | Typical and maximum current consumptions in Stop mode                          |       |

| Table 24. | Typical and maximum current consumptions in Standby mode                       |       |

| Table 25. | Typical and maximum current consumptions in V <sub>BAT</sub> mode              |       |

| Table 26. | Peripheral current consumption                                                 |       |

| Table 27. | Low-power mode wakeup timings                                                  | 88    |

| Table 28. | High-speed external user clock characteristics                                 | 89    |

| Table 29. | Low-speed external user clock characteristics                                  | 89    |

| Table 30. | HSE 4-26 MHz oscillator characteristics                                        | 91    |

| Table 31. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                 | 92    |

| Table 32. | HSI oscillator characteristics                                                 | 92    |

| Table 33. | LSI oscillator characteristics                                                 | 93    |

| Table 34. | Main PLL characteristics                                                       | 94    |

| Table 35. | PLLI2S (audio PLL) characteristics                                             | 95    |

| Table 36. | SSCG parameters constraint                                                     | 97    |

| Table 37. | Flash memory characteristics                                                   | 99    |

| Table 38. | Flash memory programming                                                       | 99    |

| Table 39. | Flash memory programming with V <sub>PP</sub>                                  |       |

| Table 40. | Flash memory endurance and data retention                                      | . 100 |

| Table 41. | EMS characteristics                                                            | . 101 |

| Table 42. | EMI characteristics                                                            |       |

| Table 43. | ESD absolute maximum ratings                                                   | . 102 |

| Table 44. | Electrical sensitivities                                                       |       |

| Table 45. | I/O current injection susceptibility                                           | . 103 |

| Table 46. | I/O static characteristics                                                     | . 104 |

STM32F20xxx List of figures

| LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline      | 158                                                                              |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------|

|                                                                          | 160                                                                              |

| · ·                                                                      |                                                                                  |

| LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline      |                                                                                  |

| LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package              |                                                                                  |

| recommended footprint                                                    | 164                                                                              |

| UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch,                       |                                                                                  |

| ultra fine pitch ball grid array package outline                         | 165                                                                              |

| UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball |                                                                                  |

| grid array package recommended footprint                                 | 166                                                                              |

|                                                                          | LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package recommended footprint |

Functional overview STM32F20xxx

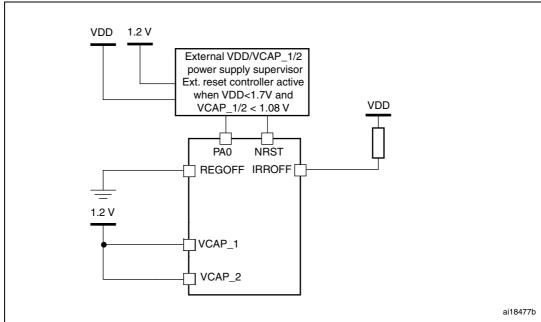

Figure 7. Regulator OFF/internal reset OFF

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains (see *Figure 8*).

- PA0 should be kept low to cover both conditions: until  $V_{CAP\_1}$  and  $V_{CAP\_2}$  reach 1.08 V, and until  $V_{DD}$  reaches 1.7 V.

- NRST should be controlled by an external reset controller to keep the device under reset when V<sub>DD</sub> is below 1.7 V (see *Figure 9*).

In this mode, when the internal reset is OFF, the following integrated features are no more supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled.

- The brownout reset (BOR) circuitry is disabled.

- The embedded programmable voltage detector (PVD) is disabled.

- V<sub>BAT</sub> functionality is no more available and V<sub>BAT</sub> pin should be connected to VDD.

Functional overview STM32F20xxx

## 3.16.3 Regulator ON/OFF and internal reset ON/OFF availability

Table 4. Regulator ON/OFF and internal reset ON/OFF availability

| Package                                 | Regulator ON/internal reset ON                     | Regulator<br>OFF/internal reset ON                    | Regulator OFF/internal reset OFF                                    |

|-----------------------------------------|----------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------|

| LQFP64<br>LQFP100<br>LQFP144<br>LQFP176 | Yes                                                | No                                                    | No                                                                  |

| WLCSP 64+2                              | Yes<br>REGOFF and IRROFF<br>set to V <sub>SS</sub> | Yes REGOFF set to $V_{DD}$ and IRROFF set to $V_{SS}$ | Yes REGOFF set to V <sub>SS</sub> and IRROFF set to V <sub>DD</sub> |

| UFBGA176                                | Yes<br>REGOFF set to V <sub>SS</sub>               | Yes<br>REGOFF set to V <sub>DD</sub>                  | No                                                                  |

# 3.17 Real-time clock (RTC), backup SRAM and backup registers

The backup domain of the STM32F20x devices includes:

- The real-time clock (RTC)

- 4 Kbytes of backup SRAM

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Its main features are the following:

- Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28, 29 (leap year), 30, and 31 day of the month.

- Programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes.

- It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal low-power RC oscillator or the high-speed external clock divided by 128. The internal low-speed RC has a typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation.

- Two alarm registers are used to generate an alarm at a specific time and calendar fields can be independently masked for alarm comparison. To generate a periodic interrupt, a 16-bit programmable binary auto-reload downcounter with programmable resolution is available and allows automatic wakeup and periodic alarms from every 120 µs to every 36 hours.

- A 20-bit prescaler is used for the time base clock. It is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

The 4-Kbyte backup SRAM is an EEPROM-like area. It can be used to store data which need to be retained in VBAT and standby mode. This memory area is disabled to minimize power consumption (see *Section 3.18: Low-power modes*). It can be enabled by software.

STM32F20xxx Functional overview

The backup registers are 32-bit registers used to store 80 bytes of user application data when V<sub>DD</sub> power is not present. Backup registers are not reset by a system, a power reset, or when the device wakes up from the Standby mode (see Section 3.18: Low-power modes).

Like backup SRAM, the RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or the  $V_{BAT}$  pin.

# 3.18 Low-power modes

The STM32F20x family supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

## Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

### Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from the Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup.

### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

Note:

The RTC, the IWDG, and the corresponding clock sources are not stopped when the device enters the Stop or Standby mode.

# 3.19 V<sub>BAT</sub> operation

The  $V_{BAT}$  pin allows to power the device  $V_{BAT}$  domain from an external battery or an external supercapacitor.

V<sub>BAT</sub> operation is activated when V<sub>DD</sub> is not present.

The VBAT pin supplies the RTC, the backup registers and the backup SRAM.

Note:

When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

When using WLCSP64+2 package, if IRROFF pin is connected to  $V_{DD}$ , the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to  $V_{DD}$ .

Table 8. STM32F20x pin and ball definitions

|        |           | Pi      | ns      |         |          |                                                      |          |               |        | ball definitions                                     |                          |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|--------|------------------------------------------------------|--------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note   | Alternate functions                                  | Additional<br>functions  |

| -      | -         | 1       | 1       | 1       | A2       | PE2                                                  | I/O      | FT            | -      | TRACECLK, FSMC_A23,<br>ETH_MII_TXD3, EVENTOUT        | -                        |

| -      | -         | 2       | 2       | 2       | A1       | PE3                                                  | I/O      | FT            | -      | TRACED0,FSMC_A19,<br>EVENTOUT                        | -                        |

| -      | -         | 3       | 3       | 3       | B1       | PE4                                                  | I/O      | FT            | -      | TRACED1,FSMC_A20,<br>DCMI_D4, EVENTOUT               | -                        |

| -      | 1         | 4       | 4       | 4       | B2       | PE5                                                  | I/O      | FT            | -      | TRACED2, FSMC_A21,<br>TIM9_CH1, DCMI_D6,<br>EVENTOUT | -                        |

| -      | 1         | 5       | 5       | 5       | В3       | PE6                                                  | I/O      | FT            | -      | TRACED3, FSMC_A22,<br>TIM9_CH2, DCMI_D7,<br>EVENTOUT | -                        |

| 1      | A9        | 6       | 6       | 6       | C1       | V <sub>BAT</sub>                                     | S        |               | -      | -                                                    | -                        |

| -      | -         | -       | ı       | 7       | D2       | PI8                                                  | I/O      | FT            | (2)(3) | EVENTOUT                                             | RTC_AF2                  |

| 2      | В8        | 7       | 7       | 8       | D1       | PC13                                                 | I/O      | FT            | (2)(3) | EVENTOUT                                             | RTC_AF1                  |

| 3      | В9        | 8       | 8       | 9       | E1       | PC14/OSC32_IN<br>(PC14)                              | I/O      | FT            | (2)(3) | EVENTOUT                                             | OSC32_IN <sup>(4)</sup>  |

| 4      | C9        | 9       | 9       | 10      | F1       | PC15-OSC32_OUT<br>(PC15)                             | I/O      | FT            | (2)(3) | EVENTOUT                                             | OSC32_OUT <sup>(4)</sup> |

| -      | -         | -       | -       | 11      | D3       | PI9                                                  | I/O      | FT            | -      | CAN1_RX,EVENTOUT                                     | -                        |

| -      | -         | -       | i       | 12      | E3       | PI10                                                 | I/O      | FT            | -      | ETH_MII_RX_ER,<br>EVENTOUT                           | -                        |

| -      | 1         | -       | 1       | 13      | E4       | PI11                                                 | I/O      | FT            | -      | OTG_HS_ULPI_DIR,<br>EVENTOUT                         | -                        |

| -      | -         | -       | 1       | 14      | F2       | $V_{SS}$                                             | S        |               | -      | -                                                    | -                        |

| -      | -         | -       | -       | 15      | F3       | $V_{DD}$                                             | S        |               | -      | -                                                    | -                        |

| -      | -         | -       | 10      | 16      | E2       | PF0                                                  | I/O      | FT            | -      | FSMC_A0, I2C2_SDA,<br>EVENTOUT                       | -                        |

| -      | -         | -       | 11      | 17      | Н3       | PF1                                                  | I/O      | FT            | -      | FSMC_A1, I2C2_SCL,<br>EVENTOUT                       | -                        |

| -      | -         | -       | 12      | 18      | H2       | PF2                                                  | I/O      | FT            | -      | FSMC_A2, I2C2_SMBA,<br>EVENTOUT                      | -                        |

| -      | -         | -       | 13      | 19      | J2       | PF3                                                  | I/O      | FT            | (4)    | FSMC_A3, EVENTOUT                                    | ADC3_IN9                 |

# 6.1.7 Current consumption measurement

IDD\_VBAT VBAT IDD VDD VDDA

Figure 20. Current consumption measurement scheme

# 6.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                                | Ratings                                                                       | Min                                                      | Max                | Unit |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------|--------------------|------|

| $V_{DD}$ – $V_{SS}$                                                   | External main supply voltage (including $V_{DDA}$ , $V_{DD}$ ) <sup>(1)</sup> | -0.3                                                     | 4.0                |      |

| \/                                                                    | Input voltage on five-volt tolerant pin <sup>(2)</sup>                        |                                                          | V <sub>DD</sub> +4 | V    |

| V <sub>IN</sub>                                                       | Input voltage on any other pin                                                | V <sub>SS</sub> -0.3                                     | 4.0                |      |

| $ \Delta V_{DDx} $                                                    | Variations between different V <sub>DD</sub> power pins                       | -                                                        | 50                 | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub>                                     | Variations between all the different ground pins                              | -                                                        | 50                 | IIIV |

| V <sub>ESD(HBM)</sub> Electrostatic discharge voltage (human body mod |                                                                               | see Sectio<br>Absolute n<br>ratings (ele<br>sensitivity) | naximum            | -    |

Table 11. Voltage characteristics

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

V<sub>IN</sub> maximum value must always be respected. Refer to *Table 12* for the values of the maximum allowed injected current.

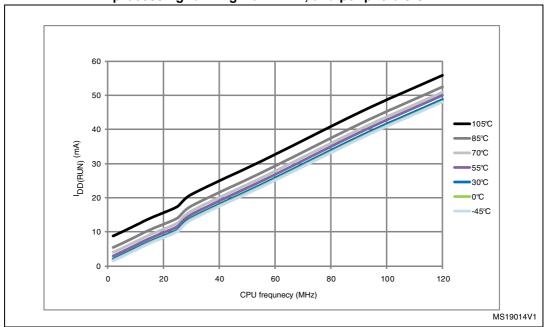

Figure 23. Typical current consumption vs. temperature, Run mode, code with data processing running from RAM, and peripherals ON

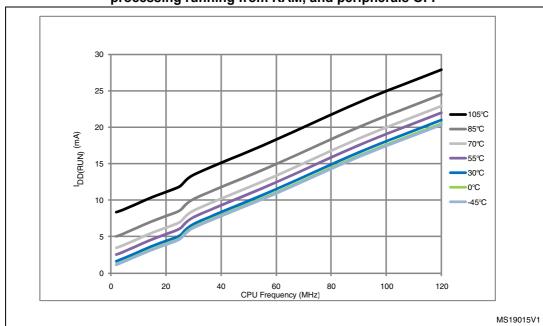

Figure 24. Typical current consumption vs. temperature, Run mode, code with data processing running from RAM, and peripherals OFF

## On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 26*. The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog inputs by firmware.

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with one peripheral clocked on (with only the clock applied)

- The code is running from Flash memory and the Flash memory access time is equal to 3 wait states at 120 MHz

- Prefetch and Cache ON

- When the peripherals are enabled, HCLK = 120MHz,  $f_{PCLK1} = f_{HCLK}/4$ , and  $f_{PCLK2} = f_{HCLK}/2$

- The typical values are obtained for V<sub>DD</sub> = 3.3 V and T<sub>A</sub>= 25 °C, unless otherwise specified.

Table 26. Peripheral current consumption

| F     | Peripheral <sup>(1)</sup>                   | Typical consumption at 25 °C | Unit |

|-------|---------------------------------------------|------------------------------|------|

|       | GPIO A                                      | 0.45                         |      |

|       | GPIO B                                      | 0.43                         |      |

|       | GPIO C                                      | 0.46                         |      |

|       | GPIO D                                      | 0.44                         |      |

|       | GPIO E                                      | 0.44                         |      |

|       | GPIO F                                      | 0.42                         |      |

|       | GPIO G                                      | 0.44                         |      |

|       | GPIO H                                      | 0.42                         |      |

| AHB1  | GPIO I                                      | 0.43                         |      |

|       | OTG_HS + ULPI                               | 3.64                         |      |

|       | CRC                                         | 1.17                         | mA   |

|       | BKPSRAM                                     | 0.21                         |      |

|       | DMA1                                        | 2.76                         |      |

|       | DMA2                                        | 2.85                         |      |

|       | ETH_MAC + ETH_MAC_TX ETH_MAC_RX ETH_MAC_PTP | 2.99                         |      |

| AHB2  | OTG_FS                                      | 3.16                         |      |

| AIIDE | DCMI                                        | 0.60                         |      |

| AHB3  | FSMC                                        | 1.74                         |      |

|      | Peripheral <sup>(1)</sup> | Typical consumption at 25 °C | Unit |

|------|---------------------------|------------------------------|------|

|      | SDIO                      | 0.69                         |      |

|      | TIM1                      | 1.06                         |      |

|      | TIM8                      | 1.03                         |      |

|      | TIM9                      | 0.58                         |      |

|      | TIM10                     | 0.37                         |      |

| APB2 | TIM11                     | 0.39                         | mA   |

| AFDZ | ADC1 <sup>(4)</sup>       | 2.13                         | IIIA |

|      | ADC2 <sup>(4)</sup>       | 2.04                         |      |

|      | ADC3 <sup>(4)</sup>       | 2.12                         |      |

|      | SPI1                      | 1.20                         |      |

|      | USART1                    | 0.38                         |      |

|      | USART6                    | 0.37                         |      |

Table 26. Peripheral current consumption (continued)

- 1. External clock is 25 MHz (HSE oscillator with 25 MHz crystal) and PLL is on.

- 2. EN1 bit is set in DAC\_CR register.

- 3. EN2 bit is set in DAC\_CR register.

- 4. f<sub>ADC</sub> = f<sub>PCLK2</sub>/2, ADON bit set in ADC\_CR2 register.

## 6.3.7 Wakeup time from low-power mode

The wakeup times given in *Table 27* is measured on a wakeup phase with a 16 MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                             | Parameter                                                                                    | Min <sup>(1)</sup> | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit     |

|------------------------------------|----------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|----------|

| t <sub>WUSLEEP</sub> (2)           | Vakeup from Sleep mode                                                                       |                    | 1                  | -                  | μs       |

| t <sub>WUSTOP</sub> <sup>(2)</sup> | Wakeup from Stop mode (regulator in Run mode)                                                | -                  | 13                 | -                  |          |

|                                    | Wakeup from Stop mode (regulator in low-power mode)                                          | -                  | 17                 | 40                 | μs       |

|                                    | Wakeup from Stop mode (regulator in low-power mode and Flash memory in Deep power down mode) | -                  | 110                | -                  | <b>,</b> |

| t <sub>WUSTDBY</sub> (2)(3)        | Wakeup from Standby mode                                                                     | 260                | 375                | 480                | μs       |

Table 27. Low-power mode wakeup timings

**577**

<sup>1.</sup> Guaranteed by characterization results, not tested in production.

<sup>2.</sup> The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

<sup>3.</sup>  $t_{WUSTDBY}$  minimum and maximum values are given at 105 °C and –45 °C, respectively.

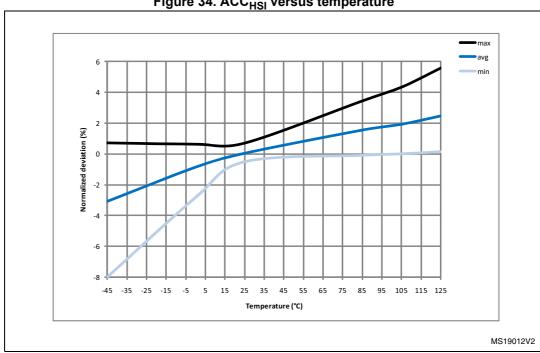

Figure 34. ACC<sub>HSI</sub> versus temperature

# Low-speed internal (LSI) RC oscillator

Table 33. LSI oscillator characteristics (1)

| Symbol                              | Parameter                        | Min | Тур | Max | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> (3)            | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

- 1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

- 2. Guaranteed by characterization results, not tested in production.

- 3. Guaranteed by design, not tested in production.

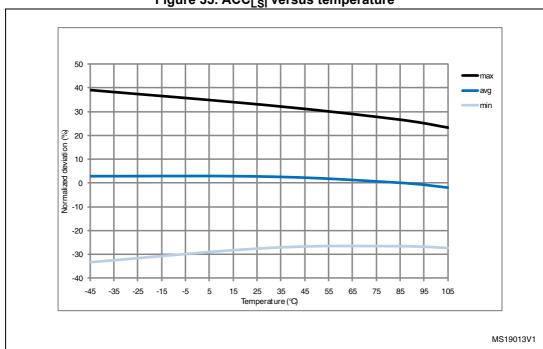

Figure 35. ACC<sub>LSI</sub> versus temperature

# 6.3.10 PLL characteristics

The parameters given in *Table 34* and *Table 35* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                 | Parameter                          | Conditions         | Min                 | Тур | Max                 | Unit |

|------------------------|------------------------------------|--------------------|---------------------|-----|---------------------|------|

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(1)</sup>     | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 <sup>(2)</sup> | MHz  |

| f <sub>PLL_OUT</sub>   | PLL multiplier output clock        | -                  | 24                  | -   | 120                 | MHz  |

| f <sub>PLL48_OUT</sub> | 48 MHz PLL multiplier output clock | -                  | -                   | -   | 48                  | MHz  |

| f <sub>VCO_OUT</sub>   | PLL VCO output                     | -                  | 192                 | -   | 432                 | MHz  |

| 4                      | PLL lock time                      | VCO freq = 192 MHz | 75                  | -   | 200                 | 116  |

| t <sub>LOCK</sub>      | PLL lock time                      | VCO freq = 432 MHz | 100                 | -   | 300                 | μs   |

**Table 34. Main PLL characteristics**

Table 35. PLLI2S (audio PLL) characteristics (continued)

| Symbol                                 | Parameter                                 | Conditions                                                          |                    | Min          | Тур  | Max          | Unit |

|----------------------------------------|-------------------------------------------|---------------------------------------------------------------------|--------------------|--------------|------|--------------|------|

| Jitter <sup>(3)</sup>                  |                                           | Cycle to cycle at                                                   | RMS                | ı            | 90   | i            |      |

|                                        | Master I2S clock jitter                   | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                        | peak<br>to<br>peak | -            | ±280 | -            | ps   |

|                                        |                                           | Average frequency of<br>12.288 MHz<br>N=432, R=5<br>on 1000 samples |                    | -            | 90   | -            | ps   |

|                                        | WS I2S clock jitter                       | Cycle to cycle at 48 KHz on 1000 samples                            |                    | -            | 400  | -            | ps   |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on $V_{DD}$      | VCO freq = 192 MHz<br>VCO freq = 432 MHz                            |                    | 0.15<br>0.45 | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> (4)           | PLLI2S power consumption on $V_{\rm DDA}$ | VCO freq = 192 MHz<br>VCO freq = 432 MHz                            |                    | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA   |

<sup>1.</sup> Take care of using the appropriate division factor M to have the specified PLL input clock values.

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>3.</sup> Value given with main PLL running.

<sup>4.</sup> Guaranteed by characterization results, not tested in production.

| Symbol                            | Parameter                                                                     | Conditions                          | Min                  | Max | Unit        |

|-----------------------------------|-------------------------------------------------------------------------------|-------------------------------------|----------------------|-----|-------------|

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | CMOS ports                          | -                    | 0.4 | V           |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2.7 V < V <sub>DD</sub> < 3.6 V     | V <sub>DD</sub> -0.4 | -   | V           |

| V <sub>OL</sub> (2)               | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | TTL ports<br>I <sub>IO</sub> =+ 8mA | -                    | 0.4 | >           |

| V <sub>OH</sub> (3)               | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2.7 V < V <sub>DD</sub> < 3.6 V     | 2.4                  | -   | V           |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +20 mA            | -                    | 1.3 | V           |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2.7 V < V <sub>DD</sub> < 3.6 V     | V <sub>DD</sub> -1.3 | -   | V           |

| V <sub>OL</sub> <sup>(2)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +6 mA             | -                    | 0.4 | V           |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2 V < V <sub>DD</sub> < 2.7 V       | V <sub>DD</sub> -0.4 | -   | <b>&gt;</b> |

Table 47. Output voltage characteristics<sup>(1)</sup>

## Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 39* and *Table 48*, respectively.

Unless otherwise specified, the parameters given in *Table 48* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

Table 48. I/O AC characteristics<sup>(1)</sup>

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                                                            | Parameter            | Conditions                                               | Min | Тур | Max | Unit    |

|-----------------------------------------------|-----------------------------------------------------------------------------------|----------------------|----------------------------------------------------------|-----|-----|-----|---------|

|                                               |                                                                                   |                      | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 2.70 V      | -   | -   | 4   |         |

|                                               | f N                                                                               | Maximum frequency(2) | $C_L = 50 \text{ pF}, V_{DD} > 1.8 \text{ V}$            | -   | 1   | 2   | MHz     |

| , ,                                           | † <sub>max(IO)out</sub>                                                           |                      | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V      | -   | -   | 8   | IVII IZ |

| 00                                            | 00                                                                                |                      | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V       | -   | -   | 4   |         |

|                                               | t <sub>f(IO)out</sub> / Output high to low level fall time and output low to high |                      | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.8 V to 3.6 V | ı   | -   | 100 | ns      |

PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. to drive an LED).

<sup>2.</sup> The  $I_{|O}$  current sunk by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of  $I_{|O|}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

<sup>3.</sup> The  $I_{\rm IO}$  current sourced by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of  $I_{\rm IO}$  (I/O ports and control pins) must not exceed  $I_{\rm VDD}$ .

<sup>4.</sup> Guaranteed by characterization results, not tested in production.

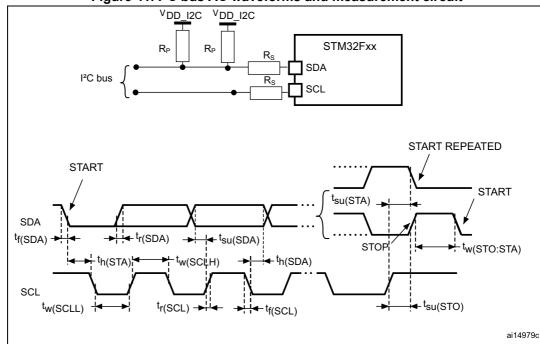

Figure 41. I<sup>2</sup>C bus AC waveforms and measurement circuit

- 1. R<sub>S</sub>= series protection resistor.

- 2. R<sub>P</sub> = external pull-up resistor.

- 3.  $V_{DD\ I2C}$  is the  $I^2C$  bus power supply.

Table 53. SCL frequency  $(f_{PCLK1} = 30 \text{ MHz.}, V_{DD} = 3.3 \text{ V})^{(1)(2)}$

| £ (kHz)                | I2C_CCR value               |

|------------------------|-----------------------------|

| f <sub>SCL</sub> (kHz) | $R_P = 4.7 \text{ k}\Omega$ |

| 400                    | 0x8019                      |

| 300                    | 0x8021                      |

| 200                    | 0x8032                      |

| 100                    | 0x0096                      |

| 50                     | 0x012C                      |

| 20                     | 0x02EE                      |

- 1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed,

- 2. For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

| Symbol                             | Parameter                                                                                                 | Min | Тур         | Max | Unit | Comments                                                                                                                                                              |

|------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Update rate <sup>(2)</sup>         | Max frequency for a correct DAC_OUT change when small variation in the input code (from code i to i+1LSB) | -   | -           | 1   | MS/s | $C_{LOAD} \le 50 \text{ pF},$ $R_{LOAD} \ge 5 \text{ k}\Omega$                                                                                                        |

| t <sub>WAKEUP</sub> <sup>(4)</sup> | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                        | -   | 6.5         | 10  | μs   | $\begin{split} &C_{LOAD} \leq 50 \text{ pF, } R_{LOAD} \geq 5 \text{ k}\Omega \\ &\text{input code between lowest and highest} \\ &\text{possible ones.} \end{split}$ |

| PSRR+ (2)                          | Power supply rejection ratio (to V <sub>DDA</sub> ) (static DC measurement)                               | -   | <b>–</b> 67 | -40 | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                                                                      |

Table 68. DAC characteristics (continued)

- On devices in WLCSP64+2 package, if IRROFF is set to  $V_{DD}$ , the supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

- 2. Guaranteed by design, not tested in production.

- The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

- 4. Guaranteed by characterization results, not tested in production.

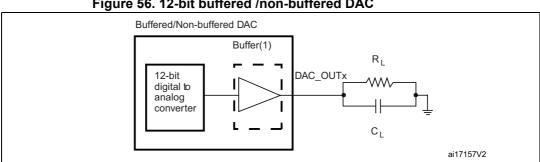

Figure 56. 12-bit buffered /non-buffered DAC

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly, without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

#### 6.3.22 **Temperature sensor characteristics**

Table 69. Temperature sensor characteristics

| Symbol                             | Parameter                                                      | Min | Тур  | Max       | Unit  |

|------------------------------------|----------------------------------------------------------------|-----|------|-----------|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature                  | -   | ±1   | <u>+2</u> | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                                  | -   | 2.5  | -         | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>     | Voltage at 25 °C                                               | -   | 0.76 | -         | V     |

| t <sub>START</sub> (2)             | Startup time                                                   | -   | 6    | 10        | μs    |

| T <sub>S_temp</sub> <sup>(2)</sup> | ADC sampling time when reading the temperature (1 °C accuracy) | 10  | -    | -         | μs    |

- 1. Guaranteed by characterization results, not tested in production.

- 2. Guaranteed by design, not tested in production.

Table 74. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup> (continued)

| Symbol                   | Parameter                          | Min | Max | Unit |

|--------------------------|------------------------------------|-----|-----|------|

| t <sub>h(Data_NE)</sub>  | Data hold time after FSMC_NEx high | 0   | -   | ns   |

| t <sub>h(Data_NOE)</sub> | Data hold time after FSMC_NOE high | 0   | -   | ns   |

<sup>1.</sup> C<sub>L</sub> = 30 pF.

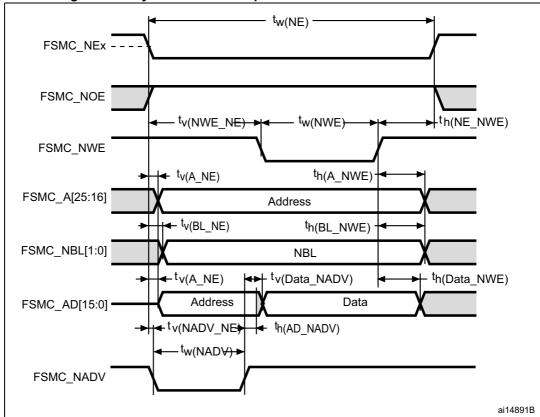

Figure 60. Asynchronous multiplexed PSRAM/NOR write waveforms

Table 75. Asynchronous multiplexed PSRAM/NOR write timings<sup>(1)(2)</sup>

| ·                       |                                                       |                       |                       |      |  |

|-------------------------|-------------------------------------------------------|-----------------------|-----------------------|------|--|

| Symbol                  | Parameter                                             | Min                   | Max                   | Unit |  |

| $t_{w(NE)}$             | FSMC_NE low time                                      | 4T <sub>HCLK</sub> -1 | 4T <sub>HCLK</sub> +1 | ns   |  |

| t <sub>v(NWE_NE)</sub>  | FSMC_NEx low to FSMC_NWE low                          | T <sub>HCLK</sub> - 1 | T <sub>HCLK</sub>     | ns   |  |

| t <sub>w(NWE)</sub>     | FSMC_NWE low tim e                                    | 2T <sub>HCLK</sub>    | 2T <sub>HCLK</sub> +1 | ns   |  |

| t <sub>h(NE_NWE)</sub>  | FSMC_NWE high to FSMC_NE high hold time               | T <sub>HCLK</sub> - 1 | -                     | ns   |  |

| t <sub>v(A_NE)</sub>    | FSMC_NEx low to FSMC_A valid                          | -                     | 0                     | ns   |  |

| t <sub>v(NADV_NE)</sub> | FSMC_NEx low to FSMC_NADV low                         | 1                     | 2                     | ns   |  |

| t <sub>w(NADV)</sub>    | FSMC_NADV low time                                    | T <sub>HCLK</sub> -2  | T <sub>HCLK</sub> + 2 | ns   |  |

| t <sub>h(AD_NADV)</sub> | FSMC_AD(adress) valid hold time after FSMC_NADV high) | T <sub>HCLK</sub>     | -                     | ns   |  |

<sup>2.</sup> Guaranteed by characterization results, not tested in production.

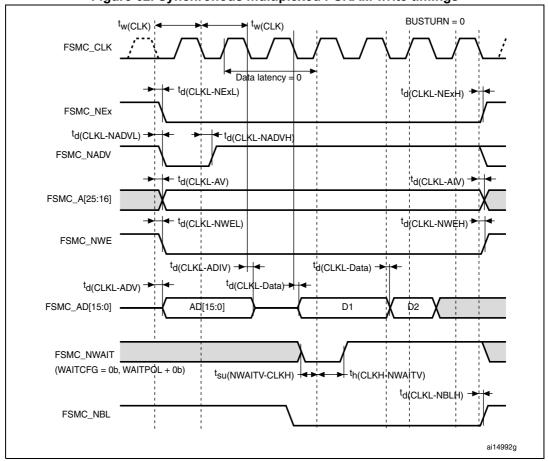

Table 76. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

| Symbol                    | Parameter                                      | Min | Max | Unit |

|---------------------------|------------------------------------------------|-----|-----|------|

| t <sub>su(ADV-CLKH)</sub> | FSMC_A/D[15:0] valid data before FSMC_CLK high | 5   | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>  | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0   | -   | ns   |

<sup>1.</sup>  $C_L = 30 pF$ .

Figure 62. Synchronous multiplexed PSRAM write timings

Table 77. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                     | Parameter                                | Min                    | Max | Unit |

|----------------------------|------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                          | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)      | -                      | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)    | 2                      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low            | -                      | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high           | 3                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)   | -                      | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625) | 7                      | -   | ns   |

<sup>2.</sup> Guaranteed by characterization results, not tested in production.

#### **Package information** 7

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK<sup>®</sup> is an ST trademark.

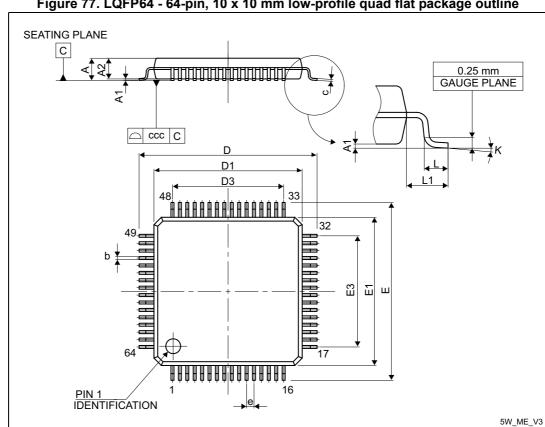

#### LQFP64 package information 7.1

Figure 77. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline

1. Drawing is not to scale.

Table 87. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package mechanical data

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |  |

| Α      | -           | -     | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170       | 0.220 | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

Revision history STM32F20xxx

Table 97. Document revision history (continued)

| Date        | Revision      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-Dec-2011 | 8 (continued) | Added maximum power consumption at T <sub>A</sub> =25 °C in Table 23: Typical and maximum current consumptions in Stop mode.  Updated md minimum value in Table 36: SSCG parameters constraint.  Added examples in Section 6.3.11: PLL spread spectrum clock generation (SSCG) characteristics.  Updated Table 54: SPI characteristics and Table 55: I2S characteristics.  Updated Figure 48: ULPI timing diagram and Table 61: ULPI timing.  Updated Table 63: Dynamics characteristics: Ethernet MAC signals for SMI, Table 64: Dynamics characteristics: Ethernet MAC signals for RMII, and Table 65: Dynamics characteristics: Ethernet MAC signals for MII.  Section 6.3.25: FSMC characteristics: updated Table 72 to Table 83, changed C <sub>L</sub> value to 30 pF, and modified FSMC configuration for asynchronous timings and waveforms. Updated Figure 62: Synchronous multiplexed PSRAM write timings.  Updated Table 84: DCMI characteristics.  Updated Table 92: UFBGA176+25 - ultra thin fine pitch ball grid array 10 × 10 × 0.6 mm mechanical data.  Updated Table 96: Ordering information scheme.  Appendix A.2: USB OTG FS (full speed) host-only connection and added Note 2, updated Figure 88: OTG FS (full speed) connection dual-role with internal PHY and added Note 3 and Note 4, modified Figure 89: OTG HS (high speed) device connection, host and dual-role in high-speed mode with external PHY and added Note 2.  Appendix A.3: USB OTG high speed (HS) interface solutions: removed figures USB OTG HS device-only connection in FS mode and USB OTG HS host-only connection in FS mode, updated Figure 89: OTG HS (high speed) device connection, host and dual-role in high-speed mode with external PHY.  Added Appendix A.4: Ethernet interface solutions.  Updated disclaimer on last page. |

| 24-Apr-2012 | 9             | Updated V <sub>DD</sub> minimum value in <i>Section 2: Description</i> .  Updated number of USB OTG HS and FS, modified packages for STM32F207lx part numbers, added <i>Note 1</i> related to FSMC and <i>Note 2</i> related to SPI/I2S, and updated <i>Note 3</i> in <i>Table 2: STM32F205xx</i> features and peripheral counts and <i>Table 3: STM32F207xx</i> features and peripheral counts.  Added <i>Note 2</i> and update TIM5 in <i>Figure 4: STM32F20x block diagram</i> . Updated maximum number of maskable interrupts in <i>Section 3.10: Nested vectored interrupt controller (NVIC)</i> .  Updated V <sub>DD</sub> minimum value in <i>Section 3.14: Power supply schemes</i> . Updated <i>Note a</i> in <i>Section 3.16.1: Regulator ON</i> .  Removed STM32F205xx in <i>Section 3.28: Universal serial bus on-the-go full-speed (OTG_FS)</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |