Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 120MHz                                                                                  |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, Memory Card, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                       |

| Number of I/O              | 140                                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 132К х 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                   |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 201-UFBGA                                                                               |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f207ieh6tr                 |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.1 Full compatibility throughout the family

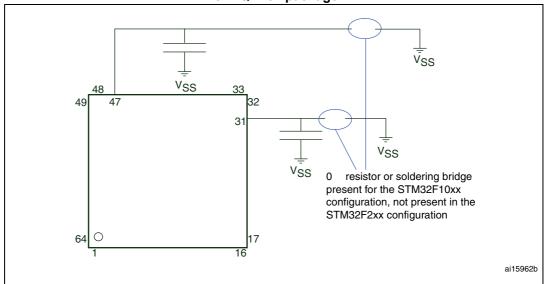

The STM32F205xx and STM32F207xx constitute the STM32F20x family whose members are fully pin-to-pin, software and feature compatible, allowing the user to try different memory densities and peripherals for a greater degree of freedom during the development cycle.

The STM32F205xx and STM32F207xx devices maintain a close compatibility with the whole STM32F10xxx family. All functional pins are pin-to-pin compatible. The STM32F205xx and STM32F207xx, however, are not drop-in replacements for the STM32F10xxx devices: the two families do not have the same power scheme, and so their power pins are different. Nonetheless, transition from the STM32F10xxx to the STM32F20x family remains simple as only a few pins are impacted.

*Figure 1*, *Figure 2* and *Figure 3* provide compatible board designs between the STM32F20x and the STM32F10xxx family.

Figure 1. Compatible board design between STM32F10xx and STM32F2xx for LQFP64 package

### 3.4 Embedded Flash memory

The STM32F20x devices embed a 128-bit wide Flash memory of 128 Kbytes, 256 Kbytes, 512 Kbytes, 768 Kbytes or 1 Mbyte available for storing programs and data.

The devices also feature 512 bytes of OTP memory that can be used to store critical user data such as Ethernet MAC addresses or cryptographic keys.

### 3.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

### 3.6 Embedded SRAM

All STM32F20x products embed:

- Up to 128 Kbytes of system SRAM accessed (read/write) at CPU clock speed with 0 wait states

- 4 Kbytes of backup SRAM.

The content of this area is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

### 3.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS) and the slaves (Flash memory, RAM, FSMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

### 3.20.4 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes. The counter can be frozen in debug mode.

### 3.20.5 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 3.20.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source

### 3.21 Inter-integrated circuit interface (I<sup>2</sup>C)

Up to three I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support the Standard- and Fast-modes. They support the 7/10-bit addressing mode and the 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

## 3.22 Universal synchronous/asynchronous receiver transmitters (UARTs/USARTs)

The STM32F20x devices embed four universal synchronous/asynchronous receiver transmitters (USART1, USART2, USART3 and USART6) and two universal asynchronous receiver transmitters (UART4 and UART5).

These six interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability. The USART1 and USART6 interfaces are able to communicate at speeds of up to 7.5 Mbit/s. The other available interfaces communicate at up to 3.75 Mbit/s.

USART1, USART2, USART3 and USART6 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller.

DocID15818 Rev 13

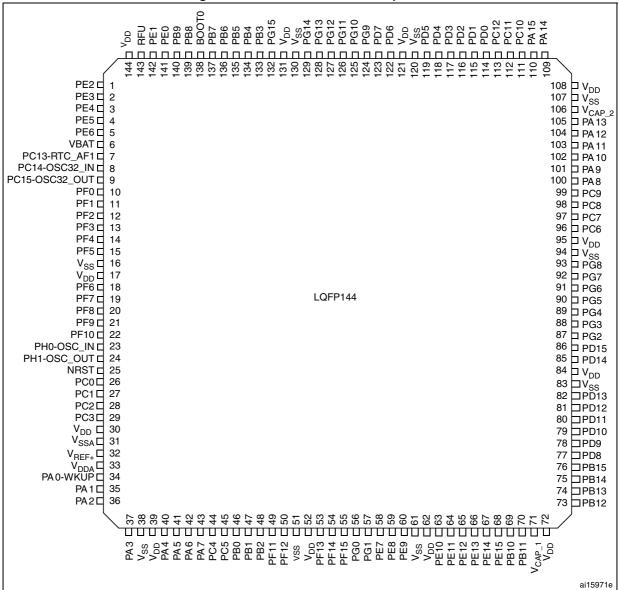

Figure 13. STM32F20x LQFP144 pinout

1. RFU means "reserved for future use". This pin can be tied to  $V_{DD}$ ,  $V_{SS}$  or left unconnected.

2. The above figure shows the package top view.

|        |           | Pi      | ns      |         |          |                                                      |          |               |      |                                                                                                               |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                                                           | Additional<br>functions |

| 22     | H5        | 31      | 42      | 52      | P3       | PA6                                                  | I/O      | FT            | (4)  | SPI1_MISO, TIM8_BKIN,<br>TIM13_CH1, DCMI_PIXCLK,<br>TIM3_CH1, TIM1_BKIN,<br>EVENTOUT                          | ADC12_IN6               |

| 23     | J7        | 32      | 43      | 53      | R3       | PA7                                                  | I/O      | FT            | (4)  | SPI1_MOSI, TIM8_CH1N,<br>TIM14_CH1, TIM3_CH2,<br>ETH_MII_RX_DV,<br>TIM1_CH1N,<br>ETH_RMII_CRS_DV,<br>EVENTOUT | ADC12_IN7               |

| 24     | H4        | 33      | 44      | 54      | N5       | PC4                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD0,<br>ETH_MII_RXD0,<br>EVENTOUT                                                                   | ADC12_IN14              |

| 25     | G3        | 34      | 45      | 55      | P5       | PC5                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD1,<br>ETH_MII_RXD1,<br>EVENTOUT                                                                   | ADC12_IN15              |

| 26     | J6        | 35      | 46      | 56      | R5       | PB0                                                  | I/O      | FT            | (4)  | TIM3_CH3, TIM8_CH2N,<br>OTG_HS_ULPI_D1,<br>ETH_MII_RXD2,<br>TIM1_CH2N, EVENTOUT                               | ADC12_IN8               |

| 27     | J5        | 36      | 47      | 57      | R4       | PB1                                                  | I/O      | FT            | (4)  | TIM3_CH4, TIM8_CH3N,<br>OTG_HS_ULPI_D2,<br>ETH_MII_RXD3,<br>TIM1_CH3N, EVENTOUT                               | ADC12_IN9               |

| 28     | J4        | 37      | 48      | 58      | M6       | PB2/BOOT1 (PB2)                                      | I/O      | FT            | -    | EVENTOUT                                                                                                      | -                       |

| -      | -         | -       | 49      | 59      | R6       | PF11                                                 | I/O      | FT            | -    | DCMI_D12, EVENTOUT                                                                                            |                         |

| -      | -         | -       | 50      | 60      | P6       | PF12                                                 | I/O      | FT            | -    | FSMC_A6, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 51      | 61      | M8       | V <sub>SS</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 52      | 62      | N8       | V <sub>DD</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 53      | 63      | N6       | PF13                                                 | I/O      | FT            | -    | FSMC_A7, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 54      | 64      | R7       | PF14                                                 | I/O      | FT            | -    | FSMC_A8, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 55      | 65      | P7       | PF15                                                 | I/O      | FT            | -    | FSMC_A9, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 56      | 66      | N7       | PG0                                                  | I/O      | FT            | -    | FSMC_A10, EVENTOUT                                                                                            | -                       |

| -      | -         | -       | 57      | 67      | M7       | PG1                                                  | I/O      | FT            | -    | FSMC_A11, EVENTOUT                                                                                            | -                       |

|        |           | Pi      | ns      |         |          |                                                      |          |                                                                                                          |      |                                                                                                                             |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure                                                                                            | Note | Alternate functions                                                                                                         | Additional<br>functions |

| -      | -         | I       | 131     | 159     | C7       | V <sub>DD</sub>                                      | S        | -                                                                                                        | -    | -                                                                                                                           | -                       |

| -      | -         | -       | 132     | 160     | B7       | PG15                                                 | I/O      | FT                                                                                                       | -    | USART6_CTS, DCMI_D13,<br>EVENTOUT                                                                                           | -                       |

| 55     | A4        | 89      | 133     | 161     | A10      | PB3<br>(JTDO/TRACESWO)                               | I/O      | FT                                                                                                       | -    | JTDO/ TRACESWO,<br>SPI3_SCK, I2S3_SCK,<br>TIM2_CH2, SPI1_SCK,<br>EVENTOUT                                                   | -                       |

| 56     | B4        | 90      | 134     | 162     | A9       | PB4                                                  | I/O      | FT                                                                                                       | -    | NJTRST, SPI3_MISO,<br>TIM3_CH1, SPI1_MISO,<br>EVENTOUT                                                                      | -                       |

| 57     | A5        | 91      | 135     | 163     | A6       | PB5                                                  | I/O      | FT                                                                                                       | -    | I2C1_SMBA, CAN2_RX,<br>OTG_HS_ULPI_D7,<br>ETH_PPS_OUT, TIM3_CH2,<br>SPI1_MOSI, SPI3_MOSI,<br>DCMI_D10, I2S3_SD,<br>EVENTOUT | -                       |

| 58     | B5        | 92      | 136     | 164     | B6       | PB6                                                  | I/O      | FT                                                                                                       | -    | I2C1_SCL,, TIM4_CH1,<br>CAN2_TX,<br>DCMI_D5,USART1_TX,<br>EVENTOUT                                                          | -                       |

| 59     | A6        | 93      | 137     | 165     | B5       | PB7                                                  | I/O      | FT                                                                                                       | -    | I2C1_SDA, FSMC_NL <sup>(6)</sup> ,<br>DCMI_VSYNC,<br>USART1_RX, TIM4_CH2,<br>EVENTOUT                                       | -                       |

| 60     | B6        | 94      | 138     | 166     | D6       | BOOT0                                                | Ι        | В                                                                                                        | -    | -                                                                                                                           | V <sub>PP</sub>         |

| 61     | B7        | 95      | 139     | 167     | A5       | PB8                                                  | I/O      | FT                                                                                                       | -    | TIM4_CH3,SDIO_D4,<br>TIM10_CH1, DCMI_D6,<br>ETH_MII_TXD3, I2C1_SCL,<br>CAN1_RX, EVENTOUT                                    | -                       |

| 62     | A7        | 96      | 140     | 168     | B4       | PB9                                                  | I/O      | /O FT - SDIO_D5, I2S2_WS,<br>TIM4_CH4, TIM11_CH1,<br>SDIO_D5, DCMI_D7,<br>I2C1_SDA, CAN1_TX,<br>EVENTOUT |      | -                                                                                                                           |                         |

| -      | -         | 97      | 141     | 169     | A4       | PE0                                                  | I/O      | FT                                                                                                       | -    | TIM4_ETR, FSMC_NBL0,<br>DCMI_D2, EVENTOUT                                                                                   | -                       |

Table 8. STM32F20x pin and ball definitions (continued)

|       |       |                | n definition (continu | ed)         |         |

|-------|-------|----------------|-----------------------|-------------|---------|

| Pins  |       | F              | SMC                   |             | LQFP100 |

| 1 113 | CF    | NOR/PSRAM/SRAM | NOR/PSRAM Mux         | NAND 16 bit | Lairio  |

| PE5   | -     | A21            | A21                   | -           | Yes     |

| PE6   | -     | A22            | A22                   | -           | Yes     |

| PF0   | A0    | A0             | -                     | -           | -       |

| PF1   | A1    | A1             | -                     | -           | -       |

| PF2   | A2    | A2             | -                     | -           | -       |

| PF3   | A3    | A3             | -                     | -           | -       |

| PF4   | A4    | A4             | -                     | -           | -       |

| PF5   | A5    | A5             | -                     | -           | -       |

| PF6   | NIORD | -              | -                     | -           | -       |

| PF7   | NREG  | -              | -                     | -           | -       |

| PF8   | NIOWR | -              | -                     | -           | -       |

| PF9   | CD    | -              | -                     | -           | -       |

| PF10  | INTR  | -              | -                     | -           | -       |

| PF12  | A6    | A6             | -                     | -           | -       |

| PF13  | A7    | A7             | -                     | -           | -       |

| PF14  | A8    | A8             | -                     | -           | -       |

| PF15  | A9    | A9             | -                     | -           | -       |

| PG0   | A10   | A10            | -                     | -           | -       |

| PG1   | -     | A11            | -                     | -           | -       |

| PE7   | D4    | D4             | DA4                   | D4          | Yes     |

| PE8   | D5    | D5             | DA5                   | D5          | Yes     |

| PE9   | D6    | D6             | DA6                   | D6          | Yes     |

| PE10  | D7    | D7             | DA7                   | D7          | Yes     |

| PE11  | D8    | D8             | DA8                   | D8          | Yes     |

| PE12  | D9    | D9             | DA9                   | D9          | Yes     |

| PE13  | D10   | D10            | DA10                  | D10         | Yes     |

| PE14  | D11   | D11            | DA11                  | D11         | Yes     |

| PE15  | D12   | D12            | DA12                  | D12         | Yes     |

| PD8   | D13   | D13            | DA13                  | D13         | Yes     |

| PD9   | D14   | D14            | DA14                  | D14         | Yes     |

| PD10  | D15   | D15            | DA15                  | D15         | Yes     |

| PD11  | -     | A16            | A16                   | CLE         | Yes     |

| PD12  | -     | A17            | A17                   | ALE         | Yes     |

|       | 1     |                |                       |             | 1       |

Table 9. FSMC pin definition (continued)

|        |      | AF0               | AF1       | AF2      | AF3          | AF4            | AF5                  | AF6                  | AF7        | AF8                | AF9                       | AF10           | AF11                                 | AF12                 | AF13       |       |          |

|--------|------|-------------------|-----------|----------|--------------|----------------|----------------------|----------------------|------------|--------------------|---------------------------|----------------|--------------------------------------|----------------------|------------|-------|----------|

|        | Port | SYS               | TIM1/2    | TIM3/4/5 | TIM8/9/10/11 | I2C1/I2C2/I2C3 | SPI1/SPI2/I2S2       | SPI3/I2S3            | USART1/2/3 | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 | OTG_FS/ OTG_HS | ETH                                  | FSMC/SDIO/<br>OTG_HS | DCMI       | AF014 | AF15     |

|        | PB0  | -                 | TIM1_CH2N | TIM3_CH3 | TIM8_CH2N    | -              | -                    | -                    | -          | -                  | -                         | OTG_HS_ULPI_D1 | ETH_MII_RXD2                         | -                    | -          | -     | EVENTOUT |

|        | PB1  | -                 | TIM1_CH3N | TIM3_CH4 | TIM8_CH3N    | -              | -                    | -                    | -          | -                  | -                         | OTG_HS_ULPI_D2 | ETH_MII_RXD3                         | -                    | -          | -     | EVENTOUT |

|        | PB2  | -                 | -         | -        | -            | -              | -                    | -                    | -          | -                  | -                         | -              | -                                    | -                    | -          | -     | EVENTOUT |

|        | PB3  | JTDO/<br>TRACESWO | TIM2_CH2  | -        | -            | -              | SPI1_SCK             | SPI3_SCK<br>I2S3_SCK | -          | -                  | -                         | -              | -                                    | -                    | -          | -     | EVENTOUT |

|        | PB4  | JTRST             | -         | TIM3_CH1 | -            | -              | SPI1_MISO            | SPI3_MISO            | -          | -                  | -                         | -              | -                                    | -                    | -          | -     | EVENTOUT |

|        | PB5  | -                 | -         | TIM3_CH2 | -            | I2C1_SMBA      | SPI1_MOSI            | SPI3_MOSI<br>I2S3_SD | -          | -                  | CAN2_RX                   | OTG_HS_ULPI_D7 | ETH _PPS_OUT                         | -                    | DCMI_D10   | -     | EVENTOUT |

|        | PB6  | -                 | -         | TIM4_CH1 | -            | I2C1_SCL       | -                    | -                    | USART1_TX  | -                  | CAN2_TX                   | -              | -                                    | -                    | DCMI_D5    | -     | EVENTOUT |

|        | PB7  | -                 | -         | TIM4_CH2 | -            | I2C1_SDA       | -                    | -                    | USART1_RX  | -                  | -                         | -              | -                                    | FSMC_NL              | DCMI_VSYNC | -     | EVENTOUT |

| Port B | PB8  | -                 | -         | TIM4_CH3 | TIM10_CH1    | I2C1_SCL       | -                    | -                    | -          | -                  | CAN1_RX                   | -              | ETH _MII_TXD3                        | SDIO_D4              | DCMI_D6    | -     | EVENTOUT |

|        | PB9  | -                 | -         | TIM4_CH4 | TIM11_CH1    | I2C1_SDA       | SPI2_NSS<br>I2S2_WS  | -                    | -          | -                  | CAN1_TX                   | -              | -                                    | SDIO_D5              | DCMI_D7    | -     | EVENTOUT |

|        | PB10 | -                 | TIM2_CH3  | -        | -            | I2C2_SCL       | SPI2_SCK<br>I2S2_SCK | -                    | USART3_TX  | -                  | -                         | OTG_HS_ULPI_D3 | ETH_MII_RX_ER                        | -                    | -          | -     | EVENTOUT |

|        | PB11 | -                 | TIM2_CH4  | -        | -            | I2C2_SDA       | -                    | -                    | USART3_RX  | -                  | -                         | OTG_HS_ULPI_D4 | ETH _MII_TX_EN<br>ETH<br>_RMII_TX_EN | -                    | -          | -     | EVENTOUT |

|        | PB12 | -                 | TIM1_BKIN | ÷        | -            | I2C2_SMBA      | SPI2_NSS<br>I2S2_WS  | -                    | USART3_CK  | -                  | CAN2_RX                   | OTG_HS_ULPI_D5 | ETH_MII_TXD0<br>ETH_RMII_TXD0        | OTG_HS_ID            | -          | -     | EVENTOUT |

|        | PB13 | -                 | TIM1_CH1N | -        | -            | -              | SPI2_SCK<br>I2S2_SCK | -                    | USART3_CTS | -                  | CAN2_TX                   | OTG_HS_ULPI_D6 | ETH_MII_TXD1<br>ETH_RMII_TXD1        | -                    | -          | -     | EVENTOUT |

|        | PB14 | -                 | TIM1_CH2N | -        | TIM8_CH2N    | -              | SPI2_MISO            | -                    | USART3_RTS | -                  | TIM12_CH1                 | -              | -                                    | OTG_HS_DM            | -          | -     | EVENTOUT |

|        | PB15 | RTC_50Hz          | TIM1_CH3N | -        | TIM8_CH3N    | -              | SPI2_MOSI<br>I2S2_SD | -                    | -          | -                  | TIM12_CH2                 | -              | -                                    | OTG_HS_DP            | -          | -     | EVENTOUT |

### Table 10. Alternate function mapping (continued)

DocID15818 Rev 13

577

| ი  |

|----|

| 2  |

| 82 |

# DocID15818 Rev 13

|        |                        | AF0  | AF1    | AF2      | AF3          | AF4            | AF5            | AF6                  | AF7        | AF8                | AF9                       | AF10                | AF11                            | AF12                 | AF13    |       |          |

|--------|------------------------|------|--------|----------|--------------|----------------|----------------|----------------------|------------|--------------------|---------------------------|---------------------|---------------------------------|----------------------|---------|-------|----------|

|        | Port                   | SYS  | TIM1/2 | TIM3/4/5 | TIM8/9/10/11 | I2C1/I2C2/I2C3 | SPI1/SPI2/I2S2 | SPI3/I2S3            | USART1/2/3 | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 | OTG_FS/ OTG_HS      | ETH                             | FSMC/SDIO/<br>OTG_HS | DCMI    | AF014 | AF15     |

|        | PC0                    | -    | -      | -        | -            | -              | -              | -                    | -          | -                  | -                         | OTG_HS_ULPI_<br>STP | -                               | -                    | -       | -     | EVENTOUT |

|        | PC1                    | -    | -      | -        | -            | -              | -              | -                    | -          | -                  | -                         | -                   | ETH_MDC                         | -                    | -       | -     | EVENTOUT |

|        | PC2                    | -    | -      | -        | -            | -              | SPI2_MISO      | -                    | -          | -                  | -                         | OTG_HS_ULPI_<br>DIR | ETH_MII_TXD2                    | -                    | -       | -     | EVENTOUT |

|        | PC3                    | -    | -      | -        | -            | -              | SPI2_MOSI      | -                    | -          | -                  | -                         | OTG_HS_ULPI_<br>NXT | ETH<br>_MII_TX_CLK              | -                    | -       | -     | EVENTOUT |

|        | PC4                    | -    | -      | -        | -            | -              | -              | -                    | -          | -                  | -                         | -                   | ETH_MII_RXD0<br>ETH_RMII_RXD0   | -                    | -       | -     | EVENTOUT |

|        | PC5                    | -    | -      | -        | -            | -              | -              | -                    | -          | -                  | -                         | -                   | ETH _MII_RXD1<br>ETH _RMII_RXD1 | -                    | -       | -     | EVENTOUT |

|        | PC6                    | -    | -      | TIM3_CH1 | TIM8_CH1     | -              | I2S2_MCK       | -                    | -          | USART6_TX          | -                         | -                   | -                               | SDIO_D6              | DCMI_D0 | -     | EVENTOUT |

|        | PC7                    | -    | -      | TIM3_CH2 | TIM8_CH2     | -              | -              | I2S3_MCK             | -          | USART6_RX          | -                         | -                   | -                               | SDIO_D7              | DCMI_D1 | -     | EVENTOUT |

| Port C | PC8                    | -    | -      | TIM3_CH3 | TIM8_CH3     | -              | -              | -                    | -          | USART6_CK          | -                         | -                   | -                               | SDIO_D0              | DCMI_D2 | -     | EVENTOUT |

|        | PC9                    | MCO2 | -      | TIM3_CH4 | TIM8_CH4     | I2C3_SDA       | I2S2_CKIN      | I2S3_CKIN            | -          | -                  | -                         | -                   | -                               | SDIO_D1              | DCMI_D3 | -     | EVENTOUT |

|        | PC10                   | -    | -      | -        | -            | -              | -              | SPI3_SCK<br>I2S3_SCK | USART3_TX  | UART4_TX           | -                         | -                   | -                               | SDIO_D2              | DCMI_D8 | -     | EVENTOUT |

|        | PC11                   | -    | -      | -        | -            | -              | -              | SPI3_MISO            | USART3_RX  | UART4_RX           | -                         | -                   | -                               | SDIO_D3              | DCMI_D4 | -     | EVENTOUT |

|        | PC12                   | -    | -      | -        | -            | -              | -              | SPI3_MOSI<br>I2S3_SD | USART3_CK  | UART5_TX           | -                         | -                   | -                               | SDIO_CK              | DCMI_D9 | -     | EVENTOUT |

|        | PC13                   | -    | -      | -        | -            | -              | -              | -                    | -          | -                  | -                         | -                   | -                               | -                    | -       | -     | EVENTOUT |

|        | PC14-<br>OSC32_IN      | -    | -      | -        | -            | -              | -              | -                    | -          | -                  | -                         | -                   | -                               | -                    | -       | -     | EVENTOUT |

|        | PC15-<br>OSC32_OU<br>T | -    | -      | _        | -            | -              | -              | -                    | -          | -                  | -                         | -                   | -                               | -                    | -       | -     | EVENTOUT |

Table 10. Alternate function mapping (continued)

|                                                  |                                    |                                                                               | chang on the op                                                                                              | <b>J</b>                                                                                               |                                                                                                                                                                                                                                                 | 1                                                |

|--------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Operating<br>power<br>supply<br>range            | ADC<br>operation                   | Maximum<br>Flash<br>memory<br>access<br>frequency<br>(f <sub>Flashmax</sub> ) | Number of wait<br>states at<br>maximum CPU<br>frequency<br>(f <sub>CPUmax</sub> =<br>120 MHz) <sup>(1)</sup> | I/O operation                                                                                          | FSMC_CLK<br>frequency for<br>synchronous<br>accesses                                                                                                                                                                                            | Possible<br>Flash<br>memory<br>operations        |

| V <sub>DD</sub> =1.8 to<br>2.1 V <sup>(2)</sup>  | Conversion<br>time up to<br>1 Msps | 16 MHz with<br>no Flash<br>memory wait<br>state                               | 7 <sup>(3)</sup>                                                                                             | <ul> <li>Degraded</li> <li>speed</li> <li>performance</li> <li>No I/O</li> <li>compensation</li> </ul> | Up to 30 MHz                                                                                                                                                                                                                                    | 8-bit erase<br>and program<br>operations<br>only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                | Conversion<br>time up to<br>1 Msps | 18 MHz with<br>no Flash<br>memory wait<br>state                               | 6 <sup>(3)</sup>                                                                                             | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>No I/O<br/>compensation</li> </ul>                | Up to 30 MHz                                                                                                                                                                                                                                    | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                | Conversion<br>time up to<br>2 Msps | 24 MHz with<br>no Flash<br>memory wait<br>state                               | 4 <sup>(3)</sup>                                                                                             | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>I/O<br/>compensation<br/>works</li> </ul>         | Up to 48 MHz                                                                                                                                                                                                                                    | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.7 to<br>3.6 V <sup>(4)</sup> | Conversion<br>time up to<br>2 Msps | 30 MHz with<br>no Flash<br>memory wait<br>state                               | 3(3)                                                                                                         | <ul> <li>Full-speed<br/>operation</li> <li>I/O<br/>compensation<br/>works</li> </ul>                   | $\begin{array}{l} - \mbox{ Up to } \\ 60 \mbox{ MHz } \\ \mbox{ when } \mbox{ V}_{DD} = \\ 3.0 \mbox{ to } 3.6 \mbox{ V} \\ - \mbox{ Up to } \\ 48 \mbox{ MHz } \\ \mbox{ when } \mbox{ V}_{DD} = \\ 2.7 \mbox{ to } 3.0 \mbox{ V} \end{array}$ | 32-bit erase<br>and program<br>operations        |

Table 15. Limitations depending on the operating power supply range

1. The number of wait states can be reduced by reducing the CPU frequency (see Figure 21).

On devices in WLCSP64+2 package, if IRROFF is set to V<sub>DD</sub>, the supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

3. Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

4. The voltage range for OTG USB FS can drop down to 2.7 V. However it is degraded between 2.7 and 3 V.

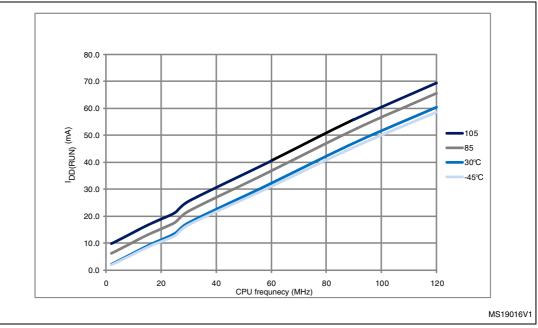

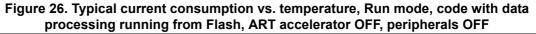

Figure 25. Typical current consumption vs. temperature, Run mode, code with data processing running from Flash, ART accelerator OFF, peripherals ON

|        |                           |                                                      |                                                                                                  | Тур |                         | Ма                      | x <sup>(1)</sup> |    |

|--------|---------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----|-------------------------|-------------------------|------------------|----|

| Symbol | Parameter                 | Conditions                                           | $T_{A} = 25 \text{ °C}$ $V_{DD} = V_{DD} = V_{DD} =$ $1.8 \text{ V} 2.4 \text{ V} 3.3 \text{ V}$ |     | T <sub>A</sub> = 85 °C  | T <sub>A</sub> = 105 °C | Unit             |    |

|        |                           |                                                      |                                                                                                  |     | V <sub>DD</sub> = 3.6 V |                         |                  |    |

|        |                           | Backup SRAM ON, low-speed<br>oscillator and RTC ON   | 3.0                                                                                              | 3.4 | 4.0                     | 15.1                    | 25.8             |    |

|        | Supply current in Standby | Backup SRAM OFF, low-<br>speed oscillator and RTC ON | 2.4                                                                                              | 2.7 | 3.3                     | 12.4                    | 20.5             | μA |

|        | mode                      | Backup SRAM ON, RTC OFF                              | 2.4                                                                                              | 2.6 | 3.0                     | 12.5                    | 24.8             |    |

|        |                           | Backup SRAM OFF, RTC<br>OFF                          | 1.7                                                                                              | 1.9 | 2.2                     | 9.8                     | 19.2             |    |

### Table 24. Typical and maximum current consumptions in Standby mode

1. Guaranteed by characterization results, not tested in production.

### Table 25. Typical and maximum current consumptions in $\rm V_{BAT}$ mode

|                      |           |                                                     |                            | Тур                        |                            | Ма                     |                         |      |

|----------------------|-----------|-----------------------------------------------------|----------------------------|----------------------------|----------------------------|------------------------|-------------------------|------|

| Symbol               | Parameter | Conditions                                          | Т                          | A = 25 °                   | С                          | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                      |           |                                                     | V <sub>DD</sub> =<br>1.8 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | V <sub>DD</sub> =      | = 3.6 V                 |      |

|                      |           | Backup SRAM ON, low-speed<br>oscillator and RTC ON  | 1.29                       | 1.42                       | 1.68                       | 12                     | 19                      |      |

| I <sub>DD_VBAT</sub> |           | Backup SRAM OFF, low-speed<br>oscillator and RTC ON | 0.62                       | 0.73                       | 0.96                       | 8                      | 10                      | μA   |

|                      |           | Backup SRAM ON, RTC OFF                             | 0.79                       | 0.81                       | 0.86                       | 9                      | 16                      |      |

|                      |           | Backup SRAM OFF, RTC OFF                            | 0.10                       | 0.10                       | 0.10                       | 5                      | 7                       |      |

1. Guaranteed by characterization results, not tested in production.

|      | Peripheral <sup>(1)</sup> | Typical consumption at 25 °C | Unit |

|------|---------------------------|------------------------------|------|

|      | SDIO                      | 0.69                         |      |

|      | TIM1                      | 1.06                         |      |

|      | TIM8                      | 1.03                         |      |

|      | TIM9                      | 0.58                         |      |

|      | TIM10                     | 0.37                         |      |

| 4002 | TIM11                     | 0.39                         | m۸   |

| APB2 | ADC1 <sup>(4)</sup>       | 2.13                         | mA   |

|      | ADC2 <sup>(4)</sup>       | 2.04                         |      |

|      | ADC3 <sup>(4)</sup>       | 2.12                         |      |

|      | SPI1                      | 1.20                         |      |

|      | USART1                    | 0.38                         |      |

|      | USART6                    | 0.37                         |      |

Table 26. Peripheral current consumption (continued)

1. External clock is 25 MHz (HSE oscillator with 25 MHz crystal) and PLL is on.

2. EN1 bit is set in DAC\_CR register.

3. EN2 bit is set in DAC\_CR register.

4.  $f_{ADC} = f_{PCLK2}/2$ , ADON bit set in ADC\_CR2 register.

### 6.3.7 Wakeup time from low-power mode

The wakeup times given in *Table 27* is measured on a wakeup phase with a 16 MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                                 | Parameter                                                                                    | Min <sup>(1)</sup> | Тур <sup>(1)</sup> | Max <sup>(1)</sup> | Unit |

|----------------------------------------|----------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>    | Wakeup from Sleep mode                                                                       | -                  | 1                  | -                  | μs   |

|                                        | Wakeup from Stop mode (regulator in Run mode)                                                | -                  | 13                 | -                  |      |

| t <sub>WUSTOP</sub> <sup>(2)</sup>     | Wakeup from Stop mode (regulator in low-power mode)                                          | -                  | 17                 | 40                 | μs   |

|                                        | Wakeup from Stop mode (regulator in low-power mode and Flash memory in Deep power down mode) | -                  | 110                | -                  | F -  |

| t <sub>WUSTDBY</sub> <sup>(2)(3)</sup> | Wakeup from Standby mode                                                                     | 260                | 375                | 480                | μs   |

1. Guaranteed by characterization results, not tested in production.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3.  $t_{WUSTDBY}$  minimum and maximum values are given at 105 °C and –45 °C, respectively.

| Symbol                          | Parameter                                        | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|---------------------------------|--------------------------------------------------|------------------------------|--------------------|-----|--------------------|------|

| t <sub>prog</sub>               | Double word programming                          |                              | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>          | Sector (16 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C | -                  | 230 | -                  |      |

| t <sub>ERASE64KB</sub>          | Sector (64 KB) erase time                        | V <sub>DD</sub> = 3.3 V      | -                  | 490 | -                  | ms   |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>PP</sub> = 8.5 V      | -                  | 875 | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                  |                              | -                  | 6.9 | -                  | S    |

| V <sub>prog</sub>               | Programming voltage                              | -                            | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -                            | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -                            | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                            | -                  | -   | 1                  | hour |

| Table 39. | Flash | memory | programming | with ' | V <sub>PP</sub> |

|-----------|-------|--------|-------------|--------|-----------------|

|-----------|-------|--------|-------------|--------|-----------------|

1. Guaranteed by design, not tested in production.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |

### Table 40. Flash memory endurance and data retention

1. Guaranteed by characterization results, not tested in production.

2. Cycling performed over the whole temperature range.

### 6.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

DocID15818 Rev 13

| Symbol                         | Param                                                   | neter                                                            | Conditions        | Min | Тур | Мах | Unit |

|--------------------------------|---------------------------------------------------------|------------------------------------------------------------------|-------------------|-----|-----|-----|------|

| R <sub>PU</sub>                | Weak pull-up<br>R <sub>PU</sub> equivalent              | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_ID,<br>OTG_HS_ID) | $V_{IN} = V_{SS}$ | 30  | 40  | 50  |      |

| resistor <sup>(6)</sup>        | PA10/PB12<br>(OTG_FS_ID,<br>OTG_HS_ID)                  | -                                                                | 7                 | 10  | 14  | kΩ  |      |

| R <sub>PD</sub>                | Weak pull-down<br>equivalent<br>resistor <sup>(7)</sup> | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_ID,<br>OTG_HS_ID) | $V_{IN} = V_{DD}$ | 30  | 40  | 50  | Ν22  |

|                                | TESISION                                                | PA10/PB12<br>(OTG_FS_ID,<br>OTG_HS_ID)                           | -                 | 7   | 10  | 14  |      |

| C <sub>IO</sub> <sup>(8)</sup> | I/O pin capacitan                                       | ce                                                               | -                 | -   | 5   | -   | pF   |

Table 46. I/O static characteristics (continued)

1. Guaranteed by design, not tested in production.

2. Guaranteed by tests in production.

3. With a minimum of 200 mV.

- 4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 45: I/O current injection susceptibility

- To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 45: I/O current injection susceptibility

- 6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

- 7. Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 8. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization, not tested in production.

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements for FT I/Os is shown in *Figure 38*.

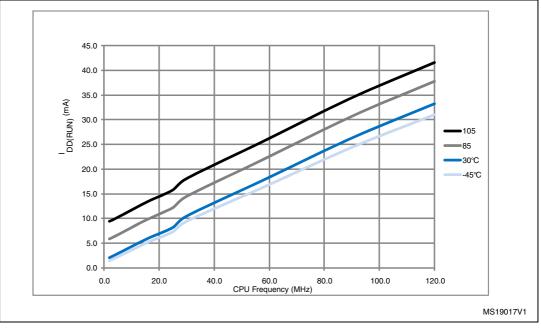

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

| Table 72. Asynchronous non-multi | plexed SRAM/PSRAM/NOR read timings <sup>(1)(2)</sup> |

|----------------------------------|------------------------------------------------------|

| Symbol                    | Parameter                               | Min                      | Мах                      | Unit |

|---------------------------|-----------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                        | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low            | 0.5                      | 2.5                      | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                       | 2T <sub>HCLK</sub> - 1   | 2T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time | 0                        | -                        | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid            | -                        | 4                        | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high   | 0                        | -                        | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid           | -                        | 0.5                      | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high   | 0                        | -                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time        | T <sub>HCLK</sub> + 0.5  | -                        | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOEx high setup time       | T <sub>HCLK</sub> + 2.5  | -                        | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high      | 0                        | -                        | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high      | 0                        | -                        | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low           | -                        | 2.5                      | ns   |

| t <sub>w(NADV</sub> )     | FSMC_NADV low time                      | -                        | T <sub>HCLK</sub> – 0.5  | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

|                           |                                                |     | (00110110 |      |

|---------------------------|------------------------------------------------|-----|-----------|------|

| Symbol                    | Parameter                                      | Min | Мах       | Unit |

| t <sub>su(ADV-CLKH)</sub> | FSMC_A/D[15:0] valid data before FSMC_CLK high | 5   | -         | ns   |

| t <sub>h(CLKH-ADV)</sub>  | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0   | -         | ns   |

### Table 76. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

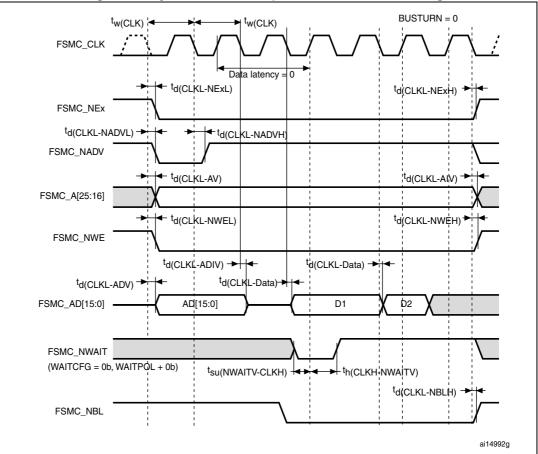

### Figure 62. Synchronous multiplexed PSRAM write timings

Table 77. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                     | Parameter                                | Min                    | Max | Unit |

|----------------------------|------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                          | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)      | -                      | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)    | 2                      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low            | -                      | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high           | 3                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)   | -                      | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625) | 7                      | _   | ns   |

DocID15818 Rev 13

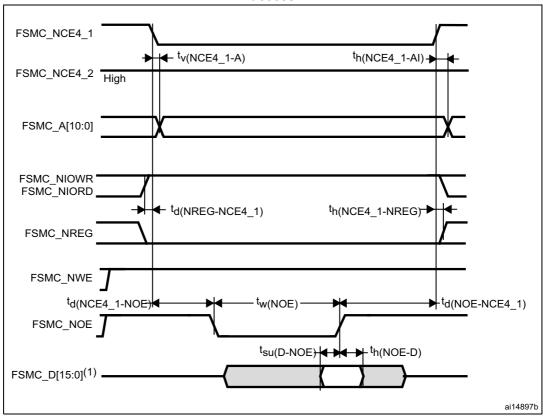

Figure 67. PC Card/CompactFlash controller waveforms for attribute memory read access

1. Only data bits 0...7 are read (bits 8...15 are disregarded).

### 7.7 Thermal characteristics

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                  | Value | Unit |

|---------------|----------------------------------------------------------------------------|-------|------|

|               | Thermal resistance junction-ambient<br>LQFP 64 - 10 × 10 mm / 0.5 mm pitch | 45    |      |

|               | Thermal resistance junction-ambient<br>WLCSP64+2 - 0.400 mm pitch          | 51    |      |

| 0             | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch | 46    | °C/W |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm / 0.5 mm pitch | 40    | 0/11 |

|               | Thermal resistance junction-ambient<br>LQFP176 - 24 × 24 mm / 0.5 mm pitch | 38    |      |

|               | Thermal resistance junction-ambient<br>UFBGA176 - 10× 10 mm / 0.5 mm pitch | 39    |      |

### **Reference document**

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

| Date                | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date<br>22-Apr-2011 |          | Changes         Changed t <sub>w(SCKH)</sub> to t <sub>w(SCLH)</sub> , t <sub>w(SCKL)</sub> to t <sub>w(SCLL)</sub> , t <sub>r(SCK)</sub> to t <sub>r(SCL)</sub> , and t <sub>f(SCK)</sub> to t <sub>f(SCL)</sub> in Table 52: I2C characteristics and in Figure 41: I2C bus AC waveforms and measurement circuit.         Added Table 57: USB OTG FS DC electrical characteristics and updated Table 58: USB OTG FS electrical characteristics.         Updated V <sub>DD</sub> minimum value in Table 62: Ethernet DC electrical characteristics.         Updated Table 66: ADC characteristics and R <sub>AIN</sub> equation.         Updated Table 66: ADC characteristics and R <sub>AIN</sub> equation.         Updated Table 66: ADC characteristics and R <sub>AIN</sub> equation.         Updated R <sub>AIN</sub> equation. Updated Table 68: DAC characteristics.         Updated R typical value in Table 70: VBAT monitoring characteristics.         Updated Table 71: Embedded internal reference voltage.         Modified FSMC_NOE waveform in Figure 57: Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms. Shifted end of |

|                     |          | <i>multiplexed SRAM/PSRAM/NOR read waveforms</i> . Shifted end of<br>FSMC_NEx/NADV/addresses/NWE/NOE/NWAIT of a half FSMC_CLK<br>period, changed t <sub>d</sub> (CLKH-NExH) to t <sub>d</sub> (CLKL-NEXH), t <sub>d</sub> (CLKH-AIV) to t <sub>d</sub> (CLKL-<br>AIV), t <sub>d</sub> (CLKH-NOEH) to t <sub>d</sub> (CLKL-NOEH), and t <sub>d</sub> (CLKH-NWEH) to t <sub>d</sub> (CLKL-NWEH),<br>and updated data latency from 1 to 0 in <i>Figure 61: Synchronous</i><br><i>multiplexed NOR/PSRAM read timings</i> , <i>Figure 62: Synchronous non-</i><br><i>multiplexed NOR/PSRAM read timings</i> , and <i>Figure 64: Synchronous</i><br><i>non-multiplexed PSRAM write timings</i> ,                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                     |          | Changed $t_{d(CLKH-NExH)}$ to $t_{d(CLKL-NExH)}$ , $t_{d(CLKH-AIV)}$ to $t_{d(CLKL-AIV)}$ , $t_{d(CLKH-NOEH)}$ to $t_{d(CLKL-NOEH)}$ , $t_{d(CLKH-NWEH)}$ to $t_{d(CLKL-NWEH)}$ , and modified $t_{w(CLK)}$ minimum value in <i>Table 76</i> , <i>Table 77</i> , <i>Table 78</i> , and <i>Table 79</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                     |          | Updated note 2 in <i>Table 72, Table 73, Table 74, Table 75, Table 76, Table 77, Table 78,</i> and <i>Table 79.</i><br>Modified t <sub>h(NIOWR-D)</sub> in <i>Figure 70: PC Card/CompactFlash controller</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     |          | Modified th(NIOWR-D) In Figure 70. FC Card/CompactFlash controller<br>waveforms for I/O space write access.<br>Modified FSMC_NCEx signal in Figure 71: NAND controller waveforms<br>for read access, Figure 72: NAND controller waveforms for write<br>access, Figure 73: NAND controller waveforms for common memory<br>read access, and Figure 74: NAND controller waveforms for common<br>memory write access<br>Specified Full speed (FS) mode for Figure 89: USB OTG HS peripheral-<br>only connection in FS mode and Figure 90: USB OTG HS host-only<br>connection in FS mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 97. Document revision history (continued)