# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 120MHz                                                                                  |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, Memory Card, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                       |

| Number of I/O              | 82                                                                                      |

| Program Memory Size        | 1MB (1M x 8)                                                                            |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 132K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                   |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 100-LQFP                                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f207vgt6                   |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 84. | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline      | 158 |

|------------|--------------------------------------------------------------------------|-----|

| Figure 85. | LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package               |     |

|            | recommended footprint                                                    | 160 |

| Figure 86. | LQFP144 marking (package top view)                                       | 161 |

|            | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline      |     |

| Figure 88. | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package              |     |

| U          | recommended footprint                                                    | 164 |

| Figure 89. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch,                       |     |

| U          | ultra fine pitch ball grid array package outline                         | 165 |

| Figure 90. | UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball |     |

| U          | grid array package recommended footprint                                 | 166 |

in the 0 to 70 °C temperature range using an external power supply supervisor (see *Section 3.16*).

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.8 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock, 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Refer to Figure 19: Power supply scheme for more details.

# 3.15 Power supply supervisor

The devices have an integrated power-on reset (POR) / power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry.

At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default BOR threshold levels, or to disable BOR permanently. Three BOR thresholds are available through option bytes.

The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for an external reset circuit. On devices in WLCSP64+2 package, the BOR, POR and PDR features can be disabled by setting IRROFF pin to  $V_{DD}$ . In this mode an external power supply supervisor is required (see Section 3.16).

The devices also feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

# 3.16 Voltage regulator

The regulator has five operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low-power regulator (LPR)

- Power-down

- Regulator OFF

- Regulator OFF/internal reset ON

- Regulator OFF/internal reset OFF

### 3.16.1 Regulator ON

The regulator ON modes are activated by default on LQFP packages. On WLCSP64+2 package, they are activated by connecting both REGOFF and IRROFF pins to V<sub>SS</sub>, while only REGOFF must be connected to V<sub>SS</sub> on UFBGA176 package (IRROFF is not available).

$V_{DD}$  minimum value is 1.8 V.

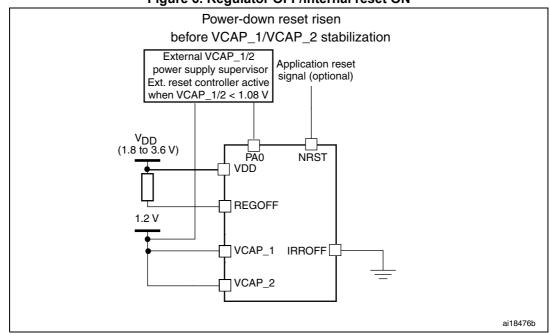

Figure 6. Regulator OFF/internal reset ON

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach 1.08 V is faster than the time for  $V_{DD}$  to reach 1.8 V, then PA0 should be kept low to cover both conditions: until  $V_{CAP_1}$  and  $V_{CAP_2}$  reach 1.08 V and until  $V_{DD}$  reaches 1.8 V (see *Figure 8*).

- Otherwise, If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach 1.08 V is slower than the time for V<sub>DD</sub> to reach 1.8 V, then PA0 should be asserted low externally (see *Figure 9*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below 1.08 V and V<sub>DD</sub> is higher than 1.8 V, then a reset must be asserted on PA0 pin.

### **Regulator OFF/internal reset OFF**

On WLCSP64+2 package, this mode activated by connecting REGOFF to V<sub>SS</sub> and IRROFF to V<sub>DD</sub>. IRROFF cannot be activated in conjunction with REGOFF. This mode is available only on the WLCSP64+2 package. It allows to supply externally a 1.2 V voltage source through V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> pins. In this mode, the integrated power-on reset (POR)/ power-down reset (PDR) circuitry is disabled.

An external power supply supervisor should monitor both the external 1.2 V and the external  $V_{DD}$  supply voltage, and should maintain the device in reset mode as long as they remain below a specified threshold. The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.8 V. This supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range. A comprehensive set of power-saving modes allows to design low-power applications.

The backup registers are 32-bit registers used to store 80 bytes of user application data when  $V_{DD}$  power is not present. Backup registers are not reset by a system, a power reset, or when the device wakes up from the Standby mode (see Section 3.18: Low-power modes).

Like backup SRAM, the RTC and backup registers are supplied through a switch that is powered either from the  $V_{DD}$  supply when present or the  $V_{BAT}$  pin.

# 3.18 Low-power modes

The STM32F20x family supports three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from the Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup.

• Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

*Note:* The RTC, the IWDG, and the corresponding clock sources are not stopped when the device enters the Stop or Standby mode.

# 3.19 V<sub>BAT</sub> operation

The  $V_{BAT}$  pin allows to power the device  $V_{BAT}$  domain from an external battery or an external supercapacitor.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The VBAT pin supplies the RTC, the backup registers and the backup SRAM.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

When using WLCSP64+2 package, if IRROFF pin is connected to  $V_{DD}$ , the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to  $V_{DD}$ .

|        |           | Pi      | ns      |         |          |                                                      |          |               |      |                                                                                                               |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|---------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                                                           | Additional<br>functions |

| 22     | H5        | 31      | 42      | 52      | P3       | PA6                                                  | I/O      | FT            | (4)  | SPI1_MISO, TIM8_BKIN,<br>TIM13_CH1, DCMI_PIXCLK,<br>TIM3_CH1, TIM1_BKIN,<br>EVENTOUT                          | ADC12_IN6               |

| 23     | J7        | 32      | 43      | 53      | R3       | PA7                                                  | I/O      | FT            | (4)  | SPI1_MOSI, TIM8_CH1N,<br>TIM14_CH1, TIM3_CH2,<br>ETH_MII_RX_DV,<br>TIM1_CH1N,<br>ETH_RMII_CRS_DV,<br>EVENTOUT | ADC12_IN7               |

| 24     | H4        | 33      | 44      | 54      | N5       | PC4                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD0,<br>ETH_MII_RXD0,<br>EVENTOUT                                                                   | ADC12_IN14              |

| 25     | G3        | 34      | 45      | 55      | P5       | PC5                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD1,<br>ETH_MII_RXD1,<br>EVENTOUT                                                                   | ADC12_IN15              |

| 26     | J6        | 35      | 46      | 56      | R5       | PB0                                                  | I/O      | FT            | (4)  | TIM3_CH3, TIM8_CH2N,<br>OTG_HS_ULPI_D1,<br>ETH_MII_RXD2,<br>TIM1_CH2N, EVENTOUT                               | ADC12_IN8               |

| 27     | J5        | 36      | 47      | 57      | R4       | PB1                                                  | I/O      | FT            | (4)  | TIM3_CH4, TIM8_CH3N,<br>OTG_HS_ULPI_D2,<br>ETH_MII_RXD3,<br>TIM1_CH3N, EVENTOUT                               | ADC12_IN9               |

| 28     | J4        | 37      | 48      | 58      | M6       | PB2/BOOT1 (PB2)                                      | I/O      | FT            | -    | EVENTOUT                                                                                                      | -                       |

| -      | -         | -       | 49      | 59      | R6       | PF11                                                 | I/O      | FT            | -    | DCMI_D12, EVENTOUT                                                                                            |                         |

| -      | -         | -       | 50      | 60      | P6       | PF12                                                 | I/O      | FT            | -    | FSMC_A6, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 51      | 61      | M8       | V <sub>SS</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 52      | 62      | N8       | V <sub>DD</sub>                                      | S        |               | -    | -                                                                                                             | -                       |

| -      | -         | -       | 53      | 63      | N6       | PF13                                                 | I/O      | FT            | -    | FSMC_A7, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 54      | 64      | R7       | PF14                                                 | I/O      | FT            | -    | FSMC_A8, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 55      | 65      | P7       | PF15                                                 | I/O      | FT            | -    | FSMC_A9, EVENTOUT                                                                                             | -                       |

| -      | -         | -       | 56      | 66      | N7       | PG0                                                  | I/O      | FT            | -    | FSMC_A10, EVENTOUT                                                                                            | -                       |

| -      | -         | -       | 57      | 67      | M7       | PG1                                                  | I/O      | FT            | -    | FSMC_A11, EVENTOUT                                                                                            | -                       |

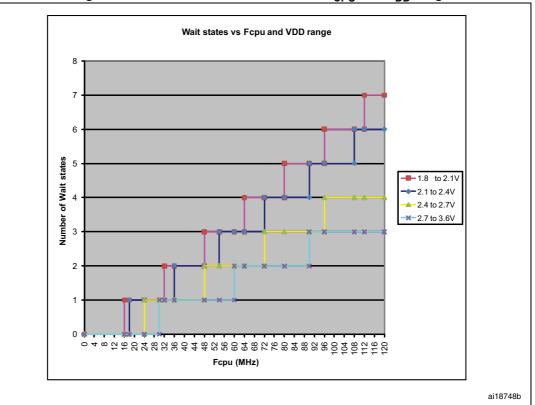

Figure 21. Number of wait states versus  $f_{\mbox{CPU}}$  and  $V_{\mbox{DD}}$  range

1. The supply voltage can drop to 1.7 V when the device operates in the 0 to 70  $^\circ\text{C}$  temperature range and IRROFF is set to V\_DD.

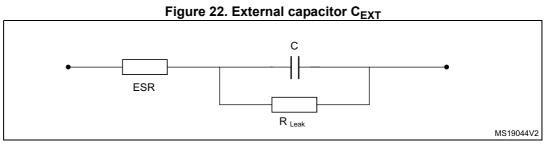

# 6.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 16*.

1. Legend: ESR is the equivalent series resistance.

### Table 16. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

| Symbol | Parameter                         | Conditions |

|--------|-----------------------------------|------------|

| CEXT   | Capacitance of external capacitor | 2.2 µF     |

| ESR    | ESR of external capacitor         | < 2 Ω      |

1. When bypassing the voltage regulator, the two 2.2  $\mu F$  V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

# 6.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for  $T_A$ .

| Symbol           | Parameter                      | Min | Max | Unit  |  |

|------------------|--------------------------------|-----|-----|-------|--|

| 1                | V <sub>DD</sub> rise time rate | 20  | 8   | us/V  |  |

| <sup>I</sup> VDD | V <sub>DD</sub> fall time rate | 20  | 8   | μ3/ ν |  |

### Table 17. Operating conditions at power-up / power-down (regulator ON)

# 6.3.4 Operating conditions at power-up / power-down (regulator OFF)

Subject to general operating conditions for  $T_A$ .

| Table 18. Operating conditions at power-up   | / power-down (regulator OFF) |

|----------------------------------------------|------------------------------|

| Table 10. Operating conditions at power-up / | power-down (regulator or r)  |

| Symbol            | Parameter                                    | Conditions | Min | Max | Unit |

|-------------------|----------------------------------------------|------------|-----|-----|------|

| t                 | V <sub>DD</sub> rise time rate               | Power-up   | 20  | 8   |      |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate               | Power-down | 20  | 8   |      |

| t                 | $V_{CAP\_1}$ and $V_{CAP\_2}$ rise time rate | Power-up   | 20  | ∞   | µs/V |

| t <sub>VCAP</sub> | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | ∞   |      |

| Table 13. Enibedded feset and power control block characteristics (continued)                                      |                                                                                    |                                                                                           |      |      |      |      |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| Symbol Parameter                                                                                                   |                                                                                    | Conditions                                                                                | Min  | Тур  | Max  | Unit |

| N .                                                                                                                | Brownout level 2                                                                   | Falling edge                                                                              | 2.44 | 2.50 | 2.56 | V    |

| V <sub>BOR2</sub>                                                                                                  | threshold                                                                          | Rising edge                                                                               | 2.53 | 2.59 | 2.63 | V    |

| M                                                                                                                  | Brownout level 3                                                                   | Falling edge                                                                              | 2.75 | 2.83 | 2.88 | V    |

| V <sub>BOR3</sub>                                                                                                  | threshold                                                                          | Rising edge                                                                               | 2.85 | 2.92 | 2.97 | V    |

| V <sub>BORhyst</sub> <sup>(1)</sup>                                                                                | BOR hysteresis                                                                     | -                                                                                         | -    | 100  | -    | mV   |

| T <sub>RSTTEMPO</sub> <sup>(1)(2)</sup>                                                                            | Reset temporization                                                                | -                                                                                         | 0.5  | 1.5  | 3.0  | ms   |

| I <sub>RUSH</sub> <sup>(1)</sup>                                                                                   | InRush current on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby) | -                                                                                         | -    | 160  | 200  | mA   |

| E <sub>RUSH</sub> <sup>(1)</sup> InRush energy on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby) |                                                                                    | V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -    | -    | 5.4  | μC   |

Table 19. Embedded reset and power control block characteristics (continued)

1. Guaranteed by design, not tested in production.

2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

# 6.3.6 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 20: Current consumption measurement scheme*.

All Run mode current consumption measurements given in this section are performed using CoreMark code.

|                 |                            | ning from Flash men                                                    |                       | Тур | ,                      | ax <sup>(1)</sup>       |      |

|-----------------|----------------------------|------------------------------------------------------------------------|-----------------------|-----|------------------------|-------------------------|------|

| Symbol          | Parameter                  | Conditions                                                             | f <sub>HCLK</sub>     | -   | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                 |                            |                                                                        | 120 MHz               | 61  | 81                     | 93                      |      |

|                 |                            |                                                                        | 90 MHz                | 48  | 68                     | 80                      |      |

|                 |                            |                                                                        | 60 MHz                | 33  | 53                     | 65                      |      |

|                 |                            | (2)                                                                    | 30 MHz                | 18  | 38                     | 50                      |      |

|                 |                            | External clock <sup>(2)</sup> , all peripherals enabled <sup>(3)</sup> | 25 MHz                | 14  | 34                     | 46                      |      |

|                 |                            |                                                                        | 16 MHz <sup>(4)</sup> | 10  | 30                     | 42                      | - mA |

|                 |                            |                                                                        | 8 MHz                 | 6   | 26                     | 38                      |      |

|                 |                            |                                                                        | 4 MHz                 | 4   | 24                     | 36                      |      |

|                 | Supply current in Run mode |                                                                        | 2 MHz                 | 3   | 23                     | 35                      |      |

| I <sub>DD</sub> |                            | External clock <sup>(2)</sup> , all peripherals disabled               | 120 MHz               | 33  | 54                     | 66                      |      |

|                 |                            |                                                                        | 90 MHz                | 27  | 47                     | 59                      |      |

|                 |                            |                                                                        | 60 MHz                | 19  | 39                     | 51                      |      |

|                 |                            |                                                                        | 30 MHz                | 11  | 31                     | 43                      |      |

|                 |                            |                                                                        | 25 MHz                | 8   | 28                     | 41                      |      |

|                 |                            |                                                                        | 16 MHz <sup>(4)</sup> | 6   | 26                     | 38                      |      |

|                 |                            |                                                                        | 8 MHz                 | 4   | 24                     | 36                      |      |

|                 |                            |                                                                        | 4 MHz                 | 3   | 23                     | 35                      |      |

|                 |                            |                                                                        | 2 MHz                 | 2   | 23                     | 34                      |      |

# Table 21. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled)

1. Guaranteed by characterization results, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 4 MHz and PLL is on when  $f_{HCLK}$  > 25 MHz.

3. When the ADC is on (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

4. In this case HCLK = system clock/2.

|                 |                   |                                                                           |                   | Тур                       | Ma                        |                            |      |

|-----------------|-------------------|---------------------------------------------------------------------------|-------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter         | Conditions                                                                | f <sub>HCLK</sub> | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                   |                                                                           | 120 MHz           | 38                        | 51                        | 61                         |      |

|                 |                   |                                                                           | 90 MHz            | 30                        | 43                        | 53                         |      |

|                 |                   |                                                                           | 60 MHz            | 20                        | 33                        | 43                         |      |

|                 |                   | <b>-</b> (2)                                                              | 30 MHz            | 11                        | 25                        | 35                         |      |

|                 |                   | External clock <sup>(2)</sup> ,<br>all peripherals enabled <sup>(3)</sup> | 25 MHz            | 8                         | 21                        | 31                         |      |

|                 |                   |                                                                           | 16 MHz            | 6                         | 19                        | 29                         | - mA |

|                 |                   |                                                                           | 8 MHz             | 3.6                       | 17.0                      | 27.0                       |      |

|                 |                   |                                                                           | 4 MHz             | 2.4                       | 15.4                      | 25.3                       |      |

|                 | Supply current in |                                                                           | 2 MHz             | 1.9                       | 14.9                      | 24.7                       |      |

| I <sub>DD</sub> | Sleep mode        | (0)                                                                       | 120 MHz           | 8                         | 21                        | 31                         |      |

|                 |                   |                                                                           | 90 MHz            | 7                         | 20                        | 30                         |      |

|                 |                   |                                                                           | 60 MHz            | 5                         | 18                        | 28                         |      |

|                 |                   |                                                                           | 30 MHz            | 3.5                       | 16.0                      | 26.0                       |      |

|                 |                   | External clock <sup>(2)</sup> , all peripherals disabled                  | 25 MHz            | 2.5                       | 16.0                      | 25.0                       |      |

|                 |                   |                                                                           | 16 MHz            | 2.1                       | 15.1                      | 25.0                       | -    |

|                 |                   |                                                                           | 8 MHz             | 1.7                       | 15.0                      | 25.0                       |      |

|                 |                   |                                                                           | 4 MHz             | 1.5                       | 14.6                      | 24.6                       |      |

|                 |                   |                                                                           | 2 MHz             | 1.4                       | 14.2                      | 24.3                       |      |

| Table 22. Typical and maximum current | consumption in Sleep mode |

|---------------------------------------|---------------------------|

|---------------------------------------|---------------------------|

1. Guaranteed by characterization results, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 4 MHz and PLL is on when  $\rm f_{HCLK}$  > 25 MHz.

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

|      | Peripheral <sup>(1)</sup>    | Typical consumption at 25 °C | Unit |

|------|------------------------------|------------------------------|------|

|      | TIM2                         | 0.61                         |      |

|      | TIM3                         | 0.49                         |      |

|      | TIM4                         | 0.54                         |      |

|      | TIM5                         | 0.62                         |      |

|      | TIM6                         | 0.20                         |      |

|      | TIM7                         | 0.20                         |      |

|      | TIM12                        | 0.36                         |      |

|      | TIM13                        | 0.28                         |      |

|      | TIM14                        | 0.25                         |      |

|      | USART2                       | 0.25                         |      |

|      | USART3                       | 0.25                         |      |

|      | UART4                        | 0.25                         |      |

| APB1 | UART5                        | 0.26                         | mA   |

|      | I2C1                         | 0.25                         |      |

|      | I2C2                         | 0.25                         |      |

|      | I2C3                         | 0.25                         |      |

|      | SPI2                         | 0.20/0.10                    |      |

|      | SPI3                         | 0.18/0.09                    |      |

|      | CAN1                         | 0.31                         |      |

|      | CAN2                         | 0.30                         |      |

|      | DAC channel 1 <sup>(2)</sup> | 1.11                         |      |

|      | DAC channel 1 <sup>(3)</sup> | 1.11                         |      |

|      | PWR                          | 0.15                         |      |

|      | WWDG                         | 0.15                         |      |

Table 26. Peripheral current consumption (continued)

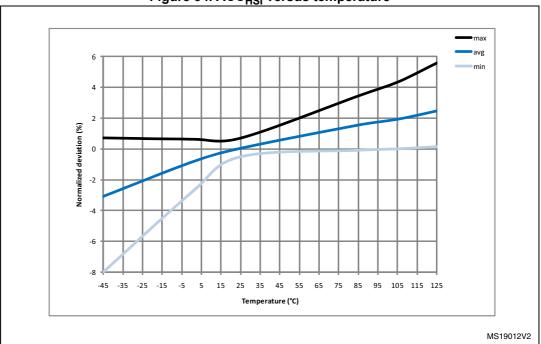

Figure 34. ACC<sub>HSI</sub> versus temperature

### Low-speed internal (LSI) RC oscillator

| Table 33. LS | l oscillator | characteristics <sup>(1)</sup> |

|--------------|--------------|--------------------------------|

|--------------|--------------|--------------------------------|

| Symbol                              | Parameter                        | Min | Тур | Мах | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by characterization results, not tested in production.

3. Guaranteed by design, not tested in production.

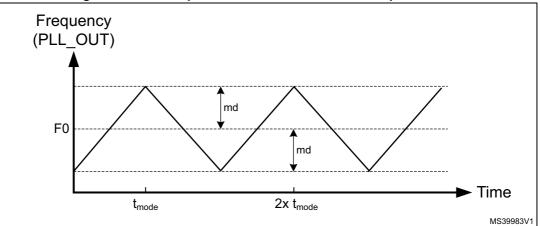

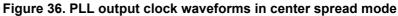

*Figure 36* and *Figure 37* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is f<sub>PLL\_OUT</sub> nominal.

T<sub>mode</sub> is the modulation period.

md is the modulation depth.

Figure 37. PLL output clock waveforms in down spread mode

# 6.3.12 Memory characteristics

### Flash memory

The characteristics are given at  $T_{\text{A}}$  = –40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

# 6.3.18 TIM timer characteristics

The parameters given in *Table 50* and *Table 51* are guaranteed by design.

Refer to Section 6.3.16: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                          | Conditions                                                     | Min         | Мах                     | Unit                                                                                                                                                  |

|------------------------|------------------------------------|----------------------------------------------------------------|-------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                                    | AHB/APB1                                                       | 1           | -                       | t <sub>TIMxCLK</sub>                                                                                                                                  |

| t <sub>res(TIM)</sub>  | Timer resolution time              | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>60 MHz | 16.7        | -                       | t <sub>TIMxCLK</sub><br>ns<br>t <sub>TIMxCLK</sub><br>ns<br>MHz<br>MHz<br>bit<br>t <sub>TIMxCLK</sub><br>t <sub>TIMxCLK</sub><br>t <sub>TIMxCLK</sub> |

|                        |                                    | AHB/APB1                                                       | 1           | -                       |                                                                                                                                                       |

|                        |                                    | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 30 MHz                | 33.3        | -                       | ns                                                                                                                                                    |

| f <sub>EXT</sub>       | Timer external clock               |                                                                | 0           | f <sub>TIMxCLK</sub> /2 | MHz                                                                                                                                                   |

| 'EXT                   | frequency on CH1 to CH4            |                                                                | 0           | 30                      | MHz                                                                                                                                                   |

| Res <sub>TIM</sub>     | Timer resolution                   |                                                                | -           | 16/32                   | bit                                                                                                                                                   |

|                        | 16-bit counter clock period        |                                                                | 1           | 65536                   | t <sub>TIMxCLK</sub>                                                                                                                                  |

| t                      | when internal clock is selected    | f <sub>TIMxCLK</sub> = 60 MHz<br>APB1= 30 MHz                  | 0.0167 1092 |                         | μs                                                                                                                                                    |

| <sup>t</sup> COUNTER   | 32-bit counter clock period        |                                                                | 1           | -                       | t <sub>TIMxCLK</sub>                                                                                                                                  |

|                        | when internal clock is<br>selected |                                                                | 0.0167      | 71582788                | μs                                                                                                                                                    |

| tury count             | Maximum possible count             |                                                                | -           | 65536 × 65536           | t <sub>TIMxCLK</sub>                                                                                                                                  |

| t <sub>MAX_COUNT</sub> |                                    |                                                                | -           | 71.6                    | s                                                                                                                                                     |

| Table 50. Characteristics of TIMx connected to the APE | 31 domain <sup>(1)</sup> |

|--------------------------------------------------------|--------------------------|

|--------------------------------------------------------|--------------------------|

1. TIMx is used as a general term to refer to the TIM2, TIM3, TIM4, TIM5, TIM6, TIM7, and TIM12 timers.

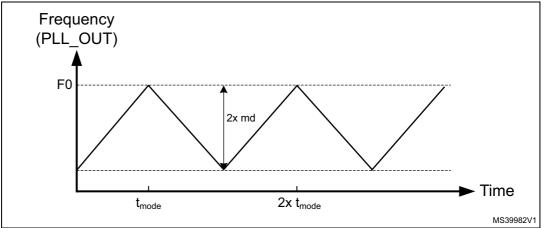

### Figure 47. USB OTG FS timings: definition of data signal rise and fall time

### Table 58. USB OTG FS electrical characteristics<sup>(1)</sup>

| Driver characteristics |                                        |                                |     |     |    |  |  |  |  |

|------------------------|----------------------------------------|--------------------------------|-----|-----|----|--|--|--|--|

| Symbol                 | mbol Parameter Conditions Min Max Unit |                                |     |     |    |  |  |  |  |

| t <sub>r</sub>         | Rise time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |  |  |

| t <sub>f</sub>         | Fall time <sup>(2)</sup>               | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |  |  |

| t <sub>rfm</sub>       | Rise/fall time matching                | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %  |  |  |  |  |

| V <sub>CRS</sub>       | Output signal crossover voltage        | -                              | 1.3 | 2.0 | V  |  |  |  |  |

1. Guaranteed by design, not tested in production.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

### **USB HS characteristics**

Table 59 shows the USB HS operating voltage.

### Table 59. USB HS DC electrical characteristics

| Symbol      |          | Parameter                    | Min. <sup>(1)</sup> | Min. <sup>(1)</sup> Max. <sup>(1)</sup> 2.7         3.6 |   |

|-------------|----------|------------------------------|---------------------|---------------------------------------------------------|---|

| Input level | $V_{DD}$ | USB OTG HS operating voltage | 2.7                 | 3.6                                                     | V |

1. All the voltages are measured from the local ground potential.

### Table 60. Clock timing parameters

| Parameter <sup>(1)</sup>                                           | Symbol              | Min                     | Nominal | Max    | Unit  |      |

|--------------------------------------------------------------------|---------------------|-------------------------|---------|--------|-------|------|

| Frequency (first transition) 8-bit ±10%                            |                     | F <sub>START_8BIT</sub> | 54      | 60     | 66    | MHz  |

| Frequency (steady state) ±500                                      | ppm                 | F <sub>STEADY</sub>     | 59.97   | 60     | 60.03 | MHz  |

| Duty cycle (first transition) 8-bit ±10%                           |                     | D <sub>START_8BIT</sub> | 40      | 50     | 60    | %    |

| Duty cycle (steady state) ±500                                     | D <sub>STEADY</sub> | 49.975                  | 50      | 50.025 | %     |      |

| Time to reach the steady state duty cycle after the first transiti |                     | T <sub>STEADY</sub>     | -       | -      | 1.4   | ms   |

| Clock startup time after the                                       | Peripheral          | T <sub>START_DEV</sub>  | -       | -      | 5.6   | ms   |

| de-assertion of SuspendM Host                                      |                     | T <sub>START_HOST</sub> | -       | -      | -     | 1115 |

| PHY preparation time after the first transition of the input clock |                     | T <sub>PREP</sub>       | -       | -      | -     | μs   |

1. Guaranteed by design, not tested in production.

# 6.3.20 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 66* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 14*.

| Symbol                                                      | Parameter                                       | Conditions                                          | Min                                                         | Тур      | Мах               | Unit               |

|-------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------|----------|-------------------|--------------------|

| V <sub>DDA</sub>                                            | Power supply                                    | -                                                   | 1.8 <sup>(1)</sup>                                          | -        | 3.6               | V                  |

| V <sub>REF+</sub>                                           | Positive reference voltage                      | -                                                   | 1.8 <sup>(1)(2)</sup>                                       | -        | V <sub>DDA</sub>  | V                  |

|                                                             |                                                 | $V_{DDA}$ = 1.8 <sup>(1)</sup> to 2.4 V             | 0.6                                                         | -        | 15                | MHz                |

| <sup>I</sup> ADC                                            | ADC Clock frequency                             | V <sub>DDA</sub> = 2.4 to 3.6 V                     | 0.6                                                         | -        | 30                | MHz                |

| f <sub>TRIG</sub> <sup>(3)</sup> External trigger frequency |                                                 | f <sub>ADC</sub> = 30 MHz with<br>12-bit resolution | -                                                           | -        | 1764              | kHz                |

| TRIG                                                        |                                                 | -                                                   | -                                                           | -        | 17                | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub>                                            | Conversion voltage range <sup>(4)</sup>         | -                                                   | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -        | V <sub>REF+</sub> | V                  |

| R <sub>AIN</sub> <sup>(3)</sup>                             | External input impedance                        | See <i>Equation 1</i> for details                   | -                                                           | -        | 50                | kΩ                 |

| R <sub>ADC</sub> <sup>(3)(5)</sup>                          | Sampling switch resistance                      | -                                                   | 1.5                                                         | -        | 6                 | kΩ                 |

| C <sub>ADC</sub> <sup>(3)</sup>                             | Internal sample and hold capacitor              | -                                                   | -                                                           | 4        | -                 | pF                 |

| t <sub>lat</sub> (3)                                        | Injection trigger conversion<br>latency         | f <sub>ADC</sub> = 30 MHz                           | -                                                           | -        | 0.100             | μs                 |

| 'lat` ´                                                     |                                                 | -                                                   | -                                                           | -        | 3 <sup>(6)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> <sup>(3)</sup> Reg                        | Regular trigger conversion latency              | f <sub>ADC</sub> = 30 MHz                           | -                                                           | -        | 0.067             | μs                 |

| 4atr` ´                                                     | Regular ingger conversion latency               | -                                                   | -                                                           | -        | 2 <sup>(6)</sup>  | 1/f <sub>ADC</sub> |

| t <sub>S</sub> <sup>(3)</sup>                               | Sampling time                                   | f <sub>ADC</sub> = 30 MHz                           | 0.100                                                       | -        | 16                | μs                 |

| LS(*)                                                       | Sampling une                                    | -                                                   | 3                                                           | -        | 480               | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(3)</sup>                            | Power-up time                                   | -                                                   | -                                                           | 2        | 3                 | μs                 |

|                                                             |                                                 | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution      | 0.5                                                         | -        | 16.40             | μs                 |

|                                                             |                                                 | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution      | MHz 0.43 - 16                                               |          | 16.34             | μs                 |

| t <sub>CONV</sub> <sup>(3)</sup>                            | Total conversion time (including sampling time) | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution       | 0.37                                                        | -        | 16.27             | μs                 |

|                                                             |                                                 | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution       | 0.3                                                         | -        | 16.20             | μs                 |

|                                                             |                                                 | 9 to 492 (t <sub>S</sub> for samplir approximation) | ng +n-bit resolutior                                        | for succ | cessive           | 1/f <sub>ADC</sub> |

| Table | 66. / | ADC | characteristics |

|-------|-------|-----|-----------------|

| Table |       |     | characteristics |

### General PCB design guidelines

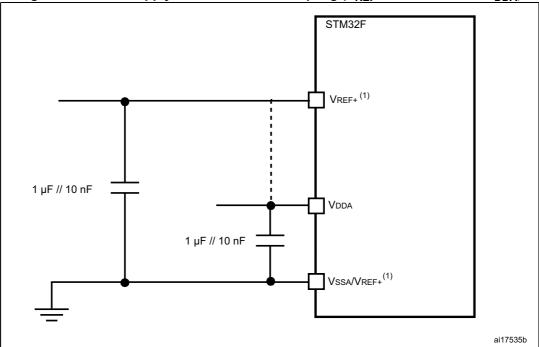

Power supply decoupling should be performed as shown in *Figure 54* or *Figure 55*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

V<sub>REF+</sub> and V<sub>REF</sub> inputs are both available on UFBGA176 package. V<sub>REF+</sub> is also available on all packages except for LQFP64. When V<sub>REF+</sub> and V<sub>REF</sub> are not available, they are internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

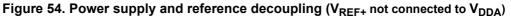

### **Device marking**

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

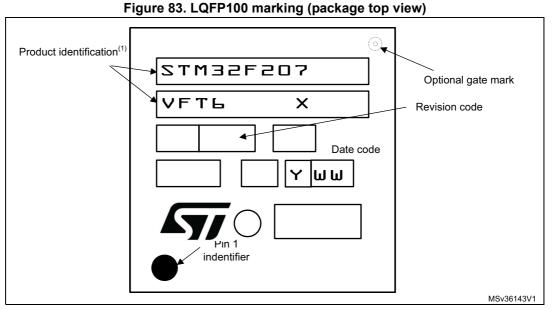

### **Device marking**

Figure 86. LQFP144 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

|                  |        |             | Dimer  | nsions |                       |        |

|------------------|--------|-------------|--------|--------|-----------------------|--------|

| Symbol           |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|                  | Min.   | Тур.        | Max.   | Min.   | Тур.                  | Max.   |

| HD               | 25.900 | -           | 26.100 | 1.0197 | -                     | 1.0276 |

| ZD               | -      | 1.250       | -      | -      | 0.0492                | -      |

| E                | 23.900 | -           | 24.100 | 0.9409 | -                     | 0.9488 |

| HE               | 25.900 | -           | 26.100 | 1.0197 | -                     | 1.0276 |

| ZE               | -      | 1.250       | -      | -      | 0.0492                | -      |

| е                | -      | 0.500       | -      | -      | 0.0197                | -      |

| L <sup>(2)</sup> | 0.450  | -           | 0.750  | 0.0177 | -                     | 0.0295 |

| L1               | -      | 1.000       | -      | -      | 0.0394                | -      |

| k                | 0°     | -           | 7°     | 0°     | -                     | 7°     |

| CCC              | -      | -           | 0.080  | -      | -                     | 0.0031 |

# Table 92. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat packagemechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. L dimension is measured at gauge plane at 0.25 mm above the seating plane.