# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 120MHz                                                                                  |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, Memory Card, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                       |

| Number of I/O              | 82                                                                                      |

| Program Memory Size        | 1MB (1M x 8)                                                                            |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 132K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                   |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                      |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 100-LQFP                                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f207vgt7                   |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

60/182

DocID15818 Rev 13

|        |          |                |                        |           |              | Та             | able 10. /     | Alternat            | te function | on map             | ping                      |                    |                                            |                      |            |       |          |

|--------|----------|----------------|------------------------|-----------|--------------|----------------|----------------|---------------------|-------------|--------------------|---------------------------|--------------------|--------------------------------------------|----------------------|------------|-------|----------|

|        |          | AF0            | AF1                    | AF2       | AF3          | AF4            | AF5            | AF6                 | AF7         | AF8                | AF9                       | AF10               | AF11                                       | AF12                 | AF13       |       |          |

|        | Port     | SYS            | TIM1/2                 | TIM3/4/5  | TIM8/9/10/11 | 12C1/12C2/12C3 | SPI1/SPI2/I2S2 | SPI3/I2S3           | USART1/2/3  | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 | OTG_FS/ OTG_HS     | ЕТН                                        | FSMC/SDIO/<br>OTG_HS | DCMI       | AF014 | AF15     |

|        | PA0-WKUP | -              | TIM2_CH1_ETR           | TIM 5_CH1 | TIM8_ETR     | -              | -              |                     | USART2_CTS  | UART4_TX           | -                         | -                  | ETH_MII_CRS                                | -                    | -          | -     | EVENTOUT |

|        | PA1      | -              | TIM2_CH2               | TIM5_CH2  | -            | -              | -              |                     | USART2_RTS  | UART4_RX           | -                         | -                  | ETH_MII<br>_RX_CLK<br>ETH_RMII<br>_REF_CLK | -                    | -          | -     | EVENTOUT |

|        | PA2      | -              | TIM2_CH3               | TIM5_CH3  | TIM9_CH1     | -              | -              |                     | USART2_TX   | -                  | -                         | -                  | ETH_MDIO                                   | -                    | -          | -     | EVENTOUT |

|        | PA3      | -              | TIM2_CH4               | TIM5_CH4  | TIM9_CH2     | -              | -              |                     | USART2_RX   | -                  | -                         | OTG_HS_ULPI_D0     | ETH _MII_COL                               | -                    | -          | -     | EVENTOUT |

|        | PA4      | -              | -                      | -         | -            | -              | SPI1_NSS       | SPI3_NSS<br>I2S3_WS | USART2_CK   | -                  | -                         |                    | -                                          | OTG_HS_SOF           | DCMI_HSYNC | -     | EVENTOUT |

|        | PA5      | -              | TIM2_CH1_ETR           | -         | TIM8_CH1N    | -              | SPI1_SCK       | -                   | -           | -                  | -                         | OTG_HS_ULPI_C<br>K | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA6      | -              | TIM1_BKIN              | TIM3_CH1  | TIM8_BKIN    | -              | SPI1_MISO      | -                   | -           | -                  | TIM13_CH1                 | -                  | -                                          | -                    | DCMI_PIXCK | -     | EVENTOUT |

| Port A | PA7      | -              | TIM1_CH1N              | TIM3_CH2  | TIM8_CH1N    | -              | SPI1_MOSI      | -                   | -           | -                  | TIM14_CH1                 | -                  | ETH_MII_RX_DV<br>ETH_RMII<br>_CRS_DV       | -                    | -          | -     | EVENTOUT |

|        | PA8      | MCO1           | TIM1_CH1               | -         | -            | I2C3_SCL       | -              | -                   | USART1_CK   | -                  | -                         | OTG_FS_SOF         | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA9      | -              | TIM1_CH2               | -         | -            | I2C3_SMBA      | -              | -                   | USART1_TX   | -                  | -                         |                    | -                                          | -                    | DCMI_D0    | -     | EVENTOUT |

|        | PA10     | -              | TIM1_CH3               | -         | -            | -              | -              | -                   | USART1_RX   | -                  | -                         | OTG_FS_ID          | -                                          | -                    | DCMI_D1    | -     | EVENTOUT |

|        | PA11     | -              | TIM1_CH4               | -         | -            | -              | -              | -                   | USART1_CTS  | -                  | CAN1_RX                   | OTG_FS_DM          | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA12     | -              | TIM1_ETR               | -         | -            | -              | -              | -                   | USART1_RTS  | -                  | CAN1_TX                   | OTG_FS_DP          | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA13     | JTMS-<br>SWDIO | -                      | -         | -            | -              | -              | -                   | -           | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA14     | JTCK-<br>SWCLK | -                      | -         | -            | -              | -              | -                   | -           | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

|        | PA15     | JTDI           | TIM 2_CH1<br>TIM 2_ETR | -         | -            | -              | SPI1_NSS       | SPI3_NSS<br>I2S3_WS | -           | -                  | -                         | -                  | -                                          | -                    | -          | -     | EVENTOUT |

5

## 5 Memory mapping

The memory map is shown in *Figure 16*.

## 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3 V (for the 1.8 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

## 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 6.1.4 Loading capacitor

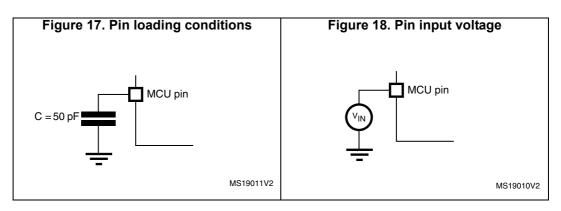

The loading conditions used for pin parameter measurement are shown in *Figure 17*.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 18*.

| Table To: Limitations depending on the operating power supply range |                                    |                                                                               |                                                                                                              |                                                                                                        |                                                                                                                                                                                                                                                               |                                                  |  |

|---------------------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|

| Operating<br>power<br>supply<br>range                               | ADC<br>operation                   | Maximum<br>Flash<br>memory<br>access<br>frequency<br>(f <sub>Flashmax</sub> ) | Number of wait<br>states at<br>maximum CPU<br>frequency<br>(f <sub>CPUmax</sub> =<br>120 MHz) <sup>(1)</sup> | I/O operation                                                                                          | FSMC_CLK<br>frequency for<br>synchronous<br>accesses                                                                                                                                                                                                          | Possible<br>Flash<br>memory<br>operations        |  |

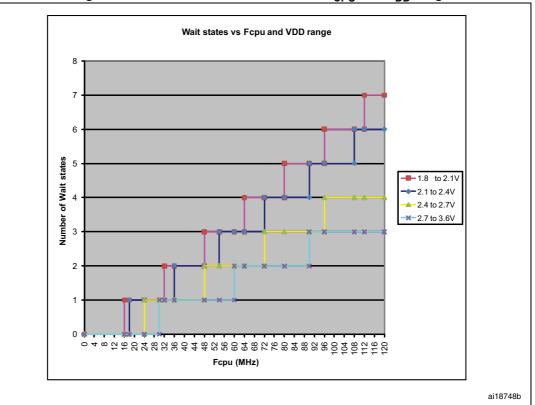

| V <sub>DD</sub> =1.8 to<br>2.1 V <sup>(2)</sup>                     | Conversion<br>time up to<br>1 Msps | 16 MHz with<br>no Flash<br>memory wait<br>state                               | 7 <sup>(3)</sup>                                                                                             | <ul> <li>Degraded</li> <li>speed</li> <li>performance</li> <li>No I/O</li> <li>compensation</li> </ul> | Up to 30 MHz                                                                                                                                                                                                                                                  | 8-bit erase<br>and program<br>operations<br>only |  |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                                   | Conversion<br>time up to<br>1 Msps | 18 MHz with<br>no Flash<br>memory wait<br>state                               | 6 <sup>(3)</sup>                                                                                             | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>No I/O<br/>compensation</li> </ul>                | Up to 30 MHz                                                                                                                                                                                                                                                  | 16-bit erase<br>and program<br>operations        |  |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                                   | Conversion<br>time up to<br>2 Msps | 24 MHz with<br>no Flash<br>memory wait<br>state                               | 4 <sup>(3)</sup>                                                                                             | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>I/O<br/>compensation<br/>works</li> </ul>         | Up to 48 MHz                                                                                                                                                                                                                                                  | 16-bit erase<br>and program<br>operations        |  |

| V <sub>DD</sub> = 2.7 to<br>3.6 V <sup>(4)</sup>                    | Conversion<br>time up to<br>2 Msps | 30 MHz with<br>no Flash<br>memory wait<br>state                               | 3(3)                                                                                                         | <ul> <li>Full-speed<br/>operation</li> <li>I/O<br/>compensation<br/>works</li> </ul>                   | $\begin{array}{l} - \mbox{ Up to } \\ 60 \mbox{ MHz } \\ \mbox{ when } \mbox{ V}_{\mbox{DD}} = \\ 3.0 \mbox{ to } 3.6 \mbox{ V} \\ - \mbox{ Up to } \\ 48 \mbox{ MHz } \\ \mbox{ when } \mbox{ V}_{\mbox{DD}} = \\ 2.7 \mbox{ to } 3.0 \mbox{ V} \end{array}$ | 32-bit erase<br>and program<br>operations        |  |

Table 15. Limitations depending on the operating power supply range

1. The number of wait states can be reduced by reducing the CPU frequency (see Figure 21).

On devices in WLCSP64+2 package, if IRROFF is set to V<sub>DD</sub>, the supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

3. Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

4. The voltage range for OTG USB FS can drop down to 2.7 V. However it is degraded between 2.7 and 3 V.

Figure 21. Number of wait states versus  $f_{\mbox{CPU}}$  and  $V_{\mbox{DD}}$  range

1. The supply voltage can drop to 1.7 V when the device operates in the 0 to 70  $^\circ\text{C}$  temperature range and IRROFF is set to V\_DD.

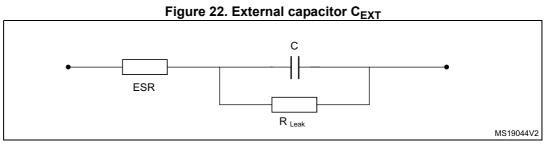

## 6.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 16*.

1. Legend: ESR is the equivalent series resistance.

#### Table 16. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

| Symbol | Parameter                         | Conditions |

|--------|-----------------------------------|------------|

| CEXT   | Capacitance of external capacitor | 2.2 µF     |

| ESR    | ESR of external capacitor         | < 2 Ω      |

1. When bypassing the voltage regulator, the two 2.2  $\mu F$  V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

## 6.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for  $T_A$ .

| Symbol           | Parameter                      | Min | Max | Unit  |

|------------------|--------------------------------|-----|-----|-------|

| 1                | V <sub>DD</sub> rise time rate | 20  | 8   | us/V  |

| <sup>I</sup> VDD | V <sub>DD</sub> fall time rate | 20  | 8   | μ3/ ν |

#### Table 17. Operating conditions at power-up / power-down (regulator ON)

## 6.3.4 Operating conditions at power-up / power-down (regulator OFF)

Subject to general operating conditions for  $T_A$ .

| Table 18. Operating conditions at power-up   | / power-down (regulator OFF) |

|----------------------------------------------|------------------------------|

| Table 10. Operating conditions at power-up / | power-down (regulator or r)  |

| Symbol            | Parameter                                    | Conditions | Min | Max | Unit |

|-------------------|----------------------------------------------|------------|-----|-----|------|

| t <sub>VDD</sub>  | V <sub>DD</sub> rise time rate               | Power-up   | 20  | 8   |      |

|                   | V <sub>DD</sub> fall time rate               | Power-down | 20  | 8   |      |

|                   | $V_{CAP\_1}$ and $V_{CAP\_2}$ rise time rate | Power-up   | 20  | ∞   | µs/V |

| t <sub>VCAP</sub> | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | ∞   |      |

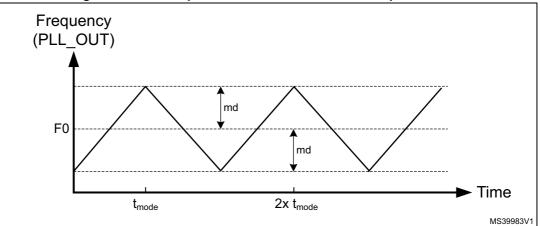

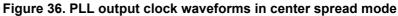

*Figure 36* and *Figure 37* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is f<sub>PLL\_OUT</sub> nominal.

T<sub>mode</sub> is the modulation period.

md is the modulation depth.

Figure 37. PLL output clock waveforms in down spread mode

## 6.3.12 Memory characteristics

#### Flash memory

The characteristics are given at  $T_{\text{A}}$  = –40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

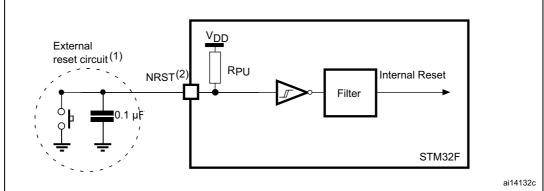

#### 6.3.17 **NRST** pin characteristics

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor, R<sub>PU</sub> (see Table 49).

Unless otherwise specified, the parameters given in Table 49 are derived from tests performed under the ambient temperature and  $V_{\text{DD}}$  supply voltage conditions summarized in Table 14.

| Symbol                               | Parameter                                       | Conditions              | Min | Тур | Max | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------|-----|-----|-----|------|

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(1)</sup> | $V_{IN} = V_{SS}$       | 30  | 40  | 50  | kΩ   |

| V <sub>F(NRST)</sub> <sup>(2)</sup>  | NRST Input filtered pulse                       | -                       | -   | -   | 100 | ns   |

| V <sub>NF(NRST)</sub> <sup>(2)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V | 300 | -   | -   | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal Reset source   | 20  | -   | -   | μs   |

#### Table 49. NRST pin characteristics

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series 1. resistance must be minimum (~10% order).

2. Guaranteed by design, not tested in production.

#### Figure 40. Recommended NRST pin protection

- The reset network protects the device against parasitic resets. 1.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in 2. Table 49. Otherwise the reset is not taken into account by the device.

#### **USB OTG FS characteristics**

The USB OTG interface is USB-IF certified (Full-Speed). This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol                              | Parameter                           | Мах | Unit |  |  |  |  |  |

|-------------------------------------|-------------------------------------|-----|------|--|--|--|--|--|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG FS transceiver startup time | 1   | μs   |  |  |  |  |  |

Table 56. USB OTG FS startup time

1. Guaranteed by design, not tested in production.

| Sym            | bol                                  | Parameter                                                 | Conditions                                                       | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup> | Unit |

|----------------|--------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------|---------------------|------|---------------------|------|

|                | $V_{DD}$                             | USB OTG FS operating<br>voltage                           |                                                                  | 3.0 <sup>(2)</sup>  | -    | 3.6                 | V    |

| Input          | V <sub>DI</sub> <sup>(3)</sup>       | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                                 | 0.2                 | -    | -                   |      |

| levels         | V <sub>CM</sub> <sup>(3)</sup>       | Differential common mode range                            | Includes V <sub>DI</sub> range                                   | 0.8                 | -    | 2.5                 | V    |

|                | $V_{SE}^{(3)}$                       | Single ended receiver threshold                           |                                                                  | 1.3                 | -    | 2.0                 |      |

| Output         | V <sub>OL</sub>                      | Static output level low                                   | $\rm R_L$ of 1.5 k\Omega to 3.6 $\rm V^{(4)}$                    | -                   | -    | 0.3                 | V    |

| levels         | V <sub>OH</sub>                      | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}{}^{(4)}$ | 2.8                 | -    | 3.6                 | v    |

| R <sub>P</sub> |                                      | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V <sub>IN</sub> = V <sub>DD</sub>                                | 17                  | 21   | 24                  |      |

|                | D                                    | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | VIN - VDD                                                        | 0.65                | 1.1  | 2.0                 | kΩ   |

|                | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP) |                                                           | V <sub>IN</sub> = V <sub>SS</sub>                                | 1.5                 | 1.8  | 2.1                 |      |

| R <sub>P</sub> | יט                                   | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>                                | 0.25                | 0.37 | 0.55                |      |

#### Table 57. USB OTG FS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The STM32F205xx and STM32F207xx USB OTG FS functionality is ensured down to 2.7 V but not the full USB OTG FS electrical characteristics which are degraded in the 2.7-to-3.0 V  $V_{DD}$  voltage range.

3. Guaranteed by design, not tested in production.

4. R<sub>L</sub> is the load connected on the USB OTG FS drivers

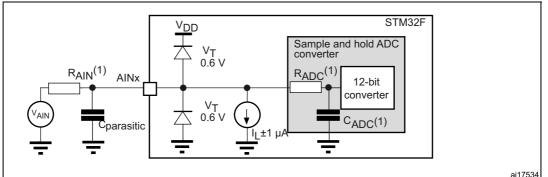

being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 6.3.16 does not affect the ADC accuracy.

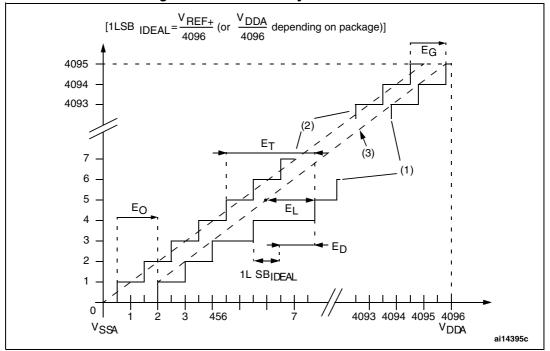

- Example of an actual transfer curve 1.

- 2. Ideal transfer curve

- End point correlation line. 3.

- $E_T$  = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. 4. EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one.

EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

$C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced. 2.

Refer to Table 66 for the values of  $\mathsf{R}_{AIN},\,\mathsf{R}_{ADC}$  and  $\mathsf{C}_{ADC}$ 1.

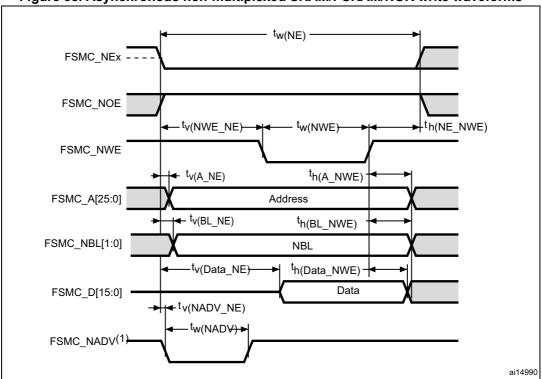

Figure 58. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

| Table 73. A | Asynchronous non-multiplexed SRAM | M/PSRAM/NO | R write timin | gs <sup>(1)(2)</sup> |

|-------------|-----------------------------------|------------|---------------|----------------------|

|             |                                   |            |               |                      |

| Symbol                   | Parameter                                | Min                     | Мах                     | Unit |

|--------------------------|------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>       | FSMC_NE low time                         | 3T <sub>HCLK</sub>      | 3T <sub>HCLK</sub> + 4  | ns   |

| t <sub>v(NWE_NE</sub> )  | FSMC_NEx low to FSMC_NWE low             | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>w(NWE)</sub>      | FSMC_NWE low time                        | T <sub>HCLK</sub> – 0.5 | T <sub>HCLK</sub> + 3   | ns   |

| t <sub>h(NE_NWE)</sub>   | FSMC_NWE high to FSMC_NE high hold time  | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>v(A_NE)</sub>     | FSMC_NEx low to FSMC_A valid             | -                       | 0                       | ns   |

| t <sub>h(A_NWE)</sub>    | Address hold time after FSMC_NWE high    | T <sub>HCLK</sub> - 3   | -                       | ns   |

| t <sub>v(BL_NE)</sub>    | FSMC_NEx low to FSMC_BL valid            | -                       | 0.5                     | ns   |

| t <sub>h(BL_NWE)</sub>   | FSMC_BL hold time after FSMC_NWE<br>high | T <sub>HCLK</sub> – 1   | -                       | ns   |

| t <sub>v(Data_NE)</sub>  | Data to FSMC_NEx low to Data valid       | -                       | T <sub>HCLK</sub> + 5   | ns   |

| t <sub>h(Data_NWE)</sub> | Data hold time after FSMC_NWE high       | T <sub>HCLK</sub> +0.5  | -                       | ns   |

| t <sub>v(NADV_NE)</sub>  | FSMC_NEx low to FSMC_NADV low            | -                       | 2                       | ns   |

| t <sub>w(NADV)</sub>     | FSMC_NADV low time                       | -                       | T <sub>HCLK</sub> + 1.5 | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

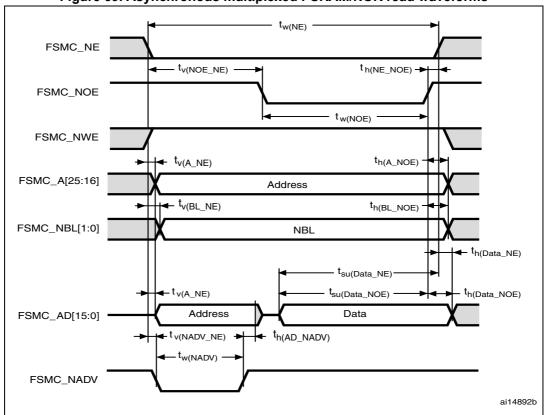

Figure 59. Asynchronous multiplexed PSRAM/NOR read waveforms

Table 74. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                                                | Min                     | Max                     | Unit |

|---------------------------|----------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                         | 3T <sub>HCLK</sub> -1   | 3T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                             | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                        | T <sub>HCLK</sub> -1    | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time                  | 0                       | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                             | -                       | 2                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                            | 1                       | 2.5                     | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                       | T <sub>HCLK</sub> – 1.5 | T <sub>HCLK</sub>       | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD(adress) valid hold time after<br>FSMC_NADV high) | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high                    | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL time after FSMC_NOE high                         | 0                       | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                            | -                       | 1                       | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time                         | T <sub>HCLK</sub> + 2   | -                       | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time                         | T <sub>HCLK</sub> + 3   | -                       | ns   |

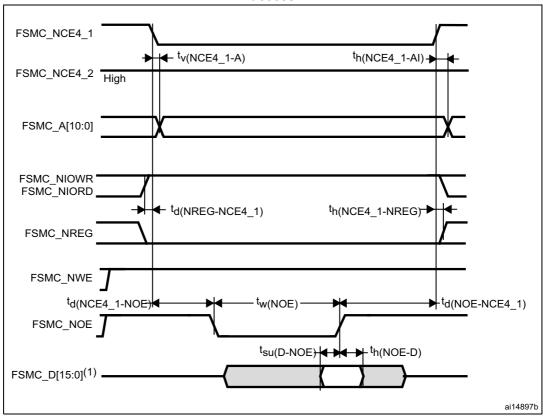

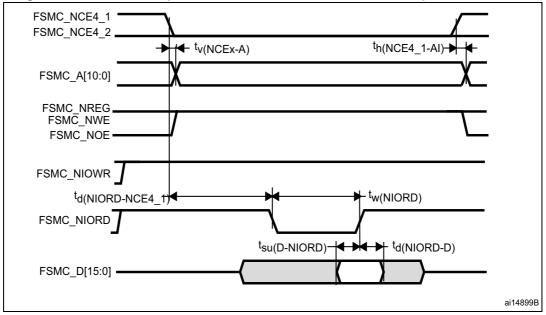

Figure 67. PC Card/CompactFlash controller waveforms for attribute memory read access

1. Only data bits 0...7 are read (bits 8...15 are disregarded).

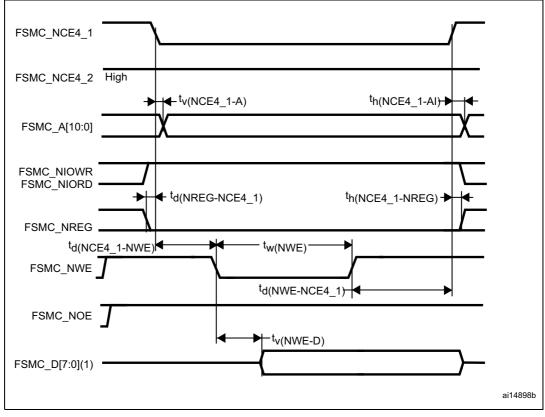

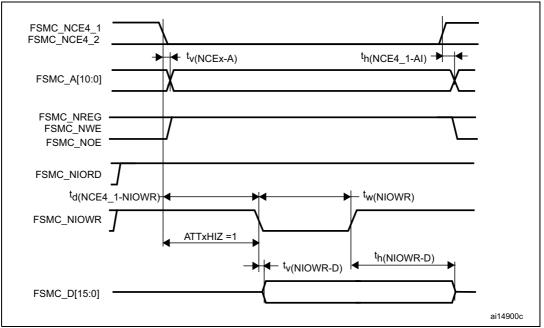

Figure 68. PC Card/CompactFlash controller waveforms for attribute memory write access

1. Only data bits 0...7 are driven (bits 8...15 remains Hi-Z).

#### Figure 69. PC Card/CompactFlash controller waveforms for I/O space read access

Figure 70. PC Card/CompactFlash controller waveforms for I/O space write access

# Table 80. Switching characteristics for PC Card/CF read and write cycles in attribute/common space<sup>(1)(2)</sup>

| Symbol                    | Parameter                                    | Min                      | Max                    | Unit |

|---------------------------|----------------------------------------------|--------------------------|------------------------|------|

| t <sub>v(NCEx-A)</sub>    | FSMC_Ncex low to FSMC_Ay valid               | -                        | 0                      | ns   |

| t <sub>h(NCEx_AI)</sub>   | FSMC_NCEx high to FSMC_Ax invalid            | 4                        | -                      | ns   |

| t <sub>d(NREG-NCEx)</sub> | FSMC_NCEx low to FSMC_NREG valid             | -                        | 3.5                    | ns   |

| t <sub>h(NCEx-NREG)</sub> | FSMC_NCEx high to FSMC_NREG invalid          | T <sub>HCLK</sub> + 4    | -                      | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                        | 5T <sub>HCLK</sub> + 1 | ns   |

| t <sub>d(NCEx-NOE)</sub>  | FSMC_NCEx low to FSMC_NOE low                | -                        | 5T <sub>HCLK</sub>     | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low width                           | 8T <sub>HCLK</sub> - 0.5 | 8T <sub>HCLK</sub> + 1 | ns   |

| t <sub>d(NOE_NCEx)</sub>  | FSMC_NOE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> + 2.5 | -                      | ns   |

| t <sub>su (D-NOE)</sub>   | FSMC_D[15:0] valid data before FSMC_NOE high | 4                        | -                      | ns   |

| t <sub>h (N0E-D)</sub>    | FSMC_N0E high to FSMC_D[15:0] invalid        | 2                        | -                      | ns   |

| t <sub>w(NWE)</sub>       | FSMC_NWE low width                           | 8T <sub>HCLK</sub> - 1   | 8T <sub>HCLK</sub> + 4 | ns   |

| t <sub>d(NWE_NCEx</sub> ) | FSMC_NWE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> + 1.5 | -                      | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                        | 5HCLK+ 1               | ns   |

| t <sub>v (NWE-D)</sub>    | FSMC_NWE low to FSMC_D[15:0] valid           | -                        | 0                      | ns   |

| t <sub>h (NWE-D)</sub>    | FSMC_NWE high to FSMC_D[15:0] invalid        | 8T <sub>HCLK</sub>       | -                      | ns   |

| t <sub>d (D-NWE)</sub>    | FSMC_D[15:0] valid before FSMC_NWE high      | 13T <sub>HCLK</sub>      | -                      | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

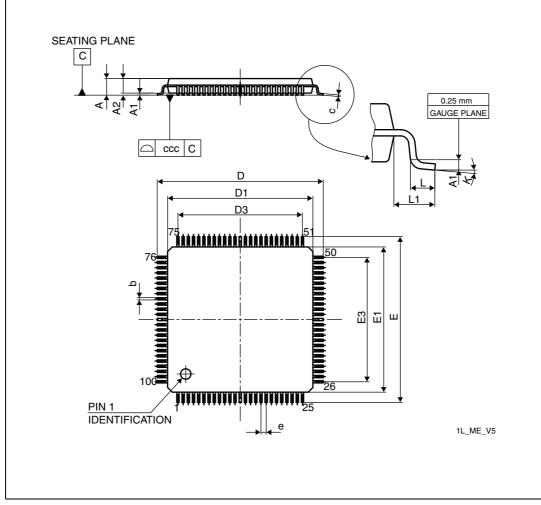

## 7.3 LQFP100 package information

Figure 81. LQFP100 - 100-pin, 14 x 14 mm low-profile quad flat package outline

1. Drawing is not to scale.

| mechanical data |        |             |        |                       |        |        |

|-----------------|--------|-------------|--------|-----------------------|--------|--------|

| Symbol          |        | millimeters |        | inches <sup>(1)</sup> |        |        |

|                 | Min    | Тур         | Мах    | Min                   | Тур    | Max    |

| А               | -      | -           | 1.600  | -                     | -      | 0.0630 |

| A1              | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |

| A2              | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |

| b               | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |

| С               | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |

| D               | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |

| D1              | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |

Table 90. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package mechanical data

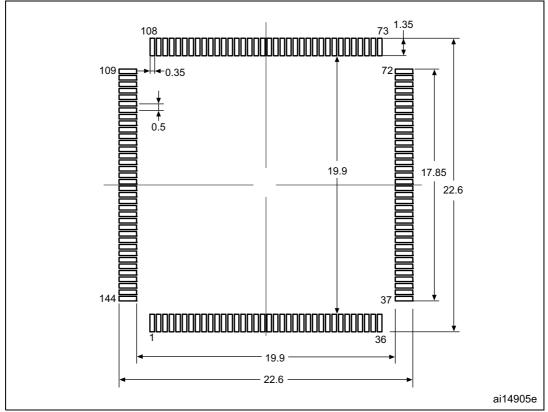

Figure 85. LQFP144 - 144-pin,20 x 20 mm low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

|             | Table 97. Document revision history (continued) |                                                                                                                                                                                                                                                                                                    |  |  |  |

|-------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date        | Revision                                        | Changes                                                                                                                                                                                                                                                                                            |  |  |  |

|             |                                                 | Update I/Os in <i>Section : Features</i> .<br>Added WLCSP64+2 package. Added note 1 related to LQFP176 on                                                                                                                                                                                          |  |  |  |

|             |                                                 | cover page.                                                                                                                                                                                                                                                                                        |  |  |  |

|             |                                                 | Added trademark for ART accelerator. Updated Section 3.2: Adaptive real-time memory accelerator (ART Accelerator™).                                                                                                                                                                                |  |  |  |

|             |                                                 | Updated Figure 5: Multi-AHB matrix.                                                                                                                                                                                                                                                                |  |  |  |

|             |                                                 | Added case of BOR inactivation using IRROFF on WLCSP devices in <i>Section 3.15: Power supply supervisor</i> .                                                                                                                                                                                     |  |  |  |

|             |                                                 | Reworked <i>Section 3.16: Voltage regulator</i> to clarify regulator off modes.<br>Renamed PDROFF, IRROFF in the whole document.                                                                                                                                                                   |  |  |  |

|             |                                                 | Added Section 3.19: VBAT operation.                                                                                                                                                                                                                                                                |  |  |  |

|             |                                                 | Updated LIN and IrDA features for UART4/5 in Table 6: USART feature comparison.                                                                                                                                                                                                                    |  |  |  |

|             |                                                 | <i>Table 8: STM32F20x pin and ball definitions</i> : Modified V <sub>DD_3</sub> pin, and added note related to the FSMC_NL pin; renamed BYPASS-REG REGOFF, and add IRROFF pin; renamed USART4/5 UART4/5. USART4 pins renamed UART4.                                                                |  |  |  |

|             |                                                 | Changed $V_{SS}$ SA to $V_{SS}$ , and $V_{DD}$ SA pin reserved for future use.                                                                                                                                                                                                                     |  |  |  |

|             |                                                 | Updated maximum HSE crystal frequency to 26 MHz.                                                                                                                                                                                                                                                   |  |  |  |

|             | 5                                               | Section 6.2: Absolute maximum ratings: Updated V <sub>IN</sub> minimum and maximum values and note related to five-volt tolerant inputs in <i>Table 11</i> . Voltage characteristics. Updated I <sub>INJ(PIN)</sub> maximum values and related notes in <i>Table 12: Current characteristics</i> . |  |  |  |

| 25-Nov-2010 |                                                 | Updated V <sub>DDA</sub> minimum value in <i>Table 14: General operating conditions</i> .                                                                                                                                                                                                          |  |  |  |

|             |                                                 | Added Note 2 and updated Maximum CPU frequency in <i>Table 15:</i><br><i>Limitations depending on the operating power supply range</i> , and added<br><i>Figure 21: Number of wait states versus fCPU and VDD range</i> .                                                                          |  |  |  |

|             |                                                 | Added brownout level 1, 2, and 3 thresholds in <i>Table 19: Embedded</i> reset and power control block characteristics.                                                                                                                                                                            |  |  |  |

|             |                                                 | Changed f <sub>OSC_IN</sub> maximum value in <i>Table 30: HSE 4-26 MHz oscillator characteristics</i> .                                                                                                                                                                                            |  |  |  |

|             |                                                 | Changed f <sub>PLL_IN</sub> maximum value in <i>Table 34: Main PLL characteristics</i> , and updated jitter parameters in <i>Table 35: PLLI2S (audio PLL) characteristics</i> .                                                                                                                    |  |  |  |

|             |                                                 | Section 6.3.16: I/O port characteristics: updated V <sub>IH</sub> and V <sub>IL</sub> in Table 48. I/O AC characteristics.                                                                                                                                                                         |  |  |  |

|             |                                                 | Added Note 1 below Table 47: Output voltage characteristics.                                                                                                                                                                                                                                       |  |  |  |

|             |                                                 | Updated R <sub>PD</sub> and R <sub>PU</sub> parameter description in <i>Table 57: USB OTG FS</i><br>DC electrical characteristics.                                                                                                                                                                 |  |  |  |

|             |                                                 | Updated V <sub>REF+</sub> minimum value in <i>Table 66: ADC characteristics</i> .                                                                                                                                                                                                                  |  |  |  |

|             |                                                 | Updated Table 71: Embedded internal reference voltage.                                                                                                                                                                                                                                             |  |  |  |

|             |                                                 | Removed Ethernet and USB2 for 64-pin devices in <i>Table 101: Main applications versus package for STM32F2xxx microcontrollers</i> .                                                                                                                                                               |  |  |  |

|             |                                                 | Added A.2: USB OTG full speed (FS) interface solutions, removed<br>"OTG FS connection with external PHY" figure, updated Figure 87,<br>Figure 88, and Figure 90 to add STULPI01B.                                                                                                                  |  |  |  |

Table 97. Document revision history (continued)

|             | Table 97. Document revision history (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date        | Revision                                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 14-Jun-2011 | 7                                               | Added SDIO in <i>Table 2: STM32F205xx features and peripheral counts.</i><br>Updated V <sub>IN</sub> for 5V tolerant pins in <i>Table 11: Voltage characteristics.</i><br>Updated jitter parameters description in <i>Table 34: Main PLL characteristics.</i><br>Remove jitter values for system clock in <i>Table 35: PLLI2S (audio PLL) characteristics.</i><br>Updated <i>Table 42: EMI characteristics.</i><br>Updated <i>Table 42: EMI characteristics.</i><br>Updated <i>Note 2</i> in <i>Table 52: I2C characteristics.</i><br>Updated Avg_Slope typical value and $T_{S\_temp}$ minimum value in <i>Table 69: Temperature sensor characteristics.</i><br>Updated $T_{S\_vbat}$ minimum value in <i>Table 70: VBAT monitoring characteristics.</i><br>Updated $T_{S\_vrefint}$ minimum value in <i>Table 71: Embedded internal reference voltage.</i><br>Added Software option in <i>Section 8: Part numbering.</i><br>In <i>Table 101: Main applications versus package for STM32F2xxx microcontrollers,</i> renamed USB1 and USB2, USB OTG FS and USB OTG HS, respectively; and removed USB OTG HS on 64-pin package; added <i>Note 1</i> and <i>Note 2.</i>                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 20-Dec-2011 | 8                                               | Updated SDIO register addresses in <i>Figure 16: Memory map</i> .<br>Updated <i>Figure 3: Compatible board design between STM32F10xx and</i><br><i>STM32F2xx for LQFP144 package, Figure 2: Compatible board design</i><br><i>between STM32F10xx and STM32F2xx for LQFP100 package,</i><br><i>Figure 1: Compatible board design between STM32F10xx and</i><br><i>STM32F2xx for LQFP64 package,</i> and added <i>Figure 4: Compatible</i><br><i>board design between STM32F10xx and STM32F2xx for LQFP176</i><br><i>package.</i><br>Updated <i>Section 3.3: Memory protection unit.</i><br>Updated <i>Section 3.6: Embedded SRAM.</i><br>Updated <i>Section 3.6: Embedded SRAM.</i><br>Updated <i>Section 3.28: Universal serial bus on-the-go full-speed</i><br>( <i>OTG_FS</i> ) to remove external FS OTG PHY support.<br>In <i>Table 8: STM32F20x pin and ball definitions:</i> changed SPI2_MCK<br>and SPI3_MCK to I2S2_MCK and I2S3_MCK, respectively. Added ETH<br>_RMII_TX_EN attlernate function to PG11. Added EVENTOUT in the<br>list of alternate functions for I/O pin/balls. Removed OTG_FS_SDA,<br>OTG_FS_SCL and OTG_FS_INTN alternate functions.<br>In <i>Table 10: Alternate function mapping:</i> changed I2S3_SCK to<br>I2S3_MCK for PC7/AF6, added FSMC_NCE3 for PG9, FSMC_NE3 for<br>PG10, and FSMC_NCE2 for PD7. Removed OTG_FS_SDA,<br>OTG_FS_SCL and OTG_FS_INTN alternate functions. Changed<br>I2S3_SCK into I2S3_MCK for PC7/AF6. Updated peripherals<br>corresponding to AF12.<br>Removed CEXT and ESR from <i>Table 14: General operating conditions</i> . |  |  |  |

Table 97. Document revision history (continued)

| Data        | Table 97. Document revision history (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date        | Revision                                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 24-Apr-2012 | 9<br>(continued)                                | Removed support of I2C for OTG PHY in Section 3.29: Universal serial bus on-the-go high-speed (OTG_HS).<br>Removed OTG_HS_SCL, OTG_HS_SDA, OTG_FS_INTN in Table 8:<br>STM32F20x pin and ball definitions and Table 10: Alternate function mapping.<br>Renamed PH10 alternate function into TIM5_CH1 in Table 10: Alternate function mapping.<br>Added Table 9: FSMC pin definition.<br>Updated Note 1 in Table 14: General operating conditions, Note 2 in<br>Table 15: Limitations depending on the operating power supply range, and Note 1 below Figure 21: Number of wait states versus fCPU and<br>VDD range.<br>Updated VpOR/PDR in Table 19: Embedded reset and power control<br>block characteristics.<br>Updated typical values in Table 24: Typical and maximum current<br>consumptions in Standby mode and Table 25: Typical and maximum<br>current consumptions in VBAT mode.<br>Updated Table 30: HSE 4-26 MHz oscillator characteristics and<br>Table 31: LSE oscillator characteristics (TaSE = 32.768 kHz).<br>Updated Table 30: HSE 4-26 MHz oscillator characteristics and<br>Table 31: LSE oscillator characteristics, Table 38: Flash<br>memory programming, and Table 39: Flash memory programming with<br>VPP.<br>Updated Section : Output driving current.<br>Updated Note 3 and removed note related to minimum hold time value<br>in Table 52: I2C characteristics.<br>Updated Note 1, C <sub>ADC</sub> , I <sub>VREF+</sub> , and I <sub>VDDA</sub> in Table 66: ADC<br>characteristics.<br>Updated Note 1 in Table 67: ADC accuracy.<br>Updated Note 1 in Table 68: DAC characteristics.<br>Updated Note 1 in Table 67: ADC accuracy.<br>Updated Note 3 and note concerning ADC accuracy vs. negative<br>injection current in Table 67: ADC accuracy.<br>Updated Note 1 in Table 68: DAC characteristics.<br>Updated Section Figure 88: UFBGA176+25 - ultra thin fine pitch ball<br>grid array 10 × 0.6 mm, package outlin |  |  |

Table 97. Document revision history (continued)