#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 120MHz                                                                                  |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, Memory Card, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                       |

| Number of I/O              | 114                                                                                     |

| Program Memory Size        | 512KB (512K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 132K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                   |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 144-LQFP                                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f207zet6                   |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                               |                         | Table                                                                        | 2. STM3 | 82F205        | xx feat       | ures a          | nd perip | heral co                  | ounts         | 5   |      |     |        |      |      |

|-------------------------------|-------------------------|------------------------------------------------------------------------------|---------|---------------|---------------|-----------------|----------|---------------------------|---------------|-----|------|-----|--------|------|------|

|                               | Peripherals             |                                                                              | ST      | /132F205R     | Rx            |                 |          | STM32                     | F205V         | x   |      | S   | TM32F2 | 05Zx |      |

| Flash memory in               | n Kbytes                | 128                                                                          | 256     | 512           | 768           | 1024            | 128      | 256                       | 512           | 768 | 1024 | 256 | 512    | 768  | 1024 |

| SRAM in Kbytes                | System<br>(SRAM1+SRAM2) | 64         96         128           (48+16)         (80+16)         (112+16) |         | 64<br>(48+16) | 96<br>(80+16) | 128<br>(112+16) |          | 6)                        | 96<br>(80+16) |     |      | 3)  |        |      |      |

|                               | Backup                  |                                                                              |         | 4             |               |                 |          |                           | 4             |     |      |     | 4      |      |      |

| FSMC memory of                | controller              | No Yes <sup>(1)</sup>                                                        |         |               |               |                 |          |                           |               |     |      |     |        |      |      |

| Ethernet                      |                         |                                                                              |         |               |               |                 |          | No                        |               |     |      |     |        |      |      |

|                               | General-purpose         |                                                                              |         |               |               |                 |          | 10                        |               |     |      |     |        |      |      |

|                               | Advanced-control        |                                                                              |         |               |               |                 |          | 2                         |               |     |      |     |        |      |      |

| Timers                        | Basic                   |                                                                              |         |               |               |                 |          | 2                         |               |     |      |     |        |      |      |

|                               | IWDG                    |                                                                              |         |               |               |                 |          | Yes                       |               |     |      |     |        |      |      |

|                               | WWDG                    |                                                                              |         |               |               |                 |          | Yes                       |               |     |      |     |        |      |      |

| RTC                           |                         |                                                                              |         |               |               |                 |          | Yes                       |               |     |      |     |        |      |      |

| Random numbei                 | r generator             |                                                                              |         |               |               |                 |          | Yes                       |               |     |      |     |        |      |      |

|                               | SPI/(I <sup>2</sup> S)  | 3/(2) <sup>(2)</sup>                                                         |         |               |               |                 |          |                           |               |     |      |     |        |      |      |

|                               | l <sup>2</sup> C        | 3                                                                            |         |               |               |                 |          |                           |               |     |      |     |        |      |      |

| Comm.<br>interfaces           | USART<br>UART           |                                                                              |         |               | 4<br>2        |                 |          |                           |               |     |      |     |        |      |      |

| interfaces                    | USB OTG FS              |                                                                              |         |               |               |                 |          | Yes                       |               |     |      |     |        |      |      |

|                               | USB OTG HS              |                                                                              |         |               |               |                 |          | Yes                       |               |     |      |     |        |      |      |

|                               | CAN                     |                                                                              |         |               |               |                 |          | 2                         |               |     |      |     |        |      |      |

| Camera interface              | e                       |                                                                              |         |               |               |                 |          | No                        |               |     |      |     |        |      |      |

| GPIOs                         |                         |                                                                              |         | 51            |               |                 |          | 8                         | 32            |     |      |     | 114    |      |      |

| SDIO                          |                         |                                                                              |         |               |               |                 |          | Yes                       |               |     |      |     |        |      |      |

| 12-bit ADC                    |                         |                                                                              |         |               |               |                 |          | 3                         |               |     |      |     |        |      |      |

| Number of chan                | nels                    |                                                                              |         | 16            |               |                 |          | 1                         | 16            |     |      |     | 24     |      |      |

| 12-bit DAC<br>Number of chanı | nels                    |                                                                              |         |               |               |                 |          | Yes<br>2                  |               |     |      |     |        |      |      |

| Maximum CPU f                 | frequency               |                                                                              |         |               |               |                 | 1        | I20 MHz                   |               |     |      |     |        |      |      |

| Operating voltag              | e                       |                                                                              |         |               |               |                 | 1.8      | V to 3.6 V <sup>(3)</sup> |               |     |      |     |        |      |      |

5

14/182

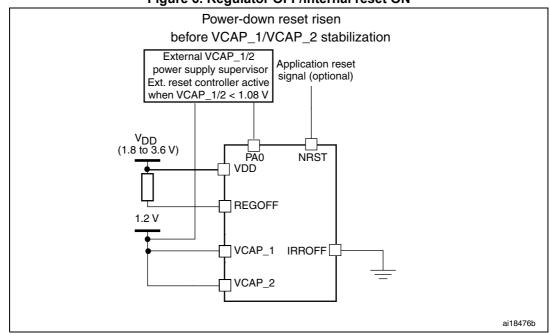

Figure 6. Regulator OFF/internal reset ON

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach 1.08 V is faster than the time for  $V_{DD}$  to reach 1.8 V, then PA0 should be kept low to cover both conditions: until  $V_{CAP_1}$  and  $V_{CAP_2}$  reach 1.08 V and until  $V_{DD}$  reaches 1.8 V (see *Figure 8*).

- Otherwise, If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach 1.08 V is slower than the time for V<sub>DD</sub> to reach 1.8 V, then PA0 should be asserted low externally (see *Figure 9*).

- If V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> go below 1.08 V and V<sub>DD</sub> is higher than 1.8 V, then a reset must be asserted on PA0 pin.

#### **Regulator OFF/internal reset OFF**

On WLCSP64+2 package, this mode activated by connecting REGOFF to V<sub>SS</sub> and IRROFF to V<sub>DD</sub>. IRROFF cannot be activated in conjunction with REGOFF. This mode is available only on the WLCSP64+2 package. It allows to supply externally a 1.2 V voltage source through V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> pins. In this mode, the integrated power-on reset (POR)/ power-down reset (PDR) circuitry is disabled.

An external power supply supervisor should monitor both the external 1.2 V and the external  $V_{DD}$  supply voltage, and should maintain the device in reset mode as long as they remain below a specified threshold. The  $V_{DD}$  specified threshold, below which the device must be maintained under reset, is 1.8 V. This supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range. A comprehensive set of power-saving modes allows to design low-power applications.

## 3.30 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S application. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an  $I^2S$  sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 kHz to 192 kHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I2S flow with an external PLL (or Codec output).

# 3.31 Digital camera interface (DCMI)

The camera interface is not available in STM32F205xx devices.

STM32F207xx products embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain up to 27 Mbyte/s at 27 MHz or 48 Mbyte/s at 48 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw Bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

## 3.32 True random number generator (RNG)

All STM32F2xxx products embed a true RNG that delivers 32-bit random numbers produced by an integrated analog circuit.

# 3.33 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O alternate function configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

To provide fast I/O handling, the GPIOs are on the fast AHB1 bus with a clock up to 120 MHz that leads to a maximum I/O toggling speed of 60 MHz.

## 3.34 ADCs (analog-to-digital converters)

Three 12-bit analog-to-digital converters are embedded and each ADC shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the timers TIM1, TIM2, TIM3, TIM4, TIM5 and TIM8 can be internally connected to the ADC start trigger and injection trigger, respectively, to allow the application to synchronize A/D conversion and timers.

# 3.35 DAC (digital-to-analog converter)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs. The design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

## 3.36 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.8 and 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

DocID15818 Rev 13

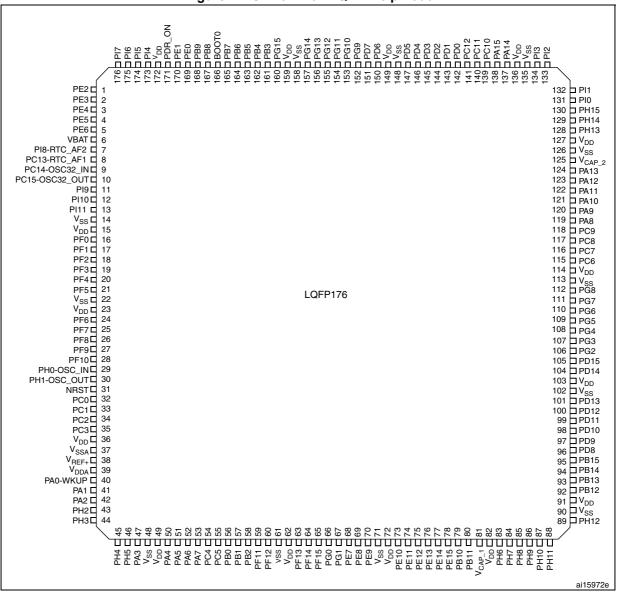

#### Pinouts and pin description

| Figure 14. | STM32F20x L | .QFP176 pi | nout |

|------------|-------------|------------|------|

|------------|-------------|------------|------|

1. RFU means "reserved for future use". This pin can be tied to  $V_{DD}$ ,  $V_{SS}$  or left unconnected.

2. The above figure shows the package top view.

|        |           | Pi      | ns      |         |          |                                                      |                                            |                                                                                   |          | ennitions (continued)                                    |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------|----------|----------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type<br>I/O structure<br>Note          |                                                                                   | Note     | Alternate functions                                      | Additional<br>functions |

| -      | -         | -       | 14      | 20      | J3       | PF4                                                  | I/O                                        | FT                                                                                | (4)      | FSMC_A4, EVENTOUT                                        | ADC3_IN14               |

| -      | -         | -       | 15      | 21      | K3       | PF5                                                  | I/O                                        | FT                                                                                | (4)      | FSMC_A5, EVENTOUT                                        | ADC3_IN15               |

| -      | H9        | 10      | 16      | 22      | G2       | V <sub>SS</sub>                                      | S                                          | -                                                                                 | -        | -                                                        | -                       |

| -      | -         | 11      | 17      | 23      | G3       | V <sub>DD</sub>                                      | S                                          | -                                                                                 | -        | -                                                        | -                       |

| -      | -         | -       | 18      | 24      | K2       | PF6                                                  | I/O                                        | FT                                                                                | (4)      | TIM10_CH1, FSMC_NIORD,<br>EVENTOUT                       | ADC3_IN4                |

| -      | -         | -       | 19      | 25      | K1       | PF7                                                  | I/O                                        | FT                                                                                | (4)      | TIM11_CH1,FSMC_NREG,<br>EVENTOUT                         | ADC3_IN5                |

| -      | -         | -       | 20      | 26      | L3       | PF8                                                  | I/O                                        | I/O FT <sup>(4)</sup> TIM13_CH1,<br>FSMC_NIOWR, EVENTOUT                          |          | ADC3_IN6                                                 |                         |

| -      | -         | -       | 21      | 27      | L2       | PF9                                                  | I/O FT (4) TIM14_CH1, FSMC_CD,<br>EVENTOUT |                                                                                   | ADC3_IN7 |                                                          |                         |

| -      | -         | -       | 22      | 28      | L1       | PF10                                                 | I/O                                        | FT                                                                                | (4)      | FSMC_INTR, EVENTOUT                                      | ADC3_IN8                |

| 5      | E9        | 12      | 23      | 29      | G1       | PH0/OSC_IN<br>(PH0)                                  | I/O                                        | FT                                                                                | -        | EVENTOUT                                                 | OSC_IN <sup>(4)</sup>   |

| 6      | F9        | 13      | 24      | 30      | H1       | PH1/OSC_OUT<br>(PH1)                                 | I/O                                        | FT                                                                                | -        | EVENTOUT                                                 | OSC_OUT <sup>(4)</sup>  |

| 7      | E8        | 14      | 25      | 31      | J1       | NRST                                                 | I/O                                        |                                                                                   | I        | -                                                        | -                       |

| 8      | G9        | 15      | 26      | 32      | M2       | PC0                                                  | I/O                                        | FT                                                                                | (4)      | OTG_HS_ULPI_STP,<br>EVENTOUT                             | ADC123_<br>IN10         |

| 9      | F8        | 16      | 27      | 33      | М3       | PC1                                                  | I/O                                        | FT                                                                                | (4)      | ETH_MDC, EVENTOUT                                        | ADC123_<br>IN11         |

| 10     | D7        | 17      | 28      | 34      | M4       | PC2                                                  | I/O                                        | FT                                                                                | (4)      | SPI2_MISO,<br>OTG_HS_ULPI_DIR,<br>ETH_MII_TXD2, EVENTOUT | ADC123_<br>IN12         |

| 11     | G8        | 18      | 29      | 35      | M5       | PC3                                                  | I/O                                        | I/O FT (4) SPI2_MOSI, I2S2_SD,<br>OTG_HS_ULPI_NXT,<br>ETH_MII_TX_CLK,<br>EVENTOUT |          | ADC123_<br>IN13                                          |                         |

| -      | -         | 19      | 30      | 36      | -        | V <sub>DD</sub>                                      | S                                          |                                                                                   | -        |                                                          |                         |

| 12     | -         | 20      | 31      | 37      | M1       | V <sub>SSA</sub>                                     | SA S                                       |                                                                                   | -        |                                                          |                         |

| -      | -         | -       | -       | -       | N1       | V <sub>REF-</sub>                                    | S                                          | -                                                                                 | -        | -                                                        | -                       |

| -      | F7        | 21      | 32      | 38      | P1       | V <sub>REF+</sub>                                    | S                                          | -                                                                                 | -        | -                                                        | -                       |

|        |           | Pins    |         |         |          |                                                      |                                                         |               |                                                                                     |                                                                                                                                                 |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|---------------------------------------------------------|---------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type                                                | I/O structure | Note                                                                                | Alternate functions                                                                                                                             | Additional<br>functions |

| -      | -         | -       | -       | 84      | N12      | PH7                                                  | I/O                                                     | FT            | -                                                                                   | I2C3_SCL, ETH_MII_RXD3,<br>EVENTOUT                                                                                                             | -                       |

| -      | -         | -       | -       | 85      | M12      | PH8                                                  | 2H8 I/O FT - I2C3_SDA, DCMI_HS<br>EVENTOUT              |               | I2C3_SDA, DCMI_HSYNC,<br>EVENTOUT                                                   | -                                                                                                                                               |                         |

| -      | -         | -       | -       | 86      | M13      | PH9                                                  | PH9 I/O FT - I2C3_SMBA, TIM12_CH2,<br>DCMI_D0, EVENTOUT |               | -                                                                                   |                                                                                                                                                 |                         |

| -      | -         | -       | -       | 87      | L13      | PH10                                                 | I/O                                                     | FT            | -                                                                                   | TIM5_CH1, DCMI_D1,<br>EVENTOUT                                                                                                                  | -                       |

| -      | -         | -       | -       | 88      | L12      | PH11                                                 | I/O                                                     | FT            | -                                                                                   | TIM5_CH2, DCMI_D2,<br>EVENTOUT                                                                                                                  | -                       |

| -      | -         | -       | -       | 89      | K12      | PH12                                                 | I/O                                                     | FT            | -                                                                                   | TIM5_CH3, DCMI_D3,<br>EVENTOUT                                                                                                                  | -                       |

| -      | -         | -       | -       | 90      | H12      | V <sub>SS</sub>                                      | S                                                       | -             | -                                                                                   | -                                                                                                                                               | -                       |

| -      | -         | -       | -       | 91      | J12      | V <sub>DD</sub>                                      | S                                                       | -             | -                                                                                   | -                                                                                                                                               | -                       |

| 33     | J1        | 51      | 73      | 92      | P12      | PB12                                                 | I/O                                                     | FT            | -                                                                                   | SPI2_NSS, I2S2_WS,<br>I2C2_SMBA, USART3_CK,<br>TIM1_BKIN, CAN2_RX,<br>OTG_HS_ULPI_D5,<br>ETH_RMII_TXD0,<br>ETH_MII_TXD0,<br>OTG_HS_ID, EVENTOUT | -                       |

| 34     | H2        | 52      | 74      | 93      | P13      | PB13                                                 | I/O                                                     | FT            | -                                                                                   | SPI2_SCK, I2S2_SCK,<br>USART3_CTS, TIM1_CH1N,<br>CAN2_TX,<br>OTG_HS_ULPI_D6,<br>ETH_RMII_TXD1,<br>ETH_MII_TXD1, EVENTOUT                        | OTG_HS_<br>VBUS         |

| 35     | H1        | 53      | 75      | 94      | R14      | PB14                                                 | PB14 I/O FT - TIM12_CH1,<br>USART3_RTS                  |               | SPI2_MISO, TIM1_CH2N,<br>TIM12_CH1, OTG_HS_DM<br>USART3_RTS, TIM8_CH2N,<br>EVENTOUT | -                                                                                                                                               |                         |

| 36     | G1        | 54      | 76      | 95      | R15      | PB15                                                 | I/O                                                     | FT            | -                                                                                   | SPI2_MOSI, I2S2_SD,<br>TIM1_CH3N, TIM8_CH3N,<br>TIM12_CH2, OTG_HS_DP,<br>RTC_50Hz, EVENTOUT                                                     | -                       |

| -      | -         | 55      | 77      | 96      | P15      | PD8                                                  | I/O                                                     | FT            | -                                                                                   | FSMC_D13, USART3_TX,<br>EVENTOUT                                                                                                                | -                       |

Table 8. STM32F20x pin and ball definitions (continued)

|        |           | Pi      | ns      |         |          |                                                      |                                          |               |      |                                   |                         |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|------------------------------------------|---------------|------|-----------------------------------|-------------------------|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type                                 | I/O structure | Note | Alternate functions               | Additional<br>functions |

| -      | -         | 98      | 142     | 170     | A3       | PE1                                                  | I/O FT - FSMC_NBL1, DCMI_D3,<br>EVENTOUT |               | -    |                                   |                         |

| -      | -         | -       | -       | -       | D5       | V <sub>SS</sub>                                      | V <sub>SS</sub> S                        |               | -    | -                                 |                         |

| 63     | D8        | I       | -       | -       | I        | V <sub>SS</sub>                                      | S                                        | -             | I    | -                                 | -                       |

| -      | -         | 99      | 143     | 171     | C6       | RFU                                                  | -                                        | -             | (7)  | -                                 | -                       |

| 64     | D9        | 100     | 144     | 172     | C5       | V <sub>DD</sub>                                      | S                                        | -             | -    | -                                 | -                       |

| -      | -         | -       | -       | 173     | D4       | Pl4                                                  | I/O                                      | FT            | -    | TIM8_BKIN, DCMI_D5,<br>EVENTOUT   | -                       |

| -      | -         | -       | I       | 174     | C4       | PI5                                                  | I/O                                      | FT            | I    | TIM8_CH1, DCMI_VSYNC,<br>EVENTOUT | -                       |

| -      | -         | -       | -       | 175     | C3       | Pl6                                                  | I/O FT - TIM8_CH2, DCMI_D6,<br>EVENTOUT  |               | -    |                                   |                         |

| -      | -         | -       | -       | 176     | C2       | PI7                                                  | I/O FT - TIM8_CH3, DCMI_D7,<br>EVENTOUT  |               | -    |                                   |                         |

| -      | C8        | -       | -       | -       | -        | IRROFF                                               | I/O                                      | -             | -    | -                                 | -                       |

Table 8. STM32F20x pin and ball definitions (continued)

1. Function availability depends on the chosen device.

PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited: the speed should not exceed 2 MHz with a maximum load of 30 pF and these I/Os must not be used as a current source (e.g. to drive an LED).

Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F20x and STM32F21x reference manual, available from the STMicroelectronics website: www.st.com.

4. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

5. If the device is delivered in an UFBGA176 package and if the REGOFF pin is set to V<sub>DD</sub> (Regulator OFF), then PA0 is used as an internal Reset (active low).

6. FSMC\_NL pin is also named FSMC\_NADV on memory devices.

7. RFU means "reserved for future use". This pin can be tied to  $V_{DD}$ ,  $V_{SS}$  or left unconnected.

#### Table 9. FSMC pin definition

| Pins  | FSMC |                |                             |   |         |  |  |  |  |

|-------|------|----------------|-----------------------------|---|---------|--|--|--|--|

| FIIIS | CF   | NOR/PSRAM/SRAM | DR/PSRAM/SRAM NOR/PSRAM Mux |   | LQFP100 |  |  |  |  |

| PE2   | -    | A23            | A23                         | - | Yes     |  |  |  |  |

| PE3   | -    | A19            | A19                         | - | Yes     |  |  |  |  |

| PE4   | -    | A20            | A20                         | - | Yes     |  |  |  |  |

|        |      | AF0               | AF1       | AF2      | AF3          | AF4            | AF5                  | AF6                  | AF7        | AF8                | AF9                       | AF10           | AF11                                 | AF12                 | AF13       |       |          |

|--------|------|-------------------|-----------|----------|--------------|----------------|----------------------|----------------------|------------|--------------------|---------------------------|----------------|--------------------------------------|----------------------|------------|-------|----------|

|        | Port | SYS               | TIM1/2    | TIM3/4/5 | TIM8/9/10/11 | I2C1/I2C2/I2C3 | SPI1/SPI2/I2S2       | SPI3/I2S3            | USART1/2/3 | UART4/5/<br>USART6 | CAN1/CAN2/<br>TIM12/13/14 | OTG_FS/ OTG_HS | ETH                                  | FSMC/SDIO/<br>OTG_HS | DCMI       | AF014 | AF15     |

|        | PB0  | -                 | TIM1_CH2N | TIM3_CH3 | TIM8_CH2N    | -              | -                    | -                    | -          | -                  | -                         | OTG_HS_ULPI_D1 | ETH_MII_RXD2                         | -                    | -          | -     | EVENTOUT |

|        | PB1  | -                 | TIM1_CH3N | TIM3_CH4 | TIM8_CH3N    | -              | -                    | -                    | -          | -                  | -                         | OTG_HS_ULPI_D2 | ETH_MII_RXD3                         | -                    | -          | -     | EVENTOUT |

|        | PB2  | -                 | -         | -        | -            | -              | -                    | -                    | -          | -                  | -                         | -              | -                                    | -                    | -          | -     | EVENTOUT |

|        | PB3  | JTDO/<br>TRACESWO | TIM2_CH2  | -        | -            | -              | SPI1_SCK             | SPI3_SCK<br>I2S3_SCK | -          | -                  | -                         | -              | -                                    | -                    | -          | -     | EVENTOUT |

|        | PB4  | JTRST             | -         | TIM3_CH1 | -            | -              | SPI1_MISO            | SPI3_MISO            | -          | -                  | -                         | -              | -                                    | -                    | -          | -     | EVENTOUT |

|        | PB5  | -                 | -         | TIM3_CH2 | -            | I2C1_SMBA      | SPI1_MOSI            | SPI3_MOSI<br>I2S3_SD | -          | -                  | CAN2_RX                   | OTG_HS_ULPI_D7 | ETH _PPS_OUT                         | -                    | DCMI_D10   | -     | EVENTOUT |

|        | PB6  | -                 | -         | TIM4_CH1 | -            | I2C1_SCL       | -                    | -                    | USART1_TX  | -                  | CAN2_TX                   | -              | -                                    | -                    | DCMI_D5    | -     | EVENTOUT |

|        | PB7  | -                 | -         | TIM4_CH2 | -            | I2C1_SDA       | -                    | -                    | USART1_RX  | -                  | -                         | -              | -                                    | FSMC_NL              | DCMI_VSYNC | -     | EVENTOUT |

| Port B | PB8  | -                 | -         | TIM4_CH3 | TIM10_CH1    | I2C1_SCL       | -                    | -                    | -          | -                  | CAN1_RX                   | -              | ETH _MII_TXD3                        | SDIO_D4              | DCMI_D6    | -     | EVENTOUT |

|        | PB9  | -                 | -         | TIM4_CH4 | TIM11_CH1    | I2C1_SDA       | SPI2_NSS<br>I2S2_WS  | -                    | -          | -                  | CAN1_TX                   | -              | -                                    | SDIO_D5              | DCMI_D7    | -     | EVENTOUT |

|        | PB10 | -                 | TIM2_CH3  | -        | -            | I2C2_SCL       | SPI2_SCK<br>I2S2_SCK | -                    | USART3_TX  | -                  | -                         | OTG_HS_ULPI_D3 | ETH_MII_RX_ER                        | -                    | -          | -     | EVENTOUT |

|        | PB11 | -                 | TIM2_CH4  | -        | -            | I2C2_SDA       | -                    | -                    | USART3_RX  | -                  | -                         | OTG_HS_ULPI_D4 | ETH _MII_TX_EN<br>ETH<br>_RMII_TX_EN | -                    | -          | -     | EVENTOUT |

|        | PB12 | -                 | TIM1_BKIN | ÷        | -            | I2C2_SMBA      | SPI2_NSS<br>I2S2_WS  | -                    | USART3_CK  | -                  | CAN2_RX                   | OTG_HS_ULPI_D5 | ETH_MII_TXD0<br>ETH_RMII_TXD0        | OTG_HS_ID            | -          | -     | EVENTOUT |

|        | PB13 | -                 | TIM1_CH1N | -        | -            | -              | SPI2_SCK<br>I2S2_SCK | -                    | USART3_CTS | -                  | CAN2_TX                   | OTG_HS_ULPI_D6 | ETH_MII_TXD1<br>ETH_RMII_TXD1        | -                    | -          | -     | EVENTOUT |

|        | PB14 | -                 | TIM1_CH2N | -        | TIM8_CH2N    | -              | SPI2_MISO            | -                    | USART3_RTS | -                  | TIM12_CH1                 | -              | -                                    | OTG_HS_DM            | -          | -     | EVENTOUT |

|        | PB15 | RTC_50Hz          | TIM1_CH3N | -        | TIM8_CH3N    | -              | SPI2_MOSI<br>I2S2_SD | -                    | -          | -                  | TIM12_CH2                 | -              | -                                    | OTG_HS_DP            | -          | -     | EVENTOUT |

### Table 10. Alternate function mapping (continued)

DocID15818 Rev 13

577

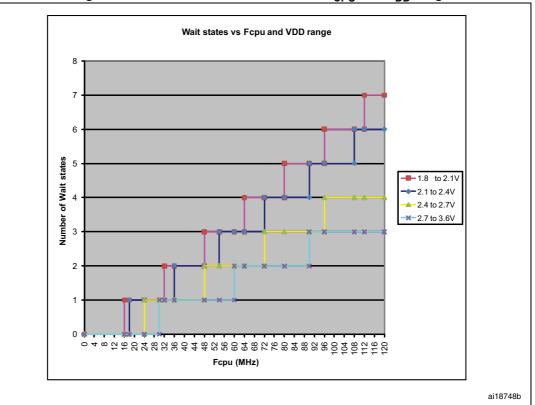

Figure 21. Number of wait states versus  $f_{\mbox{CPU}}$  and  $V_{\mbox{DD}}$  range

1. The supply voltage can drop to 1.7 V when the device operates in the 0 to 70  $^\circ\text{C}$  temperature range and IRROFF is set to V\_DD.

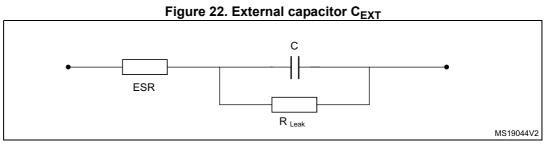

## 6.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 16*.

1. Legend: ESR is the equivalent series resistance.

#### Table 16. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

| Symbol | Parameter                         | Conditions |

|--------|-----------------------------------|------------|

| CEXT   | Capacitance of external capacitor | 2.2 µF     |

| ESR    | ESR of external capacitor         | < 2 Ω      |

1. When bypassing the voltage regulator, the two 2.2  $\mu F$  V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

#### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 26*. The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog inputs by firmware.

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with one peripheral clocked on (with only the clock applied)

- The code is running from Flash memory and the Flash memory access time is equal to 3 wait states at 120 MHz

- Prefetch and Cache ON

- When the peripherals are enabled, HCLK = 120MHz,  $f_{PCLK1}$  =  $f_{HCLK}/4,$  and  $f_{PCLK2}$  =  $f_{HCLK}/2$

- The typical values are obtained for V<sub>DD</sub> = 3.3 V and T<sub>A</sub>= 25 °C, unless otherwise specified.

|      | Peripheral <sup>(1)</sup>                            | Typical consumption at 25 °C | Unit |

|------|------------------------------------------------------|------------------------------|------|

|      | GPIO A                                               | 0.45                         |      |

|      | GPIO B                                               | 0.43                         |      |

|      | GPIO C                                               | 0.46                         |      |

|      | GPIO D                                               | 0.44                         |      |

|      | GPIO E                                               | 0.44                         |      |

|      | GPIO F                                               | 0.42                         |      |

|      | GPIO G                                               | 0.44                         |      |

|      | GPIO H                                               | 0.42                         |      |

| AHB1 | GPIO I                                               | 0.43                         |      |

|      | OTG_HS + ULPI                                        | 3.64                         |      |

|      | CRC                                                  | 1.17                         | mA   |

|      | BKPSRAM                                              | 0.21                         |      |

|      | DMA1                                                 | 2.76                         |      |

|      | DMA2                                                 | 2.85                         |      |

|      | ETH_MAC +<br>ETH_MAC_TX<br>ETH_MAC_RX<br>ETH_MAC_PTP | 2.99                         |      |

| AHB2 | OTG_FS                                               | 3.16                         |      |

|      | DCMI                                                 | 0.60                         |      |

| AHB3 | FSMC                                                 | 1.74                         |      |

Table 26. Peripheral current consumption

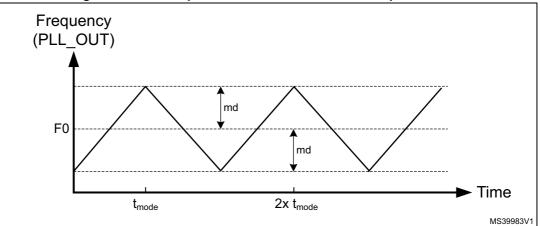

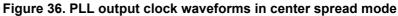

*Figure 36* and *Figure 37* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is f<sub>PLL\_OUT</sub> nominal.

T<sub>mode</sub> is the modulation period.

md is the modulation depth.

Figure 37. PLL output clock waveforms in down spread mode

## 6.3.12 Memory characteristics

### Flash memory

The characteristics are given at  $T_{\text{A}}$  = –40 to 105  $^{\circ}\text{C}$  unless otherwise specified.

## 6.3.18 TIM timer characteristics

The parameters given in *Table 50* and *Table 51* are guaranteed by design.

Refer to Section 6.3.16: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                       | Conditions                                                     | Min    | Мах                     | Unit                 |

|------------------------|---------------------------------|----------------------------------------------------------------|--------|-------------------------|----------------------|

|                        |                                 | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time           | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>60 MHz | 16.7   | -                       | ns                   |

|                        |                                 | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                 | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 30 MHz                | 33.3   | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock            |                                                                | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| 'EXT                   | frequency on CH1 to CH4         |                                                                | 0      | 30                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                |                                                                | -      | 16/32                   | bit                  |

|                        | 16-bit counter clock period     |                                                                | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t                      | when internal clock is selected | f <sub>TIMxCLK</sub> = 60 MHz<br>APB1= 30 MHz                  | 0.0167 | 1092                    | μs                   |

| <sup>t</sup> COUNTER   | 32-bit counter clock period     |                                                                | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        | when internal clock is selected |                                                                | 0.0167 | 71582788                | μs                   |

| tury count             | Maximum possible count          |                                                                | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| t <sub>MAX_COUNT</sub> |                                 |                                                                | -      | 71.6                    | s                    |

| Table 50. Characteristics of TIMx connected to the APE | 31 domain <sup>(1)</sup> |

|--------------------------------------------------------|--------------------------|

|--------------------------------------------------------|--------------------------|

1. TIMx is used as a general term to refer to the TIM2, TIM3, TIM4, TIM5, TIM6, TIM7, and TIM12 timers.

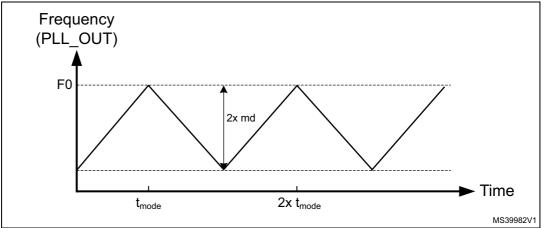

#### Figure 49. Ethernet SMI timing diagram

| Table 63. Dynamics characteristics | Ethernet MAC signals for SMI |

|------------------------------------|------------------------------|

|------------------------------------|------------------------------|

| Symbol                | Rating                     | Min | Тур | Мах | Unit |

|-----------------------|----------------------------|-----|-----|-----|------|

| t <sub>MDC</sub>      | MDC cycle time (2.38 MHz)  | 411 | 420 | 425 | ns   |

| t <sub>d(MDIO)</sub>  | MDIO write data valid time | 6   | 10  | 13  | ns   |

| t <sub>su(MDIO)</sub> | Read data setup time       | 12  | -   | -   | ns   |

| t <sub>h(MDIO)</sub>  | Read data hold time        | 0   | -   | -   | ns   |

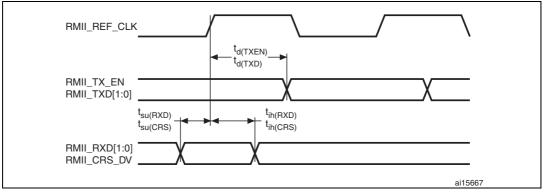

Table 64 gives the list of Ethernet MAC signals for the RMII and Figure 50 shows the corresponding timing diagram.

|                      | •                                |     | •    |     |      |

|----------------------|----------------------------------|-----|------|-----|------|

| Symbol               | Rating                           | Min | Тур  | Мах | Unit |

| t <sub>su(RXD)</sub> | Receive data setup time          | 1   | -    | -   |      |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 1.5 | -    | -   |      |

| t <sub>su(CRS)</sub> | Carrier sense set-up time        | 0   | -    | -   | 20   |

| t <sub>ih(CRS)</sub> | Carrier sense hold time          | 2   | -    | -   | ns   |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | 9   | 11   | 13  |      |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 9   | 11.5 | 14  |      |

DocID15818 Rev 13

|                           |                                                | ge  | (00110110 |      |

|---------------------------|------------------------------------------------|-----|-----------|------|

| Symbol                    | Parameter                                      | Min | Мах       | Unit |

| t <sub>su(ADV-CLKH)</sub> | FSMC_A/D[15:0] valid data before FSMC_CLK high | 5   | -         | ns   |

| t <sub>h(CLKH-ADV)</sub>  | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0   | -         | ns   |

## Table 76. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

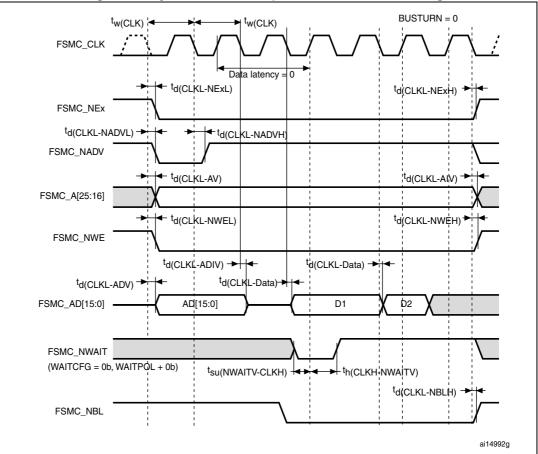

#### Figure 62. Synchronous multiplexed PSRAM write timings

Table 77. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                     | Parameter                                | Min                    | Max | Unit |

|----------------------------|------------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>        | FSMC_CLK period                          | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>  | FSMC_CLK low to FSMC_NEx low (x=02)      | -                      | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>  | FSMC_CLK low to FSMC_NEx high (x= 02)    | 2                      | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub> | FSMC_CLK low to FSMC_NADV low            | -                      | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high           | 3                      | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)   | -                      | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625) | 7                      | _   | ns   |

DocID15818 Rev 13

| Symbol                     | Parameter                                    | Min | Max | Unit |

|----------------------------|----------------------------------------------|-----|-----|------|

| t <sub>d(CLKL-NADVH)</sub> | FSMC_CLK low to FSMC_NADV high               | 4   | -   | ns   |

| t <sub>d(CLKL-AV)</sub>    | FSMC_CLK low to FSMC_Ax valid (x=1625)       | -   | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>   | FSMC_CLK low to FSMC_Ax invalid (x=1625)     | 3   | -   | ns   |

| t <sub>d(CLKH-NOEL)</sub>  | FSMC_CLK high to FSMC_NOE low                | -   | 1   | ns   |

| t <sub>d(CLKL-NOEH)</sub>  | FSMC_CLK low to FSMC_NOE high                | 1.5 | -   | ns   |

| t <sub>su(DV-CLKH)</sub>   | FSMC_D[15:0] valid data before FSMC_CLK high | 8   | -   | ns   |

| t <sub>h(CLKH-DV)</sub>    | FSMC_D[15:0] valid data after FSMC_CLK high  | 0   | -   | ns   |

## Table 78. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

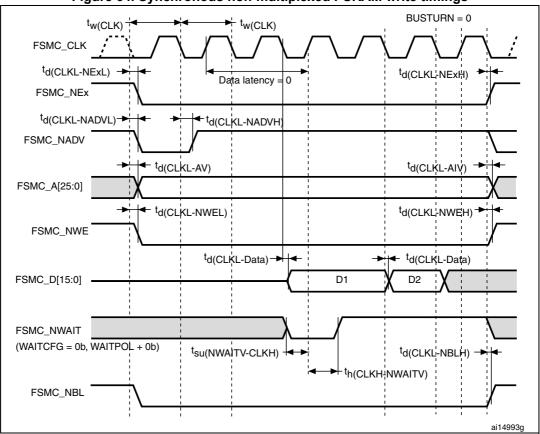

### Figure 64. Synchronous non-multiplexed PSRAM write timings

#### Table 79. Synchronous non-multiplexed PSRAM write timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                             | Min                    | Max | Unit |

|---------------------------|---------------------------------------|------------------------|-----|------|

| t <sub>w(CLK)</sub>       | FSMC_CLK period                       | 2T <sub>HCLK</sub> - 1 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub> | FSMC_CLK low to FSMC_NEx low (x=02)   | -                      | 1   | ns   |

| t <sub>d(CLKL-NExH)</sub> | FSMC_CLK low to FSMC_NEx high (x= 02) | 1                      | -   | ns   |

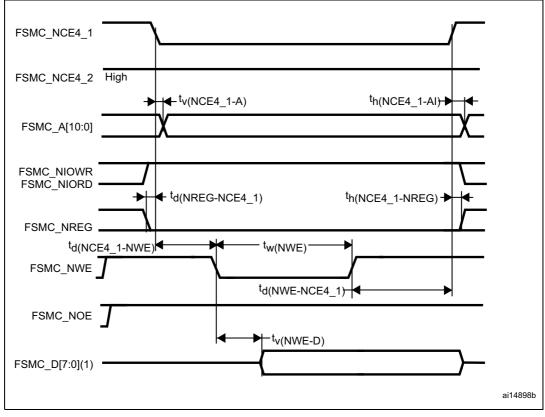

Figure 68. PC Card/CompactFlash controller waveforms for attribute memory write access

1. Only data bits 0...7 are driven (bits 8...15 remains Hi-Z).

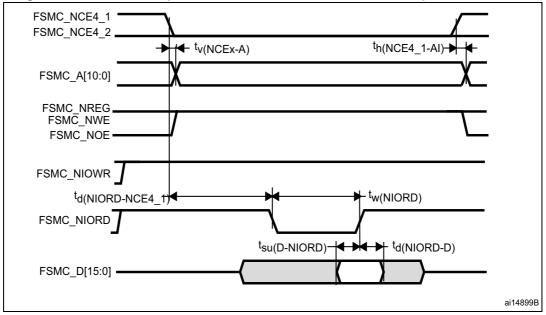

#### Figure 69. PC Card/CompactFlash controller waveforms for I/O space read access

| Symbol                  | Parameter                               | Min                    | Мах                    | Unit |

|-------------------------|-----------------------------------------|------------------------|------------------------|------|

| t <sub>w(NWE)</sub>     | FSMC_NWE low width                      | 4T <sub>HCLK</sub> - 1 | 4T <sub>HCLK</sub> + 3 | ns   |

| t <sub>v(NWE-D)</sub>   | FSMC_NWE low to FSMC_D[15-0] valid      | -                      | 0                      | ns   |

| t <sub>h(NWE-D)</sub>   | FSMC_NWE high to FSMC_D[15-0] invalid   | 3T <sub>HCLK</sub>     | -                      | ns   |

| t <sub>d(D-NWE)</sub>   | FSMC_D[15-0] valid before FSMC_NWE high | 5T <sub>HCLK</sub>     | -                      | ns   |

| t <sub>d(ALE-NWE)</sub> | FSMC_ALE valid before FSMC_NWE low      | -                      | 3T <sub>HCLK</sub> + 2 | ns   |

| t <sub>h(NWE-ALE)</sub> | FSMC_NWE high to FSMC_ALE invalid       | 3T <sub>HCLK</sub> - 2 | -                      | ns   |

Table 83. Switching characteristics for NAND Flash write cycles<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

## 6.3.26 Camera interface (DCMI) timing specifications

| Symbol | Parameter                                     | Conditions          | Min | Мах |

|--------|-----------------------------------------------|---------------------|-----|-----|

| -      | Frequency ratio DCMI_PIXCLK/f <sub>HCLK</sub> | DCMI_PIXCLK= 48 MHz | -   | 0.4 |

## 6.3.27 SD/SDIO MMC card host interface (SDIO) characteristics

Unless otherwise specified, the parameters given in *Table 85* are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

Refer to Section 6.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (D[7:0], CMD, CK).

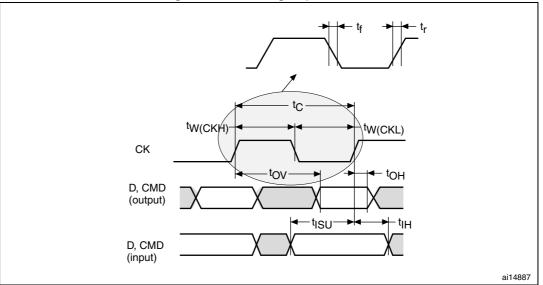

Figure 75. SDIO high-speed mode

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах   | Min                   | Тур    | Мах    |

| С      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| Е      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| E3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| е      | -           | 0.500  | -     | -                     | 0.0197 | -      |

| К      | 0°          | 3.5°   | 7°    | 0°                    | 3.5°   | 7°     |

| L      | 0.450       | 0.600  | 0.750 | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -     | -                     | 0.0394 | -      |

| CCC    | -           | -      | 0.080 | -                     | -      | 0.0031 |

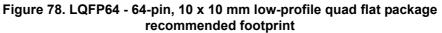

# Table 87. LQFP64 - 64-pin, 10 x 10 mm low-profile quad flatpackage mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

# Table 88. WLCSP64+2 - 66-ball, 4.539 x 4.911 mm, 0.4 mm pitch wafer level chip scale package mechanical data (continued)

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| F      | -           | 0.220 | -     | -                     | 0.0087 | -      |

| G      | -           | 0.386 | -     | -                     | 0.0152 | -      |

| ааа    | -           | -     | 0.100 | -                     | -      | 0.0039 |

| bbb    | -           | -     | 0.100 | -                     | -      | 0.0039 |

| CCC    | -           | -     | 0.100 | -                     | -      | 0.0039 |

| ddd    | -           | -     | 0.050 | -                     | -      | 0.0020 |

| eee    | -           | -     | 0.050 | -                     | -      | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

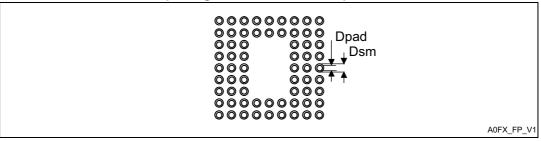

# Figure 80. WLCSP64+2 - 66-ball, 4.539 x 4.911 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

#### Table 89. WLCSP64 recommended PCB design rules (0.4 mm pitch)

| Dimension         | Recommended values                                               |  |  |

|-------------------|------------------------------------------------------------------|--|--|

| Pitch             | 0.4                                                              |  |  |

| Dpad              | 0.225 mm                                                         |  |  |

| Dsm               | 0.290 mm typ. (depends on the soldermask registration tolerance) |  |  |

| Stencil opening   | 0.250 mm                                                         |  |  |

| Stencil thickness | 0.100 mm                                                         |  |  |