#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                  |

|----------------------------|-----------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 120MHz                                                                                  |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, Memory Card, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                       |

| Number of I/O              | 114                                                                                     |

| Program Memory Size        | 1MB (1M × 8)                                                                            |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 132K x 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                             |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                   |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 144-LQFP                                                                                |

| Supplier Device Package    | 144-LQFP (20x20)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f207zgt6tr                 |

|                            |                                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2. STM32F205xx features and peripheral counts (continued)

| Peripherals            | ST                                                  | M32F205Rx               |  |                    | STM32F205Vx | STM32F205Zx |  |

|------------------------|-----------------------------------------------------|-------------------------|--|--------------------|-------------|-------------|--|

| Operating temperatures | Ambient temperatures: -40 to +85 °C /-40 to +105 °C |                         |  |                    |             |             |  |

|                        | Junction temperature: -40 to + 125 °C               |                         |  |                    |             |             |  |

| Package                | LQFP64                                              | LQFP64<br>WLCSP64<br>+2 |  | FP64<br>CSP6<br>+2 | LQFP100     | LQFP144     |  |

For the LQFP100 package, only FSMC Bank1 or Bank2 are available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package.

2. The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio mode.

On devices in WLCSP64+2 package, if IRROFF is set to V<sub>DD</sub>, the supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

|                   | Peripherals             |     | STM32F207Vx     |      |     | STM32F207Zx |     |      |                  | STM32F207lx |     |      |  |

|-------------------|-------------------------|-----|-----------------|------|-----|-------------|-----|------|------------------|-------------|-----|------|--|

| Flash memory in I | 256                     | 512 | 768             | 1024 | 256 | 512         | 768 | 1024 | 256              | 512         | 768 | 1024 |  |

| SRAM in Kbytes    | System<br>(SRAM1+SRAM2) |     | 128<br>(112+16) |      |     |             |     |      |                  |             |     |      |  |

|                   | Backup                  |     | 4               |      |     |             |     |      |                  |             |     |      |  |

| FSMC memory co    | ontroller               |     |                 |      |     |             |     | Yes  | s <sup>(1)</sup> |             |     |      |  |

| Ethernet          |                         |     | Yes             |      |     |             |     |      |                  |             |     |      |  |

|                   | General-purpose         | 10  |                 |      |     |             |     |      |                  |             |     |      |  |

|                   | Advanced-control        | 2 2 |                 |      |     |             |     |      |                  |             |     |      |  |

| Timers            | Basic                   |     |                 |      |     |             |     |      |                  |             |     |      |  |

|                   | IWDG                    |     |                 |      |     |             |     | Ye   | es               |             |     |      |  |

|                   | WWDG                    |     |                 |      |     |             |     | Ye   | es               |             |     |      |  |

| RTC               | Yes                     |     |                 |      |     |             |     |      |                  |             |     |      |  |

| Random number     | generator               |     | Yes             |      |     |             |     |      |                  |             |     |      |  |

#### Table 3. STM32F207xx features and peripheral counts

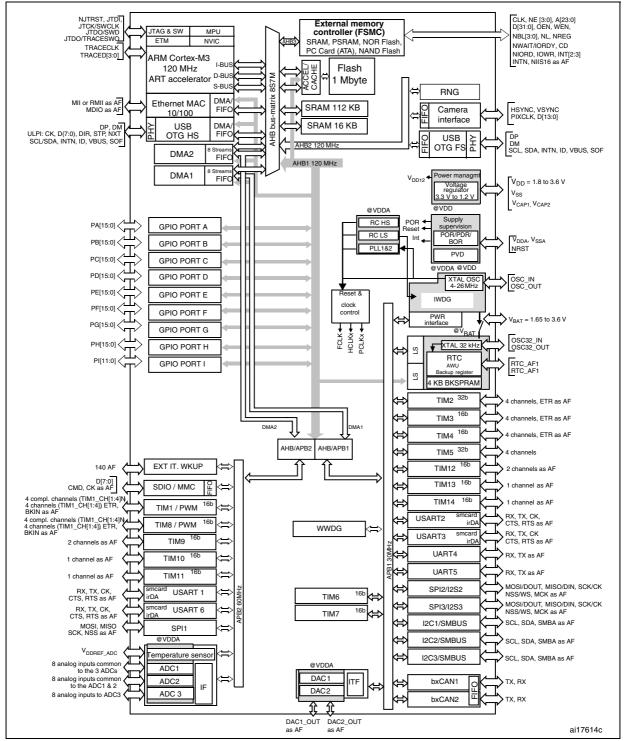

Figure 4. STM32F20x block diagram

1. The timers connected to APB2 are clocked from TIMxCLK up to 120 MHz, while the timers connected to APB1 are clocked from TIMxCLK up to 60 MHz.

2. The camera interface and Ethernet are available only in STM32F207xx devices.

in the 0 to 70 °C temperature range using an external power supply supervisor (see *Section 3.16*).

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.8 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock, 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Refer to Figure 19: Power supply scheme for more details.

# 3.15 Power supply supervisor

The devices have an integrated power-on reset (POR) / power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry.

At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default BOR threshold levels, or to disable BOR permanently. Three BOR thresholds are available through option bytes.

The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for an external reset circuit. On devices in WLCSP64+2 package, the BOR, POR and PDR features can be disabled by setting IRROFF pin to  $V_{DD}$ . In this mode an external power supply supervisor is required (see Section 3.16).

The devices also feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

# 3.16 Voltage regulator

The regulator has five operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low-power regulator (LPR)

- Power-down

- Regulator OFF

- Regulator OFF/internal reset ON

- Regulator OFF/internal reset OFF

## 3.16.1 Regulator ON

The regulator ON modes are activated by default on LQFP packages. On WLCSP64+2 package, they are activated by connecting both REGOFF and IRROFF pins to V<sub>SS</sub>, while only REGOFF must be connected to V<sub>SS</sub> on UFBGA176 package (IRROFF is not available).

$V_{DD}$  minimum value is 1.8 V.

# 3.16.3 Regulator ON/OFF and internal reset ON/OFF availability

| Table 4. Regulator ON/OFF and Internal reset ON/OFF availability |                                                    |                                                       |                                                                           |  |  |  |  |  |  |

|------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|--|--|--|

| Package                                                          | Regulator ON/internal reset ON                     | Regulator<br>OFF/internal reset ON                    | Regulator OFF/internal<br>reset OFF                                       |  |  |  |  |  |  |

| LQFP64<br>LQFP100<br>LQFP144<br>LQFP176                          | Yes                                                | No                                                    | No                                                                        |  |  |  |  |  |  |

| WLCSP 64+2                                                       | Yes<br>REGOFF and IRROFF<br>set to V <sub>SS</sub> | Yes REGOFF set to $V_{DD}$ and IRROFF set to $V_{SS}$ | Yes<br>REGOFF set to V <sub>SS</sub> and<br>IRROFF set to V <sub>DD</sub> |  |  |  |  |  |  |

| UFBGA176                                                         | Yes<br>REGOFF set to V <sub>SS</sub>               | Yes<br>REGOFF set to V <sub>DD</sub>                  | No                                                                        |  |  |  |  |  |  |

Table 4. Regulator ON/OFF and internal reset ON/OFF availability

# 3.17 Real-time clock (RTC), backup SRAM and backup registers

The backup domain of the STM32F20x devices includes:

- The real-time clock (RTC)

- 4 Kbytes of backup SRAM

- 20 backup registers

The real-time clock (RTC) is an independent BCD timer/counter. Its main features are the following:

- Dedicated registers contain the second, minute, hour (in 12/24 hour), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28, 29 (leap year), 30, and 31 day of the month.

- Programmable alarm and programmable periodic interrupts with wakeup from Stop and Standby modes.

- It is clocked by a 32.768 kHz external crystal, resonator or oscillator, the internal lowpower RC oscillator or the high-speed external clock divided by 128. The internal lowspeed RC has a typical frequency of 32 kHz. The RTC can be calibrated using an external 512 Hz output to compensate for any natural quartz deviation.

- Two alarm registers are used to generate an alarm at a specific time and calendar fields can be independently masked for alarm comparison. To generate a periodic interrupt, a 16-bit programmable binary auto-reload downcounter with programmable resolution is available and allows automatic wakeup and periodic alarms from every 120 µs to every 36 hours.

- A 20-bit prescaler is used for the time base clock. It is by default configured to generate a time base of 1 second from a clock at 32.768 kHz.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

The 4-Kbyte backup SRAM is an EEPROM-like area. It can be used to store data which need to be retained in VBAT and standby mode. This memory area is disabled to minimize power consumption (see *Section 3.18: Low-power modes*). It can be enabled by software.

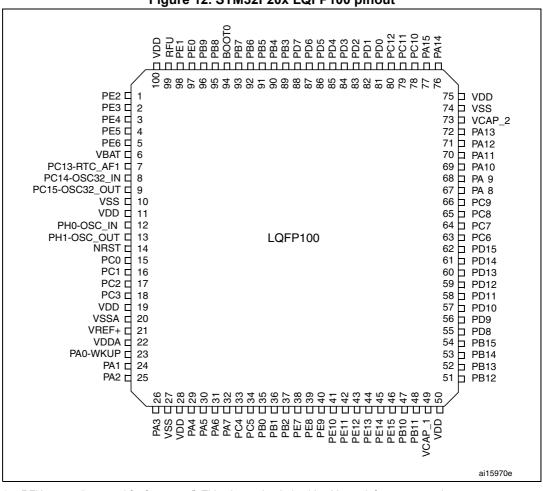

1. RFU means "reserved for future use". This pin can be tied to  $V_{\text{DD}}, V_{\text{SS}}$  or left unconnected.

2. The above figure shows the package top view.

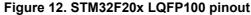

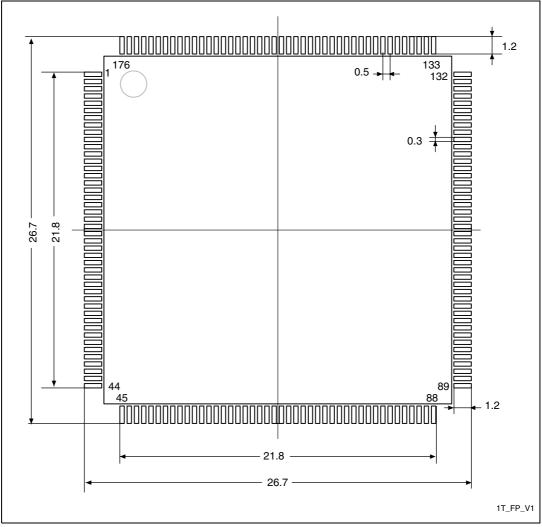

Figure 13. STM32F20x LQFP144 pinout

1. RFU means "reserved for future use". This pin can be tied to  $V_{DD}$ ,  $V_{SS}$  or left unconnected.

2. The above figure shows the package top view.

|        |           | Pi      | ns      |         |          |                                                      |          |               |      |                                                                                                               |                         |  |  |

|--------|-----------|---------|---------|---------|----------|------------------------------------------------------|----------|---------------|------|---------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| LQFP64 | WLCSP64+2 | LQFP100 | LQFP144 | LQFP176 | UFBGA176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Note | Alternate functions                                                                                           | Additional<br>functions |  |  |

| 22     | H5        | 31      | 42      | 52      | P3       | PA6                                                  | I/O      | FT            | (4)  | SPI1_MISO, TIM8_BKIN,<br>TIM13_CH1, DCMI_PIXCLK,<br>TIM3_CH1, TIM1_BKIN,<br>EVENTOUT                          | ADC12_IN6               |  |  |

| 23     | J7        | 32      | 43      | 53      | R3       | PA7                                                  | I/O      | FT            | (4)  | SPI1_MOSI, TIM8_CH1N,<br>TIM14_CH1, TIM3_CH2,<br>ETH_MII_RX_DV,<br>TIM1_CH1N,<br>ETH_RMII_CRS_DV,<br>EVENTOUT | ADC12_IN7               |  |  |

| 24     | H4        | 33      | 44      | 54      | N5       | PC4                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD0,<br>ETH_MII_RXD0,<br>EVENTOUT                                                                   | ADC12_IN14              |  |  |

| 25     | G3        | 34      | 45      | 55      | P5       | PC5                                                  | I/O      | FT            | (4)  | ETH_RMII_RXD1,<br>ETH_MII_RXD1,<br>EVENTOUT                                                                   | ADC12_IN15              |  |  |

| 26     | J6        | 35      | 46      | 56      | R5       | PB0                                                  | I/O      | FT            | (4)  | TIM3_CH3, TIM8_CH2N,<br>OTG_HS_ULPI_D1,<br>ETH_MII_RXD2,<br>TIM1_CH2N, EVENTOUT                               | ADC12_IN8               |  |  |

| 27     | J5        | 36      | 47      | 57      | R4       | PB1                                                  | I/O      | FT            | (4)  | TIM3_CH4, TIM8_CH3N,<br>OTG_HS_ULPI_D2,<br>ETH_MII_RXD3,<br>TIM1_CH3N, EVENTOUT                               | ADC12_IN9               |  |  |

| 28     | J4        | 37      | 48      | 58      | M6       | PB2/BOOT1 (PB2)                                      | I/O      | FT            | -    | EVENTOUT                                                                                                      | -                       |  |  |

| -      | -         | -       | 49      | 59      | R6       | PF11                                                 | I/O      | FT            | -    | DCMI_D12, EVENTOUT                                                                                            |                         |  |  |

| -      | -         | -       | 50      | 60      | P6       | PF12                                                 | I/O      | FT            | -    | FSMC_A6, EVENTOUT                                                                                             | -                       |  |  |

| -      | -         | -       | 51      | 61      | M8       | V <sub>SS</sub>                                      | S        |               | -    | -                                                                                                             | -                       |  |  |

| -      | -         | -       | 52      | 62      | N8       | V <sub>DD</sub>                                      | S        |               | -    | -                                                                                                             | -                       |  |  |

| -      | -         | -       | 53      | 63      | N6       | PF13                                                 | I/O      | FT            | -    | FSMC_A7, EVENTOUT                                                                                             | -                       |  |  |

| -      | -         | -       | 54      | 64      | R7       | PF14                                                 | I/O      | FT            | -    | FSMC_A8, EVENTOUT                                                                                             | -                       |  |  |

| -      | -         | -       | 55      | 65      | P7       | PF15                                                 | I/O      | FT            | -    | FSMC_A9, EVENTOUT                                                                                             | -                       |  |  |

| -      | -         | -       | 56      | 66      | N7       | PG0                                                  | I/O      | FT            | -    | FSMC_A10, EVENTOUT                                                                                            | -                       |  |  |

| -      | -         | -       | 57      | 67      | M7       | PG1                                                  | I/O      | FT            | -    | FSMC_A11, EVENTOUT                                                                                            | -                       |  |  |

| Symbol                                 | Parameter                                                      | Conditions                                               | Min                                                    | Max                                                                                                                         | Unit |

|----------------------------------------|----------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|

| V <sub>DD</sub>                        | Standard operating voltage                                     | -                                                        | 1.8 <sup>(1)</sup>                                     | 3.6                                                                                                                         |      |

| V <sub>DDA</sub> <sup>(2)</sup>        | Analog operating voltage<br>(ADC limited to 1 M samples)       | Must be the same potential as $V_{DD}^{(3)}$             | 1.8 <sup>(1)</sup>                                     | 3.6                                                                                                                         |      |

| V <sub>DDA</sub> (-/                   | Analog operating voltage<br>(ADC limited to 2 M samples)       |                                                          | 2.4                                                    | 3.6                                                                                                                         |      |

| V <sub>BAT</sub>                       | Backup operating voltage                                       | -                                                        | 1.65                                                   | 3.6                                                                                                                         |      |

|                                        | Input voltage on RST and FT pins                               | $2 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | -0.3                                                   | 5.5                                                                                                                         | V    |

| V                                      | input voltage on KST and FT pins                               | $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2 \text{ V}$ | -0.3                                                   | 5.2                                                                                                                         |      |

| V <sub>IN</sub>                        | Input voltage on TTa pins                                      | -                                                        | -0.3                                                   | V <sub>DD</sub> +0.3                                                                                                        |      |

|                                        | Input voltage on BOOT0 pin                                     | -                                                        | 0                                                      | 9                                                                                                                           |      |

| V <sub>CAP1</sub><br>V <sub>CAP2</sub> | Internal core voltage to be supplied externally in REGOFF mode | -                                                        | 1.1                                                    | 1.3                                                                                                                         |      |

|                                        |                                                                | LQFP64                                                   |                                                        | 444                                                                                                                         |      |

|                                        |                                                                | WLCSP64+2                                                | -                                                      | 392                                                                                                                         |      |

| Р                                      | Power dissipation at T <sub>A</sub> = 85 °C for                | LQFP100                                                  | -                                                      | 2.43.61.653.6 $-0.3$ 5.5 $-0.3$ 5.2 $-0.3$ $5.2$ $-0.3$ $\nabla_{DD}$ +0.3091.11.3-444-392-434-500-526-513-4085-40105-40125 | mW   |

| PD                                     | suffix 6 or $T_A = 105 \degree C$ for suffix 7 <sup>(4)</sup>  | LQFP144                                                  | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | mvv                                                                                                                         |      |

|                                        |                                                                | LQFP176                                                  | -                                                      | 526                                                                                                                         |      |

|                                        |                                                                | UFBGA176                                                 | -                                                      | 513                                                                                                                         |      |

|                                        | Ambient temperature for 6 suffix                               | Maximum power dissipation                                | -40                                                    | 85                                                                                                                          | °C   |

| Та                                     | version                                                        | Low-power dissipation <sup>(5)</sup>                     | -40                                                    | 105                                                                                                                         |      |

| IA                                     | Ambient temperature for 7 suffix                               | Maximum power dissipation                                | -40                                                    | 105                                                                                                                         | °C   |

|                                        | version                                                        | Low-power dissipation <sup>(5)</sup>                     | -40                                                    | 125                                                                                                                         | C    |

| TJ                                     | Junction temperature range                                     | 6 suffix version                                         | -40                                                    | 105                                                                                                                         | °C   |

| IJ                                     | Sunction temperature range                                     | 7 suffix version                                         | -40                                                    | 125                                                                                                                         |      |

Table 14. General operating conditions (continued)

On devices in WLCSP64+2 package, if IRROFF is set to V<sub>DD</sub>, the supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor (see Section 3.16).

2. When the ADC is used, refer to *Table 66: ADC characteristics*.

3. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and power-down operation.

4. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

5. In low-power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$ .

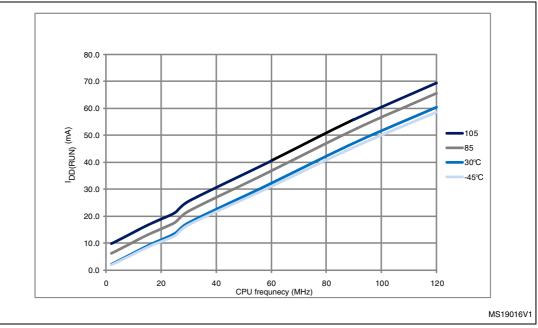

Figure 25. Typical current consumption vs. temperature, Run mode, code with data processing running from Flash, ART accelerator OFF, peripherals ON

|                      |                                                |                                                                                                                                                  | Тур                       |                           | Max                       |                            |      |

|----------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol               | Parameter                                      | Conditions                                                                                                                                       | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

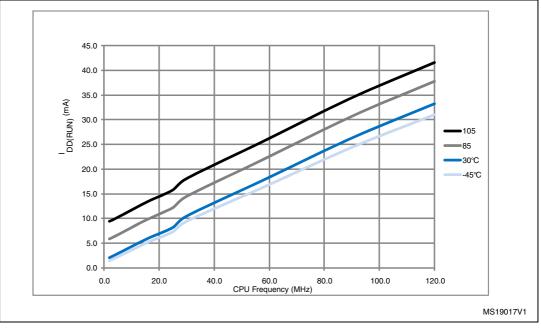

|                      | Supply current<br>in Stop mode                 | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.55                      | 1.2                       | 11.00                     | 20.00                      |      |

| I <sub>DD_STOP</sub> | with main<br>regulator in<br>Run mode          | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.50                      | 1.2                       | 11.00                     | 20.00                      | mA   |

|                      | Supply current<br>in Stop mode                 | Flash in Stop mode, low-speed and high-speed<br>internal RC oscillators and high-speed oscillator<br>OFF (no independent watchdog)               | 0.35                      | 1.1                       | 8.00                      | 15.00                      | IIIA |

|                      | with main<br>regulator in<br>Low-power<br>mode | Flash in Deep power down mode, low-speed<br>and high-speed internal RC oscillators and<br>high-speed oscillator OFF (no independent<br>watchdog) | 0.30                      | 1.1                       | 8.00                      | 15.00                      |      |

Table 23. Typical and maximum current consumptions in Stop mode

Figure 29. Typical current consumption vs. temperature in Stop mode

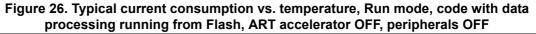

All typical and maximum values from table 18 and figure 26 will be reduced over time by up to 50% as part

of ST continuous improvement of test procedures. New versions of the datasheet will be released to reflect

these changes

| Per  | ripheral <sup>(1)</sup> | Typical consumption at 25 °C | Unit |

|------|-------------------------|------------------------------|------|

|      | SDIO                    | 0.69                         |      |

|      | TIM1                    | 1.06                         |      |

|      | TIM8                    | 1.03                         |      |

|      | TIM9                    | 0.58                         |      |

|      | TIM10                   | 0.37                         |      |

| APB2 | TIM11                   | 0.39                         | mA   |

| AFBZ | ADC1 <sup>(4)</sup>     | 2.13                         | ША   |

|      | ADC2 <sup>(4)</sup>     | 2.04                         |      |

|      | ADC3 <sup>(4)</sup>     | 2.12                         |      |

|      | SPI1                    | 1.20                         |      |

|      | USART1                  | 0.38                         |      |

|      | USART6                  | 0.37                         |      |

|  | Table 26. Peri | pheral current | consumption | (continued) |

|--|----------------|----------------|-------------|-------------|

|--|----------------|----------------|-------------|-------------|

1. External clock is 25 MHz (HSE oscillator with 25 MHz crystal) and PLL is on.

2. EN1 bit is set in DAC\_CR register.

3. EN2 bit is set in DAC\_CR register.

4.  $f_{ADC} = f_{PCLK2}/2$ , ADON bit set in ADC\_CR2 register.

## 6.3.7 Wakeup time from low-power mode

The wakeup times given in *Table 27* is measured on a wakeup phase with a 16 MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                                 | Parameter                                                                                    | Min <sup>(1)</sup> | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit |

|----------------------------------------|----------------------------------------------------------------------------------------------|--------------------|--------------------|--------------------|------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>    | Wakeup from Sleep mode                                                                       | -                  | 1                  | -                  | μs   |

|                                        | Wakeup from Stop mode (regulator in Run mode)                                                | -                  | 13                 | -                  |      |

| t <sub>WUSTOP</sub> <sup>(2)</sup>     | Wakeup from Stop mode (regulator in low-power mode)                                          | -                  | 17                 | 40                 | us   |

| WUSTOP                                 | Wakeup from Stop mode (regulator in low-power mode and Flash memory in Deep power down mode) | -                  | 110                | -                  | F -  |

| t <sub>WUSTDBY</sub> <sup>(2)(3)</sup> | Wakeup from Standby mode                                                                     | 260                | 375                | 480                | μs   |

1. Guaranteed by characterization results, not tested in production.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first instruction.

3.  $t_{WUSTDBY}$  minimum and maximum values are given at 105 °C and -45 °C, respectively.

| Symbol                               | Parameter                                    | Conditions                               | Conditions         |              | Тур         | Max          | Unit |

|--------------------------------------|----------------------------------------------|------------------------------------------|--------------------|--------------|-------------|--------------|------|

|                                      |                                              |                                          | RMS                | -            | 25          | -            |      |

|                                      | Cycle-to-cycle jitter                        | System clock                             | peak<br>to<br>peak | -            | ±150        | -            |      |

|                                      |                                              | 120 MHz                                  | RMS                | -            | 15          | -            |      |

| Jitter <sup>(3)</sup>                | Period Jitter<br>ter <sup>(3)</sup>          | itter                                    | peak<br>to<br>peak | -            | <u>+200</u> | -            | ps   |

|                                      | Main clock output (MCO) for<br>RMII Ethernet | Cycle to cycle at 50 MHz on 1000 samples |                    | -            | 32          | -            |      |

|                                      | Main clock output (MCO) for MII<br>Ethernet  | Cycle to cycle at 25 MHz on 1000 samples |                    | -            | 40          | -            |      |

|                                      | Bit Time CAN jitter                          | Cycle to cycle at 1 MHz on 1000 samples  |                    | -            | 330         | -            |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on VDD                 | VCO freq = 192 MHz<br>VCO freq = 432 MHz |                    | 0.15<br>0.45 | -           | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on VDDA                | VCO freq = 192 MHz<br>VCO freq = 432 MHz |                    | 0.30<br>0.55 | -           | 0.40<br>0.85 | mA   |

| Table 34. | Main PLL | characteristics | (continued) |

|-----------|----------|-----------------|-------------|

|-----------|----------|-----------------|-------------|

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design, not tested in production.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization results, not tested in production.

### Table 35. PLLI2S (audio PLL) characteristics

| Symbol                  | Parameter                         | Conditions         | Min                 | Тур | Мах                 | Unit |

|-------------------------|-----------------------------------|--------------------|---------------------|-----|---------------------|------|

| f <sub>PLLI2S_IN</sub>  | PLLI2S input clock <sup>(1)</sup> | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 <sup>(2)</sup> | MHz  |

| f <sub>PLLI2S_OUT</sub> | PLLI2S multiplier output clock    | -                  | -                   | -   | 216                 | MHz  |

| f <sub>VCO_OUT</sub>    | PLLI2S VCO output                 | -                  | 192                 | -   | 432                 | MHz  |

| +                       | PLLI2S lock time                  | VCO freq = 192 MHz | 75                  | -   | 200                 |      |

| <sup>t</sup> LOCK       |                                   | VCO freq = 432 MHz | 100                 | -   | 300                 | μs   |

| Symbol                         | Parameter | Conditions                                           | Min | Тур | Max | Unit |

|--------------------------------|-----------|------------------------------------------------------|-----|-----|-----|------|

|                                |           | Write / Erase 8-bit mode<br>V <sub>DD</sub> = 1.8 V  | -   | 5   | -   |      |

| I <sub>DD</sub> Supply current |           | Write / Erase 16-bit mode<br>V <sub>DD</sub> = 2.1 V | -   | 8   | -   | mA   |

|                                |           | Write / Erase 32-bit mode<br>V <sub>DD</sub> = 3.3 V | -   | 12  | -   |      |

Table 37. Flash memory characteristics

### Table 38. Flash memory programming

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |  |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|--|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |  |

| t <sub>ERASE16KB</sub>  | Sector (16 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |  |

| t <sub>ERASE64KB</sub>  | Sector (64 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |  |

|                         | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 2    | 4                  |      |  |

| t <sub>ERASE128KB</sub> |                            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 1.3  | 2.6                | s    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 1    | 2                  |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 16   | 32                 |      |  |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 11   | 22                 | s    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      |                    | 8    | 16                 |      |  |

|                         |                            | 32-bit program operation                         | 2.7                | -    | 3.6                | V    |  |

| V <sub>prog</sub>       | Programming voltage        | 16-bit program operation                         | 2.1                | -    | 3.6                | V    |  |

|                         |                            | 8-bit program operation                          | 1.8                | -    | 3.6                | V    |  |

1. Guaranteed by characterization results, not tested in production.

2. The maximum programming time is measured after 100K erase operations.

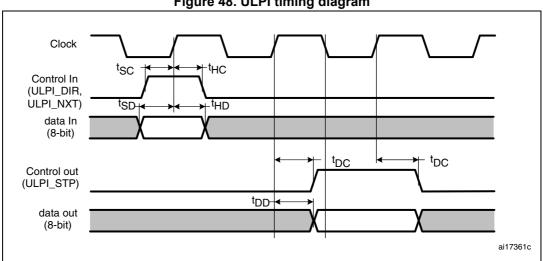

Figure 48. ULPI timing diagram

#### Table 61. ULPI timing

| Symbol          | Parameter                                       | Valu | Unit |      |

|-----------------|-------------------------------------------------|------|------|------|

| Symbol          | Farameter                                       | Min. | Max. | Unit |

| +               | Control in (ULPI_DIR) setup time                | -    | 2.0  |      |

| t <sub>SC</sub> | Control in (ULPI_NXT) setup time                | -    | 1.5  |      |

| t <sub>HC</sub> | Control in (ULPI_DIR, ULPI_NXT) hold time       | 0    | -    |      |

| t <sub>SD</sub> | Data in setup time                              | -    | 2.0  | ns   |

| t <sub>HD</sub> | Data in hold time                               | 0    | -    |      |

| t <sub>DC</sub> | Control out (ULPI_STP) setup time and hold time | -    | 9.2  |      |

| t <sub>DD</sub> | Data out available from clock rising edge       | -    | 10.7 |      |

1.  $V_{DD}$  = 2.7 V to 3.6 V and  $T_A$  = -40 to 85 °C.

### **Ethernet characteristics**

Table 62 shows the Ethernet operating voltage.

#### Table 62. Ethernet DC electrical characteristics

| Symbol Parameter |          | Min. <sup>(1)</sup>        | Max. <sup>(1)</sup> | Unit |   |

|------------------|----------|----------------------------|---------------------|------|---|

| Input level      | $V_{DD}$ | Ethernet operating voltage | 2.7                 | 3.6  | V |

1. All the voltages are measured from the local ground potential.

Table 63 gives the list of Ethernet MAC signals for the SMI (station management interface) and Figure 49 shows the corresponding timing diagram.

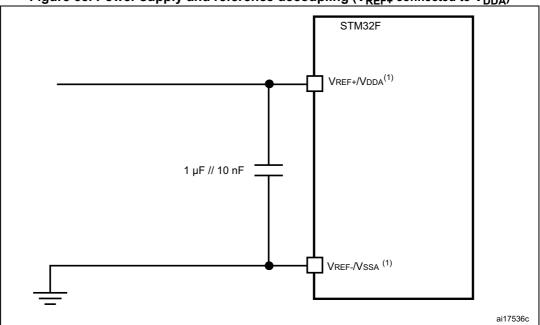

Figure 55. Power supply and reference decoupling ( $V_{REF+}$  connected to  $V_{DDA}$ )

| Table 66. DAC Characteristics    |                                       |                    |     |                        |      |                                                                                                                                                |

|----------------------------------|---------------------------------------|--------------------|-----|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                           | Parameter                             | Min                | Тур | Мах                    | Unit | Comments                                                                                                                                       |

| V <sub>DDA</sub>                 | Analog supply voltage                 | 1.8 <sup>(1)</sup> | -   | 3.6                    | V    | -                                                                                                                                              |

| V <sub>REF+</sub>                | Reference supply voltage              | 1.8 <sup>(1)</sup> | -   | 3.6                    | V    | V <sub>REF+</sub> ≤V <sub>DDA</sub>                                                                                                            |

| V <sub>SSA</sub>                 | Ground                                | 0                  | -   | 0                      | V    | -                                                                                                                                              |

| R <sub>LOAD</sub> <sup>(2)</sup> | Resistive load with buffer<br>ON      | 5                  | -   | -                      | kΩ   | -                                                                                                                                              |

| R <sub>0</sub> <sup>(2)</sup>    | Impedance output with<br>buffer OFF   | -                  | -   | 15                     | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$                        |

| C <sub>LOAD</sub> <sup>(2)</sup> | Capacitive load                       | -                  | -   | 50                     | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                                |

| DAC_OUT<br>min <sup>(2)</sup>    | Lower DAC_OUT voltage with buffer ON  | 0.2                | -   | -                      | v    | It gives the maximum output excursion<br>of the DAC.<br>It corresponds to 12-bit input code<br>(0x0E0) to (0xF1C) at V <sub>REF+</sub> = 3.6 V |

| DAC_OUT<br>max <sup>(2)</sup>    | Higher DAC_OUT voltage with buffer ON | -                  | -   | V <sub>DDA</sub> – 0.2 | V    | and (0x1C7) to (0xE38) at $V_{REF+} = 3.0 \text{ V}$<br>1.8 V                                                                                  |

## 6.3.21 DAC electrical characteristics

Table 68. DAC characteristics

V<sub>REF+</sub> and V<sub>REF-</sub> inputs are both available on UFBGA176 package. V<sub>REF+</sub> is also available on all packages except for LQFP64. When V<sub>REF+</sub> and V<sub>REF-</sub> are not available, they are internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

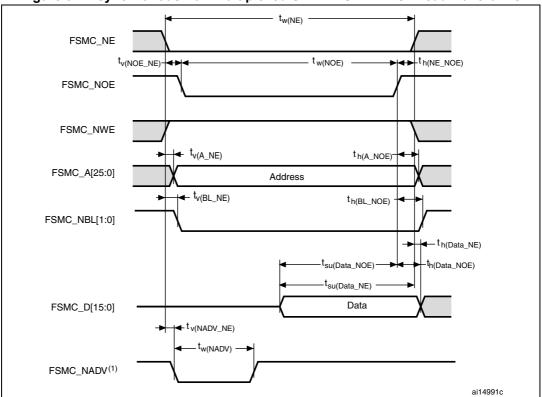

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

| Table 72. Asynchronous non-multi | plexed SRAM/PSRAM/NOR read timings <sup>(1)(2)</sup> |

|----------------------------------|------------------------------------------------------|

| Symbol                    | Parameter                               | Min                      | Мах                      | Unit |

|---------------------------|-----------------------------------------|--------------------------|--------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                        | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> +0.5  | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low            | 0.5                      | 2.5                      | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                       | 2T <sub>HCLK</sub> - 1   | 2T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time | 0                        | -                        | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid            | -                        | 4                        | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high   | 0                        | -                        | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid           | -                        | 0.5                      | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high   | 0                        | -                        | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time        | T <sub>HCLK</sub> + 0.5  | -                        | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOEx high setup time       | T <sub>HCLK</sub> + 2.5  | -                        | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high      | 0                        | -                        | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high      | 0                        | -                        | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low           | -                        | 2.5                      | ns   |

| t <sub>w(NADV</sub> )     | FSMC_NADV low time                      | -                        | T <sub>HCLK</sub> – 0.5  | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization results, not tested in production.

# Table 88. WLCSP64+2 - 66-ball, 4.539 x 4.911 mm, 0.4 mm pitch wafer level chip scale package mechanical data (continued)

| Symbol | Symbol |       |       | inches <sup>(1)</sup> |        |        |  |

|--------|--------|-------|-------|-----------------------|--------|--------|--|

| Symbol | Min    | Тур   | Max   | Min                   | Тур    | Max    |  |

| F      | -      | 0.220 | -     | -                     | 0.0087 | -      |  |

| G      | -      | 0.386 | -     | -                     | 0.0152 | -      |  |

| ааа    | -      | -     | 0.100 | -                     | -      | 0.0039 |  |

| bbb    | -      | -     | 0.100 | -                     | -      | 0.0039 |  |

| CCC    | -      | -     | 0.100 | -                     | -      | 0.0039 |  |

| ddd    | -      | -     | 0.050 | -                     | -      | 0.0020 |  |

| eee    | -      | -     | 0.050 | -                     | -      | 0.0020 |  |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

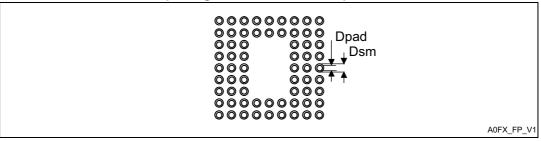

# Figure 80. WLCSP64+2 - 66-ball, 4.539 x 4.911 mm, 0.4 mm pitch wafer level chip scale package recommended footprint

#### Table 89. WLCSP64 recommended PCB design rules (0.4 mm pitch)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.4                                                              |

| Dpad              | 0.225 mm                                                         |

| Dsm               | 0.290 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.250 mm                                                         |

| Stencil thickness | 0.100 mm                                                         |

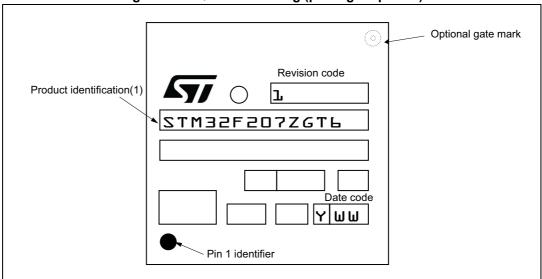

## **Device marking**

Figure 86. LQFP144 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 7.5 LQFP176 package information

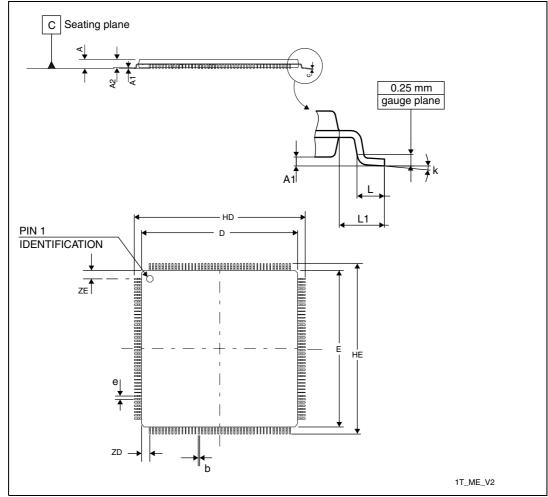

Figure 87. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline

1. Drawing is not to scale.

| Table 92. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data                                                       |

|        | Dimensions  |      |        |                       |      |        |

|--------|-------------|------|--------|-----------------------|------|--------|

| Symbol | millimeters |      |        | inches <sup>(1)</sup> |      |        |

|        | Min.        | Тур. | Max.   | Min.                  | Тур. | Max.   |

| А      | -           | -    | 1.600  | -                     | -    | 0.0630 |

| A1     | 0.050       | -    | 0.150  | 0.0020                | -    | 0.0059 |

| A2     | 1.350       | -    | 1.450  | 0.0531                | -    | 0.0571 |

| b      | 0.170       | -    | 0.270  | 0.0067                | -    | 0.0106 |

| с      | 0.090       | -    | 0.200  | 0.0035                | -    | 0.0079 |

| D      | 23.900      | -    | 24.100 | 0.9409                | -    | 0.9488 |

DocID15818 Rev 13

# Figure 88. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.