Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                           |

| Number of I/O              | 140                                                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                                                       |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320K x 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                      |

| Mounting Type              | Surface Mount                                                                                          |

| Package / Case             | 201-UFBGA                                                                                              |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f745iek6                                  |

|                            |                                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Each stream is connected to dedicated hardware DMA requests, with support for software trigger on each stream. Configuration is made by software and transfer sizes between source and destination are independent.

The DMA can be used with the main peripherals:

- SPI and I<sup>2</sup>S

- I<sup>2</sup>C

- USART

- General-purpose, basic and advanced-control timers TIMx

- DAC

- SDMMC

- Camera interface (DCMI)

- ADC

- SAI

- SPDIFRX

- Quad-SPI

- HDMI-CEC

# 2.8 Flexible memory controller (FMC)

The Flexible memory controller (FMC) includes three memory controllers:

- The NOR/PSRAM memory controller

- The NAND/memory controller

- The Synchronous DRAM (SDRAM/Mobile LPSDR SDRAM) controller

The main features of the FMC controller are the following:

- Interface with static-memory mapped devices including:

- Static random access memory (SRAM)

- NOR Flash memory/OneNAND Flash memory

- PSRAM (4 memory banks)

- NAND Flash memory with ECC hardware to check up to 8 Kbytes of data

- Interface with synchronous DRAM (SDRAM/Mobile LPSDR SDRAM) memories

- 8-,16-,32-bit data bus width

- Independent Chip Select control for each memory bank

- Independent configuration for each memory bank

- Write FIFO

- Read FIFO for SDRAM controller

- The Maximum FMC\_CLK/FMC\_SDCLK frequency for synchronous accesses is HCLK/2.

# LCD parallel interface

The FMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost-

# 2.12 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 97 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\$}$ -M7 with FPU core.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt latency.

# 2.13 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 24 edge-detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 168 GPIOs can be connected to the 16 external interrupt lines.

# 2.14 Clocks and startup

On reset the 16 MHz internal HSI RC oscillator is selected as the default CPU clock. The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock can be monitored for failure. If a failure is detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). This clock source is input to a PLL thus allowing to increase the frequency up to 216 MHz. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the two AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the two AHB buses is 216 MHz while the maximum frequency of the high-speed APB domains is 108 MHz. The maximum allowed frequency of the low-speed APB domain is 54 MHz.

The devices embed two dedicated PLL (PLLI2S and PLLSAI) which allow to achieve audio class performance. In this case, the  $I^2S$  and SAI master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

| Name                    | Abbreviation       | Definition                                                                                         |  |  |  |  |  |  |  |

|-------------------------|--------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin name                |                    | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |  |  |  |

|                         | S Supply pin       |                                                                                                    |  |  |  |  |  |  |  |

| Pin type                | I                  | Input only pin                                                                                     |  |  |  |  |  |  |  |

|                         | I/O                | Input / output pin                                                                                 |  |  |  |  |  |  |  |

|                         | FT                 | 5 V tolerant I/O                                                                                   |  |  |  |  |  |  |  |

| I/O structure           | TTa                | 3.3 V tolerant I/O directly connected to ADC                                                       |  |  |  |  |  |  |  |

| NO structure            | В                  | Dedicated BOOT pin                                                                                 |  |  |  |  |  |  |  |

|                         | RST                | Bidirectional reset pin with weak pull-up resistor                                                 |  |  |  |  |  |  |  |

| Notes                   | Unless otherwise   | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |  |  |  |

| Alternate<br>functions  | Functions selected | d through GPIOx_AFR registers                                                                      |  |  |  |  |  |  |  |

| Additional<br>functions | Functions directly | Functions directly selected/enabled through peripheral registers                                   |  |  |  |  |  |  |  |

#### Table 9. Legend/abbreviations used in the pinout table

## Table 10. STM32F745xx and STM32F746xx pin and ball definition

|         |          | F        | Pin Nu  | umbei    | r       |         |          |                                                            |          |               |       |                                                                                               |                         |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| 1       | A3       | D8       | 1       | A2       | 1       | 1       | A3       | PE2                                                        | I/O      | FT            | -     | TRACECLK, SPI4_SCK,<br>SAI1_MCLK_A,<br>QUADSPI_BK1_IO2,<br>ETH_MII_TXD3,<br>FMC_A23, EVENTOUT | -                       |

| 2       | В3       | C10      | 2       | A1       | 2       | 2       | A2       | PE3                                                        | I/O      | FT            | -     | TRACED0, SAI1_SD_B,<br>FMC_A19, EVENTOUT                                                      | -                       |

| 3       | C3       | B11      | 3       | B1       | 3       | 3       | A1       | PE4                                                        | I/O      | FT            | -     | TRACED1, SPI4_NSS,<br>SAI1_FS_A, FMC_A20,<br>DCMI_D4, LCD_B0,<br>EVENTOUT                     | -                       |

|         |          |          |         |          |         |         |          | 0 T IVI 32F 7 4                                            | 0.7.7    | pin a         | anu   | ball definition (continue                                                                                                                            | eu)                     |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         |          | I        | Pin Nı  | umber    |         |         | -        |                                                            |          |               |       |                                                                                                                                                      |                         |

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                  | Additional<br>functions |

| -       | -        | -        | -       | -        | -       | 186     | D8       | PK3                                                        | I/O      | FT            | -     | LCD_B4, EVENTOUT                                                                                                                                     | -                       |

| -       | -        | -        | -       | -        | -       | 187     | D7       | PK4                                                        | I/O      | FT            | -     | LCD_B5, EVENTOUT                                                                                                                                     | -                       |

| -       | -        | -        | -       | -        | -       | 188     | C6       | PK5                                                        | I/O      | FT            | -     | LCD_B6, EVENTOUT                                                                                                                                     | -                       |

| -       | -        | -        | -       | -        | -       | 189     | C5       | PK6                                                        | I/O      | FT            | -     | LCD_B7, EVENTOUT                                                                                                                                     | -                       |

| -       | -        | -        | -       | -        | -       | 190     | C4       | PK7                                                        | I/O      | FT            | -     | LCD_DE, EVENTOUT                                                                                                                                     | -                       |

| -       | -        | A7       | 132     | В7       | 160     | 191     | В7       | PG15                                                       | I/O      | FT            | -     | USART6_CTS,<br>FMC_SDNCAS,<br>DCMI_D13, EVENTOUT                                                                                                     | -                       |

| 89      | A7       | B7       | 133     | A10      | 161     | 192     | A10      | PB3(JTD<br>O/TRAC<br>ESWO)                                 | I/O      | FT            | -     | JTDO/TRACESWO,<br>TIM2_CH2,<br>SPI1_SCK/I2S1_CK,<br>SPI3_SCK/I2S3_CK,<br>EVENTOUT                                                                    | -                       |

| 90      | A6       | C7       | 134     | A9       | 162     | 193     | A9       | PB4(NJT<br>RST)                                            | I/O      | FT            | -     | NJTRST, TIM3_CH1,<br>SPI1_MISO, SPI3_MISO,<br>SPI2_NSS/I2S2_WS,<br>EVENTOUT                                                                          | -                       |

| 91      | C5       | C8       | 135     | A6       | 163     | 194     | A8       | PB5                                                        | I/O      | FT            | -     | TIM3_CH2, I2C1_SMBA,<br>SPI1_MOSI/I2S1_SD,<br>SPI3_MOSI/I2S3_SD,<br>CAN2_RX,<br>OTG_HS_ULPI_D7,<br>ETH_PPS_OUT,<br>FMC_SDCKE1,<br>DCMI_D10, EVENTOUT | -                       |

| 92      | B5       | A8       | 136     | B6       | 164     | 195     | B6       | PB6                                                        | I/O      | FT            | -     | TIM4_CH1, HDMI-CEC,<br>I2C1_SCL, USART1_TX,<br>CAN2_TX,<br>QUADSPI_BK1_NCS,<br>FMC_SDNE1, DCMI_D5,<br>EVENTOUT                                       | -                       |

| 93      | A5       | В8       | 137     | В5       | 165     | 196     | B5       | PB7                                                        | I/O      | FT            | -     | TIM4_CH2, I2C1_SDA,<br>USART1_RX, FMC_NL,<br>DCMI_VSYNC,<br>EVENTOUT                                                                                 | -                       |

| 94      | D5       | C9       | 138     | D6       | 166     | 197     | E6       | BOOT                                                       | I        | В             | -     | -                                                                                                                                                    | VPP                     |

| Table 10. STM32F745xx and STM32F746xx pin and ball definition ( | continued) |

|-----------------------------------------------------------------|------------|

|                                                                 |            |

|         |          | F        | Pin Ni  | umbei    | r       |         |          |                                                            |          | _                                  |   |                                                               |                         |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|------------------------------------|---|---------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | Pin type<br>I/O structure<br>Notes |   | Alternate functions                                           | Additional<br>functions |

| -       | -        | -        | -       | C3       | 175     | 207     | D6       | PI6                                                        | I/O      | FT                                 | - | TIM8_CH2, SAI2_SD_A,<br>FMC_D28, DCMI_D6,<br>LCD_B6, EVENTOUT | -                       |

| -       | -        | -        | -       | C2       | 176     | 208     | D4       | PI7                                                        | I/O      | FT                                 | - | TIM8_CH3, SAI2_FS_A,<br>FMC_D29, DCMI_D7,<br>LCD_B7, EVENTOUT | -                       |

## Table 10. STM32F745xx and STM32F746xx pin and ball definition (continued)

1. Function availability depends on the chosen device.

PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited:

- The speed should not exceed 2 MHz with a maximum load of 30 pF.

- These I/Os must not be used as a current source (e.g. to drive an LED).

3. Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F75xxx and STM32F74xxx reference manual.

4. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

If the device is delivered in an WLCSP143, UFBGA176, LQFP176, TFBGA100 or TFBGA216 package, and the BYPASS\_REG pin is set to VDD (Regulator OFF/internal reset ON mode), then PA0 is used as an internal Reset (active low).

5

DocID027590 Rev 4

|        |      | AF0 | AF1    | AF2          | AF3                             | AF4                | AF5                       | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11            | AF12                       | AF13           | AF14   | AF15         |

|--------|------|-----|--------|--------------|---------------------------------|--------------------|---------------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|-----------------|----------------------------|----------------|--------|--------------|

| P      | ort  | SYS | TIM1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6        | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI           | LCD    | SYS          |

|        | PH8  | -   | -      | -            | -                               | I2C3_SD<br>A       | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D1<br>6                | DCMI_H<br>SYNC | LCD_R2 | EVEN<br>TOUT |

|        | PH9  | -   | -      | -            | -                               | I2C3_SM<br>BA      | -                         | -             | -                                           | -                                               | TIM12_C<br>H2                              | -                                        | -               | FMC_D1<br>7                | DCMI_D<br>0    | LCD_R3 | EVEN<br>TOUT |

|        | PH10 | -   | -      | TIM5_C<br>H1 | -                               | I2C4_SM<br>BA      | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D1<br>8                | DCMI_D<br>1    | LCD_R4 | EVEN<br>TOUT |

| Port H | PH11 | -   | -      | TIM5_C<br>H2 | -                               | I2C4_SC<br>L       | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D1<br>9                | DCMI_D<br>2    | LCD_R5 | EVEN<br>TOUT |

| POILE  | PH12 | -   | -      | TIM5_C<br>H3 | -                               | I2C4_SD<br>A       | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>0                | DCMI_D<br>3    | LCD_R6 | EVEN<br>TOUT |

|        | PH13 | -   | -      | -            | TIM8_CH<br>1N                   | -                  | -                         | -             | -                                           | -                                               | CAN1_T<br>X                                | -                                        | -               | FMC_D2<br>1                | -              | LCD_G2 | EVEN<br>TOUT |

|        | PH14 | -   | -      | -            | TIM8_CH<br>2N                   | -                  | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>2                | DCMI_D<br>4    | LCD_G3 | EVEN<br>TOUT |

|        | PH15 | -   | -      | -            | TIM8_CH<br>3N                   | -                  | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>3                | DCMI_D<br>11   | LCD_G4 | EVEN<br>TOUT |

|        | PI0  | -   | -      | TIM5_C<br>H4 | -                               | -                  | SPI2_NS<br>S/I2S2_<br>WS  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>4                | DCMI_D<br>13   | LCD_G5 | EVEN<br>TOUT |

|        | PI1  | -   | -      | -            | TIM8_BKI<br>N2                  | -                  | SPI2_SC<br>K/I2S2_<br>CK  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>5                | DCMI_D<br>8    | LCD_G6 | EVEN<br>TOUT |

|        | PI2  | -   | -      | -            | TIM8_CH<br>4                    | -                  | SPI2_MI<br>SO             | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>6                | DCMI_D<br>9    | LCD_G7 | EVEN<br>TOUT |

| Port I | PI3  | -   | -      | -            | TIM8_ET<br>R                    | -                  | SPI2_M<br>OSI/I2S2<br>_SD | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>7                | DCMI_D<br>10   | -      | EVEN<br>TOUT |

|        | PI4  | -   | -      | -            | TIM8_BKI<br>N                   | -                  | -                         | -             | -                                           | -                                               | -                                          | SAI2_MC<br>K_A                           | -               | FMC_NB<br>L2               | DCMI_D<br>5    | LCD_B4 | EVEN<br>TOUT |

|        | PI5  | -   | -      | -            | TIM8_CH<br>1                    | -                  | -                         | -             | -                                           | -                                               | -                                          | SAI2_SC<br>K_A                           | -               | FMC_NB<br>L3               | DCMI_V<br>SYNC | LCD_B5 | EVEN<br>TOUT |

|        | PI6  | -   | -      | -            | TIM8_CH<br>2                    | -                  | -                         | -             | -                                           | -                                               | -                                          | SAI2_SD_<br>A                            | -               | FMC_D2<br>8                | DCMI_D<br>6    | LCD_B6 | EVEN<br>TOUT |

Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

AF0

AF1

AF2

AF3

AF4

AF6

AF7

AF8

AF9

AF10

AF11

AF12

AF13

AF14

AF15

85/227

STM32F745xx STM32F746xx

Pinouts and pin description

| Symbol                              | Parameter                                                                           | Conditions                                                                                | Min  | Тур  | Мах  | Unit |

|-------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

|                                     |                                                                                     | PLS[2:0]=000 (rising edge)                                                                | 2.09 | 2.14 | 2.19 | V    |

|                                     |                                                                                     | PLS[2:0]=000 (falling edge)                                                               | 1.98 | 2.04 | 2.08 | V    |

|                                     |                                                                                     | PLS[2:0]=001 (rising edge)                                                                | 2.23 | 2.30 | 2.37 | V    |

|                                     |                                                                                     | PLS[2:0]=001 (falling edge)                                                               | 2.13 | 2.19 | 2.25 | V    |

|                                     |                                                                                     | PLS[2:0]=010 (rising edge)                                                                | 2.39 | 2.45 | 2.51 | V    |

|                                     |                                                                                     | PLS[2:0]=010 (falling edge)                                                               | 2.29 | 2.35 | 2.39 | V    |

|                                     |                                                                                     | PLS[2:0]=011 (rising edge)                                                                | 2.54 | 2.60 | 2.65 | V    |

| M                                   | Programmable voltage                                                                | PLS[2:0]=011 (falling edge)                                                               | 2.44 | 2.51 | 2.56 | V    |

| V <sub>PVD</sub>                    | detector level selection                                                            | PLS[2:0]=100 (rising edge)                                                                | 2.70 | 2.76 | 2.82 | V    |

|                                     |                                                                                     | PLS[2:0]=100 (falling edge)                                                               | 2.59 | 2.66 | 2.71 | V    |

|                                     |                                                                                     | PLS[2:0]=101 (rising edge)                                                                | 2.86 | 2.93 | 2.99 | V    |

|                                     |                                                                                     | PLS[2:0]=101 (falling edge)                                                               | 2.65 | 2.84 | 2.92 | V    |

|                                     |                                                                                     | PLS[2:0]=110 (rising edge)                                                                | 2.96 | 3.03 | 3.10 | V    |

|                                     |                                                                                     | PLS[2:0]=110 (falling edge)                                                               | 2.85 | 2.93 | 2.99 | V    |

|                                     |                                                                                     | PLS[2:0]=111 (rising edge)                                                                | 3.07 | 3.14 | 3.21 | V    |

|                                     |                                                                                     | PLS[2:0]=111 (falling edge)                                                               | 2.95 | 3.03 | 3.09 | V    |

| V <sub>PVDhyst</sub> <sup>(1)</sup> | PVD hysteresis                                                                      | -                                                                                         | -    | 100  | -    | mV   |

| V                                   | Power-on/power-down                                                                 | Falling edge                                                                              | 1.60 | 1.68 | 1.76 | V    |

| V <sub>POR/PDR</sub>                | reset threshold                                                                     | Rising edge                                                                               | 1.64 | 1.72 | 1.80 | V    |

| V <sub>PDRhyst</sub> <sup>(1)</sup> | PDR hysteresis                                                                      | -                                                                                         | -    | 40   | -    | mV   |

|                                     | Brownout level 1                                                                    | Falling edge                                                                              | 2.13 | 2.19 | 2.24 | V    |

| V <sub>BOR1</sub>                   | threshold                                                                           | Rising edge                                                                               | 2.23 | 2.29 | 2.33 | V    |

| V                                   | Brownout level 2                                                                    | Falling edge                                                                              | 2.44 | 2.50 | 2.56 | V    |

| V <sub>BOR2</sub>                   | threshold                                                                           | Rising edge                                                                               | 2.53 | 2.59 | 2.63 | V    |

| V                                   | Brownout level 3                                                                    | Falling edge                                                                              | 2.75 | 2.83 | 2.88 | V    |

| V <sub>BOR3</sub>                   | threshold                                                                           | Rising edge                                                                               | 2.85 | 2.92 | 2.97 | V    |

| V <sub>BORhyst</sub> <sup>(1)</sup> | BOR hysteresis                                                                      | -                                                                                         | -    | 100  | -    | mV   |

| T <sub>RSTTEMPO</sub>               | POR reset temporization                                                             | -                                                                                         | 0.5  | 1.5  | 3.0  | ms   |

| I <sub>RUSH</sub> <sup>(1)</sup>    | InRush current on<br>voltage regulator power-<br>on (POR or wakeup<br>from Standby) | -                                                                                         | -    | 160  | 250  | mA   |

| E <sub>RUSH</sub> <sup>(1)</sup>    | InRush energy on<br>voltage regulator power-<br>on (POR or wakeup<br>from Standby)  | V <sub>DD</sub> = 1.7 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -    | -    | 5.4  | μC   |

| Table 22. reset and power control block characteristics |

|---------------------------------------------------------|

|---------------------------------------------------------|

| Table 27. Typical and maximum current consumption in Run mode, code with data processing |

|------------------------------------------------------------------------------------------|

| running from Flash memory on ITCM interface (ART disabled), regulator ON                 |

|                 |                   | O an diti ana                                |                         | `   |           | Max <sup>(1)</sup> |           |      |     |  |

|-----------------|-------------------|----------------------------------------------|-------------------------|-----|-----------|--------------------|-----------|------|-----|--|

| Symbol          | Parameter         | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур | TA= 25 °C | TA=85 °C           | TA=105 °C | Unit |     |  |

|                 |                   |                                              | 216                     | 205 | 237       | 261                | -         |      |     |  |

|                 |                   |                                              | 200                     | 191 | 219       | 241                | 260       |      |     |  |

|                 |                   |                                              | 180                     | 176 | 202       | 218                | 232       |      |     |  |

|                 |                   | All peripherals<br>enabled <sup>(2)(3)</sup> | 168                     | 158 | 181       | 196                | 209       |      |     |  |

|                 |                   | chabled                                      | onabiod                 |     | 144       | 130                | 148       | 161  | 172 |  |

|                 |                   |                                              | 60                      | 58  | 67        | 79                 | 89        |      |     |  |

|                 | Supply current in |                                              | 25                      | 27  | 32        | 43                 | 54        | mA   |     |  |

| I <sub>DD</sub> | RUN mode          |                                              | 216                     | 130 | 149       | 173                | -         | mA   |     |  |

|                 |                   |                                              | 200                     | 121 | 138       | 160                | 179       |      |     |  |

|                 |                   |                                              | 180                     | 113 | 129       | 145                | 159       |      |     |  |

|                 |                   | All peripherals disabled <sup>(3)</sup>      | 168                     | 102 | 116       | 131                | 144       |      |     |  |

|                 |                   |                                              | 144                     | 88  | 100       | 112                | 123       |      |     |  |

|                 |                   |                                              | 60                      | 40  | 45        | 57                 | 68        |      |     |  |

|                 |                   |                                              | 25                      | 19  | 22        | 33                 | 44        |      |     |  |

1. Guaranteed by characterization results.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

|         |                          |         | I consumption | (00111111004) | 11     |

|---------|--------------------------|---------|---------------|---------------|--------|

| Р       | eripheral                | Scale 1 | Scale 2       | Scale 3       | Unit   |

|         | TIM2                     | 19.8    | 18.7          | 16.1          |        |

| Γ       | TIM3                     | 16.6    | 15.1          | 13.6          |        |

| Ī       | TIM4                     | 16.2    | 15.1          | 13.3          |        |

| Ī       | TIM5                     | 19      | 17.8          | 15.8          |        |

| Ī       | TIM6                     | 3       | 2.7           | 2.5           |        |

| Ī       | TIM7                     | 3       | 2.7           | 2.5           |        |

| Ī       | TIM12                    | 12.4    | 11.3          | 10.3          |        |

| Ī       | TIM13                    | 6       | 5.3           | 5             |        |

| ſ       | TIM14                    | 6       | 5.3           | 5             |        |

| Ī       | LPTIM1                   | 9.4     | 8.7           | 8.1           |        |

| - F     | WWDG                     | 1.8     | 1.6           | 1.4           |        |

| Ē       | SPI2/I2S2 <sup>(3)</sup> | 3       | 2.9           | 2.8           |        |

| Ī       | SPI3/I2S3 <sup>(3)</sup> | 3.2     | 2.9           | 2.8           |        |

| APB1    | SPDIFRX                  | 2.2     | 2             | 1.7           |        |

| (up to  | USART2                   | 12.8    | 12            | 10.8          | µA/MHz |

| 54 MHz) | USART3                   | 15.6    | 14.2          | 13.1          |        |

| Ē       | UART4                    | 11.8    | 10.7          | 9.7           |        |

| ſ       | UART5                    | 11.2    | 10            | 9.2           |        |

| Ī       | I2C1                     | 9.8     | 8.7           | 7.8           |        |

| ľ       | I2C2                     | 8.6     | 7.8           | 7.2           |        |

| Ī       | I2C3                     | 8.6     | 7.8           | 7.2           |        |

| Ī       | I2C4                     | 12      | 10.9          | 9.7           |        |

| - F     | CAN1                     | 6.8     | 6             | 5.6           |        |

| Ē       | CAN2                     | 6.8     | 6             | 5.8           |        |

| Ē       | CEC                      | 1       | 0.7           | 0.8           |        |

| T       | PWR                      | 1.2     | 0.9           | 0.8           |        |

| T       | DAC <sup>(4)</sup>       | 3       | 2.7           | 2.5           |        |

| f       | UART7                    | 12.4    | 11.6          | 10            |        |

| T       | UART8                    | 10.4    | 9.3           | 8.6           |        |

Table 35. Peripheral current consumption (continued)

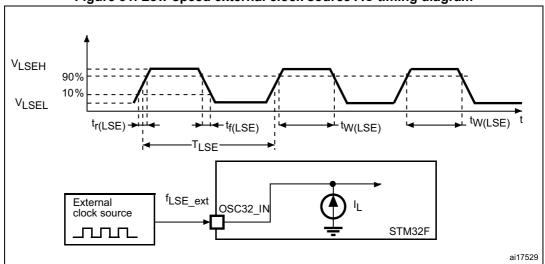

Figure 31. Low-speed external clock source AC timing diagram

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 39*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                            | Parameter                               | Conditions                                                            | Min   | Тур | Max | Unit |

|-----------------------------------|-----------------------------------------|-----------------------------------------------------------------------|-------|-----|-----|------|

| f <sub>OSC_IN</sub>               | Oscillator frequency                    | -                                                                     | 4     | -   | 26  | MHz  |

| R <sub>F</sub>                    | Feedback resistor                       | -                                                                     | -     | 200 | -   | kΩ   |

| 1                                 | HSE current consumption                 | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =5 pF@25 MHz  | -     | 450 | -   | μA   |

| IDD                               |                                         | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =10 pF@25 MHz | -     | 530 | -   | μΑ   |

| ACC <sub>HSE</sub> <sup>(2)</sup> | HSE accuracy                            | -                                                                     | - 500 | -   | 500 | ppm  |

| G <sub>m</sub> _crit_max          | Maximum critical crystal g <sub>m</sub> | Startup                                                               | -     | -   | 1   | mA/V |

| $t_{SU(HSE}^{(3)}$                | Startup time                            | $V_{\text{DD}}$ is stabilized                                         | -     | 2   | -   | ms   |

| Table 39. | HSE 4-26 | MHz    | oscillator | characteristics( | (1) |

|-----------|----------|--------|------------|------------------|-----|

| 10010 00. |          | 111112 | osomator   | onuluotonotios   |     |

1. Guaranteed by design.

2. This parameter depends on the crystal used in the application. The minimum and maximum values must be respected to comply with USB standard specifications.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is based on characterization results. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

| Symbol                  | Parameter                  | Conditions                                  | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|---------------------------------------------|--------------------|-----|--------------------|------|

| t <sub>erase256kb</sub> |                            | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 2.1 | 4                  |      |

|                         | Sector (256 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 1.5 | 2.6                | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 1   | 2                  |      |

|                         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 8   | 16                 |      |

| t <sub>ME</sub>         |                            | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 5.6 | 11.2               | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 4   | 8                  |      |

| V <sub>prog</sub>       |                            | 32-bit program operation                    | 2.7                | -   | 3                  | V    |

|                         | Programming voltage        | 16-bit program operation                    | 2.1                | -   | 3.6                | V    |

|                         |                            | 8-bit program operation                     | 1.7                | -   | 3.6                | V    |

Table 48. Flash memory programming (continued)

1. Guaranteed by characterization results.

2. The maximum programming time is measured after 100K erase operations.

| Symbol                          | Parameter                                        | Parameter Conditions Min |     | Тур | Max <sup>(1)</sup> | Unit |

|---------------------------------|--------------------------------------------------|--------------------------|-----|-----|--------------------|------|

| t <sub>prog</sub>               | Double word programming                          |                          | -   | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE32KB</sub>          | Sector (32 KB) erase time                        | $T_A = 0$ to +40 °C      | -   | 180 | -                  |      |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>DD</sub> = 3.3 V  | -   | 450 | -                  | ms   |

| t <sub>ERASE256KB</sub>         | Sector (256 KB) erase time                       | V <sub>PP</sub> = 8.5 V  | -   | 900 | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                  |                          | -   | 6.9 | -                  | S    |

| V <sub>prog</sub>               | Programming voltage                              | -                        | 2.7 | -   | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -                        | 7   | -   | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -                        | 10  | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                        | -   | -   | 1                  | hour |

#### Table 49. Flash memory programming with V<sub>PP</sub>

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

#### STM32F745xx STM32F746xx

| Symbol                         | Para                                                                      | neter                                      | Conditions                                                       | Min                                     | Тур  | Max  | Unit |

|--------------------------------|---------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------|-----------------------------------------|------|------|------|

|                                | FT, TTa and NRST I/O input high level voltage <sup>(5)</sup>              |                                            |                                                                  | 0.45V <sub>DD</sub> +0.3 <sup>(1)</sup> |      |      |      |

|                                |                                                                           |                                            | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                     | 0.7V <sub>DD</sub> <sup>(2)</sup>       | -    | -    |      |

| V <sub>IH</sub>                | BOOT I/O inpu                                                             | t high level                               | 1.75 V≤V <sub>DD</sub> ≤3.6 V, –<br>40 °C≤T <sub>A</sub> ≤105 °C | 0.17V <sub>DD</sub> +0.7 <sup>(1)</sup> |      |      | V    |

|                                | voltage                                                                   |                                            | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C     | 0.17 V <sub>DD</sub> +0.7 V             | -    | -    |      |

|                                | FT, TTa and NF hysteresis                                                 | RST I/O input                              | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                     | 10%V <sub>DD</sub> <sup>(3)</sup>       | -    | -    |      |

| V <sub>HYS</sub>               |                                                                           | thystoresis                                | 1.75 V≤V <sub>DD</sub> ≤3.6 V, –<br>40 °C≤T <sub>A</sub> ≤105 °C | 0.1                                     |      |      | V    |

|                                | BOOT I/O inpu                                                             | rysteresis                                 | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C     | 0.1                                     | -    | -    |      |

|                                | I/O input leaka                                                           | ge current <sup>(4)</sup>                  | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub>                | -                                       | - ±1 |      |      |

| l <sub>lkg</sub>               | I/O FT input lea                                                          | kage current                               | $V_{IN} = 5 V$                                                   | -                                       | -    | 3    | μA   |

| R <sub>PU</sub>                | All<br>ex<br>PA<br>(O<br>Weak pull-up<br>,O<br>R <sub>PU</sub> equivalent |                                            | V <sub>IN</sub> = V <sub>SS</sub>                                | 30                                      | 40   | 50   |      |

|                                | resistor <sup>(6)</sup>                                                   | PA10/PB12<br>(OTG_FS_ID<br>,OTG_HS_ID<br>) |                                                                  | 7                                       | 10   | 14   | ko   |

|                                | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_ID<br>,OTG_HS_ID<br>)      | V <sub>IN</sub> = V <sub>DD</sub>          | 30                                                               | 40                                      | 50   | - kΩ |      |

|                                | (OTG_FS_I                                                                 | PA10/PB12<br>(OTG_FS_ID<br>,OTG_HS_ID<br>) |                                                                  | 7                                       | 10   | 14   |      |

| C <sub>IO</sub> <sup>(8)</sup> | I/O pin capacita                                                          | ince                                       | -                                                                | -                                       | 5    | -    | pF   |

#### Table 56. I/O static characteristics (continued)

1. Guaranteed by design.

2. Tested in production.

3. With a minimum of 200 mV.

4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 55: I/O current injection susceptibility

- To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 55: I/O current injection susceptibility

- 6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

DocID027590 Rev 4

| Symbol                            | Parameter                                                            | Conditions | Min | Тур | Max | Unit |

|-----------------------------------|----------------------------------------------------------------------|------------|-----|-----|-----|------|

| I <sub>VREF+</sub> <sup>(2)</sup> | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode | -          | -   | 300 | 500 | μA   |

| I <sub>VDDA</sub> <sup>(2)</sup>  | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode | -          | -   | 1.6 | 1.8 | mA   |

Table 62. ADC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 2.17.2: Internal reset OFF).

2. Guaranteed by characterization results.

3.  $V_{\mathsf{REF}^+}$  is internally connected to  $V_{\mathsf{DDA}}$  and  $V_{\mathsf{REF}^-}$  is internally connected to  $V_{\mathsf{SSA}}.$

4.  $R_{ADC}$  maximum value is given for V<sub>DD</sub>=1.7 V, and minimum value for V<sub>DD</sub>=3.3 V.

5. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 62.

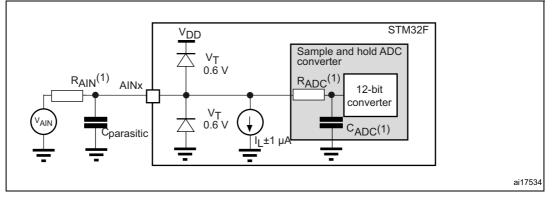

#### Equation 1: R<sub>AIN</sub> max formula

$$\mathsf{R}_{\mathsf{AIN}} = \frac{(k-0.5)}{\mathsf{f}_{\mathsf{ADC}} \times \mathsf{C}_{\mathsf{ADC}} \times \mathsf{ln}(2^{\mathsf{N}+2})} - \mathsf{R}_{\mathsf{ADC}}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

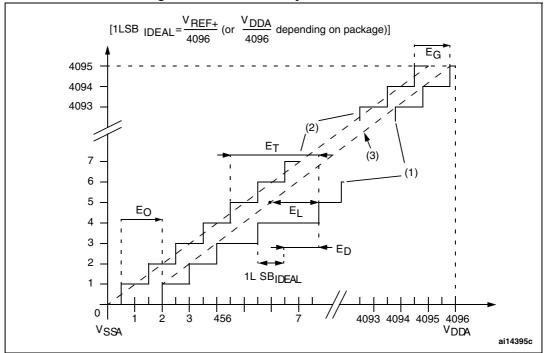

| Symbol | Parameter                    | Test conditions                                             | Тур | Max <sup>(1)</sup> | Unit |

|--------|------------------------------|-------------------------------------------------------------|-----|--------------------|------|

| ET     | Total unadjusted error       |                                                             | ±3  | ±4                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =18 MHz<br>V <sub>DDA</sub> = 1.7 to 3.6 V | ±2  | ±3                 |      |

| EG     | Gain error                   | $V_{\text{REF}}$ = 1.7 to 3.6 V                             | ±1  | ±3                 | LSB  |

| ED     | Differential linearity error | V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V                  | ±1  | ±2                 |      |

| EL     | Integral linearity error     |                                                             | ±2  | ±3                 |      |

Table 63. ADC static accuracy at f<sub>ADC</sub> = 18 MHz

1. Guaranteed by characterization results.

| Symbol | Parameter                    | Test conditions                                                                | Тур  | Max <sup>(1)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 30 MHz,<br>R <sub>AIN</sub> < 10 kΩ                         | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,                                               | ±1.5 | ±4                 | LSB  |

| ED     | Differential linearity error | V <sub>REF</sub> = 1.7 to 3.6 V,<br>V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                | ±1.5 | ±3                 |      |

1. Guaranteed by characterization results.

Figure 41. ADC accuracy characteristics

- 1. See also Table 64.

- 2. Example of an actual transfer curve.

- 3. Ideal transfer curve.

- 4 End point correlation line.

$E_T$  = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. 5.

EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

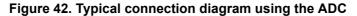

- 1. Refer to Table 62 for the values of RAIN, RADC and CADC.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

# General PCB design guidelines

1 µF // 10 nF

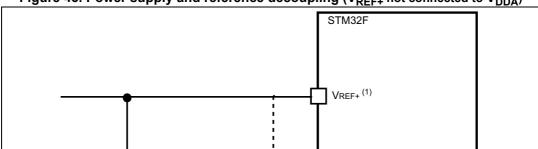

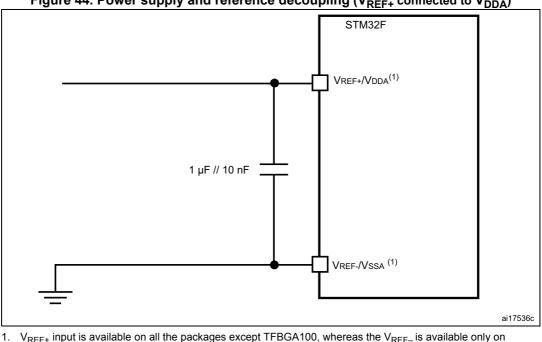

Power supply decoupling should be performed as shown in *Figure 43* or *Figure 44*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

Vdda

VSSA/VREF+<sup>(1)</sup>

Figure 43. Power supply and reference decoupling ( $V_{REF+}$  not connected to  $V_{DDA}$ )

1.  $V_{REF+}$  input is available on all the packages except TFBGA100 whereas the  $V_{REF-}$  is available only on UFBGA176 and TFBGA216. When  $V_{REF-}$  is not available, it is internally connected to  $V_{DDA}$  and  $V_{SSA}$ .

1 µF // 10 nF

Figure 44. Power supply and reference decoupling (V<sub>REF+</sub> connected to V<sub>DDA</sub>)

V<sub>REF+</sub> input is available on all the packages except TFBGA100, whereas the V<sub>REF</sub> is available only on UFBGA176 and TFBGA216. When V<sub>REF-</sub> is not available, it is internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

ai17535b

1. Guaranteed by characterization results.

| Symbol                    | Parameter                                 | Min                     | Max                     | Unit |  |  |  |  |

|---------------------------|-------------------------------------------|-------------------------|-------------------------|------|--|--|--|--|

| t <sub>w(NE)</sub>        | FMC_NE low time 9                         |                         | 9T <sub>HCLK</sub> +1.5 |      |  |  |  |  |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 7T <sub>HCLK</sub> –0.5 | 7T <sub>HCLK</sub> +0.5 | ns   |  |  |  |  |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +2   | -                       |      |  |  |  |  |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> –1   | -                       |      |  |  |  |  |

1. Guaranteed by characterization results.

# Synchronous waveforms and timings

*Figure 62* through *Figure 65* represent synchronous waveforms and *Table 96* through *Table 99* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- BurstAccessMode = FMC\_BurstAccessMode\_Enable;

- MemoryType = FMC\_MemoryType\_CRAM;

- WriteBurst = FMC\_WriteBurst\_Enable;

- CLKDivision = 1;

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

- CL = 30 pF on data and address lines. CL = 10 pF on FMC\_CLK unless otherwise specified.

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

- For 2.7 V $\leq$ V<sub>DD</sub> $\leq$ 3.6 V, maximum FMC\_CLK = 108 MHz at CL=20 pF or 90 MHz at CL=30 pF (on FMC\_CLK).

- For 1.71 V $\leq$ V<sub>DD</sub><2.7 V, maximum FMC\_CLK = 70 MHz at CL=10 pF (on FMC\_CLK).

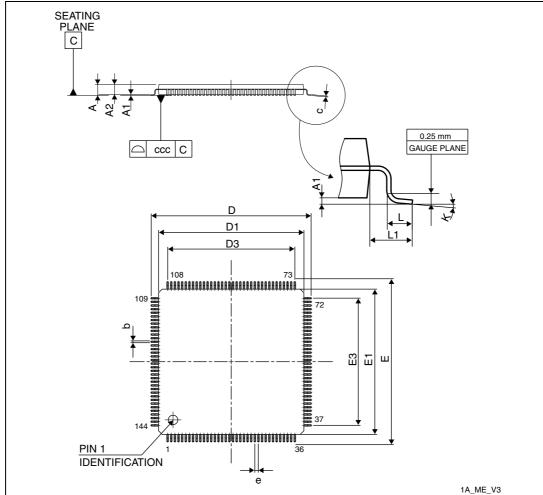

# 6.4 LQFP144, 20 x 20 mm low-profile quad flat package information

Figure 88. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline

1. Drawing is not to scale.

Table 117. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |  |

|--------|--------|-------------|--------|-----------------------|--------|--------|--|

| Symbol | Min    | Тур         | Max    | Min                   | Тур    | Мах    |  |

| А      | -      | -           | 1.600  | -                     | -      | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |  |

| D      | 21.800 | 22.000      | 22.200 | 0.8583                | 0.8661 | 0.874  |  |

| Figure 98. UFBGA176+25, 10 x 10 x 0.65 mm, ultra fine-pitch ball grid array |  |

|-----------------------------------------------------------------------------|--|

| package recommended footprint                                               |  |

## Table 121. UFBGA176+25 recommended PCB design rules (0.65 mm pitch BGA)

| Dimension         | Recommended values                                                    |

|-------------------|-----------------------------------------------------------------------|

| Pitch             | 0.65 mm                                                               |

| Dpad              | 0.300 mm                                                              |

| Dsm               | 0.400 mm typ. (depends on the soldermask reg-<br>istration tolerance) |

| Stencil opening   | 0.300 mm                                                              |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                         |

| Pad trace width   | 0.100 mm                                                              |

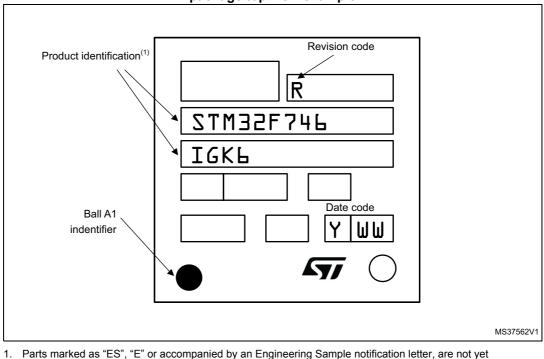

# Marking of engineering samples

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID027590 Rev 4