Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                           |

| Number of I/O              | 140                                                                                                    |

| Program Memory Size        | 1MB (1M × 8)                                                                                           |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320K x 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                      |

| Mounting Type              | Surface Mount                                                                                          |

| Package / Case             | 201-UFBGA                                                                                              |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f745igk6                                  |

|                            |                                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

SAI1 and SAI2 can be served by the DMA controller

#### 2.27 SPDIFRX Receiver Interface (SPDIFRX)

The SPDIFRX peripheral, is designed to receive an S/PDIF flow compliant with IEC-60958 and IEC-61937. These standards support simple stereo streams up to high sample rate, and compressed multi-channel surround sound, such as those defined by Dolby or DTS (up to 5.1).

The main features of the SPDIFRX are the following:

- Up to 4 inputs available

- Automatic symbol rate detection

- Maximum symbol rate: 12.288 MHz

- Stereo stream from 32 to 192 kHz supported

- Supports Audio IEC-60958 and IEC-61937, consumer applications

- Parity bit management

- Communication using DMA for audio samples

- Communication using DMA for control and user channel information

- Interrupt capabilities

The SPDIFRX receiver provides all the necessary features to detect the symbol rate, and decode the incoming data stream. The user can select the wanted SPDIF input, and when a valid signal will be available, the SPDIFRX will re-sample the incoming signal, decode the manchester stream, recognize frames, sub-frames and blocks elements. It delivers to the CPU decoded data, and associated status flags.

The SPDIFRX also offers a signal named spdif\_frame\_sync, which toggles at the S/PDIF sub-frame rate that will be used to compute the exact sample rate for clock drift algorithms.

#### 2.28 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S and SAI applications. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S/SAI sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I<sup>2</sup>S/SAI flow with an external PLL (or Codec output).

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

#### 2.42 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

#### 2.43 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F74xxx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

| Name                    | Abbreviation                                                     | Definition                                                                                         |  |  |  |  |

|-------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin name                |                                                                  | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |

|                         | S                                                                | Supply pin                                                                                         |  |  |  |  |

| Pin type                | I                                                                | Input only pin                                                                                     |  |  |  |  |

|                         | I/O                                                              | Input / output pin                                                                                 |  |  |  |  |

|                         | FT                                                               | 5 V tolerant I/O                                                                                   |  |  |  |  |

| I/O structure           | TTa                                                              | 3.3 V tolerant I/O directly connected to ADC                                                       |  |  |  |  |

| NO structure            | В                                                                | Dedicated BOOT pin                                                                                 |  |  |  |  |

|                         | RST                                                              | Bidirectional reset pin with weak pull-up resistor                                                 |  |  |  |  |

| Notes                   | Unless otherwise                                                 | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |

| Alternate<br>functions  | Functions selected                                               | d through GPIOx_AFR registers                                                                      |  |  |  |  |

| Additional<br>functions | Functions directly selected/enabled through peripheral registers |                                                                                                    |  |  |  |  |

#### Table 9. Legend/abbreviations used in the pinout table

#### Table 10. STM32F745xx and STM32F746xx pin and ball definition

|         |          | F        | Pin Nu  | umbei    | r       |         |          |                                                            |          |               |       |                                                                                               |                         |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| 1       | A3       | D8       | 1       | A2       | 1       | 1       | A3       | PE2                                                        | I/O      | FT            | -     | TRACECLK, SPI4_SCK,<br>SAI1_MCLK_A,<br>QUADSPI_BK1_IO2,<br>ETH_MII_TXD3,<br>FMC_A23, EVENTOUT | -                       |

| 2       | В3       | C10      | 2       | A1       | 2       | 2       | A2       | PE3                                                        | I/O      | FT            | -     | TRACED0, SAI1_SD_B,<br>FMC_A19, EVENTOUT                                                      | -                       |

| 3       | C3       | B11      | 3       | B1       | 3       | 3       | A1       | PE4                                                        | I/O      | FT            | -     | TRACED1, SPI4_NSS,<br>SAI1_FS_A, FMC_A20,<br>DCMI_D4, LCD_B0,<br>EVENTOUT                     | -                       |

80/227

DocID027590 Rev 4

|        | Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued) |             |        |              |                                 |                    |                           |               |                                             |                                                 |                                            |                                          |                 |                            |              |        |              |

|--------|------------------------------------------------------------------------------|-------------|--------|--------------|---------------------------------|--------------------|---------------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|-----------------|----------------------------|--------------|--------|--------------|

|        |                                                                              | AF0         | AF1    | AF2          | AF3                             | AF4                | AF5                       | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11            | AF12                       | AF13         | AF14   | AF15         |

| P      | ort                                                                          | SYS         | TIM1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6        | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI         | LCD    | SYS          |

|        | PD0                                                                          | -           | -      | -            | -                               | -                  | -                         | -             | -                                           | -                                               | CAN1_R<br>X                                | -                                        | -               | FMC_D2                     | -            | -      | EVEN<br>TOUT |

|        | PD1                                                                          | -           | -      | -            | -                               | -                  | -                         | -             | -                                           | -                                               | CAN1_T<br>X                                | -                                        | -               | FMC_D3                     | -            | -      | EVEN<br>TOUT |

|        | PD2                                                                          | TRACE<br>D2 | -      | TIM3_ET<br>R | -                               | -                  | -                         | -             | -                                           | UART5_<br>RX                                    | -                                          | -                                        | -               | SDMMC<br>1_CMD             | DCMI_D<br>11 | -      | EVEN<br>TOUT |

|        | PD3                                                                          | -           | -      | -            | -                               | -                  | SPI2_SC<br>K/I2S2_<br>CK  | -             | USART2<br>_CTS                              | -                                               | -                                          | -                                        | -               | FMC_CL<br>K                | DCMI_D<br>5  | LCD_G7 | EVEN<br>TOUT |

|        | PD4                                                                          | -           | -      | -            | -                               | -                  | -                         | -             | USART2<br>_RTS                              | -                                               | -                                          | -                                        | -               | FMC_N<br>OE                | -            | -      | EVEN<br>TOUT |

|        | PD5                                                                          | -           | -      | -            | -                               | -                  | -                         | -             | USART2<br>_TX                               | -                                               | -                                          | -                                        | -               | FMC_N<br>WE                | -            | -      | EVEN<br>TOUT |

|        | PD6                                                                          | -           | -      | -            | -                               | -                  | SPI3_M<br>OSI/I2S3<br>_SD | SAI1_SD<br>_A | USART2<br>_RX                               | -                                               | -                                          | -                                        | -               | FMC_N<br>WAIT              | DCMI_D<br>10 | LCD_B2 | EVEN<br>TOUT |

| Port D | PD7                                                                          | -           | -      | -            | -                               | -                  | -                         | -             | USART2<br>_CK                               | SPDIFRX<br>_IN0                                 | -                                          | -                                        | -               | FMC_NE<br>1                | -            | -      | EVEN<br>TOUT |

|        | PD8                                                                          | -           | -      | -            | -                               | -                  | -                         | -             | USART3<br>_TX                               | SPDIFRX<br>_IN1                                 | -                                          | -                                        | -               | FMC_D1<br>3                | -            | -      | EVEN<br>TOUT |

|        | PD9                                                                          | -           | -      | -            | -                               | -                  | -                         | -             | USART3<br>_RX                               | -                                               | -                                          | -                                        | -               | FMC_D1<br>4                | -            | -      | EVEN<br>TOUT |

|        | PD10                                                                         | -           | -      | -            | -                               | -                  | -                         | -             | USART3<br>_CK                               | -                                               | -                                          | -                                        | -               | FMC_D1<br>5                | -            | LCD_B3 | EVEN<br>TOUT |

|        | PD11                                                                         | -           | -      | -            | -                               | I2C4_SM<br>BA      | -                         | -             | USART3<br>_CTS                              | -                                               | QUADSP<br>I_BK1_IO<br>0                    | SAI2_SD_<br>A                            | -               | FMC_A1<br>6/FMC_<br>CLE    | -            | -      | EVEN<br>TOUT |

|        | PD12                                                                         | -           | -      | TIM4_C<br>H1 | LPTIM1_I<br>N1                  | I2C4_SC<br>L       | -                         | -             | USART3<br>_RTS                              | -                                               | QUADSP<br>I_BK1_IO<br>1                    | SAI2_FS_<br>A                            | -               | FMC_A1<br>7/FMC_<br>ALE    | -            | -      | EVEN<br>TOUT |

|        | PD13                                                                         | -           | -      | TIM4_C<br>H2 | LPTIM1_<br>OUT                  | I2C4_SD<br>A       | -                         | -             | -                                           | -                                               | QUADSP<br>I_BK1_IO<br>3                    | SAI2_SC<br>K_A                           | -               | FMC_A1<br>8                | -            | -      | EVEN<br>TOUT |

#### Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

84/227

DocID027590 Rev 4

|        |      |             | -      | Table 12 | 2. STM32                        | F745xx             | and ST             | //32F74       | 6xx alte                                    | rnate fu                                        | nction m                                   | napping                                  | (continu                                 | ed)                        |              |        |              |

|--------|------|-------------|--------|----------|---------------------------------|--------------------|--------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|------------------------------------------|----------------------------|--------------|--------|--------------|

|        |      | AF0         | AF1    | AF2      | AF3                             | AF4                | AF5                | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11                                     | AF12                       | AF13         | AF14   | AF15         |

| Po     | ort  | SYS         | TIM1/2 | TIM3/4/5 | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS                          | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI         | LCD    | SYS          |

|        | PG11 | -           | -      | -        | -                               | -                  | -                  | -             | SPDIFRX<br>_IN0                             | -                                               | -                                          | -                                        | ETH_MII_<br>TX_EN/E<br>TH_RMII_<br>TX_EN | -                          | DCMI_D<br>3  | LCD_B3 | EVEN<br>TOUT |

|        | PG12 | -           | -      | -        | LPTIM1_I<br>N1                  | -                  | SPI6_MI<br>SO      | -             | SPDIFRX<br>_IN1                             | USART6<br>_RTS                                  | LCD_B4                                     | -                                        | -                                        | FMC_NE<br>4                | -            | LCD_B1 | EVEN<br>TOUT |

| Port G | PG13 | TRACE<br>D0 | -      | -        | LPTIM1_<br>OUT                  | -                  | SPI6_SC<br>K       | -             | -                                           | USART6<br>_CTS                                  | -                                          | -                                        | ETH_MII_<br>TXD0/ET<br>H_RMII_T<br>XD0   | FMC_A2<br>4                | -            | LCD_R0 | EVEN<br>TOUT |

|        | PG14 | TRACE<br>D1 | -      | -        | LPTIM1_E<br>TR                  | -                  | SPI6_M<br>OSI      | -             | -                                           | USART6<br>_TX                                   | QUADSP<br>I_BK2_IO<br>3                    | -                                        | ETH_MII_<br>TXD1/ET<br>H_RMII_T<br>XD1   | FMC_A2<br>5                | -            | LCD_B0 | EVEN<br>TOUT |

|        | PG15 | -           | -      | -        | -                               | -                  | -                  | -             | -                                           | USART6<br>_CTS                                  | -                                          | -                                        | -                                        | FMC_SD<br>NCAS             | DCMI_D<br>13 | -      | EVEN<br>TOUT |

|        | PH0  | -           | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -                                        | -                          | -            | -      | EVEN<br>TOUT |

|        | PH1  | -           | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -                                        | -                          | -            | -      | EVEN<br>TOUT |

|        | PH2  | -           | -      | -        | LPTIM1_I<br>N2                  | -                  | -                  | -             | -                                           | -                                               | QUADSP<br>I_BK2_IO<br>0                    | SAI2_SC<br>K_B                           | ETH_MII_<br>CRS                          | FMC_SD<br>CKE0             | -            | LCD_R0 | EVEN<br>TOUT |

| Port H | PH3  | -           | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | QUADSP<br>I_BK2_IO<br>1                    | SAI2_MC<br>K_B                           | ETH_MII_<br>COL                          | FMC_SD<br>NE0              | -            | LCD_R1 | EVEN<br>TOUT |

|        | PH4  | -           | -      | -        | -                               | I2C2_SC<br>L       | -                  | -             | -                                           | -                                               | -                                          | OTG_HS_<br>ULPI_NX<br>T                  | -                                        | -                          | -            | -      | EVEN<br>TOUT |

|        | PH5  | -           | -      | -        | -                               | I2C2_SD<br>A       | SPI5_NS<br>S       | -             | -                                           | -                                               | -                                          | -                                        | -                                        | FMC_SD<br>NWE              | -            | -      | EVEN<br>TOUT |

|        | PH6  | -           | -      | -        | -                               | I2C2_SM<br>BA      | SPI5_SC<br>K       | -             | -                                           | -                                               | TIM12_C<br>H1                              | -                                        | ETH_MII_<br>RXD2                         | FMC_SD<br>NE1              | DCMI_D<br>8  | -      | EVEN<br>TOUT |

|        | PH7  | -           | -      | -        | -                               | I2C3_SC<br>L       | SPI5_MI<br>SO      | -             | -                                           | -                                               | -                                          | -                                        | ETH_MII_<br>RXD3                         | FMC_SD<br>CKE1             | DCMI_D<br>9  | -      | EVEN<br>TOUT |

# Pinouts and pin description

STM32F745xx STM32F746xx

| Bus  | Boundary address          | Peripheral               |

|------|---------------------------|--------------------------|

|      | 0x4008 0000- 0x4FFF FFFF  | Reserved                 |

|      | 0x4004 0000 - 0x4007 FFFF | USB OTG HS               |

|      | 0x4002 BC00- 0x4003 FFFF  | Reserved                 |

|      | 0x4002 B000 - 0x4002 BBFF | Chrom-ART (DMA2D)        |

|      | 0x4002 9400 - 0x4002 AFFF | Reserved                 |

|      | 0x4002 9000 - 0x4002 93FF |                          |

|      | 0x4002 8C00 - 0x4002 8FFF |                          |

|      | 0x4002 8800 - 0x4002 8BFF | ETHERNET MAC             |

|      | 0x4002 8400 - 0x4002 87FF |                          |

|      | 0x4002 8000 - 0x4002 83FF |                          |

|      | 0x4002 6800 - 0x4002 7FFF | Reserved                 |

|      | 0x4002 6400 - 0x4002 67FF | DMA2                     |

|      | 0x4002 6000 - 0x4002 63FF | DMA1                     |

|      | 0x4002 5000 - 0X4002 5FFF | Reserved                 |

|      | 0x4002 4000 - 0x4002 4FFF | BKPSRAM                  |

|      | 0x4002 3C00 - 0x4002 3FFF | Flash interface register |

| AHB1 | 0x4002 3800 - 0x4002 3BFF | RCC                      |

|      | 0X4002 3400 - 0X4002 37FF | Reserved                 |

|      | 0x4002 3000 - 0x4002 33FF | CRC                      |

|      | 0x4002 2C00 - 0x4002 2FFF | Reserved                 |

|      | 0x4002 2800 - 0x4002 2BFF | GPIOK                    |

|      | 0x4002 2400 - 0x4002 27FF | GPIOJ                    |

|      | 0x4002 2000 - 0x4002 23FF | GPIOI                    |

|      | 0x4002 1C00 - 0x4002 1FFF | GPIOH                    |

|      | 0x4002 1800 - 0x4002 1BFF | GPIOG                    |

|      | 0x4002 1400 - 0x4002 17FF | GPIOF                    |

|      | 0x4002 1000 - 0x4002 13FF | GPIOE                    |

|      | 0X4002 0C00 - 0x4002 0FFF | GPIOD                    |

|      | 0x4002 0800 - 0x4002 0BFF | GPIOC                    |

|      | 0x4002 0400 - 0x4002 07FF | GPIOB                    |

|      | 0x4002 0000 - 0x4002 03FF | GPIOA                    |

#### Table 13. STM32F745xx and STM32F746xx register boundary addresses (continued)

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 8000- 0x4000 FFFF  | Reserved            |

|      | 0x4000 7C00 - 0x4000 7FFF | UART8               |

|      | 0x4000 7800 - 0x4000 7BFF | UART7               |

|      | 0x4000 7400 - 0x4000 77FF | DAC                 |

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6C00 - 0x4000 6FFF | HDMI-CEC            |

|      | 0x4000 6800 - 0x4000 6BFF | CAN2                |

|      | 0x4000 6400 - 0x4000 67FF | CAN1                |

|      | 0x4000 6000 - 0x4000 63FF | 12C4                |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | 12C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 5000 - 0x4000 53FF | UART5               |

|      | 0x4000 4C00 - 0x4000 4FFF | UART4               |

|      | 0x4000 4800 - 0x4000 4BFF | USART3              |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

| APB1 | 0x4000 4000 - 0x4000 43FF | SPDIFRX             |

| AFDI | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

|      | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | Reserved            |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 2400 - 0x4000 27FF | LPTIM1              |

|      | 0x4000 2000 - 0x4000 23FF | TIM14               |

|      | 0x4000 1C00 - 0x4000 1FFF | TIM13               |

|      | 0x4000 1800 - 0x4000 1BFF | TIM12               |

|      | 0x4000 1400 - 0x4000 17FF | TIM7                |

|      | 0x4000 1000 - 0x4000 13FF | TIM6                |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | ТІМЗ                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

#### Table 13. STM32F745xx and STM32F746xx register boundary addresses (continued)

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted both to f<sub>HCLK</sub> frequency and V<sub>DD</sub> range (see *Table 18: Limitations depending on the operating power supply range*).

- When the regulator is ON, the voltage scaling and over-drive mode are adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for  $f_{HCLK} \le 144$  MHz

- Scale 2 for 144 MHz <  $f_{HCLK} \le 168$  MHz

- Scale 1 for 168 MHz <  $f_{HCLK} \le 216$  MHz. The over-drive is only ON at 216 MHz.

- When the regulator is OFF, the V12 is provided externally as described in *Table 17: General operating conditions*:

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/4$ , and  $f_{PCLK2} = f_{HCLK}/2$ .

- External clock frequency is 25 MHz and PLL is ON when f<sub>HCLK</sub> is higher than 25 MHz.

- The typical current consumption values are obtained for 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range and for T<sub>A</sub>= 25 °C unless otherwise specified.

- The maximum values are obtained for 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range and a maximum ambient temperature (T<sub>A</sub>) unless otherwise specified.

- For the voltage range 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V, the maximum frequency is 180 MHz.

### Table 24. Typical and maximum current consumption in Run mode, code with data processingrunning from ITCM RAM, regulator ON

| Symbol          | Doromotor            | Conditions                                   | £ (MILI-)               | Turn |                        | Max <sup>(1)</sup>     |                         | Unit       |

|-----------------|----------------------|----------------------------------------------|-------------------------|------|------------------------|------------------------|-------------------------|------------|

| Symbol          | Parameter            | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур  | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Onit       |

|                 |                      |                                              | 216                     | 178  | 208 <sup>(4)</sup>     | 230 <sup>(4)</sup>     | -                       |            |

|                 |                      |                                              | 200                     | 165  | 193                    | 212                    | 230                     |            |

|                 |                      |                                              | 180                     | 147  | 171 <sup>(4)</sup>     | 185 <sup>(4)</sup>     | 198 <sup>(4)</sup>      |            |

|                 |                      | All peripherals<br>enabled <sup>(2)(3)</sup> | 168                     | 130  | 152                    | 164                    | 177                     |            |

|                 |                      |                                              | 144                     | 100  | 116                    | 127                    | 137                     |            |

|                 |                      |                                              | 60                      | 44   | 52                     | 63                     | 73                      |            |

|                 | Supply<br>current in |                                              | 25                      | 21   | 25                     | 36                     | 46                      | <b>m</b> ( |

| I <sub>DD</sub> | RUN mode             |                                              | 216                     | 102  | 120 <sup>(4)</sup>     | 141 <sup>(4)</sup>     | -                       | mA         |

|                 |                      |                                              | 200                     | 95   | 111                    | 131                    | 149                     |            |

|                 |                      |                                              | 180                     | 84   | 98 <sup>(4)</sup>      | 112 <sup>(4)</sup>     | 125 <sup>(4)</sup>      |            |

|                 |                      | All peripherals<br>disabled <sup>(3)</sup>   | 168                     | 75   | 87                     | 100                    | 112                     |            |

|                 |                      | uisabicu .                                   | 144                     | 58   | 67                     | 77                     | 88                      |            |

|                 |                      |                                              | 60                      | 25   | 30                     | 41                     | 51                      |            |

|                 |                      |                                              | 25                      | 12   | 15                     | 25                     | 36                      |            |

1. Guaranteed by characterization results.

|         |                          |         | I consumption | (00111111004) | 11     |

|---------|--------------------------|---------|---------------|---------------|--------|

| Р       | eripheral                | Scale 1 | Scale 2       | Scale 3       | Unit   |

|         | TIM2                     | 19.8    | 18.7          | 16.1          |        |

| Γ       | TIM3                     | 16.6    | 15.1          | 13.6          |        |

| Ī       | TIM4                     | 16.2    | 15.1          | 13.3          |        |

| Ī       | TIM5                     | 19      | 17.8          | 15.8          |        |

| Ī       | TIM6                     | 3       | 2.7           | 2.5           |        |

| Ī       | TIM7                     | 3       | 2.7           | 2.5           |        |

| Ī       | TIM12                    | 12.4    | 11.3          | 10.3          |        |

| Ī       | TIM13                    | 6       | 5.3           | 5             |        |

| ſ       | TIM14                    | 6       | 5.3           | 5             |        |

| Ī       | LPTIM1                   | 9.4     | 8.7           | 8.1           |        |

| - F     | WWDG                     | 1.8     | 1.6           | 1.4           |        |

| Ē       | SPI2/I2S2 <sup>(3)</sup> | 3       | 2.9           | 2.8           |        |

| Ī       | SPI3/I2S3 <sup>(3)</sup> | 3.2     | 2.9           | 2.8           |        |

| APB1    | SPDIFRX                  | 2.2     | 2             | 1.7           |        |

| (up to  | USART2<br>USART3         | 12.8    | 12            | 10.8          | µA/MHz |

| 54 MHz) |                          | 15.6    | 14.2          | 13.1          |        |

| Ē       | UART4                    | 11.8    | 10.7          | 9.7           |        |

| ſ       | UART5                    | 11.2    | 10            | 9.2           |        |

| Ī       | I2C1                     | 9.8     | 8.7           | 7.8           |        |

| ľ       | I2C2                     | 8.6     | 7.8           | 7.2           |        |

| Ī       | I2C3                     | 8.6     | 7.8           | 7.2           |        |

| Ī       | I2C4                     | 12      | 10.9          | 9.7           |        |

| - F     | CAN1                     | 6.8     | 6             | 5.6           |        |

| Ē       | CAN2                     | 6.8     | 6             | 5.8           |        |

| Ē       | CEC                      | 1       | 0.7           | 0.8           |        |

| T       | PWR                      | 1.2     | 0.9           | 0.8           |        |

| T       | DAC <sup>(4)</sup>       | 3       | 2.7           | 2.5           |        |

| T       | UART7                    | 12.4    | 11.6          | 10            |        |

| T       | UART8                    | 10.4    | 9.3           | 8.6           |        |

Table 35. Peripheral current consumption (continued)

| Symbol           | Parameter      | Conditions                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |  |

|------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------|---------|--|

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |  |

|                  | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |  |

| t <sub>RET</sub> |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |  |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |  |

Table 50. Flash memory endurance and data retention

1. Guaranteed by characterization results.

2. Cycling performed over the whole temperature range.

#### 5.3.14 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 51*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                              | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 216 MHz, conforms<br>to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, TFBGA216, T <sub>A</sub><br>=+25 °C, f <sub>HCLK</sub> = 216 MHz,<br>conforms to IEC 61000-4-2 | 4A              |

Table 51. EMS characteristics

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$ ) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

#### 5.3.19 TIM timer characteristics

The parameters given in Table 60 are guaranteed by design.

Refer to Section 5.3.17: I/O port characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

|                        |                                                 |                                                                      |     |                         | 1                    |

|------------------------|-------------------------------------------------|----------------------------------------------------------------------|-----|-------------------------|----------------------|

| Symbol                 | Parameter                                       | Conditions <sup>(3)</sup>                                            | Min | Max                     | Unit                 |

| t <sub>res(TIM)</sub>  | Timer resolution time                           | AHB/APBx prescaler=1<br>or 2 or 4, f <sub>TIMxCLK</sub> =<br>216 MHz |     | -                       | t <sub>TIMxCLK</sub> |

|                        |                                                 | AHB/APBx<br>prescaler>4, f <sub>TIMxCLK</sub> =<br>108 MHz           | 1   | -                       | t <sub>TIMxCLK</sub> |

| f <sub>EXT</sub>       | Timer external clock<br>frequency on CH1 to CH4 | f <sub>TIMxCLK</sub> = 216 MHz                                       | 0   | f <sub>TIMxCLK</sub> /2 | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                                |                                                                      | -   | 16/32                   | bit                  |

| t <sub>MAX_COUNT</sub> | Maximum possible count with 32-bit counter      | -                                                                    | -   | 65536 ×<br>65536        | t <sub>TIMxCLK</sub> |

| Table 60. | TIMx | characteristics <sup>(1)(2</sup> | 2) |

|-----------|------|----------------------------------|----|

|-----------|------|----------------------------------|----|

1. TIMx is used as a general term to refer to the TIM1 to TIM12 timers.

2. Guaranteed by design.

The maximum timer frequency on APB1 or APB2 is up to 216 MHz, by setting the TIMPRE bit in the RCC\_DCKCFGR register, if APBx prescaler is 1 or 2 or 4, then TIMxCLK = HCLK, otherwise TIMxCLK = 4x PCLKx.

#### 5.3.20 RTC characteristics

#### Table 61. RTC characteristics

| Symbol | Parameter                                  | Parameter Conditions                                |   | Max |

|--------|--------------------------------------------|-----------------------------------------------------|---|-----|

| -      | f <sub>PCLK1</sub> /RTCCLK frequency ratio | Any read/write operation<br>from/to an RTC register | 4 | -   |

#### 5.3.21 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 62* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 17*.

| Table | 62. | ADC | characteristics |

|-------|-----|-----|-----------------|

|-------|-----|-----|-----------------|

| Symbol            | Parameter                  | Conditions                                  | Min                | Тур | Max       | Unit |

|-------------------|----------------------------|---------------------------------------------|--------------------|-----|-----------|------|

| V <sub>DDA</sub>  | Power supply               | V <sub>DDA</sub> –V <sub>REF+</sub> < 1.2 V | 1.7 <sup>(1)</sup> | -   | 3.6       | V    |

| V <sub>REF+</sub> | Positive reference voltage | VDDA VREF+ VI.2 V                           | 1.7 <sup>(1)</sup> | -   | $V_{DDA}$ | V    |

| V <sub>REF-</sub> | Negative reference voltage | -                                           | -                  | 0   | -         | V    |

| Symbol                            | Parameter               | Conditions | Min | Тур | Мах | Unit   |

|-----------------------------------|-------------------------|------------|-----|-----|-----|--------|

| T <sub>Coeff</sub> <sup>(2)</sup> | Temperature coefficient | -          | -   | 30  | 50  | ppm/°C |

| t <sub>START</sub> <sup>(2)</sup> | Startup time            | -          | -   | 6   | 10  | μs     |

Table 71. internal reference voltage (continued)

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

#### Table 72. Internal reference voltage calibration values

| Symbol                 | Parameter                                                             | Memory address            |

|------------------------|-----------------------------------------------------------------------|---------------------------|

| V <sub>REFIN_CAL</sub> | Raw data acquired at temperature of 30 $^\circ\text{C}$ V_DDA = 3.3 V | 0x1FF0 F44A - 0x1FF0 F44B |

#### 5.3.25 DAC electrical characteristics

| Symbol                            | Parameter                                                | Min                | Тур | Max                         | Unit | Comments                                                                                                                |

|-----------------------------------|----------------------------------------------------------|--------------------|-----|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                  | Analog supply voltage                                    | 1.7 <sup>(1)</sup> | -   | 3.6                         | V    | -                                                                                                                       |

| V <sub>REF+</sub>                 | Reference supply voltage                                 | 1.7 <sup>(1)</sup> | -   | 3.6                         | V    | V <sub>REF+</sub> ≤V <sub>DDA</sub>                                                                                     |

| V <sub>SSA</sub>                  | Ground                                                   | 0                  | -   | 0                           | V    | -                                                                                                                       |

| R <sub>LOAD</sub> <sup>(2)</sup>  | Resistive load with buffer ON                            | 5                  | -   | -                           | kΩ   | -                                                                                                                       |

| R <sub>0</sub> <sup>(2)</sup>     | Impedance output with buffer<br>OFF                      | -                  | -   | 15                          | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$ |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                          | -                  | -   | 50                          | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT voltage with buffer ON                     | 0.2                | -   | -                           | V    | It gives the maximum output excursion of the DAC.<br>It corresponds to 12-bit input code                                |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT voltage<br>with buffer ON                 | -                  | -   | V <sub>DDA</sub> -<br>0.2   | V    | (0x0E0) to (0xF1C) at $V_{REF+}$ = 3.6 V and<br>(0x1C7) to (0xE38) at $V_{REF+}$ = 1.7 V                                |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT voltage<br>with buffer OFF                 | -                  | 0.5 | -                           | mV   | It gives the maximum output excursion of                                                                                |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT voltage<br>with buffer OFF                | -                  | -   | V <sub>REF+</sub> –<br>1LSB | V    | the DAC.                                                                                                                |

| I <sub>VREF+</sub> <sup>(4)</sup> | DAC DC V <sub>REF</sub> current consumption in guiescent | -                  | 170 | 240                         | μA   | With no load, worst code (0x800) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs            |

| VREF+`´                           | mode (Standby mode)                                      | -                  | 50  | 75                          | μΑ   | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs            |

#### Table 73. DAC characteristics

#### USB OTG full speed (FS) characteristics

This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol                              | Parameter                                   | Мах | Unit |

|-------------------------------------|---------------------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG full speed transceiver startup time | 1   | μs   |

#### Table 79. USB OTG full speed startup time

1. Guaranteed by design.

| Syn             | nbol                                                       | Parameter                                                 | Conditions                                                     | Min.<br>(1)        | Тур. | Max.<br>(1) | Unit |

|-----------------|------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------|--------------------|------|-------------|------|

|                 | V <sub>DDUSB</sub>                                         | USB OTG full speed<br>transceiver operating<br>voltage    | -                                                              | 3.0 <sup>(2)</sup> | -    | 3.6         | V    |

| Input<br>levels | V <sub>DI</sub> <sup>(3)</sup>                             | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                               | 0.2                | -    | -           |      |

| levels          | V <sub>CM</sub> <sup>(3)</sup>                             | Differential common mode range                            | Includes V <sub>DI</sub> range                                 | 0.8                | -    | 2.5         | V    |

|                 | $V_{SE}^{(3)}$                                             | Single ended receiver threshold                           | -                                                              | 1.3                | -    | 2.0         |      |

| Output          | V <sub>OL</sub>                                            | Static output level low                                   | ${\sf R}_{\sf L}$ of 1.5 k\Omega to 3.6 ${\sf V}^{(4)}$        | -                  | -    | 0.3         | v    |

| levels          | V <sub>OH</sub>                                            | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}^{(4)}$ | 2.8                | -    | 3.6         | v    |

|                 |                                                            | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V <sub>IN</sub> = V <sub>DD</sub>                              | 17                 | 21   | 24          |      |

| R <sub>PD</sub> | PD                                                         | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | VIN - VDD                                                      | 0.65               | 1.1  | 2.0         | kΩ   |

|                 |                                                            | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP)                      | V <sub>IN</sub> = V <sub>SS</sub>                              | 1.5                | 1.8  | 2.1         |      |

| R               | R <sub>PU</sub> PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS) |                                                           | V <sub>IN</sub> = V <sub>SS</sub>                              | 0.25               | 0.37 | 0.55        |      |

#### Table 80. USB OTG full speed DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The USB OTG full speed transceiver functionality is ensured down to 2.7 V but not the full USB full speed electrical characteristics which are degraded in the 2.7-to-3.0 V V<sub>DDUSB</sub> voltage range.

- 3. Guaranteed by design.

- 4.  $R_L$  is the load connected on the USB OTG full speed drivers.

Note:

When VBUS sensing feature is enabled, PA9 and PB13 should be left at their default state (floating input), not as alternate function. A typical 200  $\mu$ A current consumption of the sensing block (current to voltage conversion to determine the different sessions) can be observed on PA9 and PB13 when the feature is enabled.

| Symbol                  | Parameter                                                                 |                                        | Min    | Тур | Мах    | Unit |  |  |

|-------------------------|---------------------------------------------------------------------------|----------------------------------------|--------|-----|--------|------|--|--|

| -                       | f <sub>HCLK</sub> value to guarantee proper operation of USB HS interface |                                        | 30     | -   | -      | MHz  |  |  |

| F <sub>START_8BIT</sub> | Frequency (first transition)                                              | 8-bit ±10%                             | 54     | 60  | 66     | MHz  |  |  |

| F <sub>STEADY</sub>     | Frequency (steady state) ±500                                             | uency (steady state) ±500 ppm          |        | 60  | 60.03  | MHz  |  |  |

| D <sub>START_8BIT</sub> | Duty cycle (first transition)                                             | ty cycle (first transition) 8-bit ±10% |        | 50  | 60     | %    |  |  |

| D <sub>STEADY</sub>     | Duty cycle (steady state) ±500                                            | ppm                                    | 49.975 | 50  | 50.025 | %    |  |  |

| t <sub>STEADY</sub>     | Time to reach the steady state duty cycle after the first transiti        |                                        | -      | -   | 1.4    | ms   |  |  |

| t <sub>START_DEV</sub>  | Clock startup time after the                                              | Peripheral                             | -      | -   | 5.6    | me   |  |  |

| t <sub>START_HOST</sub> | de-assertion of SuspendM                                                  | Host                                   | -      | -   | -      | ms   |  |  |

| t <sub>PREP</sub>       | PHY preparation time after the<br>of the input clock                      | first transition                       | -      | -   | -      | μs   |  |  |

| Table 83. USB HS | clock timina | parameters <sup>(1)</sup> |

|------------------|--------------|---------------------------|

|------------------|--------------|---------------------------|

1. Guaranteed by design.

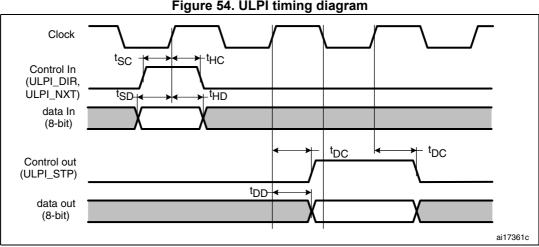

#### Figure 54. ULPI timing diagram

| Symbol                    | Parameter                                               | Min                     | Max                     | Unit |

|---------------------------|---------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                         | 3T <sub>HCLK</sub> -0.5 | 3T <sub>HCLK</sub> +1.5 |      |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low                              | 2T <sub>HCLK</sub> -1   | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>tw(NOE)</sub>      | FMC_NOE low time                                        | T <sub>HCLK</sub> -0.5  | T <sub>HCLK</sub> +0.5  |      |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time                   | 0                       | -                       |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                              | -                       | 0.5                     |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                             | 0                       | 0.5                     |      |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                       | T <sub>HCLK</sub> -0.5  | T <sub>HCLK</sub> +1.5  |      |

| t <sub>h(AD_NADV)</sub>   | FMC_AD(address) valid hold time after<br>FMC_NADV high) | 0                       | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high                    | T <sub>HCLK</sub> -0.5  | -                       |      |

| t <sub>h(BL_NOE)</sub>    | FMC_BL time after FMC_NOE high                          | 0                       | -                       |      |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid                             | -                       | 0.5                     |      |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time                         | T <sub>HCLK</sub> -2    | -                       |      |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOE high setup time                         | T <sub>HCLK</sub> -2    | -                       |      |

| t <sub>h(Data_NE)</sub>   | Data hold time after FMC_NEx high                       | 0                       | -                       |      |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FMC_NOE high                       | 0                       | -                       |      |

| Table 92. Asynchronous multiplexed PSRAM/NOR read timings <sup>(1)</sup> | Table 92. As | vnchronous mult | iplexed PSRAM/NO | R read timings <sup>(1)</sup> |

|--------------------------------------------------------------------------|--------------|-----------------|------------------|-------------------------------|

|--------------------------------------------------------------------------|--------------|-----------------|------------------|-------------------------------|

1. Guaranteed by characterization results.

| Symbol                    | Parameter                                 | Min                     | Мах                   | Unit |

|---------------------------|-------------------------------------------|-------------------------|-----------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> -1   | 8T <sub>HCLK</sub> +2 |      |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                          | 5T <sub>HCLK</sub> -1   | 5T <sub>HCLK</sub> +1 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 5T <sub>HCLK</sub> +1.5 | -                     |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +1   | -                     |      |

1. Guaranteed by characterization results.

1. Guaranteed by characterization results.

| Symbol                    | Parameter                                 | Min                     | Max                     | Unit |  |  |

|---------------------------|-------------------------------------------|-------------------------|-------------------------|------|--|--|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 9T <sub>HCLK</sub>      | 9T <sub>HCLK</sub> +1.5 |      |  |  |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 7T <sub>HCLK</sub> –0.5 | 7T <sub>HCLK</sub> +0.5 | ns   |  |  |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> +2   | -                       |      |  |  |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4Т <sub>НСLК</sub> –1   | -                       |      |  |  |

1. Guaranteed by characterization results.

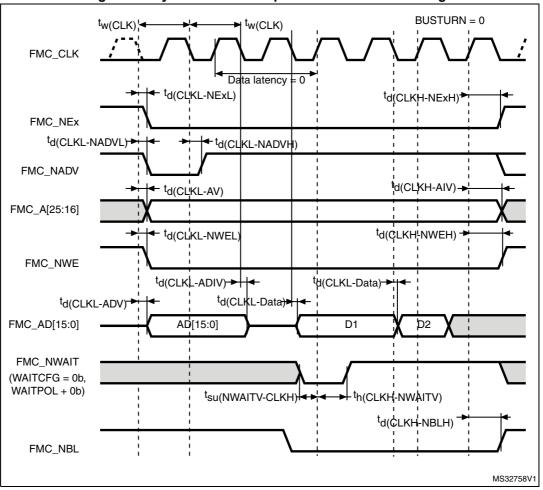

#### Synchronous waveforms and timings

*Figure 62* through *Figure 65* represent synchronous waveforms and *Table 96* through *Table 99* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- BurstAccessMode = FMC\_BurstAccessMode\_Enable;

- MemoryType = FMC\_MemoryType\_CRAM;

- WriteBurst = FMC\_WriteBurst\_Enable;

- CLKDivision = 1;

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

- CL = 30 pF on data and address lines. CL = 10 pF on FMC\_CLK unless otherwise specified.

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

- For 2.7 V $\leq$ V<sub>DD</sub> $\leq$ 3.6 V, maximum FMC\_CLK = 108 MHz at CL=20 pF or 90 MHz at CL=30 pF (on FMC\_CLK).

- For 1.71 V $\leq$ V<sub>DD</sub><2.7 V, maximum FMC\_CLK = 70 MHz at CL=10 pF (on FMC\_CLK).

Figure 63. Synchronous multiplexed PSRAM write timings

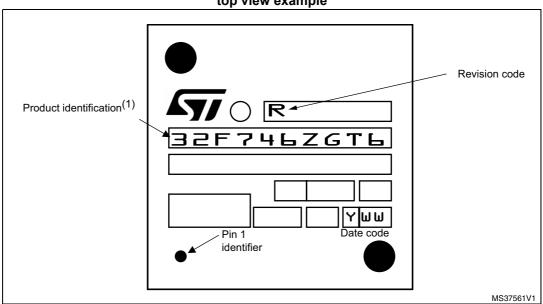

#### Marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 90. LQFP144, 20 x 20mm, 144-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 6.5 LQFP176, 24 x 24 mm low-profile quad flat package information

C Seating plane 0.25 mm gauge plane A1 HD 11 PIN 1 D **IDENTIFICATION** b ZE Е HE е ZD b 1T\_ME\_V2

Figure 91. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package outline

1. Drawing is not to scale.

## Table 118. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat packagemechanical data

| Symbol   | millimeters |     |        | inches <sup>(1)</sup> |     |        |  |

|----------|-------------|-----|--------|-----------------------|-----|--------|--|

| Symbol - | Min         | Тур | Max    | Min                   | Тур | Max    |  |

| A        | -           | -   | 1.600  | -                     | -   | 0.0630 |  |

| A1       | 0.050       | -   | 0.150  | 0.0020                | -   | 0.0059 |  |

| A2       | 1.350       | -   | 1.450  | 0.0531                | -   | 0.0060 |  |

| b        | 0.170       | -   | 0.270  | 0.0067                | -   | 0.0106 |  |

| С        | 0.090       | -   | 0.200  | 0.0035                | -   | 0.0079 |  |

| D        | 23.900      | -   | 24.100 | 0.9409                | -   | 0.9488 |  |

## 6.6 LQFP208, 28 x 28 mm low-profile quad flat package information

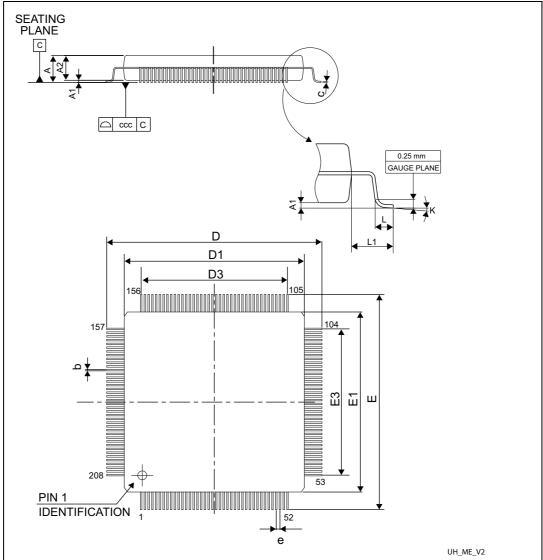

Figure 94. LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 119. LQFP208, 2 | 28 x 28 mm, 208-pin low-profile quad flat package |

|-----------------------|---------------------------------------------------|

|                       | mechanical data                                   |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| A      | -           | -     | 1.600 |                       | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

DocID027590 Rev 4