Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 168                                                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                                                       |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320K x 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                      |

| Mounting Type              | Surface Mount                                                                                          |

| Package / Case             | 208-LQFP                                                                                               |

| Supplier Device Package    | 208-LQFP (28x28)                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f746bet6                                  |

|                            |                                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Figure 42.<br>Figure 43. | Typical connection diagram using the ADC<br>Power supply and reference decoupling ( $V_{REF+}$ not connected to $V_{DDA}$ ) | 150 |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 44.<br>Figure 45. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )                                    |     |

| Figure 46.               | SPI timing diagram - slave mode and CPHA = 0                                                                                |     |

| Figure 47.               | SPI timing diagram - slave mode and CPHA = 1                                                                                |     |

| Figure 48.               | SPI timing diagram - master mode                                                                                            |     |

| Figure 49.               | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>                                                     |     |

| Figure 50.               | $I^2S$ master timing diagram (Philips protocol) <sup>(1)</sup>                                                              | 160 |

| Figure 51.               | SAI master timing waveforms                                                                                                 |     |

| Figure 52.               | SAI slave timing waveforms                                                                                                  |     |

| Figure 53.               | USB OTG full speed timings: definition of data signal rise and fall time                                                    |     |

| Figure 54.               | ULPI timing diagram                                                                                                         |     |

| Figure 55.               | Ethernet SMI timing diagram                                                                                                 |     |

| Figure 56.               | Ethernet RMII timing diagram                                                                                                |     |

| Figure 57.               | Ethernet MII timing diagram                                                                                                 |     |

| Figure 58.               | Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms                                                                  |     |

| Figure 59.               | Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms                                                                 |     |

| Figure 60.               | Asynchronous multiplexed PSRAM/NOR read waveforms.                                                                          |     |

| Figure 61.               | Asynchronous multiplexed PSRAM/NOR write waveforms                                                                          |     |

| Figure 62.               | Synchronous multiplexed NOR/PSRAM read timings                                                                              |     |

| Figure 63.               | Synchronous multiplexed PSRAM write timings                                                                                 |     |

| Figure 64.               | Synchronous non-multiplexed NOR/PSRAM read timings                                                                          |     |

| Figure 65.               | Synchronous non-multiplexed PSRAM write timings                                                                             |     |

| Figure 66.               | NAND controller waveforms for read access                                                                                   |     |

| Figure 67.               | NAND controller waveforms for write access                                                                                  |     |

| Figure 68.               | NAND controller waveforms for common memory read access                                                                     |     |

| •                        | •                                                                                                                           |     |

| Figure 69.               | NAND controller waveforms for common memory write access                                                                    |     |

| Figure 70.               | SDRAM write access waveforms                                                                                                |     |

| Figure 71.               | Quad-SPI timing diagram - SDR mode.                                                                                         |     |

| Figure 72.               |                                                                                                                             |     |

| Figure 73.               | Quad-SPI timing diagram - DDR mode                                                                                          |     |

| Figure 74.<br>Figure 75. | DCMI timing diagram                                                                                                         |     |

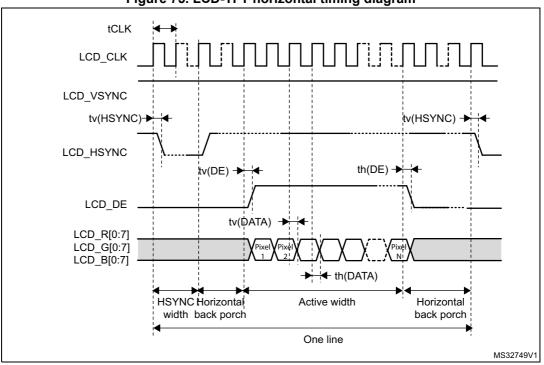

| •                        | LCD-TFT horizontal timing diagram                                                                                           |     |

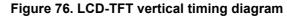

| Figure 76.               | LCD-TFT vertical timing diagram                                                                                             |     |

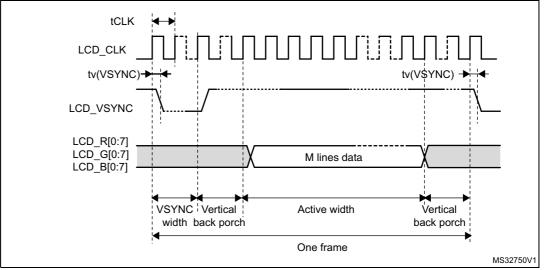

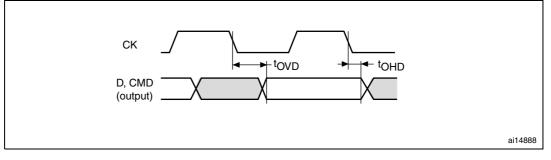

| Figure 77.               | SDIO high-speed mode                                                                                                        |     |

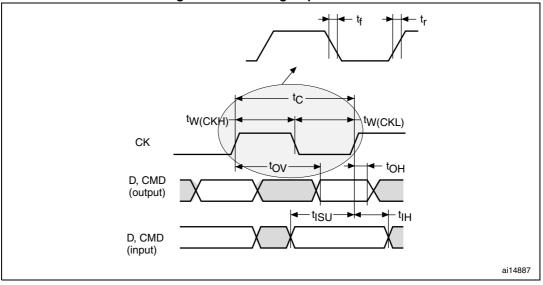

| Figure 78.               | SD default mode                                                                                                             |     |

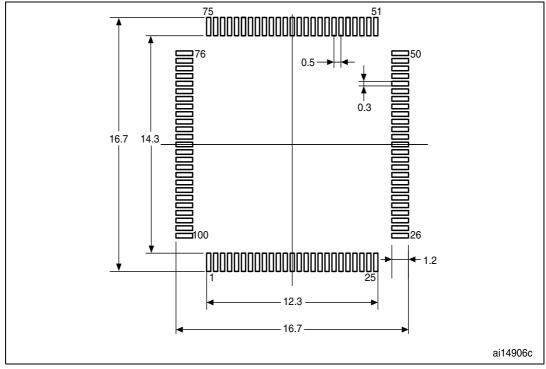

| Figure 79.               | LQFP100, 14 x 14 mm 100-pin low-profile quad flat package outline                                                           | 190 |

| Figure 80.               | LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package                                                                  | 100 |

|                          | recommended footprint.                                                                                                      | 198 |

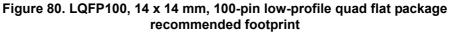

| Figure 81.               | LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package                                                                  | 400 |

|                          | top view example                                                                                                            | 198 |

| Figure 82.               | TFBGA100, 8 × 8 × 0.8 mm thin fine-pitch ball grid array                                                                    | 400 |

| <b>-</b> ; 00            | package outline.                                                                                                            | 199 |

| Figure 83.               | TFBGA100, 8 x 8 x 0.8 mm thin fine-pitch ball grid array                                                                    | ~~~ |

| <b>E</b> inen 04         | package recommended footprint                                                                                               | 200 |

| Figure 84.               | TFBGA100, 8 × 8 × 0.8mm thin fine-pitch ball grid array package                                                             | 004 |

|                          | top view example                                                                                                            | 201 |

| Figure 85.               | WLCSP143, 4.539x 5.849 mm, 0.4 mm pitch wafer level chip scale                                                              | 000 |

|                          | package outline                                                                                                             | 202 |

| Figure 86.               | WLCSP143, 4.539x 5.849 mm, 0.4 mm pitch wafer level chip scale                                                              | 000 |

|                          | package recommended footprint                                                                                               | 203 |

effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

# 2.9 Quad-SPI memory interface (QUADSPI)

All devices embed a Quad-SPI memory interface, which is a specialized communication interface targetting Single, Dual or Quad-SPI Flash memories. It can work in:

- Direct mode through registers.

- External flash status register polling mode.

- Memory mapped mode.

Up to 256 Mbytes external flash are memory mapped, supporting 8, 16 and 32-bit access. Code execution is supported.

The opcode and the frame format are fully programmable. Communication can be either in Single Data Rate or Dual Data Rate.

# 2.10 LCD-TFT controller

The LCD-TFT display controller provides a 24-bit parallel digital RGB (Red, Green, Blue) and delivers all signals to interface directly to a broad range of LCD and TFT panels up to XGA (1024x768) resolution with the following features:

- 2 displays layers with dedicated FIFO (64x32-bit)

- Color Look-Up table (CLUT) up to 256 colors (256x24-bit) per layer

- Up to 8 Input color formats selectable per layer

- Flexible blending between two layers using alpha value (per pixel or constant)

- Flexible programmable parameters for each layer

- Color keying (transparency color)

- Up to 4 programmable interrupt events.

# 2.11 Chrom-ART Accelerator<sup>™</sup> (DMA2D)

The Chrom-Art Accelerator <sup>™</sup> (DMA2D) is a graphic accelerator which offers advanced bit blitting, row data copy and pixel format conversion. It supports the following functions:

- Rectangle filling with a fixed color

- Rectangle copy

- Rectangle copy with pixel format conversion

- Rectangle composition with blending and pixel format conversion.

Various image format coding are supported, from indirect 4bpp color mode up to 32bpp direct color. It embeds dedicated memory to store color lookup tables.

An interrupt can be generated when an operation is complete or at a programmed watermark.

All the operations are fully automatized and are running independently from the CPU or the DMAs.

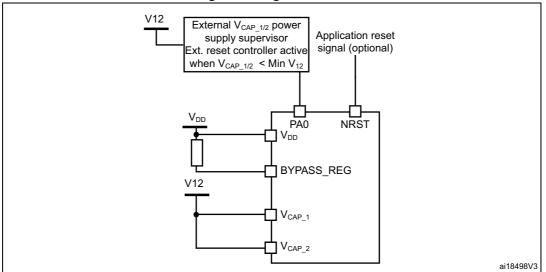

In regulator OFF mode, the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The over-drive and under-drive modes are not available.

- The Standby mode is not available.

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is faster than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach V<sub>12</sub> minimum value and until V<sub>DD</sub> reaches 1.7 V (see *Figure 9*).

- Otherwise, if the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is slower than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 10*).

- If  $V_{CAP_1}$  and  $V_{CAP_2}$  go below  $V_{12}$  minimum value and  $V_{DD}$  is higher than 1.7 V, then a reset must be asserted on PA0 pin.

Note: The minimum value of V<sub>12</sub> depends on the maximum frequency targeted in the application.

# 2.18.3 Regulator ON/OFF and internal reset ON/OFF availability

| Table 4. Regulator ON/OFF and Internal reset ON/OFF availability |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                             |                                         |                             |  |  |  |  |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------|-----------------------------|--|--|--|--|

| Package                                                          | Regulator ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Regulator OFF                               | Internal reset ON                       | Internal reset OFF          |  |  |  |  |

| LQFP100                                                          | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | No                                          | Yes                                     | No                          |  |  |  |  |

| LQFP144,<br>LQFP208                                              | The second secon | No                                          |                                         |                             |  |  |  |  |

| TFBGA100,<br>LQFP176,<br>WLCSP143,<br>UFBGA176,<br>TFBGA216      | Yes<br>BYPASS_REG set<br>to V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Yes<br>BYPASS_REG set<br>to V <sub>DD</sub> | Yes<br>PDR_ON set to<br>V <sub>DD</sub> | Yes<br>PDR_ON set to<br>VSS |  |  |  |  |

Table 4. Regulator ON/OFF and internal reset ON/OFF availability

# 2.19 Real-time clock (RTC), backup SRAM and backup registers

The RTC is an independent BCD timer/counter. It supports the following features:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28, 29 (leap year), 30, and 31 days of the month.

- Two programmable alarms.

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 0.95 ppm resolution, to compensate for quartz crystal inaccuracy.

- Three anti-tamper detection pins with programmable filter.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event, or by a switch to V<sub>BAT</sub> mode.

- 17-bit auto-reload wakeup timer (WUT) for periodic events with programmable resolution and period.

The RTC and the 32 backup registers are supplied through a switch that takes power either from the  $V_{\text{DD}}$  supply when present or from the  $V_{\text{BAT}}$  pin.

The backup registers are 32-bit registers used to store 128 bytes of user application data when VDD power is not present. They are not reset by a system or power reset, or when the device wakes up from Standby mode.

The RTC clock sources can be:

- A 32.768 kHz external crystal (LSE)

- An external resonator or oscillator(LSE)

- The internal low-power RC oscillator (LSI, with typical frequency of 32 kHz)

- The high-speed external clock (HSE) divided by 32.

# 2.22.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 and TIM8 support independent DMA request generation.

# 2.22.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F74xxx devices (see *Table 6* for differences).

#### • TIM2, TIM3, TIM4, TIM5

The STM32F74xxx include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### • TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

| features <sup>(1)</sup>               | USART1/2/3/6 | UART4/5/7/8 |

|---------------------------------------|--------------|-------------|

| Smartcard mode                        | Х            | -           |

| Single-wire half-duplex communication | Х            | Х           |

| IrDA SIR ENDEC block                  | Х            | Х           |

| LIN mode                              | Х            | Х           |

| Dual clock domain                     | Х            | Х           |

| Receiver timeout interrupt            | Х            | Х           |

| Modbus communication                  | Х            | Х           |

| Auto baud rate detection              | Х            | Х           |

| Driver Enable                         | Х            | х           |

Table 8. USART implementation (continued)

1. X: supported.

# 2.25 Serial peripheral interface (SPI)/inter- integrated sound interfaces (I2S)

The devices feature up to six SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1, SPI4, SPI5, and SPI6 can communicate at up to 50 Mbits/s, SPI2 and SPI3 can communicate at up to 25 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable from 4 to 16 bits. The SPI interfaces support NSS pulse mode, TI mode and Hardware CRC calculation. All SPIs can be served by the DMA controller.

Three standard  $I^2S$  interfaces (multiplexed with SPI1, SPI2 and SPI3) are available. They can be operated in master or slave mode, in simplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the  $I^2S$  interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx can be served by the DMA controller.

# 2.26 Serial audio interface (SAI)

The devices embed two serial audio interfaces.

The serial audio interface is based on two independent audio subblocks which can operate as transmitter or receiver with their FIFO. Many audio protocols are supported by each block: I2S standards, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF output, supporting audio sampling frequencies from 8 kHz up to 192 kHz. Both subblocks can be

configured in master or in slave mode.

In master mode, the master clock can be output to the external DAC/CODEC at 256 times of the sampling frequency.

The two sub-blocks can be configured in synchronous mode when full-duplex mode is required.

DocID027590 Rev 4

# 2.32 Controller area network (bxCAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one CAN is used). 256 bytes of SRAM are allocated for each CAN.

# 2.33 Universal serial bus on-the-go full-speed (OTG\_FS)

The device embeds an USB OTG full-speed device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 2.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator.

The major features are:

- Combined Rx and Tx FIFO size of 1.28 Kbytes with dynamic FIFO sizing

- Support of the session request protocol (SRP) and host negotiation protocol (HNP)

- 1 bidirectional control endpoint + 5 IN endpoints + 5 OUT endpoints

- 12 host channels with periodic OUT support

- Software configurable to OTG1.3 and OTG2.0 modes of operation

- USB 2.0 LPM (Link Power Management) support

- Internal FS OTG PHY support

- HNP/SNP/IP inside (no need for any external resistor)

For OTG/Host modes, a power switch is needed in case bus-powered devices are connected

# 2.34 Universal serial bus on-the-go high-speed (OTG\_HS)

The device embeds a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 2.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator.

| Table 10. STM32F745xx and STM32F746xx pin and ball definition (continued) |          |          |         |          |         |         |          |                                                            |          |               |       |                                                                                                                                                      |                         |

|---------------------------------------------------------------------------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|                                                                           |          | I        | Pin Nı  | umber    |         |         | -        |                                                            |          |               |       |                                                                                                                                                      |                         |

| LQFP100                                                                   | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                  | Additional<br>functions |

| -                                                                         | -        | -        | -       | -        | -       | 186     | D8       | PK3                                                        | I/O      | FT            | -     | LCD_B4, EVENTOUT                                                                                                                                     | -                       |

| -                                                                         | -        | -        | -       | -        | -       | 187     | D7       | PK4                                                        | I/O      | FT            | -     | LCD_B5, EVENTOUT                                                                                                                                     | -                       |

| -                                                                         | -        | -        | -       | -        | -       | 188     | C6       | PK5                                                        | I/O      | FT            | -     | LCD_B6, EVENTOUT                                                                                                                                     | -                       |

| -                                                                         | -        | -        | -       | -        | -       | 189     | C5       | PK6                                                        | I/O      | FT            | -     | LCD_B7, EVENTOUT                                                                                                                                     | -                       |

| -                                                                         | -        | -        | -       | -        | -       | 190     | C4       | PK7                                                        | I/O      | FT            | -     | LCD_DE, EVENTOUT                                                                                                                                     | -                       |

| -                                                                         | -        | A7       | 132     | В7       | 160     | 191     | В7       | PG15                                                       | I/O      | FT            | -     | USART6_CTS,<br>FMC_SDNCAS,<br>DCMI_D13, EVENTOUT                                                                                                     | -                       |

| 89                                                                        | A7       | B7       | 133     | A10      | 161     | 192     | A10      | PB3(JTD<br>O/TRAC<br>ESWO)                                 | I/O      | FT            | -     | JTDO/TRACESWO,<br>TIM2_CH2,<br>SPI1_SCK/I2S1_CK,<br>SPI3_SCK/I2S3_CK,<br>EVENTOUT                                                                    | -                       |

| 90                                                                        | A6       | C7       | 134     | A9       | 162     | 193     | A9       | PB4(NJT<br>RST)                                            | I/O      | FT            | -     | NJTRST, TIM3_CH1,<br>SPI1_MISO, SPI3_MISO,<br>SPI2_NSS/I2S2_WS,<br>EVENTOUT                                                                          | -                       |

| 91                                                                        | C5       | C8       | 135     | A6       | 163     | 194     | A8       | PB5                                                        | I/O      | FT            | -     | TIM3_CH2, I2C1_SMBA,<br>SPI1_MOSI/I2S1_SD,<br>SPI3_MOSI/I2S3_SD,<br>CAN2_RX,<br>OTG_HS_ULPI_D7,<br>ETH_PPS_OUT,<br>FMC_SDCKE1,<br>DCMI_D10, EVENTOUT | -                       |

| 92                                                                        | B5       | A8       | 136     | B6       | 164     | 195     | B6       | PB6                                                        | I/O      | FT            | -     | TIM4_CH1, HDMI-CEC,<br>I2C1_SCL, USART1_TX,<br>CAN2_TX,<br>QUADSPI_BK1_NCS,<br>FMC_SDNE1, DCMI_D5,<br>EVENTOUT                                       | -                       |

| 93                                                                        | A5       | В8       | 137     | В5       | 165     | 196     | B5       | PB7                                                        | I/O      | FT            | -     | TIM4_CH2, I2C1_SDA,<br>USART1_RX, FMC_NL,<br>DCMI_VSYNC,<br>EVENTOUT                                                                                 | -                       |

| 94                                                                        | D5       | C9       | 138     | D6       | 166     | 197     | E6       | BOOT                                                       | I        | В             | -     | -                                                                                                                                                    | VPP                     |

| Table 10. STM32F745xx and STM32F746xx pin and ball definition ( | continued) |

|-----------------------------------------------------------------|------------|

|                                                                 |            |

# Pinouts and pin description

|          |                    | IC pin definition | (continueu) | 1     |

|----------|--------------------|-------------------|-------------|-------|

| Pin name | NOR/PSRAM/SR<br>AM | NOR/PSRAM<br>Mux  | NAND16      | SDRAM |

| PE11     | D8                 | DA8               | D8          | D8    |

| PE12     | D9                 | DA9               | D9          | D9    |

| PE13     | D10                | DA10              | D10         | D10   |

| PE14     | D11                | DA11              | D11         | D11   |

| PE15     | D12                | DA12              | D12         | D12   |

| PD8      | D13                | DA13              | D13         | D13   |

| PD9      | D14                | DA14              | D14         | D14   |

| PD10     | D15                | DA15              | D15         | D15   |

| PH8      | D16                | -                 | -           | D16   |

| PH9      | D17                | -                 | -           | D17   |

| PH10     | D18                | -                 | -           | D18   |

| PH11     | D19                | -                 | -           | D19   |

| PH12     | D20                | -                 | -           | D20   |

| PH13     | D21                | -                 | -           | D21   |

| PH14     | D22                | -                 | -           | D22   |

| PH15     | D23                | -                 | -           | D23   |

| PI0      | D24                | -                 | -           | D24   |

| PI1      | D25                | -                 | -           | D25   |

| Pl2      | D26                | -                 | -           | D26   |

| PI3      | D27                | -                 | -           | D27   |

| Pl6      | D28                | -                 | -           | D28   |

| PI7      | D29                | -                 | -           | D29   |

| PI9      | D30                | -                 | -           | D30   |

| PI10     | D31                | -                 | -           | D31   |

| PD7      | NE1                | NE1               | -           | -     |

| PG9      | NE2                | NE2               | NCE         | -     |

| PG10     | NE3                | NE3               | -           | -     |

| PG11     | -                  | -                 | -           | -     |

| PG12     | NE4                | NE4               | -           | -     |

| PD3      | CLK                | CLK               | -           | -     |

| PD4      | NOE                | NOE               | NOE         | -     |

| PD5      | NWE                | NWE               | NWE         | -     |

| PD6      | NWAIT              | NWAIT             | NWAIT       | -     |

| PB7      | NADV               | NADV              | -           | -     |

|          |                    |                   |             |       |

Table 11. FMC pin definition (continued)

78/227

DocID027590 Rev 4

# Pinouts and pin description

STM32F745xx STM32F746xx

| Symbol | Parameter                         | Conditions |  |  |  |  |  |  |

|--------|-----------------------------------|------------|--|--|--|--|--|--|

| CEXT   | Capacitance of external capacitor | 2.2 µF     |  |  |  |  |  |  |

| ESR    | ESR of external capacitor         | < 2 Ω      |  |  |  |  |  |  |

#### Table 19. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

When bypassing the voltage regulator, the two 2.2 μF V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

## 5.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for T<sub>A</sub>.

#### Table 20. Operating conditions at power-up / power-down (regulator ON)

| Symbol | Parameter                      | Min | Мах | Unit  |

|--------|--------------------------------|-----|-----|-------|

| +      | V <sub>DD</sub> rise time rate | 20  | ~   | µs/V  |

| tvdd   | V <sub>DD</sub> fall time rate | 20  | ∞   | μ5/ ν |

# 5.3.4 Operating conditions at power-up / power-down (regulator OFF)

Subject to general operating conditions for  $T_A$ .

#### Table 21. Operating conditions at power-up / power-down (regulator OFF)<sup>(1)</sup>

| Symbol            | Parameter                                    | Conditions | Min | Max                                     | Unit |

|-------------------|----------------------------------------------|------------|-----|-----------------------------------------|------|

| t <sub>VDD</sub>  | V <sub>DD</sub> rise time rate               | Power-up   | 20  | ~                                       |      |

|                   | V <sub>DD</sub> fall time rate               | Power-down | 20  | ~                                       |      |

| 4                 | $V_{CAP\_1}$ and $V_{CAP\_2}$ rise time rate | Power-up   | 20  | ~                                       | µs/V |

| <sup>t</sup> VCAP | $V_{CAP\_1}$ and $V_{CAP\_2}$ fall time rate | Power-down | 20  | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |      |

1. To reset the internal logic at power-down, a reset must be applied on pin PA0 when  $V_{\text{DD}}$  reach below 1.08 V.

# 5.3.5 Reset and power control block characteristics

The parameters given in *Table 22* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

# 5.3.9 External clock source characteristics

#### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 56: I/O static characteristics*. However, the recommended clock input waveform is shown in *Figure 30*.

The characteristics given in *Table 37* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 17*.

| Symbol                                     | Parameter                                           | Conditions                       | Min                | Тур | Max                | Unit |

|--------------------------------------------|-----------------------------------------------------|----------------------------------|--------------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>                       | External user clock source frequency <sup>(1)</sup> |                                  | 1                  | -   | 50                 | MHz  |

| V <sub>HSEH</sub>                          | OSC_IN input pin high level voltage                 |                                  | 0.7V <sub>DD</sub> | -   | V <sub>DD</sub>    | V    |

| V <sub>HSEL</sub>                          | OSC_IN input pin low level voltage                  | -                                | $V_{SS}$           | -   | $0.3V_{\text{DD}}$ | v    |

| t <sub>w(HSE)</sub><br>t <sub>w(HSE)</sub> | OSC_IN high or low time <sup>(1)</sup>              |                                  | 5                  | -   | -                  | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub> | OSC_IN rise or fall time <sup>(1)</sup>             |                                  | -                  | -   | 10                 | 115  |

| C <sub>in(HSE)</sub>                       | OSC_IN input capacitance <sup>(1)</sup>             | -                                | -                  | 5   | -                  | pF   |

| DuCy <sub>(HSE)</sub>                      | Duty cycle                                          | -                                | 45                 | -   | 55                 | %    |

| ١L                                         | OSC_IN Input leakage current                        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -   | ±1                 | μA   |

Table 37. High-speed external user clock characteristics

1. Guaranteed by design.

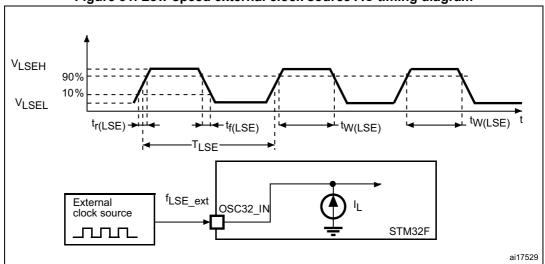

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard I/O. The external clock signal has to respect the *Table 56: I/O static characteristics*. However, the recommended clock input waveform is shown in *Figure 31*.

The characteristics given in *Table 38* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 17*.

Figure 31. Low-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 39*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                            | Parameter                               | Conditions                                                            | Min   | Тур | Мах | Unit |  |  |  |  |

|-----------------------------------|-----------------------------------------|-----------------------------------------------------------------------|-------|-----|-----|------|--|--|--|--|

| f <sub>OSC_IN</sub>               | Oscillator frequency                    | -                                                                     | 4     | -   | 26  | MHz  |  |  |  |  |

| R <sub>F</sub>                    | Feedback resistor                       | -                                                                     | -     | 200 | -   | kΩ   |  |  |  |  |

| 1                                 |                                         | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =5 pF@25 MHz  | -     | 450 | -   | μA   |  |  |  |  |

| IDD                               | HSE current consumption                 | V <sub>DD</sub> =3.3 V,<br>ESR= 30 Ω,<br>C <sub>L</sub> =10 pF@25 MHz | -     | 530 | -   | μΑ   |  |  |  |  |

| ACC <sub>HSE</sub> <sup>(2)</sup> | HSE accuracy                            | -                                                                     | - 500 | -   | 500 | ppm  |  |  |  |  |

| G <sub>m</sub> _crit_max          | Maximum critical crystal g <sub>m</sub> | Startup                                                               | -     | -   | 1   | mA/V |  |  |  |  |

| $t_{SU(HSE}^{(3)}$                | Startup time                            | $V_{\text{DD}}$ is stabilized                                         | -     | 2   | -   | ms   |  |  |  |  |

| Table 39. | HSE 4-26 | MHz oscillator | characteristics <sup>(1)</sup> |

|-----------|----------|----------------|--------------------------------|

| 10010 00. |          |                | onuluotonotioo                 |

1. Guaranteed by design.

2. This parameter depends on the crystal used in the application. The minimum and maximum values must be respected to comply with USB standard specifications.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is based on characterization results. It is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

#### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*. All I/Os are CMOS and TTL compliant.

| Symbol                         | Parameter                                            | Conditions                                                                                     | Min                                 | Max                | Unit |

|--------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin              | CMOS port <sup>(2)</sup><br>I <sub>IO</sub> = +8 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V           | -                                   | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14 | CMOS port <sup>(2)</sup><br>$I_{IO} = -8 \text{ mA}$<br>2.7 V $\leq V_{DD} \leq 3.6 \text{ V}$ | V <sub>DD</sub> - 0.4               | -                  | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for PC14                   | CMOS port <sup>(2)</sup><br>I <sub>IO</sub> = -2 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V           | V <sub>DD</sub> - 0.4               | -                  |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin              | TTL port <sup>(2)</sup><br>I <sub>IO</sub> =+8mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V              | -                                   | 0.4                | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14 | TTL port <sup>(2)</sup><br>I <sub>IO</sub> =-8mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V              | 2.4                                 | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin              | I <sub>IO</sub> = +20 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V                                      | -                                   | 1.3 <sup>(4)</sup> | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14 | I <sub>IO</sub> = -20 mA<br>2.7 V ≤V <sub>DD</sub> ≤3.6 V                                      | V <sub>DD</sub> -1.3 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin              | I <sub>IO</sub> = +6 mA<br>1.8 V ≤V <sub>DD</sub> ≤3.6 V                                       | -                                   | 0.4 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14 | I <sub>IO</sub> = -6 mA<br>1.8 V ≤V <sub>DD</sub> ≤3.6 V                                       | V <sub>DD</sub> -0.4 <sup>(4)</sup> | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin              | I <sub>IO</sub> = +4 mA<br>1.7 V ≤V <sub>DD</sub> ≤3.6V                                        | -                                   | 0.4 <sup>(5)</sup> |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14 | I <sub>IO</sub> = -4 mA<br>1.7 V ≤V <sub>DD</sub> ≤3.6V                                        | V <sub>DD</sub> -0.4 <sup>(5)</sup> | -                  | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for PC14                   | I <sub>IO</sub> = -1 mA<br>1.7 V ≤V <sub>DD</sub> ≤3.6V                                        | V <sub>DD</sub> -0.4 <sup>(5)</sup> | -                  |      |

#### Table 57. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 15*. and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 15 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Based on characterization data.

5. Guaranteed by design.

| Symbol                    | Parameter                                               | Min                     | Max                     | Unit |

|---------------------------|---------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                         | 3T <sub>HCLK</sub> -0.5 | 3T <sub>HCLK</sub> +1.5 |      |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low                              | 2T <sub>HCLK</sub> -1   | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>tw(NOE)</sub>      | FMC_NOE low time                                        | T <sub>HCLK</sub> -0.5  | T <sub>HCLK</sub> +0.5  |      |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time                   | 0                       | -                       |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                              | -                       | 0.5                     |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                             | 0                       | 0.5                     |      |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                       | T <sub>HCLK</sub> -0.5  | T <sub>HCLK</sub> +1.5  |      |

| t <sub>h(AD_NADV)</sub>   | FMC_AD(address) valid hold time after<br>FMC_NADV high) | 0                       | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high                    | T <sub>HCLK</sub> -0.5  | -                       |      |

| t <sub>h(BL_NOE)</sub>    | FMC_BL time after FMC_NOE high                          | 0                       | -                       |      |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid                             | -                       | 0.5                     |      |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time                         | T <sub>HCLK</sub> -2    | -                       |      |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOE high setup time                         | T <sub>HCLK</sub> -2    | -                       |      |

| t <sub>h(Data_NE)</sub>   | Data hold time after FMC_NEx high                       | 0                       | -                       |      |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FMC_NOE high                       | 0                       | -                       |      |

| Table 92. Asynchronous multiplexed PSRAM/NOR read timings <sup>(1)</sup> | Table 92. As | vnchronous mult | iplexed PSRAM/NO | R read timings <sup>(1)</sup> |

|--------------------------------------------------------------------------|--------------|-----------------|------------------|-------------------------------|

|--------------------------------------------------------------------------|--------------|-----------------|------------------|-------------------------------|

1. Guaranteed by characterization results.

| Symbol                    | Parameter                                 | Min                     | Min Max               |    |

|---------------------------|-------------------------------------------|-------------------------|-----------------------|----|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> -1   | 8T <sub>HCLK</sub> +2 |    |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                          | 5T <sub>HCLK</sub> -1   | 5T <sub>HCLK</sub> +1 | ns |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 5T <sub>HCLK</sub> +1.5 | -                     |    |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +1   | -                     |    |

1. Guaranteed by characterization results.

Figure 75. LCD-TFT horizontal timing diagram

## 5.3.31 SD/SDIO MMC card host interface (SDMMC) characteristics

Unless otherwise specified, the parameters given in *Table 110* for the SDIO/MMC interface are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 5.3.17: I/O port characteristics for more details on the input/output characteristics.

Figure 77. SDIO high-speed mode

1. Dimensions are expressed in millimeters.

#### Marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 81. LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

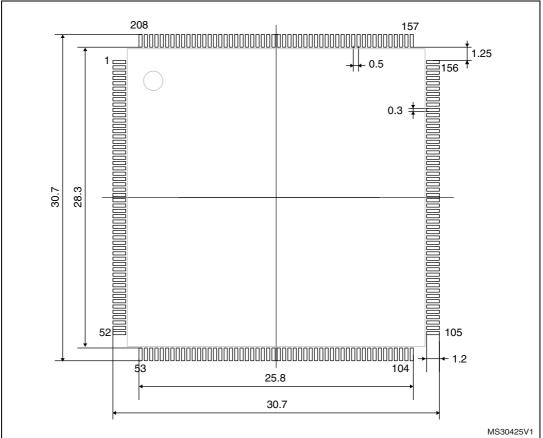

Figure 95. LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID027590 Rev 4