Welcome to E-XFL.COM

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 140                                                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                                                       |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320K x 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                      |

| Mounting Type              | Surface Mount                                                                                          |

| Package / Case             | 176-UFBGA                                                                                              |

| Supplier Device Package    | 176-UFBGA (10x10)                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f746iek6                                  |

|                            |                                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Periph                       | orals                  | STM32E745Vx | STM32E746Vx           | STM32F7457x     | STM32F7467x   | STM32E745Ix         | STM32E746ly          | STM32F745Bx            | STM32F746By    | STM32F745Nx    | STM32F746N  |  |  |

|------------------------------|------------------------|-------------|-----------------------|-----------------|---------------|---------------------|----------------------|------------------------|----------------|----------------|-------------|--|--|

| renpi                        |                        |             |                       | 01111021 / 402X | 51W3217402X   | 01WJ2174JIX         |                      |                        | 01111321 740DX | 51111521 745NX | 01100217400 |  |  |

|                              | SPI / I <sup>2</sup> S | 4/3 (sin    | nplex) <sup>(2)</sup> |                 |               |                     | 6/3 (si              | implex) <sup>(2)</sup> |                |                |             |  |  |

|                              | l <sup>2</sup> C       |             |                       |                 |               |                     | 4                    |                        |                |                |             |  |  |

|                              | USART/<br>UART         |             |                       |                 |               | 4                   | 1/4                  |                        |                |                |             |  |  |

| Communication                | USB OTG<br>FS          |             |                       |                 |               | Y                   | ′es                  |                        |                |                |             |  |  |

| interfaces                   | USB OTG<br>HS          |             |                       |                 |               |                     |                      |                        |                |                |             |  |  |

|                              | CAN                    |             |                       |                 |               |                     | 2                    |                        |                |                |             |  |  |

|                              | SAI                    |             | 2                     |                 |               |                     |                      |                        |                |                |             |  |  |

|                              | SPDIFRX                |             | 4 inputs              |                 |               |                     |                      |                        |                |                |             |  |  |

|                              | SDMMC                  |             | Yes                   |                 |               |                     |                      |                        |                |                |             |  |  |

| Camera interfac              | e                      |             | Yes                   |                 |               |                     |                      |                        |                |                |             |  |  |

| LCD-TFT                      |                        | No          | Yes                   | No              | Yes           | No                  | Yes                  | No                     | Yes            | No             | Yes         |  |  |

| Chrom-ART Acc<br>(DMA2D)     | celerator™             |             |                       |                 |               | Ŷ                   | ′es                  |                        |                |                |             |  |  |

| GPIOs                        |                        | 8           | 2                     | 1               | 14            | 14                  | 40                   |                        | 1              | 68             |             |  |  |

| 12-bit ADC                   |                        |             |                       |                 |               |                     | 3                    |                        |                |                |             |  |  |

| Number of chan               | inels                  | 1           | 6                     |                 |               |                     |                      | 24                     |                |                |             |  |  |

| 12-bit DAC<br>Number of chan | nels                   |             |                       | I               |               |                     | ′es<br>2             |                        |                |                |             |  |  |

| Maximum CPU                  | frequency              |             |                       |                 |               | 216                 | MHz <sup>(3)</sup>   |                        |                |                |             |  |  |

| Operating voltage            | je                     |             |                       |                 |               | 1.7 to              | 3.6 V <sup>(4)</sup> |                        |                |                |             |  |  |

|                              |                        |             |                       |                 | Ambient t     | emperatures: -4     | 0 to +85 °C /–40     | to +105 °C             |                |                |             |  |  |

| Operating temp               | eratures               |             |                       |                 | Ju            | unction temperation | ure: -40 to + 125    | 5 °C                   |                |                |             |  |  |

| Package                      |                        | LQF<br>TFB0 | P100<br>GA100         | WLC:<br>LQF     | SP143<br>P144 | UFBC                |                      | LQF                    | P208           | TFBG           | A216        |  |  |

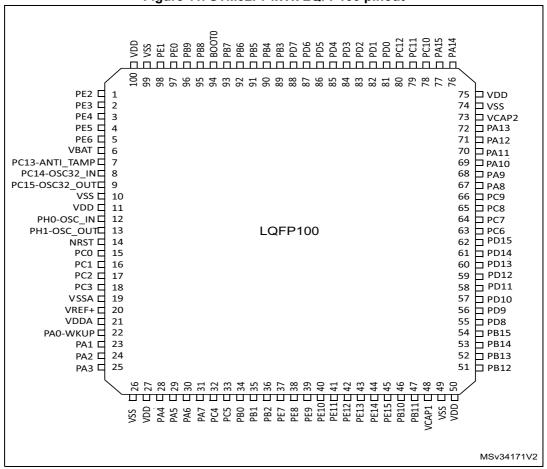

1. For the LQFP100 package, only FMC Bank1 is available. Bank1 can only support a multiplexed NOR/PSRAM memory using the NE1 Chip Select.

2. The SPI1, SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the I2S audio mode.

3. 216 MHz maximum frequency for -40°C to + 85°C ambient temperature range (200 MHz maximum frequency for -40°C to + 105°C ambient temperature range).

4. VDD/VDDA minimum value of 1.7 V is obtained when the internal reset is OFF (refer to Section 2.17.2: Internal reset OFF).

STM32F745xx STM32F746xx

effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

## 2.9 Quad-SPI memory interface (QUADSPI)

All devices embed a Quad-SPI memory interface, which is a specialized communication interface targetting Single, Dual or Quad-SPI Flash memories. It can work in:

- Direct mode through registers.

- External flash status register polling mode.

- Memory mapped mode.

Up to 256 Mbytes external flash are memory mapped, supporting 8, 16 and 32-bit access. Code execution is supported.

The opcode and the frame format are fully programmable. Communication can be either in Single Data Rate or Dual Data Rate.

## 2.10 LCD-TFT controller

The LCD-TFT display controller provides a 24-bit parallel digital RGB (Red, Green, Blue) and delivers all signals to interface directly to a broad range of LCD and TFT panels up to XGA (1024x768) resolution with the following features:

- 2 displays layers with dedicated FIFO (64x32-bit)

- Color Look-Up table (CLUT) up to 256 colors (256x24-bit) per layer

- Up to 8 Input color formats selectable per layer

- Flexible blending between two layers using alpha value (per pixel or constant)

- Flexible programmable parameters for each layer

- Color keying (transparency color)

- Up to 4 programmable interrupt events.

## 2.11 Chrom-ART Accelerator<sup>™</sup> (DMA2D)

The Chrom-Art Accelerator <sup>™</sup> (DMA2D) is a graphic accelerator which offers advanced bit blitting, row data copy and pixel format conversion. It supports the following functions:

- Rectangle filling with a fixed color

- Rectangle copy

- Rectangle copy with pixel format conversion

- Rectangle composition with blending and pixel format conversion.

Various image format coding are supported, from indirect 4bpp color mode up to 32bpp direct color. It embeds dedicated memory to store color lookup tables.

An interrupt can be generated when an operation is complete or at a programmed watermark.

All the operations are fully automatized and are running independently from the CPU or the DMAs.

#### STM32F745xx STM32F746xx

| Timer<br>type        | Timer           | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                      | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complem<br>entary<br>output | Max<br>interfac<br>e clock<br>(MHz) | Max<br>timer<br>clock<br>(MHz) <sup>(1)</sup> |

|----------------------|-----------------|-----------------------|-------------------------|------------------------------------------|------------------------------|---------------------------------|-----------------------------|-------------------------------------|-----------------------------------------------|

| Advance<br>d-control | TIM1,<br>TIM8   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                         | 108                                 | 216                                           |

|                      | TIM2,<br>TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                          | 54                                  | 108/216                                       |

|                      | TIM3,<br>TIM4   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                          | 54                                  | 108/216                                       |

| General              | TIM9            | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 2                               | No                          | 108                                 | 216                                           |

| purpose              | TIM10,<br>TIM11 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 1                               | No                          | 108                                 | 216                                           |

|                      | TIM12           | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 2                               | No                          | 54                                  | 108/216                                       |

|                      | TIM13,<br>TIM14 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 1                               | No                          | 54                                  | 108/216                                       |

| Basic                | TIM6,<br>TIM7   | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                          | 54                                  | 108/216                                       |

| Table 6. | Timer | feature  | comparison |

|----------|-------|----------|------------|

|          |       | ioutai o | oompanoon  |

1. The maximum timer clock is either 108 or 216 MHz depending on TIMPRE bit configuration in the RCC\_DCKCFGR register.

# 2.23 Inter-integrated circuit interface (I<sup>2</sup>C)

The device embeds 4 I2C. Refer to *Table 7: I2C implementation* for the features implementation.

The I<sup>2</sup>C bus interface handles communication between the microcontroller and the serial I<sup>2</sup>C bus. It controls all I<sup>2</sup>C bus-specific sequencing, protocol, arbitration and timing.

The I2C peripheral supports:

- I<sup>2</sup>C-bus specification and user manual rev. 5 compatibility:

- Slave and master modes, multimaster capability

- Standard-mode (Sm), with a bitrate up to 100 kbit/s

- Fast-mode (Fm), with a bitrate up to 400 kbit/s

- 7-bit and 10-bit addressing mode, multiple 7-bit slave addresses

- Programmable setup and hold times

- Optional clock stretching

- System Management Bus (SMBus) specification rev 2.0 compatibility:

- Hardware PEC (Packet Error Checking) generation and verification with ACK control

- Address resolution protocol (ARP) support

- SMBus alert

- Power System Management Protocol (PMBus<sup>TM</sup>) specification rev 1.1 compatibility

- Independent clock: a choice of independent clock sources allowing the I2C communication speed to be independent from the PCLK reprogramming.

- Programmable analog and digital noise filters

- 1-byte buffer with DMA capability

#### Table 7. I2C implementation

| I2C features <sup>(1)</sup>                   | I2C1 | 12C2 | 12C3 | I2C4 |

|-----------------------------------------------|------|------|------|------|

| Standard-mode (up to 100 kbit/s)              | Х    | Х    | Х    | Х    |

| Fast-mode (up to 400 kbit/s)                  | Х    | Х    | Х    | Х    |

| Programmable analog and digital noise filters | Х    | Х    | Х    | Х    |

| SMBus/PMBus hardware support                  | Х    | Х    | Х    | Х    |

| Independent clock                             | Х    | Х    | Х    | Х    |

1. X: supported

SAI1 and SAI2 can be served by the DMA controller

### 2.27 SPDIFRX Receiver Interface (SPDIFRX)

The SPDIFRX peripheral, is designed to receive an S/PDIF flow compliant with IEC-60958 and IEC-61937. These standards support simple stereo streams up to high sample rate, and compressed multi-channel surround sound, such as those defined by Dolby or DTS (up to 5.1).

The main features of the SPDIFRX are the following:

- Up to 4 inputs available

- Automatic symbol rate detection

- Maximum symbol rate: 12.288 MHz

- Stereo stream from 32 to 192 kHz supported

- Supports Audio IEC-60958 and IEC-61937, consumer applications

- Parity bit management

- Communication using DMA for audio samples

- Communication using DMA for control and user channel information

- Interrupt capabilities

The SPDIFRX receiver provides all the necessary features to detect the symbol rate, and decode the incoming data stream. The user can select the wanted SPDIF input, and when a valid signal will be available, the SPDIFRX will re-sample the incoming signal, decode the manchester stream, recognize frames, sub-frames and blocks elements. It delivers to the CPU decoded data, and associated status flags.

The SPDIFRX also offers a signal named spdif\_frame\_sync, which toggles at the S/PDIF sub-frame rate that will be used to compute the exact sample rate for clock drift algorithms.

#### 2.28 Audio PLL (PLLI2S)

The devices feature an additional dedicated PLL for audio I<sup>2</sup>S and SAI applications. It allows to achieve error-free I<sup>2</sup>S sampling clock accuracy without compromising on the CPU performance, while using USB peripherals.

The PLLI2S configuration can be modified to manage an I<sup>2</sup>S/SAI sample rate change without disabling the main PLL (PLL) used for CPU, USB and Ethernet interfaces.

The audio PLL can be programmed with very low error to obtain sampling rates ranging from 8 KHz to 192 KHz.

In addition to the audio PLL, a master clock input pin can be used to synchronize the I<sup>2</sup>S/SAI flow with an external PLL (or Codec output).

# 3 Pinouts and pin description

#### Figure 11. STM32F74xVx LQFP100 pinout

2. The above figure shows the package top view.

|         |          |          |         | umber    |         |         |          |                                                            |          |               |       | ball definition (continue                                                                                                              |                         |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|-------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                                                                    | Additional<br>functions |

| 31      | КЗ       | L8       | 43      | R3       | 53      | 56      | R3       | PA7                                                        | I/O      | FT            | (4)   | TIM1_CH1N, TIM3_CH2,<br>TIM8_CH1N,<br>SPI1_MOSI/I2S1_SD,<br>TIM14_CH1,<br>ETH_MII_RX_DV/ETH_R<br>MII_CRS_DV,<br>FMC_SDNWE,<br>EVENTOUT | ADC12_IN7               |

| 32      | G4       | M8       | 44      | N5       | 54      | 57      | N5       | PC4                                                        | I/O      | FT            | (4)   | I2S1_MCK,<br>SPDIFRX_IN2,<br>ETH_MII_RXD0/ETH_RM<br>II_RXD0, FMC_SDNE0,<br>EVENTOUT                                                    | ADC12_IN14              |

| 33      | H4       | N9       | 45      | P5       | 55      | 58      | P5       | PC5                                                        | I/O      | FT            | (4)   | SPDIFRX_IN3,<br>ETH_MII_RXD1/ETH_RM<br>II_RXD1, FMC_SDCKE0,<br>EVENTOUT                                                                | ADC12_IN15              |

| -       | -        | J7       | -       | -        | -       | 59      | L7       | VDD                                                        | S        | -             | -     | -                                                                                                                                      | -                       |

| -       | -        | -        | -       | -        | -       | 60      | L6       | VSS                                                        | S        | -             | -     | -                                                                                                                                      | -                       |

| 34      | J4       | N8       | 46      | R5       | 56      | 61      | R5       | PB0                                                        | I/O      | FT            | (4)   | TIM1_CH2N, TIM3_CH3,<br>TIM8_CH2N,<br>UART4_CTS, LCD_R3,<br>OTG_HS_ULPI_D1,<br>ETH_MII_RXD2,<br>EVENTOUT                               | ADC12_IN8               |

| 35      | K4       | K7       | 47      | R4       | 57      | 62      | R4       | PB1                                                        | I/O      | FT            | (4)   | TIM1_CH3N, TIM3_CH4,<br>TIM8_CH3N, LCD_R6,<br>OTG_HS_ULPI_D2,<br>ETH_MII_RXD3,<br>EVENTOUT                                             | ADC12_IN9               |

| 36      | G5       | L7       | 48      | M6       | 58      | 63      | M5       | PB2                                                        | I/O      | FT            | -     | SAI1_SD_A,<br>SPI3_MOSI/I2S3_SD,<br>QUADSPI_CLK,<br>EVENTOUT                                                                           | -                       |

| -       | -        | -        | -       | -        | -       | 64      | G4       | PI15                                                       | I/O      | FT            | -     | - LCD_R0, EVENTOUT -                                                                                                                   |                         |

| -       | -        | -        | -       | -        | -       | 65      | R6       | PJ0                                                        | I/O      | FT            | -     | LCD_R1, EVENTOUT                                                                                                                       | -                       |

| -       | -        | -        | -       | -        | -       | 66      | R7       | PJ1                                                        | I/O      | FT            | -     | LCD_R2, EVENTOUT                                                                                                                       | -                       |

#### Table 10. STM32F745xx and STM32F746xx pin and ball definition (continued)

|         |          |          |         | umbei    | r       |         |          |                                                            |          |               |       | ,                                                                |                         |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|-------|------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                              | Additional<br>functions |

| -       | -        | -        | -       | -        | -       | 67      | P7       | PJ2                                                        | I/O      | FT            | -     | LCD_R3, EVENTOUT                                                 | -                       |

| -       | -        | -        | -       | -        | -       | 68      | N8       | PJ3                                                        | I/O      | FT            | -     | LCD_R4, EVENTOUT                                                 | -                       |

| -       | -        | -        | -       | -        | -       | 69      | M9       | PJ4                                                        | I/O      | FT            | -     | LCD_R5, EVENTOUT                                                 | -                       |

| -       | -        | M7       | 49      | R6       | 59      | 70      | P8       | PF11                                                       | I/O      | FT            | -     | SPI5_MOSI, SAI2_SD_B,<br>FMC_SDNRAS,<br>DCMI_D12, EVENTOUT       | -                       |

| -       | -        | N7       | 50      | P6       | 60      | 71      | M6       | PF12                                                       | I/O      | FT            | -     | FMC_A6, EVENTOUT                                                 | -                       |

| -       | -        | -        | 51      | M8       | 61      | 72      | K7       | VSS                                                        | S        | -             | -     | -                                                                | -                       |

| -       | -        | -        | 52      | N8       | 62      | 73      | L8       | VDD                                                        | S        | -             | -     | -                                                                | -                       |

| -       | -        | K6       | 53      | N6       | 63      | 74      | N6       | PF13                                                       | I/O      | FT            | -     | I2C4_SMBA, FMC_A7,<br>EVENTOUT                                   | -                       |

| -       | -        | L6       | 54      | R7       | 64      | 75      | P6       | PF14                                                       | I/O      | FT            | -     | I2C4_SCL, FMC_A8,<br>EVENTOUT                                    | -                       |

| -       | -        | M6       | 55      | P7       | 65      | 76      | M8       | PF15                                                       | I/O      | FT            | -     | I2C4_SDA, FMC_A9,<br>EVENTOUT                                    | -                       |

| -       | -        | N6       | 56      | N7       | 66      | 77      | N7       | PG0                                                        | I/O      | FT            | -     | FMC_A10, EVENTOUT                                                | -                       |

| -       | -        | K5       | 57      | M7       | 67      | 78      | M7       | PG1                                                        | I/O      | FT            | -     | FMC_A11, EVENTOUT                                                | -                       |

| 37      | H5       | L5       | 58      | R8       | 68      | 79      | R8       | PE7                                                        | I/O      | FT            | -     | TIM1_ETR, UART7_Rx,<br>QUADSPI_BK2_IO0,<br>FMC_D4, EVENTOUT      | -                       |

| 38      | J5       | M5       | 59      | P8       | 69      | 80      | N9       | PE8                                                        | I/O      | FT            | -     | TIM1_CH1N, UART7_Tx,<br>QUADSPI_BK2_IO1,<br>FMC_D5, EVENTOUT     | -                       |

| 39      | K5       | N5       | 60      | P9       | 70      | 81      | P9       | PE9                                                        | I/O      | FT            | -     | TIM1_CH1, UART7_RTS,<br>QUADSPI_BK2_IO2,<br>FMC_D6, EVENTOUT     | -                       |

| -       | -        | H3       | 61      | M9       | 71      | 82      | K8       | VSS                                                        | S        | -             | I     | -                                                                | -                       |

| -       | -        | J5       | 62      | N9       | 72      | 83      | L9       | VDD                                                        | S        | -             | -     | -                                                                | -                       |

| 40      | G6       | J4       | 63      | R9       | 73      | 84      | R9       | PE10                                                       | I/O      | FT            | -     | TIM1_CH2N,<br>UART7_CTS,<br>QUADSPI_BK2_IO3,<br>FMC_D7, EVENTOUT | -                       |

| Table 10. STM32F745xx and STM32F746xx pin and ball definition (c | continued) |

|------------------------------------------------------------------|------------|

|                                                                  |            |

5

DocID027590 Rev 4

|        |      | AF0 | AF1    | AF2          | AF3                             | AF4                | AF5                       | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11            | AF12                       | AF13           | AF14   | AF15         |

|--------|------|-----|--------|--------------|---------------------------------|--------------------|---------------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|-----------------|----------------------------|----------------|--------|--------------|

| P      | ort  | SYS | TIM1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6        | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI           | LCD    | SYS          |

|        | PH8  | -   | -      | -            | -                               | I2C3_SD<br>A       | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D1<br>6                | DCMI_H<br>SYNC | LCD_R2 | EVEN<br>TOUT |

|        | PH9  | -   | -      | -            | -                               | I2C3_SM<br>BA      | -                         | -             | -                                           | -                                               | TIM12_C<br>H2                              | -                                        | -               | FMC_D1<br>7                | DCMI_D<br>0    | LCD_R3 | EVEN<br>TOUT |

|        | PH10 | -   | -      | TIM5_C<br>H1 | -                               | I2C4_SM<br>BA      | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D1<br>8                | DCMI_D<br>1    | LCD_R4 | EVEN<br>TOUT |

| Port H | PH11 | -   | -      | TIM5_C<br>H2 | -                               | I2C4_SC<br>L       | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D1<br>9                | DCMI_D<br>2    | LCD_R5 | EVEN<br>TOUT |

| POILE  | PH12 | -   | -      | TIM5_C<br>H3 | -                               | I2C4_SD<br>A       | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>0                | DCMI_D<br>3    | LCD_R6 | EVEN<br>TOUT |

|        | PH13 | -   | -      | -            | TIM8_CH<br>1N                   | -                  | -                         | -             | -                                           | -                                               | CAN1_T<br>X                                | -                                        | -               | FMC_D2<br>1                | -              | LCD_G2 | EVEN<br>TOUT |

|        | PH14 | -   | -      | -            | TIM8_CH<br>2N                   | -                  | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>2                | DCMI_D<br>4    | LCD_G3 | EVEN<br>TOUT |

|        | PH15 | -   | -      | -            | TIM8_CH<br>3N                   | -                  | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>3                | DCMI_D<br>11   | LCD_G4 | EVEN<br>TOUT |

|        | PI0  | -   | -      | TIM5_C<br>H4 | -                               | -                  | SPI2_NS<br>S/I2S2_<br>WS  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>4                | DCMI_D<br>13   | LCD_G5 | EVEN<br>TOUT |

|        | PI1  | -   | -      | -            | TIM8_BKI<br>N2                  | -                  | SPI2_SC<br>K/I2S2_<br>CK  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>5                | DCMI_D<br>8    | LCD_G6 | EVEN<br>TOUT |

|        | PI2  | -   | -      | -            | TIM8_CH<br>4                    | -                  | SPI2_MI<br>SO             | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>6                | DCMI_D<br>9    | LCD_G7 | EVEN<br>TOUT |

| Port I | PI3  | -   | -      | -            | TIM8_ET<br>R                    | -                  | SPI2_M<br>OSI/I2S2<br>_SD | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>7                | DCMI_D<br>10   | -      | EVEN<br>TOUT |

|        | PI4  | -   | -      | -            | TIM8_BKI<br>N                   | -                  | -                         | -             | -                                           | -                                               | -                                          | SAI2_MC<br>K_A                           | -               | FMC_NB<br>L2               | DCMI_D<br>5    | LCD_B4 | EVEN<br>TOUT |

|        | PI5  | -   | -      | -            | TIM8_CH<br>1                    | -                  | -                         | -             | -                                           | -                                               | -                                          | SAI2_SC<br>K_A                           | -               | FMC_NB<br>L3               | DCMI_V<br>SYNC | LCD_B5 | EVEN<br>TOUT |

|        | PI6  | -   | -      | -            | TIM8_CH<br>2                    | -                  | -                         | -             | -                                           | -                                               | -                                          | SAI2_SD_<br>A                            | -               | FMC_D2<br>8                | DCMI_D<br>6    | LCD_B6 | EVEN<br>TOUT |

Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

AF0

AF1

AF2

AF3

AF4

AF6

AF7

AF8

AF9

AF10

AF11

AF12

AF13

AF14

AF15

85/227

STM32F745xx STM32F746xx

Pinouts and pin description

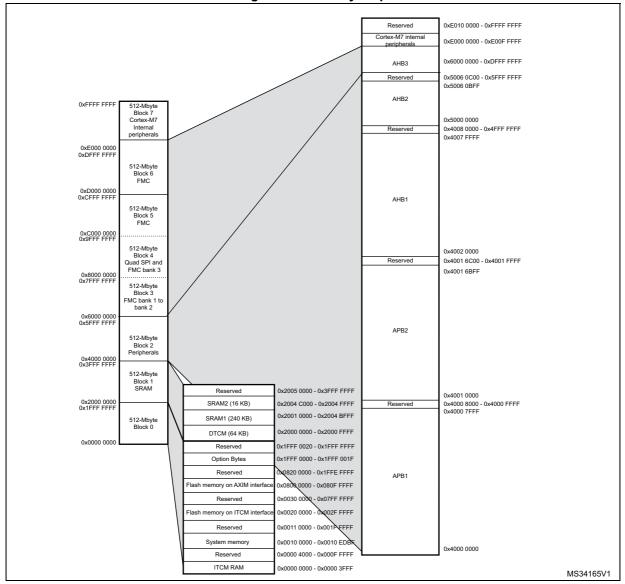

# 4 Memory mapping

The memory map is shown in *Figure 19*.

Figure 19. Memory map

| Bus  | Boundary address          | Peripheral         |

|------|---------------------------|--------------------|

|      | 0x4001 6C00- 0x4001 FFFF  | Reserved           |

|      | 0x4001 6800 - 0x4001 6BFF | LCD-TFT            |

|      | 0x4001 6000 - 0x4001 67FF | Reserved           |

|      | 0x4001 5C00 - 0x4001 5FFF | SAI2               |

|      | 0x4001 5800 - 0x4001 5BFF | SAI1               |

|      | 0x4001 5400 - 0x4001 57FF | SPI6               |

|      | 0x4001 5000 - 0x4001 53FF | SPI5               |

|      | 0x4001 4C00 - 0x4001 4FFF | Reserved           |

|      | 0x4001 4800 - 0x4001 4BFF | TIM11              |

|      | 0x4001 4400 - 0x4001 47FF | TIM10              |

|      | 0x4001 4000 - 0x4001 43FF | ТІМ9               |

|      | 0x4001 3C00 - 0x4001 3FFF | EXTI               |

| APB2 | 0x4001 3800 - 0x4001 3BFF | SYSCFG             |

|      | 0x4001 3400 - 0x4001 37FF | SPI4               |

|      | 0x4001 3000 - 0x4001 33FF | SPI1/I2S1          |

|      | 0x4001 2C00 - 0x4001 2FFF | SDMMC              |

|      | 0x4001 2400 - 0x4001 2BFF | Reserved           |

|      | 0x4001 2000 - 0x4001 23FF | ADC1 - ADC2 - ADC3 |

|      | 0x4001 1800 - 0x4001 1FFF | Reserved           |

|      | 0x4001 1400 - 0x4001 17FF | USART6             |

|      | 0x4001 1000 - 0x4001 13FF | USART1             |

|      | 0x4001 0800 - 0x4001 0FFF | Reserved           |

|      | 0x4001 0400 - 0x4001 07FF | TIM8               |

|      | 0x4001 0000 - 0x4001 03FF | TIM1               |

#### Table 13. STM32F745xx and STM32F746xx register boundary addresses (continued)

- 1. Guaranteed by design.

- 2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

#### 5.3.6 Over-drive switching characteristics

When the over-drive mode switches from enabled to disabled or disabled to enabled, the system clock is stalled during the internal voltage set-up.

The over-drive switching characteristics are given in *Table 23*. They are sbject to general operating conditions for  $T_A$ .

| Symbol    | Parameter                        | Conditions                              | Min | Тур | Мах | Unit |

|-----------|----------------------------------|-----------------------------------------|-----|-----|-----|------|

|           |                                  | HSI                                     | -   | 45  | -   |      |

| Tod_swen  | Over_drive switch<br>enable time | HSE max for 4 MHz<br>and min for 26 MHz | 45  | -   | 100 |      |

|           |                                  | External HSE<br>50 MHz                  | -   | 40  | -   | 110  |

|           |                                  | HSI                                     | -   | 20  | -   | μs   |

| Tod_swdis | Over_drive switch disable time   | HSE max for 4 MHz and min for 26 MHz.   | 20  | -   | 80  |      |

|           |                                  | External HSE<br>50 MHz                  | -   | 15  | -   |      |

Table 23. Over-drive switching characteristics<sup>(1)</sup>

1. Guaranteed by design.

#### 5.3.7 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 23: Current consumption measurement scheme*.

All the run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

| Querra have     | Demonstern             | O an ditian a                                | £ (MIL_)                                   | <b>T</b>                                   |                                            | Max <sup>(1)</sup>                         |           | 11   |     |     |     |  |

|-----------------|------------------------|----------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|-----------|------|-----|-----|-----|--|

| Symbol          | Parameter              | Conditions                                   | f <sub>HCLK</sub> (MHz)                    | Тур                                        | TA= 25 °C                                  | TA=85 °C                                   | TA=105 °C | Unit |     |     |     |  |

|                 |                        |                                              | 216                                        | 181                                        | 210                                        | 233                                        | -         |      |     |     |     |  |

|                 |                        |                                              | 200                                        | 168                                        | 194                                        | 216                                        | 234       |      |     |     |     |  |

|                 |                        |                                              | 180                                        | 153                                        | 176                                        | 192                                        | 206       |      |     |     |     |  |

|                 |                        | All peripherals<br>enabled <sup>(2)(3)</sup> | 168                                        | 136                                        | 157                                        | 172                                        | 184       |      |     |     |     |  |

|                 |                        |                                              | 0.100.000                                  | 144                                        | 109                                        | 125                                        | 137       | 148  |     |     |     |  |

|                 |                        |                                              | 60                                         | 53                                         | 61                                         | 73                                         | 84        |      |     |     |     |  |

|                 | Supply                 |                                              | 25                                         | 26                                         | 30                                         | 41                                         | 52        | m۸   |     |     |     |  |

| I <sub>DD</sub> | current in<br>RUN mode |                                              | 216                                        | 105                                        | 121                                        | 145                                        | -         | mA   |     |     |     |  |

|                 |                        |                                              |                                            |                                            | 200                                        | 98                                         | 112       | 134  | 153 |     |     |  |

|                 |                        |                                              | 180                                        | 90                                         | 103                                        | 119                                        | 132       |      |     |     |     |  |

|                 |                        | All peripherals                              | All peripherals<br>disabled <sup>(3)</sup> | All peripherals<br>disabled <sup>(3)</sup> | All peripherals<br>disabled <sup>(3)</sup> | All peripherals<br>disabled <sup>(3)</sup> | 168       | 81   | 93  | 107 | 120 |  |

|                 |                        | 0.000100                                     | 144                                        | 67                                         | 76                                         | 88                                         | 89        |      |     |     |     |  |

|                 |                        | -                                            | 60                                         | 34                                         | 40                                         | 51                                         | 62        |      |     |     |     |  |

|                 |                        |                                              | 25                                         | 17                                         | 20                                         | 31                                         | 42        |      |     |     |     |  |

# Table 26. Typical and maximum current consumption in Run mode, code with data processingrunning from Flash memory or SRAM on AXI (L1-cache disabled), regulator ON

1. Guaranteed by characterization results.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

| D          | ا <sub>DD</sub> (Typ) <sup>(1)</sup> |                         |      |      | Unit   |  |

|------------|--------------------------------------|-------------------------|------|------|--------|--|

| renpilerai |                                      | Scale 1 Scale 2 Scale 3 |      |      | Unit   |  |

|            | TIM1                                 | 25.2                    | 23.9 | 20.4 |        |  |

| Γ          | TIM8                                 | 25.3                    | 24   | 20.4 |        |  |

| Γ          | USART1                               | 10.3                    | 9.8  | 8.2  |        |  |

| Γ          | USART6                               | 10.1                    | 9.7  | 8.1  |        |  |

| Γ          | ADC1 <sup>(5)</sup>                  | 4.5                     | 4.4  | 3.5  |        |  |

| Ī          | ADC2 <sup>(5)</sup>                  | 4.5                     | 4.4  | 3.5  |        |  |

| Ī          | ADC3 <sup>(5)</sup>                  | 4.5                     | 4.4  | 3.3  |        |  |

| Ī          | SDMMC1                               | 8.5                     | 7.9  | 6.7  |        |  |

| APB2       | SPI1/I2S1 <sup>(3)</sup>             | 3.1                     | 3    | 2.5  |        |  |

| (up to     | SPI4                                 | 3.1                     | 3    | 2.5  | µA/MHz |  |

| 108 MHz)   | SYSCFG                               | 1.5                     | 1.4  | 1    |        |  |

| Γ          | TIM9                                 | 8.8                     | 8.4  | 6.9  |        |  |

| Γ          | TIM10                                | 5.6                     | 5.2  | 4.3  |        |  |

| Ī          | TIM11                                | 5.4                     | 5.2  | 4.3  |        |  |

| Ī          | SPI5                                 | 3                       | 2.8  | 2.2  |        |  |

| Ī          | SPI6                                 | 3                       | 2.8  | 2.2  |        |  |

| -          | SAI1                                 | 3.4                     | 3.3  | 2.6  |        |  |

|            | SAI2                                 | 3.3                     | 3.2  | 2.5  |        |  |

|            | LTDC                                 | 56.7                    | 53.8 | 45.7 |        |  |

Table 35. Peripheral current consumption (continued)

1. When the I/O compensation cell  $\,$  is ON,  $I_{\text{DD}}$  typical value increases by 0.22 mA.

2. The BusMatrix is automatically active when at least one master is ON.

3. To enable an I2S peripheral, first set the I2SMOD bit and then the I2SE bit in the SPI\_I2SCFGR register.

4. When the DAC is ON and EN1/2 bits are set in DAC\_CR register, add an additional power consumption of 0.75 mA per DAC channel for the analog part.

5. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

#### 5.3.22 Temperature sensor characteristics

| Table 68. Temperature sensor character | teristics |

|----------------------------------------|-----------|

|----------------------------------------|-----------|

| Symbol                             | Parameter                                                      | Min | Тур  | Max | Unit  |

|------------------------------------|----------------------------------------------------------------|-----|------|-----|-------|

| T <sub>L</sub> <sup>(1)</sup>      | V <sub>SENSE</sub> linearity with temperature                  | -   | ±1   | ±2  | °C    |

| Avg_Slope <sup>(1)</sup>           | Average slope                                                  | -   | 2.5  | -   | mV/°C |

| V <sub>25</sub> <sup>(1)</sup>     | Voltage at 25 °C                                               | -   | 0.76 | -   | V     |

| t <sub>START</sub> <sup>(2)</sup>  | Startup time                                                   | -   | 6    | 10  | μs    |

| T <sub>S_temp</sub> <sup>(2)</sup> | ADC sampling time when reading the temperature (1 °C accuracy) | 10  | -    | -   | μs    |

1. Guaranteed by characterization results.

2. Guaranteed by design.

| Table 69. Temperature sensor calibration values |                                                                            |                           |  |  |  |

|-------------------------------------------------|----------------------------------------------------------------------------|---------------------------|--|--|--|

| Symbol                                          | Parameter                                                                  | Memory address            |  |  |  |

| TS_CAL1                                         | TS ADC raw data acquired at temperature of 30 °C, V <sub>DDA</sub> = 3.3 V | 0x1FF0 F44C - 0x1FF0 F44D |  |  |  |

| TS_CAL2                                         | TS ADC raw data acquired at temperature of 110 °C, $V_{DDA}$ = 3.3 V       | 0x1FF0 F44E - 0x1FF0 F44F |  |  |  |

#### 5.3.23 V<sub>BAT</sub> monitoring characteristics

#### Table 70. V<sub>BAT</sub> monitoring characteristics

| Symbol                                | Parameter                                                            | Min | Тур | Мах | Unit |

|---------------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| R                                     | Resistor bridge for V <sub>BAT</sub>                                 | -   | 50  | -   | KΩ   |

| Q                                     | Ratio on V <sub>BAT</sub> measurement                                | -   | 4   | -   | -    |

| Er <sup>(1)</sup>                     | Error on Q                                                           | -1  | -   | +1  | %    |

| T <sub>S_vbat</sub> <sup>(2)(2)</sup> | ADC sampling time when reading the V <sub>BAT</sub><br>1 mV accuracy | 5   | -   | -   | μs   |

1. Guaranteed by design.

2. Shortest sampling time can be determined in the application by multiple iterations.

#### 5.3.24 Reference voltage

The parameters given in *Table 71* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol                                | Parameter                                                     | Conditions                        | Min  | Тур  | Max  | Unit |

|---------------------------------------|---------------------------------------------------------------|-----------------------------------|------|------|------|------|

| V <sub>REFINT</sub>                   | Internal reference voltage                                    | –40 °C < T <sub>A</sub> < +105 °C | 1.18 | 1.21 | 1.24 | V    |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when reading the internal reference voltage | -                                 | 10   | -    | -    | μs   |

| V <sub>RERINT_s</sub> <sup>(2)</sup>  | Internal reference voltage spread over the temperature range  | $V_{DD}$ = 3V $\pm$ 10mV          | -    | 3    | 5    | mV   |

DocID027590 Rev 4

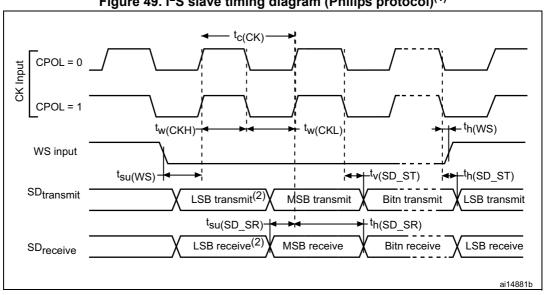

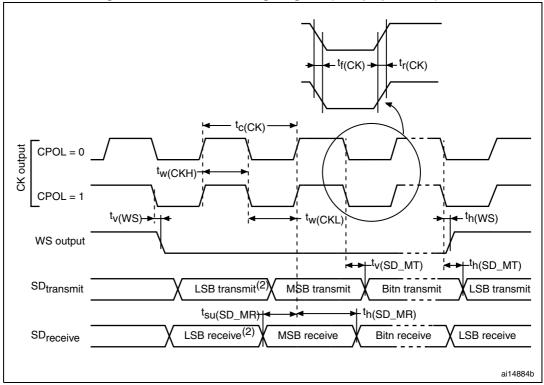

Figure 49. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### Figure 50. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

| Symbol                      | Parameter                                  | Min                     | Max | Unit |

|-----------------------------|--------------------------------------------|-------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                             | 2T <sub>HCLK</sub> -0.5 | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)          | -                       | 1.5 |      |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)       | T <sub>HCLK</sub> +0.5  | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                | -                       | 1.5 |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high               | 0                       | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)       | -                       | 2   |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)    | T <sub>HCLK</sub>       | -   |      |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low                 | -                       | 1.5 |      |

| t <sub>(CLKH-NWEH)</sub>    | FMC_CLK high to FMC_NWE high               | T <sub>HCLK</sub> -0.5  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid          | -                       | 3   |      |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid        | 0                       | -   |      |

| t <sub>d(CLKL-DATA)</sub>   | FMC_A/D[15:0] valid data after FMC_CLK low | -                       | 3.5 |      |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low                 | 1                       | -   |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high               | T <sub>HCLK</sub> +0.5  | -   | ]    |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high        | 2                       | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high         | 3.5                     | -   |      |

Table 97. Synchronous multiplexed PSRAM write timings<sup>(1)</sup>

1. Guaranteed by characterization results.

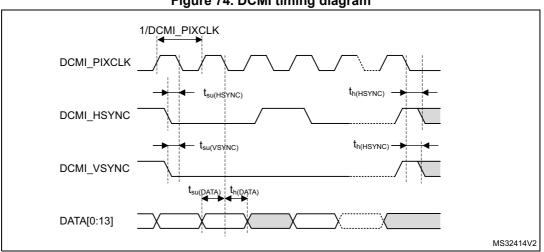

Figure 74. DCMI timing diagram

#### 5.3.30 LCD-TFT controller (LTDC) characteristics

Unless otherwise specified, the parameters given in *Table 109* for LCD-TFT are derived from tests performed under the ambient temperature, fHCLK frequency and VDD supply voltage summarized in *Table 17*, with the following configuration:

- LCD\_CLK polarity: high •

- LCD DE polarity : low •

- LCD\_VSYNC and LCD\_HSYNC polarity: high

- Pixel formats: 24 bits

#### Table 109. LTDC characteristics <sup>(1)</sup>

| Symbol                                       | Parameter                        | Min             | Мах           | Unit |  |  |

|----------------------------------------------|----------------------------------|-----------------|---------------|------|--|--|

| f <sub>CLK</sub>                             | LTDC clock output frequency      | -               | 45            | MHz  |  |  |

| D <sub>CLK</sub>                             | LTDC clock output duty cycle     | 45              | 55            | %    |  |  |

| t <sub>w(CLKH)</sub><br>t <sub>w(CLKL)</sub> | Clock High time, low time        | tw(CLK)/2 - 0.5 | tw(CLK)/2+0.5 |      |  |  |

| t <sub>v(DATA)</sub>                         | Data output valid time           | -               | 6             |      |  |  |

| t <sub>h(DATA)</sub>                         | Data output hold time            | 2               | -             |      |  |  |

| t <sub>v(HSYNC)</sub>                        |                                  |                 |               |      |  |  |

| t <sub>v(VSYNC)</sub>                        | HSYNC/VSYNC/DE output valid time | -               | 3             | ns   |  |  |

| t <sub>v(DE)</sub>                           |                                  |                 |               |      |  |  |

| t <sub>h(HSYNC)</sub>                        |                                  |                 |               |      |  |  |

| t <sub>h(VSYNC)</sub>                        | HSYNC/VSYNC/DE output hold time  | 0.5             | -             |      |  |  |

| th(DE)                                       |                                  |                 |               |      |  |  |

1. Guaranteed by characterization results.

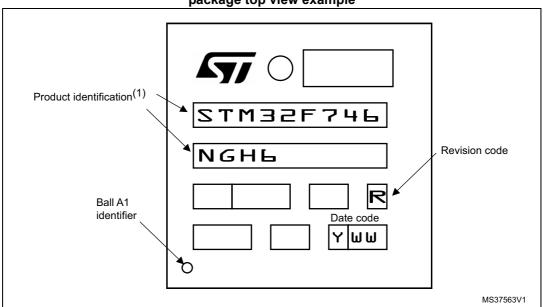

#### Marking of engineering samples

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID027590 Rev 4