Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                                        |

|----------------------------|--------------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                                 |

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTC |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 140                                                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                                                       |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320K x 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                      |

| Mounting Type              | Surface Mount                                                                                          |

| Package / Case             | 176-LQFP                                                                                               |

| Supplier Device Package    | 176-LQFP (24x24)                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f746iet6                                  |

#### 2.15 Boot modes

At startup, the boot memory space is selected by the BOOT pin and BOOT\_ADDx option bytes, allowing to program any boot memory address from 0x0000 0000 to 0x3FFF FFFF which includes:

- All Flash address space mapped on ITCM or AXIM interface

- All RAM address space: ITCM, DTCM RAMs and SRAMs mapped on AXIM interface

- The System memory bootloader

The boot loader is located in system memory. It is used to reprogram the Flash memory through a serial interface.

## 2.16 Power supply schemes

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

- V<sub>DD</sub> = 1.7 to 3.6 Vexternal power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, DAC, reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

Note:

$V_{DD}/V_{DDA}$  minimum value of 1.7 V is obtained when the internal reset is OFF (refer to Section 2.17.2: Internal reset OFF). Refer to Table 3: Voltage regulator configuration mode versus device operating mode to identify the packages supporting this option.

- V<sub>DDUSB</sub> can be connected either to V<sub>DD</sub> or an external independent power supply (3.0 to 3.6V) for USB transceivers (refer to *Figure 4* and *Figure 5*). For example, when device is powered at 1.8V, an independent power supply 3.3V can be connected to V<sub>DDUSB</sub>. When the V<sub>DDUSB</sub> is connected to a separated power supply, it is independent from V<sub>DD</sub> or V<sub>DDA</sub> but it must be the last supply to be provided and the first to disappear. The following conditions V<sub>DDUSB</sub> must be respected:

- During power-on phase ( $V_{DD} < V_{DD\_MIN}$ ),  $V_{DDUSB}$  should be always lower than  $V_{DD}$

- During power-down phase ( $V_{DD} < V_{DD\_MIN}$ ),  $V_{DDUSB}$  should be always lower than  $V_{DD}$

- V<sub>DDSUB</sub> rising and falling time rate specifications must be respected (see *Table 20* and *Table 21*)

- In operating mode phase, V<sub>DDUSB</sub> could be lower or higher than V<sub>DD</sub>.

- If USB (USB OTG\_HS/OTG\_FS) is used, the associated GPIOs powered by  $V_{DDUSB}$  are operating between  $V_{DDUSB\ MIN}$  and  $V_{DDUSB\ MAX}.$

- The  $V_{DDUSB}$  supply both USB transceiver (USB OTG\_HS and USB OTG\_FS). If only one USB transceiver is used in the application, the GPIOs associated to the other USB transceiver are still supplied by  $V_{DDUSB}$ .

- If USB (USB OTG\_HS/OTG\_FS) is not used, the associated GPIOs powered by  $V_{DDUSB}$  are operating between  $V_{DD\_MIN}$  and  $V_{DD\_MAX}.$

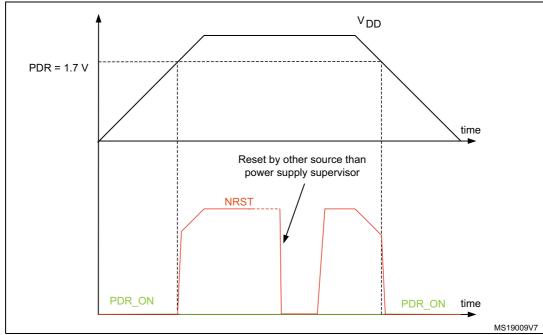

Figure 7. PDR\_ON control with internal reset OFF

# 2.18 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low-power regulator (LPR)

- Power-down

- Regulator OFF

## 2.18.1 Regulator ON

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when the regulator is ON:

- MR mode used in Run/sleep modes or in Stop modes

- In Run/Sleep mode

The MR mode is used either in the normal mode (default mode) or the over-drive mode (enabled by software). Different voltages scaling are provided to reach the best compromise between the maximum frequency and dynamic power

26/227 DocID027590 Rev 4

PDR = 1.7 V or 1.8 V

Min V<sub>12</sub>

Min V<sub>12</sub>

NRST

time

ai18491f

Figure 9. Startup in regulator OFF: slow  $V_{DD}$  slope - power-down reset risen after  $V_{CAP\ 1}/V_{CAP\ 2}$  stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

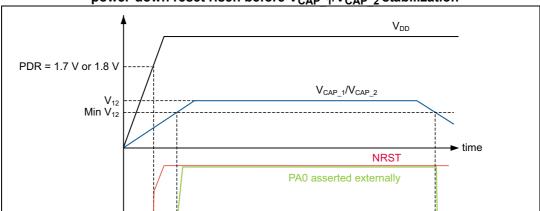

Figure 10. Startup in regulator OFF mode: fast  $V_{DD}$  slope - power-down reset risen before  $V_{CAP\ 1}/V_{CAP\ 2}$  stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

ai18492e

time

# 2.21 V<sub>BAT</sub> operation

The  $V_{BAT}$  pin allows to power the device  $V_{BAT}$  domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present.

$V_{\text{BAT}}$  operation is activated when  $V_{\text{DD}}$  is not present.

The V<sub>BAT</sub> pin supplies the RTC, the backup registers and the backup SRAM.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

When PDR\_ON pin is connected to  $V_{SS}$  (Internal Reset OFF), the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to  $V_{DD}$ .

## 2.22 Timers and watchdogs

The devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

*Table 6* compares the features of the advanced-control, general-purpose and basic timers.

#### 2.22.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

#### 2.22.4 Low-power timer (LPTIM1)

The low-power timer has an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one-shot mode

- Selectable software / hardware input trigger

- Selectable clock source:

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

#### 2.22.5 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

#### 2.22.6 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 2.22.7 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

# 2.24 Universal synchronous/asynchronous receiver transmitters (USART)

The device embeds USART. Refer to *Table 8: USART implementation* for the features implementation.

The universal synchronous asynchronous receiver transmitter (USART) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format.

The USART peripheral supports:

- Full-duplex asynchronous communications

- Configurable oversampling method by 16 or 8 to give flexibility between speed and clock tolerance

- Dual clock domain allowing convenient baud rate programming independent from the PCLK reprogramming

- A common programmable transmit and receive baud rate of up to 27 Mbit/s when USART clock source is system clock frequency (Max is 216 MHz) and oversampling by 8 is used.

- Auto baud rate detection

- Programmable data word length (7 or 8 or 9 bits) word length

- Programmable data order with MSB-first or LSB-first shifting

- Programmable parity (odd, even, no parity)

- Configurable stop bits (1 or 1.5 or 2 stop bits)

- Synchronous mode and clock output for synchronous communications

- Single-wire half-duplex communications

- Separate signal polarity control for transmission and reception

- Swappable Tx/Rx pin configuration

- Hardware flow control for modem and RS-485 transceiver

- Multiprocessor communications

- LIN master synchronous break send capability and LIN slave break detection capability

- IrDA SIR encoder decoder supporting 3/16 bit duration for normal mode

- Smartcard mode ( T=0 and T=1 asynchronous protocols for Smartcards as defined in the ISO/IEC 7816-3 standard )

- Support for Modbus communication

The table below summarizes the implementation of all U(S)ARTs instances

Table 8. USART implementation

| features <sup>(1)</sup>            | USART1/2/3/6    | UART4/5/7/8 |  |  |  |

|------------------------------------|-----------------|-------------|--|--|--|

| Data Length                        | 7, 8 and 9 bits |             |  |  |  |

| Hardware flow control for modem    | Х               | Х           |  |  |  |

| Continuous communication using DMA | X               | Х           |  |  |  |

| Multiprocessor communication       | X               | Х           |  |  |  |

| Synchronous mode                   | Х               | -           |  |  |  |

### 2.38 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allowing maximum I/O toggling up to 108 MHz.

# 2.39 Analog-to-digital converters (ADCs)

Three 12-bit analog-to-digital converters are embedded and each ADC shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1, TIM2, TIM3, TIM4, TIM5, or TIM8 timer.

# 2.40 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.7 V and 3.6 V. The temperature sensor is internally connected to the same input channel as  $V_{BAT}$ , ADC1\_IN18, which is used to convert the sensor output voltage into a digital value. When the temperature sensor and  $V_{BAT}$  conversion are enabled at the same time, only  $V_{BAT}$  conversion is performed.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

# 2.41 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs.

Table 10. STM32F745xx and STM32F746xx pin and ball definition (continued)

|         |          |          |         | umber    |         |         |          |                                                            |          |               |       | ban deminion (continue                                                                                          |                         |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                                             | Additional<br>functions |

| 41      | H6       | K4       | 64      | P10      | 74      | 85      | P10      | PE11                                                       | I/O      | FT            | -     | TIM1_CH2, SPI4_NSS,<br>SAI2_SD_B, FMC_D8,<br>LCD_G3, EVENTOUT                                                   | -                       |

| 42      | J6       | L4       | 65      | R10      | 75      | 86      | R10      | PE12                                                       | I/O      | FT            | -     | TIM1_CH3N, SPI4_SCK,<br>SAI2_SCK_B, FMC_D9,<br>LCD_B4, EVENTOUT                                                 | -                       |

| 43      | K6       | N4       | 66      | N11      | 76      | 87      | R12      | PE13                                                       | I/O      | FT            | -     | TIM1_CH3, SPI4_MISO,<br>SAI2_FS_B, FMC_D10,<br>LCD_DE, EVENTOUT                                                 | -                       |

| 44      | G7       | M4       | 67      | P11      | 77      | 88      | P11      | PE14                                                       | I/O      | FT            | -     | TIM1_CH4, SPI4_MOSI,<br>SAI2_MCK_B, FMC_D11,<br>LCD_CLK, EVENTOUT                                               | -                       |

| 45      | H7       | L3       | 68      | R11      | 78      | 89      | R11      | PE15                                                       | I/O      | FT            | -     | TIM1_BKIN, FMC_D12,<br>LCD_R7, EVENTOUT                                                                         | -                       |

| 46      | J7       | M3       | 69      | R12      | 79      | 90      | P12      | PB10                                                       | I/O      | FT            | -     | TIM2_CH3, I2C2_SCL,<br>SPI2_SCK/I2S2_CK,<br>USART3_TX,<br>OTG_HS_ULPI_D3,<br>ETH_MII_RX_ER,<br>LCD_G4, EVENTOUT | -                       |

| 47      | K7       | N3       | 70      | R13      | 80      | 91      | R13      | PB11                                                       | I/O      | FT            | -     | TIM2_CH4, I2C2_SDA, USART3_RX, OTG_HS_ULPI_D4, ETH_MII_TX_EN/ETH_R MII_TX_EN, LCD_G5, EVENTOUT                  | -                       |

| 48      | F8       | N2       | 71      | M10      | 81      | 92      | L11      | VCAP_1                                                     | S        | -             | -     | -                                                                                                               | -                       |

| 49      | -        | H2       | -       | -        | -       | 93      | K9       | VSS                                                        | S        | -             | -     | -                                                                                                               | -                       |

| 50      | -        | J6       | 72      | N10      | 82      | 94      | L10      | VDD                                                        | S        | -             | -     | -                                                                                                               | -                       |

| -       | -        | -        | -       | -        | -       | 95      | M14      | PJ5                                                        | I/O      | FT            | -     | LCD_R6, EVENTOUT                                                                                                | -                       |

| -       | -        | -        | -       | M11      | 83      | 96      | P13      | PH6                                                        | I/O      | FT            | -     | I2C2_SMBA, SPI5_SCK,<br>TIM12_CH1,<br>ETH_MII_RXD2,<br>FMC_SDNE1, DCMI_D8,<br>EVENTOUT                          | -                       |

Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

|        |      | AF0         | AF1    | AF2          | AF3                             | AF4                | AF5                | AF6                       | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11                                   | AF12                       | AF13        | AF14          | AF15         |

|--------|------|-------------|--------|--------------|---------------------------------|--------------------|--------------------|---------------------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|----------------------------------------|----------------------------|-------------|---------------|--------------|

| Po     | ort  | sys         | TIM1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1             | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS                        | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI        | LCD           | sys          |

|        | PC4  | 1           | -      | -            | -                               | -                  | I2S1_M<br>CK       | -                         | -                                           | SPDIFRX<br>_IN2                                 | -                                          | -                                        | ETH_MII_<br>RXD0/ET<br>H_RMII_<br>RXD0 | FMC_SD<br>NE0              | -           | -             | EVEN<br>TOUT |

|        | PC5  | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | SPDIFRX<br>_IN3                                 | -                                          | -                                        | ETH_MII_<br>RXD1/ET<br>H_RMII_<br>RXD1 | FMC_SD<br>CKE0             | -           | -             | EVEN<br>TOUT |

|        | PC6  | -           | -      | TIM3_C<br>H1 | TIM8_CH<br>1                    | -                  | I2S2_M<br>CK       | -                         | -                                           | USART6<br>_TX                                   | -                                          | -                                        | -                                      | SDMMC<br>1_D6              | DCMI_D<br>0 | LCD_HS<br>YNC | EVEN<br>TOUT |

|        | PC7  | -           | -      | TIM3_C<br>H2 | TIM8_<br>CH2                    | -                  | -                  | I2S3_M<br>CK              | -                                           | USART6<br>_RX                                   | -                                          | -                                        | =                                      | SDMMC<br>1_D7              | DCMI_D<br>1 | LCD_G6        | EVEN<br>TOUT |

|        | PC8  | TRACE<br>D1 | -      | TIM3_C<br>H3 | TIM8_<br>CH3                    | -                  | -                  | -                         | UART5_<br>RTS                               | USART6<br>_CK                                   | -                                          | -                                        | -                                      | SDMMC<br>1_D0              | DCMI_D<br>2 | -             | EVEN<br>TOUT |

| Port C | PC9  | MCO2        | -      | TIM3_C<br>H4 | TIM8_<br>CH4                    | I2C3_SD<br>A       | I2S_CKI<br>N       | -                         | UART5_<br>CTS                               | -                                               | QUADSP<br>I_BK1_IO<br>0                    | -                                        | -                                      | SDMMC<br>1_D1              | DCMI_D<br>3 | -             | EVEN<br>TOUT |

|        | PC10 | -           | -      | -            | -                               | -                  | -                  | SPI3_SC<br>K/I2S3_<br>CK  | USART3<br>_TX                               | UART4_T<br>X                                    | QUADSP<br>I_BK1_IO<br>1                    | -                                        | -                                      | SDMMC<br>1_D2              | DCMI_D<br>8 | LCD_R2        | EVEN<br>TOUT |

|        | PC11 | -           | -      | -            | -                               | -                  | -                  | SPI3_MI<br>SO             | USART3<br>_RX                               | UART4_<br>RX                                    | QUADSP<br>I_BK2_N<br>CS                    | -                                        | -                                      | SDMMC<br>1_D3              | DCMI_D<br>4 | -             | EVEN<br>TOUT |

|        | PC12 | TRACE<br>D3 | -      | -            | -                               | -                  | -                  | SPI3_M<br>OSI/I2S3<br>_SD | USART3<br>_CK                               | UART5_T<br>X                                    | -                                          | -                                        | -                                      | SDMMC<br>1_CK              | DCMI_D<br>9 | -             | EVEN<br>TOUT |

|        | PC13 | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | -,          | -,            | EVEN<br>TOUT |

|        | PC14 | 1           | ı      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | ı           | -             | EVEN<br>TOUT |

|        | PC15 | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | -           | -             | EVEN<br>TOUT |

Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

|        |      |     |        |          | 2. 3 I WI32                     |                    |                    |               |                                             |                                                 |                                            |                                          | (               | /                          |      |        |              |

|--------|------|-----|--------|----------|---------------------------------|--------------------|--------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|-----------------|----------------------------|------|--------|--------------|

|        |      | AF0 | AF1    | AF2      | AF3                             | AF4                | AF5                | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11            | AF12                       | AF13 | AF14   | AF15         |

| Po     | ort  | sys | TIM1/2 | TIM3/4/5 | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI | LCD    | sys          |

|        | PJ7  | -   | -      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_G0 | EVEN<br>TOUT |

|        | PJ8  | -   | -      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_G1 | EVEN<br>TOUT |

|        | PJ9  | -   | -      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_G2 | EVEN<br>TOUT |

|        | PJ10 | -   | ı      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | 1                                          | -                                        | -               | -                          | -    | LCD_G3 | EVEN<br>TOUT |

| Port J | PJ11 | -   | -      | -        | -                               | -                  | -                  | i             | -                                           | -                                               | ı                                          | -                                        | -               | -                          | -    | LCD_G4 | EVEN<br>TOUT |

|        | PJ12 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B0 | EVEN<br>TOUT |

|        | PJ13 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B1 | EVEN<br>TOUT |

|        | PJ14 | -   | -      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B2 | EVEN<br>TOUT |

|        | PJ15 | -   | -      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B3 | EVEN<br>TOUT |

Table 32. Typical and maximum current consumptions in Standby mode

|          |                |                                                                |                                                           | Typ <sup>(1)</sup>         |                         |                         | Max <sup>(2)</sup>     |                         |      |

|----------|----------------|----------------------------------------------------------------|-----------------------------------------------------------|----------------------------|-------------------------|-------------------------|------------------------|-------------------------|------|

| Symbol   | Parameter      | Conditions                                                     | Т                                                         | <sub>A</sub> = 25 °        | C                       | T <sub>A</sub> = 25 °C  | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|          |                |                                                                | V <sub>DD</sub> = 1.7 V                                   | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> = 3.3 V | V <sub>DD</sub> = 3.3 V |                        |                         |      |

|          |                | Backup SRAM OFF, RTC and LSE OFF                               | 1.7                                                       | 1.9                        | 2.3                     | 5 <sup>(3)</sup>        | 15 <sup>(3)</sup>      | 31 <sup>(3)</sup>       |      |

|          |                | Backup SRAM ON, RTC and LSE OFF                                | 2.4                                                       | 2.6                        | 3.0                     | 6 <sup>(3)</sup>        | 20 <sup>(3)</sup>      | 40 <sup>(3)</sup>       |      |

|          |                | Backup SRAM OFF, RTC ON and LSE in low drive mode              | 2.1                                                       | 2.4                        | 2.9                     | 6                       | 19                     | 39                      |      |

|          | Supply current | Backup SRAM OFF, RTC ON and LSE in medium low drive mode       | 2.1                                                       | 2.4                        | 2.9                     | 6                       | 19                     | 39                      |      |

| Inn orny |                | Supply current in Standby                                      | Backup SRAM OFF, RTC ON and LSE in medium high drive mode | 2.2                        | 2.5                     | 3.0                     | 7                      | 20                      | 40   |

| 2187 מחי | mode           | Backup SRAM OFF, RTC ON and LSE in high drive mode             | 2.3                                                       | 2.6                        | 3.1                     | 7                       | 20                     | 42                      | μΛ   |

|          |                | Backup SRAM ON, RTC ON and LSE in low drive mode               | 2.7                                                       | 3.0                        | 3.6                     | 8                       | 23                     | 49                      |      |

|          |                | Backup SRAM ON, RTC ON and LSE in Medium low drive mode        | 2.7                                                       | 3.0                        | 3.6                     | 8                       | 23                     | 49                      |      |

|          |                | Backup SRAM ON, RTC ON<br>and LSE in Medium high drive<br>mode |                                                           | 3.1                        | 3.7                     | 8                       | 24                     | 50                      |      |

|          |                | Backup SRAM ON, RTC ON and LSE in High drive mode              | 2.9                                                       | 3.2                        | 3.8                     | 8                       | 25                     | 51                      |      |

<sup>1.</sup> PDR is OFF for  $V_{DD}$ =1.7V. When the PDR is OFF (internal reset OFF), the typical current consumption is reduced by additional 1.2  $\mu$ A.

<sup>2.</sup> Guaranteed by characterization results.

<sup>3.</sup> Based on characterization, tested in production.

| Symbol                   | Parameter                               | Conditions                                  | Min | Тур | Max  | Unit |

|--------------------------|-----------------------------------------|---------------------------------------------|-----|-----|------|------|

|                          | LSEDRV[1:0]=00  Low drive capability    |                                             | -   | -   | 0.48 |      |

| G crit may               | Maximum critical crystal g <sub>m</sub> | LSEDRV[1:0]=10 Medium low drive capability  | -   | -   | 0.75 | μΑ/V |

| G <sub>m</sub> _crit_max | Maximum chilical crystal g <sub>m</sub> | LSEDRV[1:0]=01 Medium high drive capability | -   | -   | 1.7  | μΑνν |

|                          |                                         | LSEDRV[1:0]=11 High drive capability        | -   | -   | 2.7  |      |

| t <sub>SU</sub> (2)      | start-up time                           | V <sub>DD</sub> is stabilized               | -   | 2   | -    | s    |

Table 40. LSE oscillator characteristics ( $f_{LSE}$  = 32.768 kHz) <sup>(1)</sup> (continued)

Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

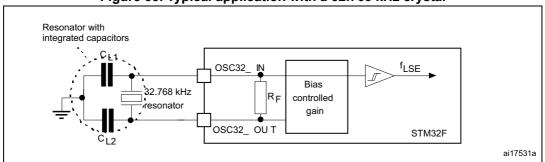

Figure 33. Typical application with a 32.768 kHz crystal

4

<sup>1.</sup> Guaranteed by design.

Guaranteed by characterization results. t<sub>SU</sub> is the start-up time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

Table 56. I/O static characteristics (continued)

| Symbol                         | Parar                                           | neter                                                                | Conditions                                                       | Min                                                                          | Тур | Max | Unit |

|--------------------------------|-------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------|-----|-----|------|

|                                | FT, TTa and NR high level voltage               |                                                                      | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                     | 0.45V <sub>DD</sub> +0.3 <sup>(1)</sup><br>0.7V <sub>DD</sub> <sup>(2)</sup> | -   | -   |      |

| V <sub>IH</sub>                | BOOT I/O input                                  | high level                                                           | 1.75 V≤V <sub>DD</sub> ≤3.6 V, −<br>40 °C≤T <sub>A</sub> ≤105 °C | 0.17V <sub>DD</sub> +0.7 <sup>(1)</sup>                                      |     | _   | ٧    |

|                                | voltage                                         |                                                                      | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C     | 0.17 ФДД+0.7                                                                 |     | _   |      |

|                                | FT, TTa and NR hysteresis                       | ST I/O input                                                         | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                     | 10%V <sub>DD</sub> <sup>(3)</sup>                                            | -   | -   |      |

| V <sub>HYS</sub>               | BOOT I/O input                                  | hvetorosis                                                           | 1.75 V≤V <sub>DD</sub> ≤3.6 V, −<br>40 °C≤T <sub>A</sub> ≤105 °C | 0.1                                                                          |     | _   | V    |

|                                | BOOT I/O IIIput                                 | Trysteresis                                                          | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C     |                                                                              |     | _   |      |

|                                | I/O input leakag                                | je current <sup>(4)</sup>                                            | $V_{SS} \leq V_{IN} \leq V_{DD}$                                 | -                                                                            | -   | ±1  |      |

| l <sub>lkg</sub>               | I/O FT input lea                                | kage current                                                         | $V_{IN} = 5 V$                                                   | -                                                                            | -   | 3   | μA   |

| R <sub>PU</sub>                | Weak pull-up equivalent resistor <sup>(6)</sup> | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_ID<br>,OTG_HS_ID<br>) | $V_{IN} = V_{SS}$                                                | 30                                                                           | 40  | 50  |      |

|                                | resistor                                        | PA10/PB12<br>(OTG_FS_ID<br>,OTG_HS_ID<br>)                           |                                                                  | 7                                                                            | 10  | 14  | kΩ   |

| R <sub>PD</sub>                | Weak pull-<br>down<br>equivalent                | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_ID<br>,OTG_HS_ID<br>) | $V_{IN} = V_{DD}$                                                | 30                                                                           | 40  | 50  | NS2  |

|                                | resistor <sup>(7)</sup>                         | PA10/PB12<br>(OTG_FS_ID<br>,OTG_HS_ID<br>)                           |                                                                  | 7                                                                            | 10  | 14  |      |

| C <sub>IO</sub> <sup>(8)</sup> | I/O pin capacita                                | nce                                                                  | -                                                                | -                                                                            | 5   | -   | pF   |

- 1. Guaranteed by design.

- 2. Tested in production.

- 3. With a minimum of 200 mV.

- Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 55: I/O current injection susceptibility

- To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 55: I/O current injection susceptibility

- 6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

| Symbol                           | Parameter                                                      | Conditions | Min | Тур | Max | Unit |

|----------------------------------|----------------------------------------------------------------|------------|-----|-----|-----|------|

| I <sub>VREF+</sub> (2)           | ADC V <sub>REF</sub> DC current consumption in conversion mode | -          | -   | 300 | 500 | μΑ   |

| I <sub>VDDA</sub> <sup>(2)</sup> | ADC V <sub>DDA</sub> DC current consumption in conversion mode | -          | -   | 1.6 | 1.8 | mA   |

Table 62. ADC characteristics (continued)

- V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 2.17.2: Internal reset OFF).

- 2. Guaranteed by characterization results.

- 3.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is internally connected to  $V_{SSA}$ .

- 4.  $R_{ADC}$  maximum value is given for  $V_{DD}$ =1.7 V, and minimum value for  $V_{DD}$ =3.3 V.

- 5. For external triggers, a delay of 1/f<sub>PCI K2</sub> must be added to the latency specified in *Table 62*.

## Equation 1: $R_{AIN}$ max formula

$$R_{AIN} = \frac{(k-0.5)}{f_{ADC} \times C_{ADC} \times ln(2^{N+2})} - R_{ADC}$$

The formula above (Equation 1) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

Table 63. ADC static accuracy at  $f_{ADC} = 18 \text{ MHz}$

|        |                              | <u> </u>                                      | DC - |                    |      |

|--------|------------------------------|-----------------------------------------------|------|--------------------|------|

| Symbol | Parameter                    | Test conditions                               | Тур  | Max <sup>(1)</sup> | Unit |

| ET     | Total unadjusted error       |                                               | ±3   | ±4                 |      |

| EO     | Offset error                 | $f_{ADC}$ =18 MHz<br>$V_{DDA}$ = 1.7 to 3.6 V | ±2   | ±3                 |      |

| EG     | Gain error                   | V <sub>REF</sub> = 1.7 to 3.6 V               | ±1   | ±3                 | LSB  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                   | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                               | ±2   | ±3                 |      |

<sup>1.</sup> Guaranteed by characterization results.

Table 64. ADC static accuracy at f<sub>ADC</sub> = 30 MHz

| Symbol | Parameter                    | Test conditions                                                                | Тур  | Max <sup>(1)</sup> | Unit |

|--------|------------------------------|--------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 30 MHz,<br>R <sub>AIN</sub> < 10 kΩ                         | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | $V_{DDA} = 2.4 \text{ to } 3.6 \text{ V},$                                     | ±1.5 | ±4                 | LSB  |

| ED     | Differential linearity error | V <sub>REF</sub> = 1.7 to 3.6 V,<br>V <sub>DDA</sub> –V <sub>REF</sub> < 1.2 V | ±1   | ±2                 |      |

| EL     | Integral linearity error     | DDA KEI                                                                        | ±1.5 | ±3                 |      |

<sup>1.</sup> Guaranteed by characterization results.

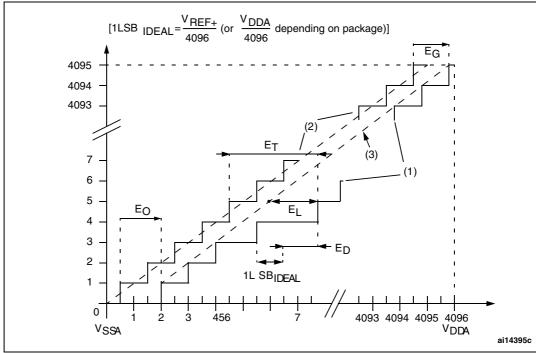

Figure 41. ADC accuracy characteristics

- 1. See also Table 64.

- 2. Example of an actual transfer curve.

- Ideal transfer curve.

- End point correlation line.

- $\mathsf{E}_\mathsf{T}$  = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves.  $\mathsf{EO}$  = Offset Error: deviation between the first actual transition and the first ideal one.

- EG = Gain Error: deviation between the last ideal transition and the last actual one.

- ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

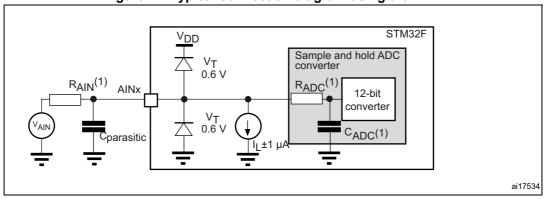

Figure 42. Typical connection diagram using the ADC

- 1. Refer to *Table 62* for the values of R<sub>AIN</sub>, R<sub>ADC</sub> and C<sub>ADC</sub>.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced.

The 20mA output drive requirement in Fast-mode Plus is not supported. This limits the maximum load Cload supported in Fm+, which is given by these formulas:

- Tr(SDA/SCL)=0.8473xR<sub>p</sub>xC<sub>load</sub>

- $R_p(min) = (VDD-V_{OL}(max))/I_{OL}(max)$

Where Rp is the I2C lines pull-up. Refer to *Section 5.3.17: I/O port characteristics* for the I2C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

Table 75. I2C analog filter characteristics<sup>(1)</sup>

| Symbol          | Parameter                                                              | Min               | Max                | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 150 <sup>(3)</sup> | ns   |

- 1. Guaranteed by characterization results.

- 2. Spikes with widths below  $t_{AF(min)}$  are filtered.

- 3. Spikes with widths above  $t_{\text{AF}(\text{max})}$  are not filtered

Table 92. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)</sup>

| Symbol                    | Parameter                                            | Min                       | Max                     | Unit |

|---------------------------|------------------------------------------------------|---------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                                      | 3T <sub>HCLK</sub> -0.5   | 3T <sub>HCLK</sub> +1.5 |      |

| t <sub>v(NOE_NE)</sub>    | FMC_NEx low to FMC_NOE low                           | 2T <sub>HCLK</sub> -1     | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>tw(NOE)</sub>      | FMC_NOE low time                                     | T <sub>HCLK</sub> -0.5    | T <sub>HCLK</sub> +0.5  |      |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time                | 0                         | -                       |      |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                           | -                         | 0.5                     |      |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                          | 0                         | 0.5                     |      |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                    | T <sub>HCLK</sub> -0.5    | T <sub>HCLK</sub> +1.5  |      |

| t <sub>h(AD_NADV)</sub>   | FMC_AD(address) valid hold time after FMC_NADV high) | 0 -                       |                         | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high                 | T <sub>HCLK</sub> -0.5    | -                       | •    |

| t <sub>h(BL_NOE)</sub>    | FMC_BL time after FMC_NOE high                       | 0                         | -                       | •    |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid                          | - 0.5                     |                         | •    |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time                      | T <sub>HCLK</sub> -2 -    |                         | 7    |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOE high setup time                      | T <sub>HCLK</sub> -2 -    |                         |      |

| t <sub>h(Data_NE)</sub>   | Data hold time after FMC_NEx high                    | ne after FMC_NEx high 0 - |                         | •    |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FMC_NOE high                    | 0 -                       |                         |      |

<sup>1.</sup> Guaranteed by characterization results.

Table 93. Asynchronous multiplexed PSRAM/NOR read-NWAIT timings<sup>(1)</sup>

| Symbol                    | Parameter                                 | Min                     | Max                   | Unit |

|---------------------------|-------------------------------------------|-------------------------|-----------------------|------|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> -1   | 8T <sub>HCLK</sub> +2 |      |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                          | 5T <sub>HCLK</sub> −1   | 5T <sub>HCLK</sub> +1 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 5T <sub>HCLK</sub> +1.5 | -                     |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +1   | -                     |      |

<sup>1.</sup> Guaranteed by characterization results.

DocID027590 Rev 4 174/227

#### **Package information** 6

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK® is an ST trademark.

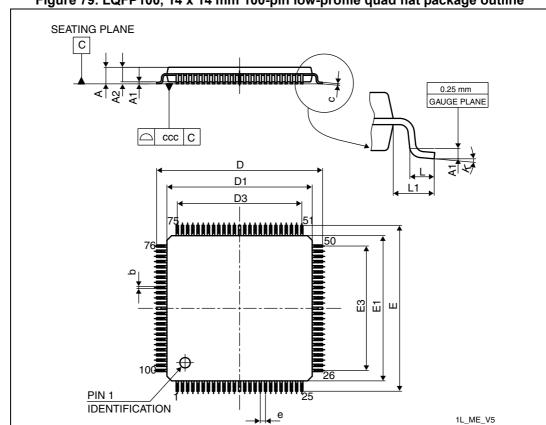

#### LQFP100, 14 x 14 mm low-profile quad flat package 6.1 information

Figure 79. LQFP100, 14 x 14 mm 100-pin low-profile quad flat package outline

1. Drawing is not to scale.

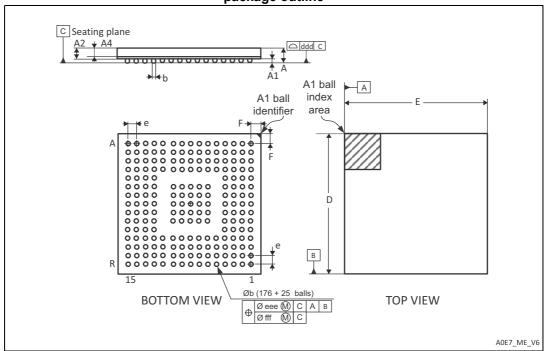

# 6.7 UFBGA 176+25, 10 x 10 x 0.65 mm ultra thin-pitch ball grid array package information

Figure 97. UFBGA 176+25, 10 × 10 × 0.65 mm ultra thin fine-pitch ball grid array package outline

1. Drawing is not to scale.

Table 120. UFBGA 176+25, 10 × 10 × 0.65 mm ultra thin fine-pitch ball grid array package mechanical data

|          |             | packag | je iliecilaliici      | ui uutu |        |        |

|----------|-------------|--------|-----------------------|---------|--------|--------|

| Symbol - | millimeters |        | inches <sup>(1)</sup> |         |        |        |

|          | Min         | Тур    | Max                   | Min     | Тур    | Max    |

| Α        | 0.460       | 0.530  | 0.600                 | 0.0181  | 0.0209 | 0.0236 |

| A1       | 0.050       | 0.080  | 0.110                 | 0.002   | 0.0031 | 0.0043 |

| A2       | 0.400       | 0.450  | 0.500                 | 0.0157  | 0.0177 | 0.0197 |

| b        | 0.230       | 0.280  | 0.330                 | 0.0091  | 0.0110 | 0.0130 |

| D        | 9.950       | 10.000 | 10.050                | 0.3917  | 0.3937 | 0.3957 |

| Е        | 9.950       | 10.000 | 10.050                | 0.3917  | 0.3937 | 0.3957 |

| е        | -           | 0.650  | -                     | -       | 0.0256 | -      |

| F        | 0.400       | 0.450  | 0.500                 | 0.0157  | 0.0177 | 0.0197 |

| ddd      | -           | -      | 0.080                 | -       | -      | 0.0031 |

| eee      | -           | -      | 0.150                 | -       | -      | 0.0059 |

| fff      | -           | -      | 0.080                 | -       | -      | 0.0031 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

#### 6.9 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$

#### Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Θ<sub>JA</sub> is the package junction-to-ambient thermal resistance, in ° C/W,

- $P_D$  max is the sum of  $P_{INT}$  max and  $P_{I/O}$  max ( $P_D$  max =  $P_{INT}$  max +  $P_{I/O}$ max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$$\mathsf{P}_{\mathsf{I/O}} \; \mathsf{max} = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$$

taking into account the actual  $V_{OL}$  /  $I_{OL}$  and  $V_{OH}$  /  $I_{OH}$  of the I/Os at low and high level in the application.

| Symbol            | Parameter Value                                                             |      | Unit |  |

|-------------------|-----------------------------------------------------------------------------|------|------|--|

| $\Theta_{\sf JA}$ | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch  | 43   |      |  |

|                   | Thermal resistance junction-ambient TFBGA100 - 8 × 8 mm / 0.8 mm pitch      | 57   |      |  |

|                   | Thermal resistance junction-ambient WLCSP143                                | 31.2 |      |  |

|                   | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm / 0.5 mm pitch  | 40   | °C/W |  |

|                   | Thermal resistance junction-ambient<br>LQFP176 - 24 × 24 mm / 0.5 mm pitch  | 38   | C/VV |  |

|                   | Thermal resistance junction-ambient<br>LQFP208 - 28 × 28 mm / 0.5 mm pitch  | 19   |      |  |

|                   | Thermal resistance junction-ambient<br>UFBGA176 - 10 × 10 mm / 0.5 mm pitch | 39   |      |  |

|                   | Thermal resistance junction-ambient<br>TFBGA216 - 13 × 13 mm / 0.8 mm pitch | 29   |      |  |

Table 124. Package thermal characteristics

#### Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

222/227 DocID027590 Rev 4