Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 140                                                                                                    |

| Program Memory Size        | 1MB (1M x 8)                                                                                           |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320K x 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                      |

| Mounting Type              | Surface Mount                                                                                          |

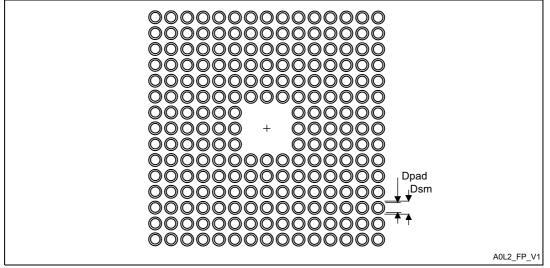

| Package / Case             | 201-UFBGA                                                                                              |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f746igk6                                  |

|                            |                                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

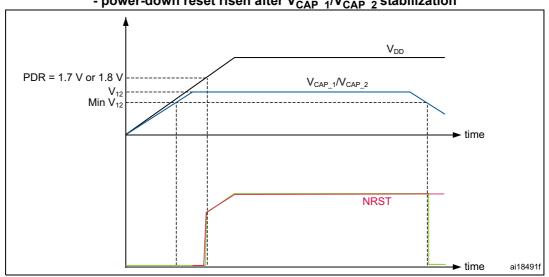

### Figure 9. Startup in regulator OFF: slow $V_{DD}$ slope - power-down reset risen after $V_{CAP}$ $_1/V_{CAP}$ $_2$ stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

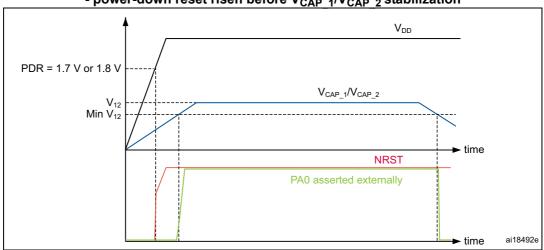

Figure 10. Startup in regulator OFF mode: fast V<sub>DD</sub> slope - power-down reset risen before  $V_{CAP_1}/V_{CAP_2}$  stabilization

1. This figure is valid whatever the internal reset mode (ON or OFF).

## 2.18.3 Regulator ON/OFF and internal reset ON/OFF availability

| Table                                                       | 4. Regulator ON/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | OFF and internal                            | reset ON/OFF ava                        | anability                   |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------|-----------------------------|

| Package                                                     | Regulator ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Regulator OFF                               | Internal reset ON                       | Internal reset OFF          |

| LQFP100                                                     | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | No                                          | Yes                                     | No                          |

| LQFP144,<br>LQFP208                                         | The second secon | No                                          |                                         |                             |

| TFBGA100,<br>LQFP176,<br>WLCSP143,<br>UFBGA176,<br>TFBGA216 | Yes<br>BYPASS_REG set<br>to V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Yes<br>BYPASS_REG set<br>to V <sub>DD</sub> | Yes<br>PDR_ON set to<br>V <sub>DD</sub> | Yes<br>PDR_ON set to<br>VSS |

Table 4. Regulator ON/OFF and internal reset ON/OFF availability

# 2.19 Real-time clock (RTC), backup SRAM and backup registers

The RTC is an independent BCD timer/counter. It supports the following features:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28, 29 (leap year), 30, and 31 days of the month.

- Two programmable alarms.

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 0.95 ppm resolution, to compensate for quartz crystal inaccuracy.

- Three anti-tamper detection pins with programmable filter.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event, or by a switch to V<sub>BAT</sub> mode.

- 17-bit auto-reload wakeup timer (WUT) for periodic events with programmable resolution and period.

The RTC and the 32 backup registers are supplied through a switch that takes power either from the  $V_{\text{DD}}$  supply when present or from the  $V_{\text{BAT}}$  pin.

The backup registers are 32-bit registers used to store 128 bytes of user application data when VDD power is not present. They are not reset by a system or power reset, or when the device wakes up from Standby mode.

The RTC clock sources can be:

- A 32.768 kHz external crystal (LSE)

- An external resonator or oscillator(LSE)

- The internal low-power RC oscillator (LSI, with typical frequency of 32 kHz)

- The high-speed external clock (HSE) divided by 32.

|         |          |          |         | umber    |         |         |          |                                                            |          |               |       | ball definition (continue                                                             |                                         |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------|-----------------------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                   | Additional<br>functions                 |

| _       | -        | H11      | 20      | L3       | 26      | 29      | L3       | PF8                                                        | I/O      | FT            | -     | SPI5_MISO,<br>SAI1_SCK_B,<br>UART7_RTS,<br>TIM13_CH1,<br>QUADSPI_BK1_IO0,<br>EVENTOUT | ADC3_IN6                                |

| -       | -        | G8       | 21      | L2       | 27      | 30      | L2       | PF9                                                        | I/O      | FT            | -     | SPI5_MOSI, SAI1_FS_B,<br>UART7_CTS,<br>TIM14_CH1,<br>QUADSPI_BK1_IO1,<br>EVENTOUT     | ADC3_IN7                                |

| -       | -        | G9       | 22      | L1       | 28      | 31      | L1       | PF10                                                       | I/O      | FT            | -     | DCMI_D11, LCD_DE,<br>EVENTOUT                                                         | ADC3_IN8                                |

| 12      | C1       | J11      | 23      | G1       | 29      | 32      | G1       | PH0-<br>OSC_IN(<br>PH0)                                    | I/O      | FT            | -     | EVENTOUT                                                                              | OSC_IN <sup>(4)</sup>                   |

| 13      | D1       | H10      | 24      | H1       | 30      | 33      | H1       | PH1-<br>OSC_OU<br>T(PH1)                                   | I/O      | FT            | -     | EVENTOUT                                                                              | OSC_OUT <sup>(4)</sup>                  |

| 14      | E1       | H9       | 25      | J1       | 31      | 34      | J1       | NRST                                                       | I/O      | RS<br>T       | -     | -                                                                                     | -                                       |

| 15      | F1       | H8       | 26      | M2       | 32      | 35      | M2       | PC0                                                        | I/O      | FT            | (4)   | SAI2_FS_B,<br>OTG_HS_ULPI_STP,<br>FMC_SDNWE, LCD_R5,<br>EVENTOUT                      | ADC123_IN1<br>0                         |

| 16      | F2       | K11      | 27      | М3       | 33      | 36      | М3       | PC1                                                        | I/O      | FT            | (4)   | TRACED0,<br>SPI2_MOSI/I2S2_SD,<br>SAI1_SD_A, ETH_MDC,<br>EVENTOUT                     | ADC123_IN1<br>1,<br>RTC_TAMP3,<br>WKUP3 |

| 17      | E2       | J10      | 28      | M4       | 34      | 37      | M4       | PC2                                                        | I/O      | FT            | (4)   | SPI2_MISO,<br>OTG_HS_ULPI_DIR,<br>ETH_MII_TXD2,<br>FMC_SDNE0,<br>EVENTOUT             | ADC123_IN1<br>2                         |

### Table 10. STM32F745xx and STM32F746xx pin and ball definition (continued)

| Pin Number |          |          |         |          |         |         |          |                                                            | P C      |               | ball definition (continue | ,                                                                |                         |

|------------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|---------------------------|------------------------------------------------------------------|-------------------------|

| LQFP100    | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes                     | Alternate functions                                              | Additional<br>functions |

| -          | -        | -        | -       | -        | -       | 67      | P7       | PJ2                                                        | I/O      | FT            | -                         | LCD_R3, EVENTOUT                                                 | -                       |

| -          | -        | -        | -       | -        | -       | 68      | N8       | PJ3                                                        | I/O      | FT            | -                         | LCD_R4, EVENTOUT                                                 | -                       |

| -          | -        | -        | -       | -        | -       | 69      | M9       | PJ4                                                        | I/O      | FT            | -                         | LCD_R5, EVENTOUT                                                 | -                       |

| -          | -        | M7       | 49      | R6       | 59      | 70      | P8       | PF11                                                       | I/O      | FT            | -                         | SPI5_MOSI, SAI2_SD_B,<br>FMC_SDNRAS,<br>DCMI_D12, EVENTOUT       | -                       |

| -          | -        | N7       | 50      | P6       | 60      | 71      | M6       | PF12                                                       | I/O      | FT            | -                         | FMC_A6, EVENTOUT                                                 | -                       |

| -          | -        | -        | 51      | M8       | 61      | 72      | K7       | VSS                                                        | S        | -             | -                         | -                                                                | -                       |

| -          | -        | -        | 52      | N8       | 62      | 73      | L8       | VDD                                                        | S        | -             | -                         | -                                                                | -                       |

| -          | -        | K6       | 53      | N6       | 63      | 74      | N6       | PF13                                                       | I/O      | FT            | -                         | I2C4_SMBA, FMC_A7,<br>EVENTOUT                                   | -                       |

| -          | -        | L6       | 54      | R7       | 64      | 75      | P6       | PF14                                                       | I/O      | FT            | -                         | I2C4_SCL, FMC_A8,<br>EVENTOUT                                    | -                       |

| -          | -        | M6       | 55      | P7       | 65      | 76      | M8       | PF15                                                       | I/O      | FT            | -                         | I2C4_SDA, FMC_A9,<br>EVENTOUT                                    | -                       |

| -          | -        | N6       | 56      | N7       | 66      | 77      | N7       | PG0                                                        | I/O      | FT            | -                         | FMC_A10, EVENTOUT                                                | -                       |

| -          | -        | K5       | 57      | M7       | 67      | 78      | M7       | PG1                                                        | I/O      | FT            | -                         | FMC_A11, EVENTOUT                                                | -                       |

| 37         | H5       | L5       | 58      | R8       | 68      | 79      | R8       | PE7                                                        | I/O      | FT            | -                         | TIM1_ETR, UART7_Rx,<br>QUADSPI_BK2_IO0,<br>FMC_D4, EVENTOUT      | -                       |

| 38         | J5       | M5       | 59      | P8       | 69      | 80      | N9       | PE8                                                        | I/O      | FT            | -                         | TIM1_CH1N, UART7_Tx,<br>QUADSPI_BK2_IO1,<br>FMC_D5, EVENTOUT     | -                       |

| 39         | K5       | N5       | 60      | P9       | 70      | 81      | P9       | PE9                                                        | I/O      | FT            | -                         | TIM1_CH1, UART7_RTS,<br>QUADSPI_BK2_IO2,<br>FMC_D6, EVENTOUT     | -                       |

| -          | -        | H3       | 61      | M9       | 71      | 82      | K8       | VSS                                                        | S        | -             | I                         | -                                                                | -                       |

| -          | -        | J5       | 62      | N9       | 72      | 83      | L9       | VDD                                                        | S        | -             | -                         | -                                                                | -                       |

| 40         | G6       | J4       | 63      | R9       | 73      | 84      | R9       | PE10                                                       | I/O      | FT            | -                         | TIM1_CH2N,<br>UART7_CTS,<br>QUADSPI_BK2_IO3,<br>FMC_D7, EVENTOUT | -                       |

| Table 10. STM32F745xx and STM32F746xx pin and ball definition (c | continued) |

|------------------------------------------------------------------|------------|

|                                                                  |            |

|         |          |          |         |          |         |         |          |                                                                                                                          |          | pin c         |       | ball definition (continue                                                                                                            | eu)                     |

|---------|----------|----------|---------|----------|---------|---------|----------|--------------------------------------------------------------------------------------------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         |          |          | Pin Nı  | umbei    | ·       |         |          |                                                                                                                          |          |               |       |                                                                                                                                      |                         |

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup>                                                               | Pin type | I/O structure | Notes | Alternate functions                                                                                                                  | Additional<br>functions |

| -       | _        | E5       | 124     | C10      | 152     | 178     | D9       | PG9 I/O FT - SPDIFRX_IN3,<br>USART6_RX,<br>QUADSPI_BK2_IO2,<br>SAI2_FS_B,<br>FMC_NE2/FMC_NCE,<br>DCMI_VSYNC,<br>EVENTOUT |          | -             |       |                                                                                                                                      |                         |

| -       | -        | C6       | 125     | B10      | 153     | 179     | C8       | PG10                                                                                                                     | I/O      | FT            | -     | LCD_G3, SAI2_SD_B,<br>FMC_NE3, DCMI_D2,<br>LCD_B2, EVENTOUT                                                                          | -                       |

| -       |          | B6       | 126     | В9       | 154     | 180     | B8       | PG11                                                                                                                     | I/O      | FT            | -     | SPDIFRX_IN0,<br>ETH_MII_TX_EN/ETH_R<br>MII_TX_EN, DCMI_D3,<br>LCD_B3, EVENTOUT                                                       | -                       |

| -       | -        | A6       | 127     | B8       | 155     | 181     | C7       | PG12                                                                                                                     | I/O      | FT            | -     | LPTIM1_IN1,<br>SPI6_MISO,<br>SPDIFRX_IN1,<br>USART6_RTS, LCD_B4,<br>FMC_NE4, LCD_B1,<br>EVENTOUT                                     | -                       |

| -       | _        | D6       | 128     | A8       | 156     | 182     | В3       | PG13                                                                                                                     | I/O      | FT            | -     | TRACED0, LPTIM1_OUT,<br>SPI6_SCK,<br>USART6_CTS,<br>ETH_MII_TXD0/ETH_RM<br>II_TXD0, FMC_A24,<br>LCD_R0, EVENTOUT                     | -                       |

| -       | -        | F6       | 129     | A7       | 157     | 183     | A4       | PG14                                                                                                                     | I/O      | FT            | -     | TRACED1, LPTIM1_ETR,<br>SPI6_MOSI,<br>USART6_TX,<br>QUADSPI_BK2_IO3,<br>ETH_MII_TXD1/ETH_RM<br>II_TXD1, FMC_A25,<br>LCD_B0, EVENTOUT | -                       |

| -       | -        | -        | 130     | D7       | 158     | 184     | F7       | VSS                                                                                                                      | S        | -             | -     | -                                                                                                                                    | -                       |

| -       | -        | E6       | 131     | C7       | 159     | 185     | E8       | VDD                                                                                                                      | S        | -             | -     | -                                                                                                                                    | -                       |

| Table 10. STM32F745xx and STM32F746xx pin and ball definition ( | continued) |

|-----------------------------------------------------------------|------------|

|                                                                 |            |

| 8 <u>3</u> |  |

|------------|--|

| Ñ          |  |

| 22         |  |

DocID027590 Rev 4

577

|        |      | AF0 | AF1    | AF2      | AF3                             | AF4                | AF5                | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11            | AF12                       | AF13           | AF14        | AF15         |

|--------|------|-----|--------|----------|---------------------------------|--------------------|--------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|-----------------|----------------------------|----------------|-------------|--------------|

| Po     | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI           | LCD         | SYS          |

|        | PF13 | -   | -      | -        | -                               | I2C4_SM<br>BA      | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A7                     | -              | -           | EVEN<br>TOUT |

| Port F | PF14 | -   | -      | -        | -                               | I2C4_SC<br>L       | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A8                     | -              | -           | EVEN<br>TOUT |

|        | PF15 | -   | -      | -        | -                               | I2C4_SD<br>A       | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A9                     | -              | -           | EVEN<br>TOUT |

|        | PG0  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>0                | -              | -           | EVEN<br>TOUT |

|        | PG1  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>1                | -              | -           | EVEN<br>TOUT |

|        | PG2  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>2                | -              | -           | EVEN<br>TOUT |

|        | PG3  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>3                | -              | -           | EVEN<br>TOUT |

|        | PG4  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>4/FMC_<br>BA0    | -              | -           | EVEN<br>TOUT |

| Port G | PG5  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>5/FMC_<br>BA1    | -              | -           | EVEN<br>TOUT |

|        | PG6  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | DCMI_D<br>12   | LCD_R7      | EVEN<br>TOUT |

|        | PG7  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | USART6<br>_CK                                   | -                                          | -                                        | -               | FMC_IN<br>T                | DCMI_D<br>13   | LCD_CL<br>K | EVEN<br>TOUT |

|        | PG8  | -   | -      | -        | -                               | -                  | SPI6_NS<br>S       | -             | SPDIFRX<br>_IN2                             | USART6<br>_RTS                                  | -                                          | -                                        | ETH_PPS<br>_OUT | FMC_SD<br>CLK              | -              | -           | EVEN<br>TOUT |

|        | PG9  | -   | -      | -        | -                               | -                  | -                  | -             | SPDIFRX<br>_IN3                             | USART6<br>_RX                                   | QUADSP<br>I_BK2_IO<br>2                    | SAI2_FS_<br>B                            | -               | FMC_NE<br>2/FMC_<br>NCE    | DCMI_V<br>SYNC | -           | EVEN<br>TOUT |

|        | PG10 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | LCD_G3                                     | SAI2_SD_<br>B                            | -               | FMC_NE<br>3                | DCMI_D<br>2    | LCD_B2      | EVEN<br>TOUT |

Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

| Symbol                              | Parameter                                                                           | Conditions                                                                                | Min  | Тур                                                                                                                                                                                                                                                                                                                                                                                     | Мах  | Unit |

|-------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

|                                     |                                                                                     | PLS[2:0]=000 (rising edge)                                                                | 2.09 | 2.14                                                                                                                                                                                                                                                                                                                                                                                    | 2.19 | V    |

|                                     |                                                                                     | PLS[2:0]=000 (falling edge)                                                               | 1.98 | 2.04                                                                                                                                                                                                                                                                                                                                                                                    | 2.08 | V    |

|                                     |                                                                                     | PLS[2:0]=001 (rising edge)                                                                | 2.23 | 2.30                                                                                                                                                                                                                                                                                                                                                                                    | 2.37 | V    |

|                                     |                                                                                     | PLS[2:0]=001 (falling edge)                                                               | 2.13 | 2.19                                                                                                                                                                                                                                                                                                                                                                                    | 2.25 | V    |

|                                     |                                                                                     | PLS[2:0]=010 (rising edge)                                                                | 2.39 | 2.45                                                                                                                                                                                                                                                                                                                                                                                    | 2.51 | V    |

|                                     |                                                                                     | PLS[2:0]=010 (falling edge)                                                               | 2.29 | 2.35                                                                                                                                                                                                                                                                                                                                                                                    | 2.39 | V    |

|                                     |                                                                                     | PLS[2:0]=011 (rising edge)                                                                | 2.54 | 2.60                                                                                                                                                                                                                                                                                                                                                                                    | 2.65 | V    |

| M                                   | Programmable voltage                                                                | PLS[2:0]=011 (falling edge)                                                               | 2.44 | 2.51                                                                                                                                                                                                                                                                                                                                                                                    | 2.56 | V    |

| V <sub>PVD</sub>                    | detector level selection                                                            | PLS[2:0]=100 (rising edge)                                                                | 2.70 | 2.76                                                                                                                                                                                                                                                                                                                                                                                    | 2.82 | V    |

|                                     |                                                                                     | PLS[2:0]=100 (falling edge)                                                               | 2.59 | 2.66                                                                                                                                                                                                                                                                                                                                                                                    | 2.71 | V    |

|                                     |                                                                                     | PLS[2:0]=101 (rising edge)                                                                | 2.86 | 2.93                                                                                                                                                                                                                                                                                                                                                                                    | 2.99 | V    |

|                                     |                                                                                     | PLS[2:0]=101 (falling edge)                                                               | 2.65 | 2.84                                                                                                                                                                                                                                                                                                                                                                                    | 2.92 | V    |

|                                     |                                                                                     | PLS[2:0]=110 (rising edge)                                                                | 2.96 | 2.04       2.08       V         2.30       2.37       V         2.19       2.25       V         2.45       2.51       V         2.35       2.39       V         2.60       2.65       V         2.51       2.56       V         2.60       2.65       V         2.51       2.56       V         2.51       2.56       V         2.66       2.71       V         2.93       2.99       V |      |      |

|                                     |                                                                                     | PLS[2:0]=110 (falling edge)                                                               | 2.85 | 2.93                                                                                                                                                                                                                                                                                                                                                                                    | 2.99 | V    |

| V <sub>POR/PDR</sub> F              |                                                                                     | PLS[2:0]=111 (rising edge)                                                                | 3.07 | 3.14                                                                                                                                                                                                                                                                                                                                                                                    | 3.21 | V    |

|                                     |                                                                                     | PLS[2:0]=111 (falling edge)                                                               | 2.95 | 3.03                                                                                                                                                                                                                                                                                                                                                                                    | 3.09 | V    |

| V <sub>PVDhyst</sub> <sup>(1)</sup> | PVD hysteresis                                                                      | -                                                                                         | -    | 100                                                                                                                                                                                                                                                                                                                                                                                     | -    | mV   |

| V                                   | _ Power-on/power-down                                                               | ower-on/power-down Falling edge 1.0                                                       |      |                                                                                                                                                                                                                                                                                                                                                                                         |      | V    |

| V POR/PDR                           | reset threshold                                                                     | Rising edge                                                                               | 1.64 | 1.72                                                                                                                                                                                                                                                                                                                                                                                    | 1.80 | V    |

| V <sub>PDRhyst</sub> <sup>(1)</sup> | PDR hysteresis                                                                      | -                                                                                         | -    | 40                                                                                                                                                                                                                                                                                                                                                                                      | -    | mV   |

|                                     | Brownout level 1                                                                    | Falling edge                                                                              | 2.13 | 2.19                                                                                                                                                                                                                                                                                                                                                                                    | 2.24 | V    |

| V <sub>BOR1</sub>                   | threshold                                                                           | Rising edge                                                                               | 2.23 | 2.29                                                                                                                                                                                                                                                                                                                                                                                    | 2.33 | V    |

| V                                   | Brownout level 2                                                                    | Falling edge                                                                              | 2.44 | 2.50                                                                                                                                                                                                                                                                                                                                                                                    | 2.56 | V    |

| V <sub>BOR2</sub>                   | threshold                                                                           | Rising edge                                                                               | 2.53 | 2.59                                                                                                                                                                                                                                                                                                                                                                                    | 2.63 | V    |

| V                                   | Brownout level 3                                                                    | Falling edge                                                                              | 2.75 | 2.83                                                                                                                                                                                                                                                                                                                                                                                    | 2.88 | V    |

| V <sub>BOR3</sub>                   | threshold                                                                           | Rising edge                                                                               | 2.85 | 2.92                                                                                                                                                                                                                                                                                                                                                                                    | 2.97 | V    |

| V <sub>BORhyst</sub> <sup>(1)</sup> | BOR hysteresis                                                                      | -                                                                                         | -    | 100                                                                                                                                                                                                                                                                                                                                                                                     | -    | mV   |

| T <sub>RSTTEMPO</sub>               | POR reset temporization                                                             | -                                                                                         | 0.5  | 1.5                                                                                                                                                                                                                                                                                                                                                                                     | 3.0  | ms   |

| I <sub>RUSH</sub> <sup>(1)</sup>    | InRush current on<br>voltage regulator power-<br>on (POR or wakeup<br>from Standby) | -                                                                                         | -    | 160                                                                                                                                                                                                                                                                                                                                                                                     | 250  | mA   |

| E <sub>RUSH</sub> <sup>(1)</sup>    | InRush energy on<br>voltage regulator power-<br>on (POR or wakeup<br>from Standby)  | V <sub>DD</sub> = 1.7 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -    | -                                                                                                                                                                                                                                                                                                                                                                                       | 5.4  | μC   |

| Table 22. reset and power control block characteristics |

|---------------------------------------------------------|

|---------------------------------------------------------|

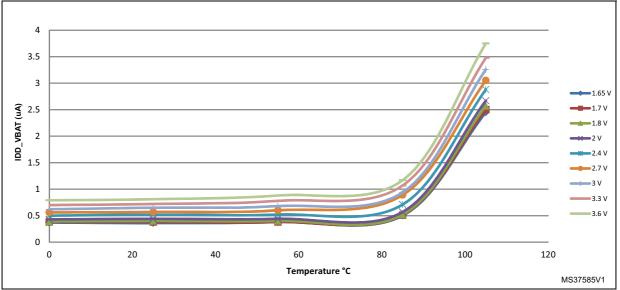

Figure 25. Typical V<sub>BAT</sub> current consumption (RTC ON/BKP SRAM OFF and LSE in low drive mode)

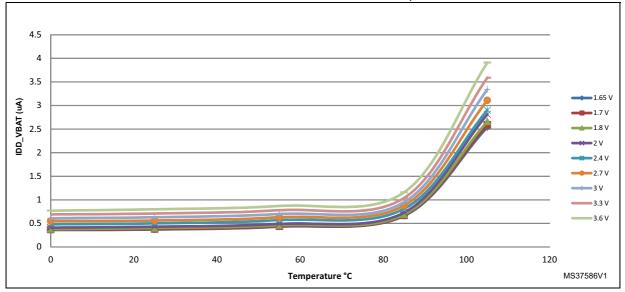

Figure 26. Typical V<sub>BAT</sub> current consumption (RTC ON/BKP SRAM OFF and LSE in medium low drive mode)

### 5.3.15 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts × (n+1) supply pins). This test conforms to the ANSI/ESDA/JEDEC JS-001-2012 and ANSI/ESD S5.3.1-2009 standards.

| Symbol                | Ratings                                               | Conditions                                                                                                                                            | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge voltage (human body model)    | T <sub>A</sub> = +25 °C conforming to<br>ANSI/ESDA/JEDEC JS-001-2012                                                                                  | 2     | 2000                            |      |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model) | $T_A$ = +25 °C conforming to ANSI/ESD<br>S5.3.1-2009, LQFP100, LQFP144,<br>LQFP176, LQFP208, WLCSP143,<br>UFBGA176, TFBGA100 and TFBGA216<br>packages | C3    | 250                             | V    |

#### Table 53. ESD absolute maximum ratings

1. Guaranteed by characterization results.

#### Static latchup

Two complementary static tests are required on six parts to assess the latchup performance:

- A supply overvoltage is applied to each power supply pin

- A current injection is applied to each input, output and configurable I/O pin

These tests are compliant with EIA/JESD 78A IC latchup standard.

#### Table 54. Electrical sensitivities

| Symbol | Parameter             | Conditions                                    | Class      |

|--------|-----------------------|-----------------------------------------------|------------|

| LU     | Static latch-up class | $T_A = +105 \text{ °C conforming to JESD78A}$ | II level A |

#### 5.3.16 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

| Symbol | Parameter                    | Test conditions                                                     | Тур | Max <sup>(1)</sup> | Unit |

|--------|------------------------------|---------------------------------------------------------------------|-----|--------------------|------|

| ET     | Total unadjusted error       |                                                                     | ±4  | ±7                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,       | ±2  | ±3                 |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REF</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                         | ±2  | ±3                 |      |

| EL     | Integral linearity error     |                                                                     | ±3  | ±6                 |      |

Table 65. ADC static accuracy at f<sub>ADC</sub> = 36 MHz

1. Guaranteed by characterization results.

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =18 MHz     | 10.3 | 10.4 | -   | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+} = 1.7 V$ | 64   | 64.2 | -   |      |

| SNR    | Signal-to-noise ratio                | Input Frequency = 20 KHz     | 64   | 65   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 67 | - 72 | -   |      |

1. Guaranteed by characterization results.

# Table 67. ADC dynamic accuracy at $f_{ADC}$ = 36 MHz - limited test conditions<sup>(1)</sup>

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =36 MHz     | 10.6 | 10.8 | -   | bits |

| SINAD  | Signal-to noise and distortion ratio | $V_{DDA} = V_{REF+} = 3.3 V$ | 66   | 67   | -   |      |

| SNR    | Signal-to noise ratio                | Input Frequency = 20 KHz     | 64   | 68   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 70 | - 72 | -   |      |

1. Guaranteed by characterization results.

Note: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.17 does not affect the ADC accuracy.

#### General PCB design guidelines

1 µF // 10 nF

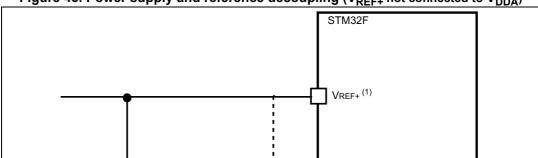

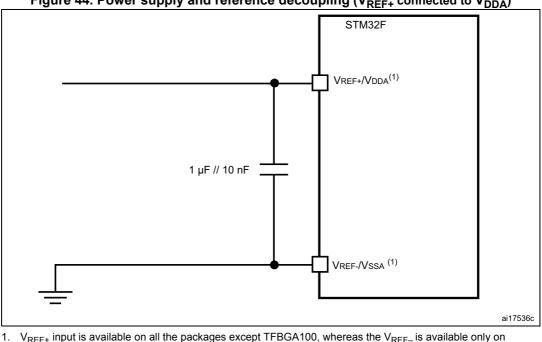

Power supply decoupling should be performed as shown in *Figure 43* or *Figure 44*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

Vdda

VSSA/VREF+<sup>(1)</sup>

Figure 43. Power supply and reference decoupling ( $V_{REF+}$  not connected to  $V_{DDA}$ )

1.  $V_{REF+}$  input is available on all the packages except TFBGA100 whereas the  $V_{REF-}$  is available only on UFBGA176 and TFBGA216. When  $V_{REF-}$  is not available, it is internally connected to  $V_{DDA}$  and  $V_{SSA}$ .

1 µF // 10 nF

Figure 44. Power supply and reference decoupling (V<sub>REF+</sub> connected to V<sub>DDA</sub>)

V<sub>REF+</sub> input is available on all the packages except TFBGA100, whereas the V<sub>REF</sub> is available only on UFBGA176 and TFBGA216. When V<sub>REF-</sub> is not available, it is internally connected to V<sub>DDA</sub> and V<sub>SSA</sub>.

ai17535b

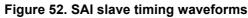

Refer to Section 5.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (CK, SD, WS).

| Symbol                 | Parameter                      | Conditions                                        | Min    | Max                   | Unit |

|------------------------|--------------------------------|---------------------------------------------------|--------|-----------------------|------|

| f <sub>MCK</sub>       | I2S Main clock output          | -                                                 | 256x8K | 256xFs <sup>(2)</sup> | MHz  |

| f                      | I2S clock frequency            | Master data: 32 bits                              | -      | 64xFs                 | MHz  |

| f <sub>СК</sub>        | 123 Clock frequency            | Slave data: 32 bits                               | -      | 64xFs                 |      |

| D <sub>CK</sub>        | I2S clock frequency duty cycle | Slave receiver                                    | 30     | 70                    | %    |

| t <sub>v(WS)</sub>     | WS valid time                  | Master mode                                       | -      | 5                     | ns   |

| t <sub>h(WS)</sub>     | WS hold time                   | Master mode                                       | 0      | -                     | 115  |

|                        |                                | Slave mode                                        | 5      | -                     |      |

| t <sub>su(WS)</sub>    | WS setup time                  | Slave mode<br>PCM short pulse mode <sup>(3)</sup> | 3      | -                     |      |

|                        |                                | Slave mode                                        | 0      | -                     |      |

| t <sub>h(WS)</sub>     | WS hold time                   | Slave mode<br>PCM short pulse mode <sup>(3)</sup> | 2      | -                     |      |

| t <sub>su(SD_MR)</sub> | Data input setup time          | Master receiver                                   | 5      | -                     |      |

| t <sub>su(SD_SR)</sub> |                                | Slave receiver                                    | 1      | -                     | ns   |

| t <sub>h(SD_MR)</sub>  | Data input hold time           | Master receiver                                   | 5      | -                     |      |

| t <sub>h(SD_SR)</sub>  | Data input noid time           | Slave receiver                                    | 1.5    | -                     |      |

| t <sub>v(SD_ST)</sub>  | Data output valid time         | Slave transmitter (after enable edge)             | -      | 16                    |      |

| t <sub>v(SD_MT)</sub>  |                                | Master transmitter (after enable edge)            | -      | 3.5                   |      |

| t <sub>h(SD_ST)</sub>  | Data output hold time          | Slave transmitter (after enable edge)             | 5      | -                     |      |

| t <sub>h(SD_MT)</sub>  |                                | Master transmitter (after enable edge)            | 0      | -                     |      |

| Table 77. 12 | S dv | vnamic | characteristics <sup>(1)</sup> |

|--------------|------|--------|--------------------------------|

|              | Ju   | ynanne | characteristics.               |

1. Guaranteed by characterization results.

2. The maximum value of 256xFs is 45 MHz (APB1 maximum frequency).

3. Measurement done with respect to I2S\_CK rising edge.

Note: Refer to RM0385 reference manual I2S section for more details on the sampling frequency  $(F_S)$ .

$f_{MCK}$ ,  $f_{CK}$ , and  $D_{CK}$  values reflect only the digital peripheral behavior. The values of these parameters might be slightly impacted by the source clock precision.  $D_{CK}$  depends mainly on the value of ODD bit. The digital contribution leads to a minimum value of (I2SDIV/(2\*I2SDIV+ODD) and a maximum value of (I2SDIV+ODD)/(2\*I2SDIV+ODD).  $F_S$  maximum value is supported for each mode/condition.

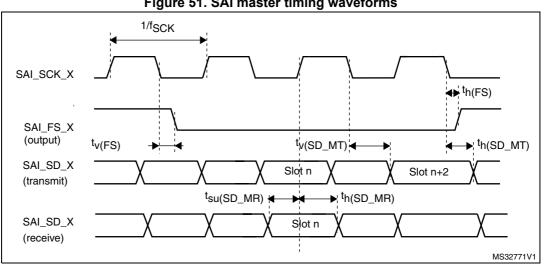

Figure 51. SAI master timing waveforms

### USB OTG full speed (FS) characteristics

This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol                              | Parameter                                   | Мах | Unit |

|-------------------------------------|---------------------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG full speed transceiver startup time | 1   | μs   |

### Table 79. USB OTG full speed startup time

1. Guaranteed by design.

| Syn             | nbol                           | Parameter                                                 | Conditions                                                     | Min.<br>(1)        | Тур. | Max.<br>(1) | Unit |

|-----------------|--------------------------------|-----------------------------------------------------------|----------------------------------------------------------------|--------------------|------|-------------|------|

|                 | V <sub>DDUSB</sub>             | USB OTG full speed<br>transceiver operating<br>voltage    | -                                                              | 3.0 <sup>(2)</sup> | -    | 3.6         | V    |

| Input<br>levels | V <sub>DI</sub> <sup>(3)</sup> | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                               | 0.2                | -    | -           |      |

| levels          | V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range                            | Includes V <sub>DI</sub> range                                 | 0.8                | -    | 2.5         | V    |

|                 | $V_{SE}^{(3)}$                 | Single ended receiver threshold                           | -                                                              | 1.3                | -    | 2.0         |      |

| Output          | V <sub>OL</sub>                | Static output level low                                   | ${\sf R}_{\sf L}$ of 1.5 k\Omega to 3.6 ${\sf V}^{(4)}$        | -                  | -    | 0.3         | v    |

| levels          | V <sub>OH</sub>                | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}^{(4)}$ | 2.8                | -    | 3.6         | v    |

| R <sub>PD</sub> |                                | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V <sub>IN</sub> = V <sub>DD</sub>                              | 17                 | 21   | 24          |      |

|                 |                                | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | VIN - VDD                                                      | 0.65               | 1.1  | 2.0         | kΩ   |

|                 |                                | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP)                      | V <sub>IN</sub> = V <sub>SS</sub>                              | 1.5                | 1.8  | 2.1         |      |

| R               | PU                             | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>                              | 0.25               | 0.37 | 0.55        |      |

#### Table 80. USB OTG full speed DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The USB OTG full speed transceiver functionality is ensured down to 2.7 V but not the full USB full speed electrical characteristics which are degraded in the 2.7-to-3.0 V V<sub>DDUSB</sub> voltage range.

- 3. Guaranteed by design.

- 4.  $R_L$  is the load connected on the USB OTG full speed drivers.

Note:

When VBUS sensing feature is enabled, PA9 and PB13 should be left at their default state (floating input), not as alternate function. A typical 200  $\mu$ A current consumption of the sensing block (current to voltage conversion to determine the different sessions) can be observed on PA9 and PB13 when the feature is enabled.

| Symbol                           | Parameter                                  | Conditions                                                                           | Min. | Тур. | Max. | Unit |

|----------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------|------|------|------|------|

| t <sub>SC</sub>                  | Control in (ULPI_DIR, ULPI_NXT) setup time | -                                                                                    | 3    | -    | -    |      |

| t <sub>HC</sub>                  | Control in (ULPI_DIR, ULPI_NXT) hold time  | -                                                                                    | 1    | -    | -    |      |

| t <sub>SD</sub>                  | Data in setup time                         | -                                                                                    | 1.5  | -    | -    |      |

| t <sub>HD</sub>                  | Data in hold time                          | -                                                                                    | 0.5  | -    | -    |      |

|                                  |                                            | 2.7 V < V <sub>DD</sub> < 3.6 V,<br>C <sub>L</sub> = 20 pF and<br>OSPEEDRy[1:0] = 11 | -    | 5.5  | 9    | ns   |

| t <sub>DC</sub> /t <sub>DD</sub> | Data/control output delay                  | -                                                                                    | -    |      |      |      |

|                                  |                                            | $1.7 V < V_{DD} < 3.6 V,$<br>C <sub>L</sub> = 15 pF and<br>OSPEEDRy[1:0] = 11        | -    | 5.5  | 5 9  |      |

Table 84. Dynamic characteristics: USB ULPI<sup>(1)</sup>

1. Guaranteed by characterization results.

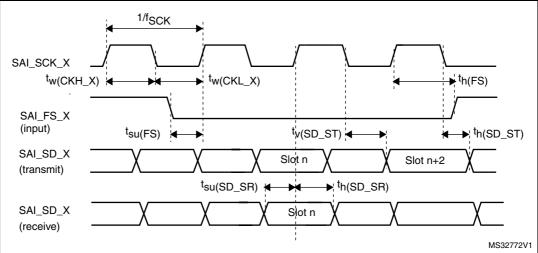

#### Ethernet characteristics

Unless otherwise specified, the parameters given in *Table 85*, *Table 86* and *Table 87* for SMI, RMII and MII are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency summarized in *Table 17* and  $V_{DD}$  supply voltage conditions summarized in *Table 85*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 20 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>.

Refer to Section 5.3.17: I/O port characteristics for more details on the input/output characteristics.

*Table 85* gives the list of Ethernet MAC signals for the SMI (station management interface) and *Figure 55* shows the corresponding timing diagram.

#### Figure 55. Ethernet SMI timing diagram

# 5.3.29 Camera interface (DCMI) timing specifications