Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                                        |

|----------------------------|--------------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                                 |

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 140                                                                                                    |

| Program Memory Size        | 1MB (1M x 8)                                                                                           |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320К х 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                      |

| Mounting Type              | Surface Mount                                                                                          |

| Package / Case             | 176-LQFP                                                                                               |

| Supplier Device Package    | 176-LQFP (24x24)                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f746igt6                                  |

|                            |                                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Description

The STM32F745xx and STM32F746xx devices are based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M7 32-bit RISC core operating at up to 216 MHz frequency. The Cortex<sup>®</sup>-M7 core features a single floating point unit (SFPU) precision which supports all ARM<sup>®</sup> single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances the application security.

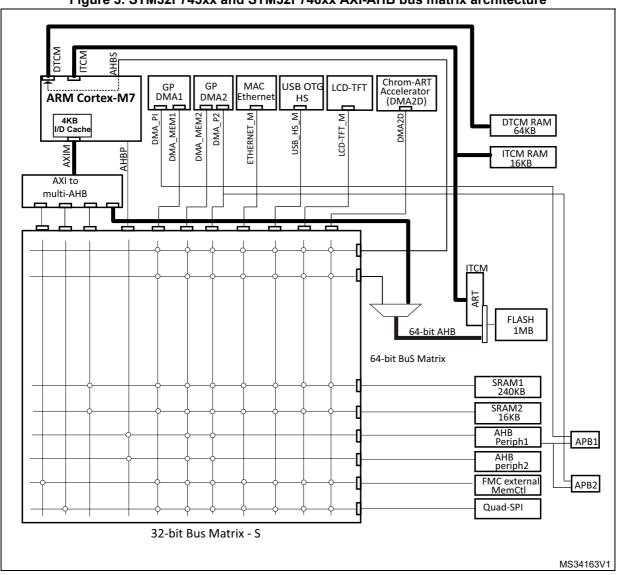

The STM32F745xx and STM32F746xx devices incorporate high-speed embedded memories with a Flash memory up to 1 Mbyte, 320 Kbytes of SRAM (including 64 Kbytes of Data TCM RAM for critical real-time data), 16 Kbytes of instruction TCM RAM (for critical real-time routines), 4 Kbytes of backup SRAM available in the lowest power modes, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses, a 32-bit multi-AHB bus matrix and a multi layer AXI interconnect supporting internal and external memories access.

All the devices offer three 12-bit ADCs, two DACs, a low-power RTC, thirteen generalpurpose 16-bit timers including two PWM timers for motor control and one low-power timer available in Stop mode, two general-purpose 32-bit timers, a true random number generator (RNG). They also feature standard and advanced communication interfaces.

- Up to four I<sup>2</sup>Cs

- Six SPIs, three I<sup>2</sup>Ss in duplex mode. To achieve the audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Four USARTs plus four UARTs

- An USB OTG full-speed and a USB OTG high-speed with full-speed capability (with the ULPI),

- Two CANs

- Two SAI serial audio interfaces

- An SDMMC host interface

- Ethernet and camera interfaces

- LCD-TFT display controller

- Chrom-ART Accelerator™

- SPDIFRX interface

- HDMI-CEC

Advanced peripherals include an SDMMC interface, a flexible memory control (FMC) interface, a Quad-SPI Flash memory interface, a camera interface for CMOS sensors. Refer to *Table 2: STM32F745xx and STM32F746xx features and peripheral counts* for the list of peripherals available on each part number.

The STM32F745xx and STM32F746xx devices operate in the –40 to +105 °C temperature range from a 1.7 to 3.6 V power supply. A dedicated supply input for USB (OTG\_FS and OTG\_HS) is available on all the packages except LQFP100 for a greater power supply choice.

The supply voltage can drop to 1.7 V with the use of an external power supply supervisor (refer to *Section 2.17.2: Internal reset OFF*). A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F745xx and STM32F746xx devices offer devices in 8 packages ranging from 100 pins to 216 pins. The set of included peripherals changes with the device chosen.

Figure 3. STM32F745xx and STM32F746xx AXI-AHB bus matrix architecture

1. The above figure has large wires for 64-bits bus and thin wires for 32-bits bus.

# 2.7 DMA controller (DMA)

The devices feature two general-purpose dual-port DMAs (DMA1 and DMA2) with 8 streams each. They are able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers. They feature dedicated FIFOs for APB/AHB peripherals, support burst transfer and are designed to provide the maximum peripheral bandwidth (AHB/APB).

The two DMA controllers support circular buffer management, so that no specific code is needed when the controller reaches the end of the buffer. The two DMA controllers also have a double buffering feature, which automates the use and switching of two memory buffers without requiring any special code.

# 2.15 Boot modes

At startup, the boot memory space is selected by the BOOT pin and BOOT\_ADDx option bytes, allowing to program any boot memory address from 0x0000 0000 to 0x3FFF FFFF which includes:

- All Flash address space mapped on ITCM or AXIM interface

- All RAM address space: ITCM, DTCM RAMs and SRAMs mapped on AXIM interface

- The System memory bootloader

The boot loader is located in system memory. It is used to reprogram the Flash memory through a serial interface.

# 2.16 Power supply schemes

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

- V<sub>DD</sub> = 1.7 to 3.6 Vexternal power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, DAC, reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

Note: V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the internal reset is OFF (refer to Section 2.17.2: Internal reset OFF). Refer to Table 3: Voltage regulator configuration mode versus device operating mode to identify the packages supporting this option.

- $V_{DDUSB}$  can be connected either to  $V_{DD}$  or an external independent power supply (3.0 to 3.6V) for USB transceivers (refer to *Figure 4* and *Figure 5*). For example, when device is powered at 1.8V, an independent power supply 3.3V can be connected to  $V_{DDUSB}$ . When the  $V_{DDUSB}$  is connected to a separated power supply, it is independent from  $V_{DD}$  or  $V_{DDA}$  but it must be the last supply to be provided and the first to disappear. The following conditions  $V_{DDUSB}$  must be respected:

- During power-on phase (V\_DD < V\_DD\_MIN), V\_DDUSB should be always lower than V\_DD

- During power-down phase (V<sub>DD</sub> < V<sub>DD\_MIN</sub>), V<sub>DDUSB</sub> should be always lower than  $V_{DD}$

- V<sub>DDSUB</sub> rising and falling time rate specifications must be respected (see *Table 20* and *Table 21*)

- In operating mode phase, V<sub>DDUSB</sub> could be lower or higher than V<sub>DD</sub>.

- If USB (USB OTG\_HS/OTG\_FS) is used, the associated GPIOs powered by  $V_{DDUSB}$  are operating between  $V_{DDUSB\ MIN}$  and  $V_{DDUSB\ MAX}.$

- The V<sub>DDUSB</sub> supply both USB transceiver (USB OTG\_HS and USB OTG\_FS). If only one USB transceiver is used in the application, the GPIOs associated to the other USB transceiver are still supplied by V<sub>DDUSB</sub>.

- If USB (USB OTG\_HS/OTG\_FS) is not used, the associated GPIOs powered by  $V_{DDUSB}$  are operating between  $V_{DD\_MIN}$  and  $V_{DD\_MAX}.$

# 2.24 Universal synchronous/asynchronous receiver transmitters (USART)

The device embeds USART. Refer to *Table 8: USART implementation* for the features implementation.

The universal synchronous asynchronous receiver transmitter (USART) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format.

The USART peripheral supports:

- Full-duplex asynchronous communications

- Configurable oversampling method by 16 or 8 to give flexibility between speed and clock tolerance

- Dual clock domain allowing convenient baud rate programming independent from the PCLK reprogramming

- A common programmable transmit and receive baud rate of up to 27 Mbit/s when USART clock source is system clock frequency (Max is 216 MHz) and oversampling by 8 is used.

- Auto baud rate detection

- Programmable data word length (7 or 8 or 9 bits) word length

- Programmable data order with MSB-first or LSB-first shifting

- Programmable parity (odd, even, no parity)

- Configurable stop bits (1 or 1.5 or 2 stop bits)

- Synchronous mode and clock output for synchronous communications

- Single-wire half-duplex communications

- Separate signal polarity control for transmission and reception

- Swappable Tx/Rx pin configuration

- Hardware flow control for modem and RS-485 transceiver

- Multiprocessor communications

- LIN master synchronous break send capability and LIN slave break detection capability

- IrDA SIR encoder decoder supporting 3/16 bit duration for normal mode

- Smartcard mode (T=0 and T=1 asynchronous protocols for Smartcards as defined in the ISO/IEC 7816-3 standard )

- Support for Modbus communication

The table below summarizes the implementation of all U(S)ARTs instances

#### Table 8. USART implementation

| features <sup>(1)</sup>            | USART1/2/3/6 | UART4/5/7/8     |  |  |  |

|------------------------------------|--------------|-----------------|--|--|--|

| Data Length                        | 7, 8 an      | 7, 8 and 9 bits |  |  |  |

| Hardware flow control for modem    | Х            | X               |  |  |  |

| Continuous communication using DMA | X            | X               |  |  |  |

| Multiprocessor communication       | Х            | Х               |  |  |  |

| Synchronous mode                   | Х            | -               |  |  |  |

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

Eight DAC trigger inputs are used in the device. The DAC channels are triggered through the timer update outputs that are also connected to different DMA streams.

# 2.42 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target.

Debug is performed using 2 pins only instead of 5 required by the JTAG (JTAG pins could be re-use as GPIO with alternate function): the JTAG TMS and TCK pins are shared with SWDIO and SWCLK, respectively, and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

# 2.43 Embedded Trace Macrocell™

The ARM Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F74xxx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer that runs the debugger software. TPA hardware is commercially available from common development tool vendors.

The Embedded Trace Macrocell operates with third party debugger software tools.

|         |          |          |         | umbei    |         |         |          |                                                            |          |               |       | ball definition (continued)                                                       |                         |  |  |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------|-------------------------|--|--|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                               | Additional<br>functions |  |  |

| 69      | D10      | D5       | 102     | D15      | 121     | 144     | D15      | PA10                                                       | I/O      | FT            | -     | TIM1_CH3, USART1_RX,<br>OTG_FS_ID, DCMI_D1,<br>EVENTOUT                           | -                       |  |  |

| 70      | C10      | D4       | 103     | C15      | 122     | 145     | C15      | PA11                                                       | I/O      | FT            | -     | TIM1_CH4,<br>USART1_CTS,<br>CAN1_RX, OTG_FS_DM,<br>LCD_R4, EVENTOUT               | -                       |  |  |

| 71      | B10      | E1       | 104     | B15      | 123     | 146     | B15      | PA12                                                       | I/O      | FT            | -     | TIM1_ETR,<br>USART1_RTS,<br>SAI2_FS_B, CAN1_TX,<br>OTG_FS_DP, LCD_R5,<br>EVENTOUT | -                       |  |  |

| 72      | A10      | D3       | 105     | A15      | 124     | 147     | A15      | PA13(JT<br>MS-<br>SWDIO)                                   | I/O      | FT            | -     | JTMS-SWDIO,<br>EVENTOUT                                                           | -                       |  |  |

| 73      | E7       | D1       | 106     | F13      | 125     | 148     | E11      | VCAP_2                                                     | S        | -             | -     | -                                                                                 | -                       |  |  |

| 74      | E5       | D2       | 107     | F12      | 126     | 149     | F10      | VSS                                                        | S        | 1             | -     | -                                                                                 | -                       |  |  |

| 75      | F5       | C1       | 108     | G13      | 127     | 150     | F11      | VDD                                                        | S        | -             | -     | -                                                                                 | -                       |  |  |

| -       | -        | -        | -       | E12      | 128     | 151     | E12      | PH13                                                       | I/O      | FT            | -     | TIM8_CH1N, CAN1_TX,<br>FMC_D21, LCD_G2,<br>EVENTOUT                               | -                       |  |  |

| -       | -        | -        | -       | E13      | 129     | 152     | E13      | PH14                                                       | I/O      | FT            | -     | TIM8_CH2N, FMC_D22,<br>DCMI_D4, LCD_G3,<br>EVENTOUT                               | -                       |  |  |

| -       | -        | -        | -       | D13      | 130     | 153     | D13      | PH15                                                       | I/O      | FT            | -     | TIM8_CH3N, FMC_D23,<br>DCMI_D11, LCD_G4,<br>EVENTOUT                              | -                       |  |  |

| -       | -        | -        | -       | E14      | 131     | 154     | E14      | P10                                                        | I/O      | FT            | -     | TIM5_CH4,<br>SPI2_NSS/I2S2_WS,<br>FMC_D24, DCMI_D13,<br>LCD_G5, EVENTOUT          | -                       |  |  |

| -       | -        | -        | -       | D14      | 132     | 155     | D14      | PI1                                                        | I/O      | FT            | -     | TIM8_BKIN2,<br>SPI2_SCK/I2S2_CK,<br>FMC_D25, DCMI_D8,<br>LCD_G6, EVENTOUT         | -                       |  |  |

## STM32F745xx STM32F746xx

|          |                    | 11. FMC pin defin |        |       |

|----------|--------------------|-------------------|--------|-------|

| Pin name | NOR/PSRAM/SR<br>AM | NOR/PSRAM<br>Mux  | NAND16 | SDRAM |

| PF0      | A0                 | -                 | -      | A0    |

| PF1      | A1                 | -                 | -      | A1    |

| PF2      | A2                 | -                 | -      | A2    |

| PF3      | A3                 | -                 | -      | A3    |

| PF4      | A4                 | -                 | -      | A4    |

| PF5      | A5                 | -                 | -      | A5    |

| PF12     | A6                 | -                 | -      | A6    |

| PF13     | A7                 | -                 | -      | A7    |

| PF14     | A8                 | -                 | -      | A8    |

| PF15     | A9                 | -                 | -      | A9    |

| PG0      | A10                | -                 | -      | A10   |

| PG1      | A11                | -                 | -      | A11   |

| PG2      | A12                | -                 | -      | A12   |

| PG3      | A13                | -                 | -      | -     |

| PG4      | A14                | -                 | -      | BA0   |

| PG5      | A15                | -                 | -      | BA1   |

| PD11     | A16                | A16               | CLE    | -     |

| PD12     | A17                | A17               | ALE    | -     |

| PD13     | A18                | A18               | -      | -     |

| PE3      | A19                | A19               | -      | -     |

| PE4      | A20                | A20               | -      | -     |

| PE5      | A21                | A21               | -      | -     |

| PE6      | A22                | A22               | -      | -     |

| PE2      | A23                | A23               | -      | -     |

| PG13     | A24                | A24               | -      | -     |

| PG14     | A25                | A25               | -      | -     |

| PD14     | D0                 | DA0               | D0     | D0    |

| PD15     | D1                 | DA1               | D1     | D1    |

| PD0      | D2                 | DA2               | D2     | D2    |

| PD1      | D3                 | DA3               | D3     | D3    |

| PE7      | D4                 | DA4               | D4     | D4    |

| PE8      | D5                 | DA5               | D5     | D5    |

| PE9      | D6                 | DA6               | D6     | D6    |

| PE10     | D7                 | DA7               | D7     | D7    |

# Table 11. FMC pin definition

# Pinouts and pin description

| Table 11. FMC pin definition (continued) |                    |                  |        |       |  |  |  |  |

|------------------------------------------|--------------------|------------------|--------|-------|--|--|--|--|

| Pin name                                 | NOR/PSRAM/SR<br>AM | NOR/PSRAM<br>Mux | NAND16 | SDRAM |  |  |  |  |

| PE11                                     | D8                 | DA8              | D8     | D8    |  |  |  |  |

| PE12                                     | D9                 | DA9              | D9     | D9    |  |  |  |  |

| PE13                                     | D10                | DA10             | D10    | D10   |  |  |  |  |

| PE14                                     | D11                | DA11             | D11    | D11   |  |  |  |  |

| PE15                                     | D12                | DA12             | D12    | D12   |  |  |  |  |

| PD8                                      | D13                | DA13             | D13    | D13   |  |  |  |  |

| PD9                                      | D14                | DA14             | D14    | D14   |  |  |  |  |

| PD10                                     | D15                | DA15             | D15    | D15   |  |  |  |  |

| PH8                                      | D16                | -                | -      | D16   |  |  |  |  |

| PH9                                      | D17                | -                | -      | D17   |  |  |  |  |

| PH10                                     | D18                | -                | -      | D18   |  |  |  |  |

| PH11                                     | D19                | -                | -      | D19   |  |  |  |  |

| PH12                                     | D20                | -                | -      | D20   |  |  |  |  |

| PH13                                     | D21                | -                | -      | D21   |  |  |  |  |

| PH14                                     | D22                | -                | -      | D22   |  |  |  |  |

| PH15                                     | D23                | -                | -      | D23   |  |  |  |  |

| PI0                                      | D24                | -                | -      | D24   |  |  |  |  |

| PI1                                      | D25                | -                | -      | D25   |  |  |  |  |

| Pl2                                      | D26                | -                | -      | D26   |  |  |  |  |

| PI3                                      | D27                | -                | -      | D27   |  |  |  |  |

| Pl6                                      | D28                | -                | -      | D28   |  |  |  |  |

| PI7                                      | D29                | -                | -      | D29   |  |  |  |  |

| PI9                                      | D30                | -                | -      | D30   |  |  |  |  |

| PI10                                     | D31                | -                | -      | D31   |  |  |  |  |

| PD7                                      | NE1                | NE1              | -      | -     |  |  |  |  |

| PG9                                      | NE2                | NE2              | NCE    | -     |  |  |  |  |

| PG10                                     | NE3                | NE3              | -      | -     |  |  |  |  |

| PG11                                     | -                  | -                | -      | -     |  |  |  |  |

| PG12                                     | NE4                | NE4              | -      | -     |  |  |  |  |

| PD3                                      | CLK                | CLK              | -      | -     |  |  |  |  |

| PD4                                      | NOE                | NOE              | NOE    | -     |  |  |  |  |

| PD5                                      | NWE                | NWE              | NWE    | -     |  |  |  |  |

| PD6                                      | NWAIT              | NWAIT            | NWAIT  | -     |  |  |  |  |

| PB7                                      | NADV               | NADV             | -      | -     |  |  |  |  |

|                                          |                    |                  |        |       |  |  |  |  |

Table 11. FMC pin definition (continued)

78/227

DocID027590 Rev 4

# Pinouts and pin description

STM32F745xx STM32F746xx

| 5 |

|---|

|---|

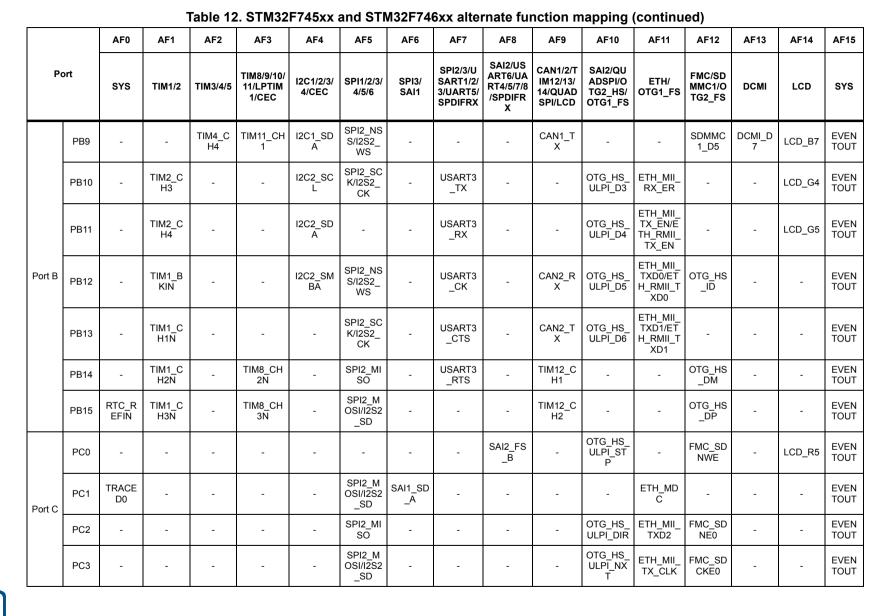

#### Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

| Table 12. STMS2F745XX and STMS2F746XX alternate function mapping (continued) |      |             |        |              |                                 |                    |                    |                           |                                             |                                                 |                                            |                                          |                                        |                            |             |               |              |

|------------------------------------------------------------------------------|------|-------------|--------|--------------|---------------------------------|--------------------|--------------------|---------------------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|----------------------------------------|----------------------------|-------------|---------------|--------------|

|                                                                              |      | AF0         | AF1    | AF2          | AF3                             | AF4                | AF5                | AF6                       | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11                                   | AF12                       | AF13        | AF14          | AF15         |

| Po                                                                           | ort  | SYS         | TIM1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1             | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS                        | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI        | LCD           | SYS          |

|                                                                              | PC4  | -           | -      | -            | -                               | -                  | I2S1_M<br>CK       | -                         | -                                           | SPDIFRX<br>_IN2                                 | -                                          | -                                        | ETH_MII_<br>RXD0/ET<br>H_RMII_<br>RXD0 | FMC_SD<br>NE0              | -           | -             | EVEN<br>TOUT |

|                                                                              | PC5  | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | SPDIFRX<br>_IN3                                 | -                                          | -                                        | ETH_MII_<br>RXD1/ET<br>H_RMII_<br>RXD1 | FMC_SD<br>CKE0             | -           | -             | EVEN<br>TOUT |

|                                                                              | PC6  | -           | -      | TIM3_C<br>H1 | TIM8_CH<br>1                    | -                  | I2S2_M<br>CK       | -                         | -                                           | USART6<br>_TX                                   | -                                          | -                                        | -                                      | SDMMC<br>1_D6              | DCMI_D<br>0 | LCD_HS<br>YNC | EVEN<br>TOUT |

|                                                                              | PC7  | -           | -      | TIM3_C<br>H2 | TIM8_<br>CH2                    | -                  | -                  | I2S3_M<br>CK              | -                                           | USART6<br>_RX                                   | -                                          | -                                        | -                                      | SDMMC<br>1_D7              | DCMI_D<br>1 | LCD_G6        | EVEN<br>TOUT |

|                                                                              | PC8  | TRACE<br>D1 | -      | TIM3_C<br>H3 | TIM8_<br>CH3                    | -                  | -                  | -                         | UART5_<br>RTS                               | USART6<br>_CK                                   | -                                          | -                                        | -                                      | SDMMC<br>1_D0              | DCMI_D<br>2 | -             | EVEN<br>TOUT |

| Port C                                                                       | PC9  | MCO2        | -      | TIM3_C<br>H4 | TIM8_<br>CH4                    | I2C3_SD<br>A       | I2S_CKI<br>N       | -                         | UART5_<br>CTS                               | -                                               | QUADSP<br>I_BK1_IO<br>0                    | -                                        | -                                      | SDMMC<br>1_D1              | DCMI_D<br>3 | -             | EVEN<br>TOUT |

|                                                                              | PC10 | -           | -      | -            | -                               | -                  | -                  | SPI3_SC<br>K/I2S3_<br>CK  | USART3<br>_TX                               | UART4_T<br>X                                    | QUADSP<br>I_BK1_IO<br>1                    | -                                        | -                                      | SDMMC<br>1_D2              | DCMI_D<br>8 | LCD_R2        | EVEN<br>TOUT |

|                                                                              | PC11 | -           | -      | -            | -                               | -                  | -                  | SPI3_MI<br>SO             | USART3<br>_RX                               | UART4_<br>RX                                    | QUADSP<br>I_BK2_N<br>CS                    | -                                        | -                                      | SDMMC<br>1_D3              | DCMI_D<br>4 | -             | EVEN<br>TOUT |

|                                                                              | PC12 | TRACE<br>D3 | -      | -            | -                               | -                  | -                  | SPI3_M<br>OSI/I2S3<br>_SD | USART3<br>_CK                               | UART5_T<br>X                                    | -                                          | -                                        | -                                      | SDMMC<br>1_CK              | DCMI_D<br>9 | -             | EVEN<br>TOUT |

|                                                                              | PC13 | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | -           | -             | EVEN<br>TOUT |

|                                                                              | PC14 | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | -           | -             | EVEN<br>TOUT |

|                                                                              | PC15 | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | -           | -             | EVEN<br>TOUT |

STM32F745xx STM32F746xx

79/227

Pinouts and pin description

| Symbol                          | Ratings                                                                         | Max.   | Unit |

|---------------------------------|---------------------------------------------------------------------------------|--------|------|

| $\Sigma I_{VDD}$                | Total current into sum of all $V_{DD_x}$ power lines (source) <sup>(1)</sup>    | 320    |      |

| $\Sigma I_{VSS}$                | Total current out of sum of all $V_{SS_x}$ ground lines $(sink)^{(1)}$          | - 320  |      |

| $\Sigma I_{VDDUSB}$             | Total current into V <sub>DDUSB</sub> power line (source)                       | 25     |      |

| I <sub>VDD</sub>                | Maximum current into each V <sub>DD_x</sub> power line (source) <sup>(1)</sup>  | 100    |      |

| I <sub>VSS</sub>                | Maximum current out of each $V_{SS_x}$ ground line (sink) <sup>(1)</sup>        | - 100  |      |

| 1                               | Output current sunk by any I/O and control pin                                  | 25     |      |

| Ι <sub>ΙΟ</sub>                 | Output current sourced by any I/Os and control pin                              | - 25   | mA   |

|                                 | Total output current sunk by sum of all I/O and control pins <sup>(2)</sup>     | 120    |      |

| $\Sigma I_{IO}$                 | Total output current sunk by sum of all USB I/Os                                | 25     |      |

|                                 | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | - 120  |      |

| 1                               | Injected current on FT, FTf, RST and B pins (3)                                 | - 5/+0 |      |

| I <sub>INJ(PIN)</sub>           | Injected current on TTa pins <sup>(4)</sup>                                     | ±5     | 1    |

| $\Sigma I_{\rm INJ(PIN)}^{(4)}$ | Total injected current (sum of all I/O and control pins) <sup>(5)</sup>         | ±25    | 1    |

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count LQFP packages.

3. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

A positive injection is induced by V<sub>IN</sub>>V<sub>DDA</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to Table 14: Voltage characteristics for the values of the maximum allowed input voltage.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 16. Thermal characteristics

| Symbol           | Ratings                      | Value        | Unit |

|------------------|------------------------------|--------------|------|

| T <sub>STG</sub> | Storage temperature range    | – 65 to +150 | °C   |

| Т <sub>Ј</sub>   | Maximum junction temperature | 125          | C    |

- 6. It is recommended to power V<sub>DD</sub> and V<sub>DDA</sub> from the same source. A maximum difference of 300 mV between V<sub>DD</sub> and V<sub>DDA</sub> can be tolerated during power-up and power-down operation.

- 7. The over-drive mode is not supported when the internal regulator is OFF.

- 8. To sustain a voltage higher than VDD+0.3, the internal Pull-up and Pull-Down resistors must be disabled

- 9. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

- 10. In low power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_{Jmax}$ .

| Operating<br>power supply<br>range                | ADC operation                     | Maximum Flash<br>memory access<br>frequency with<br>no wait states<br>(f <sub>Flashmax</sub> ) | Maximum HCLK<br>frequency vs Flash<br>memory wait states<br>(1)(2) | I/O operation          | Possible Flash<br>memory<br>operations        |

|---------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------|-----------------------------------------------|

| V <sub>DD</sub> =1.7 to<br>2.1 V <sup>(3)</sup>   | Conversion time<br>up to 1.2 Msps | 20 MHz                                                                                         | 180 MHz with 8 wait<br>states and over-drive<br>OFF                | No I/O<br>compensation | 8-bit erase and<br>program<br>operations only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                 | Conversion time<br>up to 1.2 Msps | 22 MHz                                                                                         | 216 MHz with 9 wait<br>states and over-drive<br>ON                 | No I/O<br>compensation | 16-bit erase and<br>program<br>operations     |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                 | Conversion time<br>up to 2.4 Msps | 24 MHz                                                                                         | 216 MHz with 8 wait<br>states and over-drive<br>ON                 | I/O compensation works | 16-bit erase and<br>program<br>operations     |

| $V_{DD} = 2.7 \text{ to}$<br>3.6 V <sup>(4)</sup> | Conversion time<br>up to 2.4 Msps | 30 MHz                                                                                         | 216 MHz with 7 wait<br>states and over-drive<br>ON                 | I/O compensation works | 32-bit erase and program operations           |

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

Thanks to the ART accelerator on ITCM interface and L1-cache on AXI interface, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator or L1-cache allows to achieve a performance equivalent to 0-wait state program execution.

3. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to *Section 2.17.2: Internal reset OFF*).

4. The voltage range for USB full speed PHYs can drop down to 2.7 V. However the electrical characteristics of D- and D+ pins will be degraded between 2.7 and 3 V.

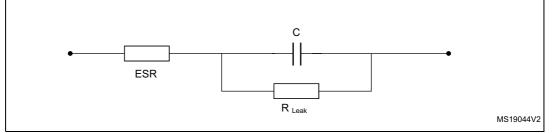

# 5.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor  $C_{EXT}$  to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 19*.

#### Figure 24. External capacitor CEXT

1. Legend: ESR is the equivalent series resistance.

- 1. Guaranteed by design.

- 2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

# 5.3.6 Over-drive switching characteristics

When the over-drive mode switches from enabled to disabled or disabled to enabled, the system clock is stalled during the internal voltage set-up.

The over-drive switching characteristics are given in *Table 23*. They are sbject to general operating conditions for  $T_A$ .

| Symbol                                 | Parameter                               | Conditions                            | Min | Тур | Мах | Unit |

|----------------------------------------|-----------------------------------------|---------------------------------------|-----|-----|-----|------|

| Tod_swen Over_drive switch enable time |                                         | HSI                                   | -   | 45  | -   |      |

|                                        | HSE max for 4 MHz<br>and min for 26 MHz | 45                                    | -   | 100 |     |      |

|                                        |                                         | External HSE<br>50 MHz                | -   | 40  | -   | 110  |

|                                        |                                         | HSI                                   | -   | 20  | -   | μs   |

|                                        | Over_drive switch<br>disable time       | HSE max for 4 MHz and min for 26 MHz. | 20  | -   | 80  |      |

|                                        |                                         | External HSE<br>50 MHz                | -   | 15  | -   |      |

Table 23. Over-drive switching characteristics<sup>(1)</sup>

1. Guaranteed by design.

# 5.3.7 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 23: Current consumption measurement scheme*.

All the run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to CoreMark code.

| Symbol            | Parameter                | Conditions                                                                           | I/O toggling<br>frequency (fsw)<br>MHz | Typ<br>V <sub>DD</sub> = 3.3 V | Typ<br>V <sub>DD</sub> = 1.8 V | Unit |

|-------------------|--------------------------|--------------------------------------------------------------------------------------|----------------------------------------|--------------------------------|--------------------------------|------|

|                   |                          |                                                                                      | 2                                      | 0.3                            | 0.1                            |      |

|                   |                          |                                                                                      | 8                                      | 1.0                            | 0.5                            |      |

|                   |                          |                                                                                      | 25                                     | 3.5                            | 1.6                            | - mA |

|                   | I/O switching<br>Current | C <sub>EXT</sub> = 22 pF<br>C = C <sub>INT</sub> + C <sub>S</sub> + C <sub>EXT</sub> | 50                                     | 5.9                            | 4.2                            |      |

|                   |                          |                                                                                      | 60                                     | 10.0                           | 4.4                            |      |

|                   |                          |                                                                                      | 84                                     | 19.12                          | 5.8                            |      |

| I <sub>DDIO</sub> |                          |                                                                                      | 90                                     | 19.6                           | -                              |      |

|                   |                          |                                                                                      | 2                                      | 0.3                            | 0.2                            |      |

|                   |                          |                                                                                      | 8                                      | 1.3                            | 0.7                            |      |

|                   |                          | $C_{EXT} = 33 \text{ pF}$<br>$C = C_{INT} + C_S + C_{EXT}$                           | 25                                     | 3.5                            | 2.3                            |      |

|                   |                          |                                                                                      | 50                                     | 10.26                          | 5.19                           |      |

|                   |                          |                                                                                      | 60                                     | 16.53                          | -                              |      |

### Table 34. Switching output I/O current consumption<sup>(1)</sup> (continued)

1. CINT + C<sub>S.</sub> PCB board capacitance including the pad pin is estimated to15 pF.

# On-chip peripheral current consumption

The MCU is placed under the following conditions:

- At startup, all I/O pins are in analog input configuration.

- All peripherals are disabled unless otherwise mentioned.

- I/O compensation cell enabled.

- The ART/L1-cache is ON.

- Scale 1 mode selected, internal digital voltage V12 = 1.32 V.

- HCLK is the system clock. f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2.

The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- f<sub>HCLK</sub> = 216 MHz (Scale 1 + over-drive ON), f<sub>HCLK</sub> = 168 MHz (Scale 2), f<sub>HCLK</sub> = 144 MHz (Scale 3)

- Ambient operating temperature is 25 °C and V<sub>DD</sub>=3.3 V.

### 5.3.8 Wakeup time from low-power modes

The wakeup times given in *Table 36* are measured starting from the wakeup event trigger up to the first instruction executed by the CPU:

- For Stop or Sleep modes: the wakeup event is WFE.

- WKUP (PA0) pin is used to wakeup from Standby, Stop and Sleep modes.

All timings are derived from tests performed under ambient temperature and  $V_{DD}$ =3.3 V.

| Symbol                                                                                             | Parameter                                                            | Conditions                                                                              | Typ <sup>(1)</sup> | Max <sup>(1)</sup> | Unit                   |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|--------------------|------------------------|

| t <sub>WUSLEEP</sub> <sup>(2)</sup>                                                                | Wakeup from Sleep                                                    | -                                                                                       | 13                 | 13                 | CPU<br>clock<br>cycles |

|                                                                                                    |                                                                      | Main regulator is ON                                                                    | 14                 | 14.9               |                        |

| t <sub>WUSTOP</sub> <sup>(2)</sup> Wakeup from Stop mode<br>with MR/LP regulator in<br>normal mode | Main regulator is ON and Flash<br>memory in Deep power down mode     | 104.1                                                                                   | 107.6              |                    |                        |

|                                                                                                    | -                                                                    | Low power regulator is ON                                                               | 21.4               | 24.2               |                        |

|                                                                                                    |                                                                      | Low power regulator is ON and Flash memory in Deep power down mode                      | 111.5              | 116.5              | μs                     |

|                                                                                                    | Wakeup from Stop mode<br>with MR/LP regulator in<br>Under-drive mode | Main regulator in under-drive mode<br>(Flash memory in Deep power-down<br>mode)         | 107.4              | 113.2              |                        |

| t <sub>WUSTOP</sub> <sup>(2)</sup>                                                                 |                                                                      | Low power regulator in under-drive<br>mode<br>(Flash memory in Deep power-down<br>mode) | 112.7              | 120                |                        |

| tWUSTDBY                                                                                           | Wakeup from Standby                                                  | Exit Standby mode on rising edge                                                        | 308                | 313                |                        |

| (2)                                                                                                | mode                                                                 | Exit Standby mode on falling edge                                                       | 307                | 313                |                        |

#### Table 36. Low-power mode wakeup timings

1. Guaranteed by characterization results.

2. The wakeup times are measured from the wakeup event to the point in which the application code reads the first

# Low-speed internal (LSI) RC oscillator

| Table 42. LSI oscillator characteristics <sup>(1)</sup> | ) |

|---------------------------------------------------------|---|

|---------------------------------------------------------|---|

| Symbol                              | Parameter                        | Min | Тур | Мах | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = –40 to 105  $^\circ C$  unless otherwise specified.

2. Guaranteed by characterization results.

3. Guaranteed by design.

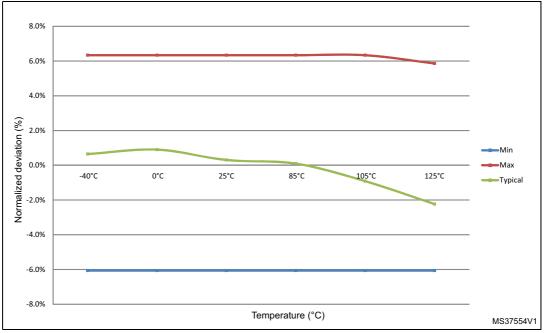

#### Figure 35. LSI deviation versus temperature

# 5.3.11 PLL characteristics

The parameters given in *Table 43* and *Table 44* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Table 43. | Main | PLL | characteristics |

|-----------|------|-----|-----------------|

|-----------|------|-----|-----------------|

| Symbol                 | Parameter                             | Conditions | Min                 | Тур | Max  | Unit |

|------------------------|---------------------------------------|------------|---------------------|-----|------|------|

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(1)</sup>        | -          | 0.95 <sup>(2)</sup> | 1   | 2.10 |      |

| f <sub>PLL_OUT</sub>   | PLL multiplier output clock           | -          | 24                  | -   | 216  |      |

| f <sub>PLL48_OUT</sub> | 48 MHz PLL multiplier output<br>clock | -          | -                   | 48  | 75   | MHz  |

| f <sub>VCO_OUT</sub>   | PLL VCO output                        | -          | 100                 | -   | 432  | 1    |

| Symbol                      | Parameter                                | Min                    | Max | Unit |

|-----------------------------|------------------------------------------|------------------------|-----|------|

| t <sub>(CLK)</sub>          | FMC_CLK period                           | 2T <sub>HCLK</sub> -1  | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)        | -                      | 2.5 |      |

| t <sub>(CLKH-NExH)</sub>    | FMC_CLK high to FMC_NEx high (x= 02)     | T <sub>HCLK</sub> +0.5 | -   | 1    |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low              | -                      | 1.5 | 1    |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high             | 0                      | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)     | -                      | 2.5 | 1    |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)  | 0                      | -   |      |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low               | -                      | 1.5 | ns   |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high             | T <sub>HCLK</sub> +1   | -   | 1    |

| t <sub>d(CLKL-Data)</sub>   | FMC_D[15:0] valid data after FMC_CLK low | -                      | 3   | 1    |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low               | 1.5                    | -   |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high             | T <sub>HCLK</sub> +0.5 | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high      | 2                      | -   | 1    |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high       | 3.5                    | -   | 1    |

Table 99. Synchronous non-multiplexed PSRAM write timings<sup>(1)</sup>

1. Guaranteed by characterization results.

# NAND controller waveforms and timings

*Figure 66* through *Figure 69* represent synchronous waveforms, and *Table 100* and *Table 101* provide the corresponding timings. The results shown in this table are obtained with the following FMC configuration:

- COM.FMC\_SetupTime = 0x01;

- COM.FMC\_WaitSetupTime = 0x03;

- COM.FMC HoldSetupTime = 0x02;

- COM.FMC\_HiZSetupTime = 0x01;

- ATT.FMC\_SetupTime = 0x01;

- ATT.FMC\_WaitSetupTime = 0x03;

- ATT.FMC\_HoldSetupTime = 0x02;

- ATT.FMC\_HiZSetupTime = 0x01;

- Bank = FMC\_Bank\_NAND;

- MemoryDataWidth = FMC\_MemoryDataWidth\_16b;

- ECC = FMC\_ECC\_Enable;

- ECCPageSize = FMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{\mbox{HCLK}}$  is the HCLK clock period.

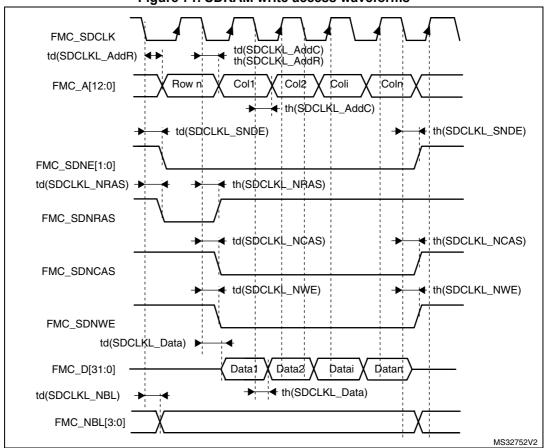

Figure 71. SDRAM write access waveforms

# Table 104. SDRAM write timings<sup>(1)</sup>

| Symbol                        | Parameter              | Min                     | Мах                     | Unit |

|-------------------------------|------------------------|-------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> -0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>d(SDCLKL_Data</sub> )  | Data output valid time | -                       | 2                       |      |

| t <sub>h(SDCLKL</sub> _Data)  | Data output hold time  | 0.5                     | -                       |      |

| t <sub>d</sub> (SDCLKL_Add)   | Address valid time     | -                       | 4                       |      |

| t <sub>d(SDCLKL_SDNWE)</sub>  | SDNWE valid time       | -                       | 0.5                     |      |

| t <sub>h(SDCLKL_SDNWE)</sub>  | SDNWE hold time        | 0                       | -                       | ns   |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -                       | 0.5                     | 115  |

| t <sub>h(SDCLKLSDNE)</sub>    | Chip select hold time  | 0                       | -                       |      |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                       | 0.5                     |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0                       | -                       |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                       | 0.5                     |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0                       | -                       |      |

1. Guaranteed by characterization results.

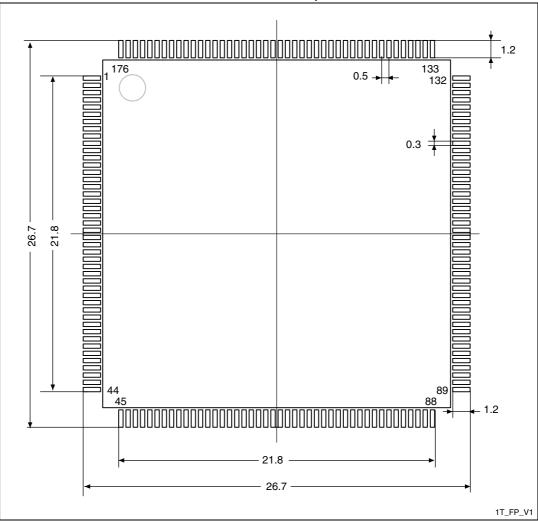

Figure 92. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

# 6.6 LQFP208, 28 x 28 mm low-profile quad flat package information

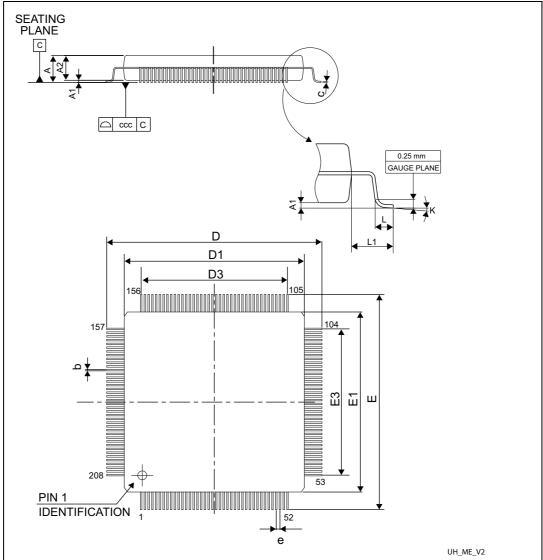

Figure 94. LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 119. LQFP208, 2 | 28 x 28 mm, 208-pin low-profile quad flat package |

|-----------------------|---------------------------------------------------|

|                       | mechanical data                                   |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| A      | -           | -     | 1.600 |                       | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

DocID027590 Rev 4