Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

EXF

| Product Status             | Active                                                                                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 168                                                                                                    |

| Program Memory Size        | 1MB (1M x 8)                                                                                           |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320K x 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                      |

| Mounting Type              | Surface Mount                                                                                          |

| Package / Case             | 216-TFBGA                                                                                              |

| Supplier Device Package    | 216-TFBGA (13x13)                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f746ngh6g                                 |

|                            |                                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

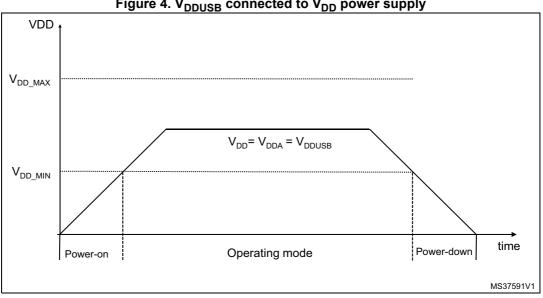

Figure 4. V<sub>DDUSB</sub> connected to V<sub>DD</sub> power supply

#### 2.17 Power supply supervisor

#### 2.17.1 Internal reset ON

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR ON high. On the other packages, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR)/ power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is

DocID027590 Rev 4

The RTC is functional in V<sub>BAT</sub> mode and in all low-power modes when it is clocked by the LSE. When clocked by the LSI, the RTC is not functional in V<sub>BAT</sub> mode, but is functional in all low-power modes.

All RTC events (Alarm, WakeUp Timer, Timestamp or Tamper) can generate an interrupt and wakeup the device from the low-power modes.

# 2.20 Low-power modes

The devices support three low-power modes to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### • Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The voltage regulator can be put either in main regulator mode (MR) or in low-power mode (LPR). Both modes can be configured as follows (see *Table 5: Voltage regulator modes in Stop mode*):

- Normal mode (default mode when MR or LPR is enabled)

- Under-drive mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup and LPTIM1 asynchronous interrupt).

| Voltage regulator<br>configuration | Main regulator (MR)    | Low-power regulator (LPR) |

|------------------------------------|------------------------|---------------------------|

| Normal mode                        | MR ON                  | LPR ON                    |

| Under-drive mode                   | MR in under-drive mode | LPR in under-drive mode   |

#### Table 5. Voltage regulator modes in Stop mode

#### • Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising or falling edge on one of the 6 WKUP pins (PA0, PA2, PC1, PC13, PI8, PI11), or an RTC alarm / wakeup / tamper /time stamp event occurs.

The Standby mode is not supported when the embedded voltage regulator is bypassed and the 1.2 V domain is controlled by an external power.

# 2.21 V<sub>BAT</sub> operation

The V<sub>BAT</sub> pin allows to power the device V<sub>BAT</sub> domain from an external battery, an external supercapacitor, or from V<sub>DD</sub> when no external battery and an external supercapacitor are present.

$V_{\text{BAT}}$  operation is activated when  $V_{\text{DD}}$  is not present.

The V<sub>BAT</sub> pin supplies the RTC, the backup registers and the backup SRAM.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

When PDR\_ON pin is connected to  $V_{SS}$  (Internal Reset OFF), the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to VDD.

# 2.22 Timers and watchdogs

The devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

Table 6 compares the features of the advanced-control, general-purpose and basic timers.

# 2.22.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 and TIM8 support independent DMA request generation.

# 2.22.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F74xxx devices (see *Table 6* for differences).

## • TIM2, TIM3, TIM4, TIM5

The STM32F74xxx include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

## • TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

# 2.24 Universal synchronous/asynchronous receiver transmitters (USART)

The device embeds USART. Refer to *Table 8: USART implementation* for the features implementation.

The universal synchronous asynchronous receiver transmitter (USART) offers a flexible means of full-duplex data exchange with external equipment requiring an industry standard NRZ asynchronous serial data format.

The USART peripheral supports:

- Full-duplex asynchronous communications

- Configurable oversampling method by 16 or 8 to give flexibility between speed and clock tolerance

- Dual clock domain allowing convenient baud rate programming independent from the PCLK reprogramming

- A common programmable transmit and receive baud rate of up to 27 Mbit/s when USART clock source is system clock frequency (Max is 216 MHz) and oversampling by 8 is used.

- Auto baud rate detection

- Programmable data word length (7 or 8 or 9 bits) word length

- Programmable data order with MSB-first or LSB-first shifting

- Programmable parity (odd, even, no parity)

- Configurable stop bits (1 or 1.5 or 2 stop bits)

- Synchronous mode and clock output for synchronous communications

- Single-wire half-duplex communications

- Separate signal polarity control for transmission and reception

- Swappable Tx/Rx pin configuration

- Hardware flow control for modem and RS-485 transceiver

- Multiprocessor communications

- LIN master synchronous break send capability and LIN slave break detection capability

- IrDA SIR encoder decoder supporting 3/16 bit duration for normal mode

- Smartcard mode (T=0 and T=1 asynchronous protocols for Smartcards as defined in the ISO/IEC 7816-3 standard )

- Support for Modbus communication

The table below summarizes the implementation of all U(S)ARTs instances

#### Table 8. USART implementation

| features <sup>(1)</sup>            | USART1/2/3/6 | UART4/5/7/8 |

|------------------------------------|--------------|-------------|

| Data Length                        | 7, 8 an      | d 9 bits    |

| Hardware flow control for modem    | Х            | X           |

| Continuous communication using DMA | X            | X           |

| Multiprocessor communication       | Х            | Х           |

| Synchronous mode                   | Х            | -           |

# 2.29 Audio and LCD PLL(PLLSAI)

An additional PLL dedicated to audio and LCD-TFT is used for SAI1 peripheral in case the PLLI2S is programmed to achieve another audio sampling frequency (49.152 MHz or 11.2896 MHz) and the audio application requires both sampling frequencies simultaneously.

The PLLSAI is also used to generate the LCD-TFT clock.

# 2.30 SD/SDIO/MMC card host interface (SDMMC)

An SDMMC host interface is available, that supports MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 50 MHz, and is compliant with the SD Memory card specification version 2.0.

The SDMMC card specification version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDMMC/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

The SDMMC can be served by the DMA controller

# 2.31 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

The devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard medium-independent interface (MII) or a reduced medium-independent interface (RMII). The microcontroller requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). The PHY is connected to the device MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the microcontroller.

The devices include the following features:

- Support of 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes.

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

| Name                    | Abbreviation                                                      | Definition                                                                                         |  |  |  |  |

|-------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin name                |                                                                   | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |

|                         | S                                                                 | Supply pin                                                                                         |  |  |  |  |

| Pin type                | I                                                                 | Input only pin                                                                                     |  |  |  |  |

|                         | I/O                                                               | Input / output pin                                                                                 |  |  |  |  |

|                         | FT                                                                | 5 V tolerant I/O                                                                                   |  |  |  |  |

| I/O structure           | TTa                                                               | 3.3 V tolerant I/O directly connected to ADC                                                       |  |  |  |  |

| NO structure            | В                                                                 | Dedicated BOOT pin                                                                                 |  |  |  |  |

|                         | RST                                                               | Bidirectional reset pin with weak pull-up resistor                                                 |  |  |  |  |

| Notes                   | Unless otherwise                                                  | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |

| Alternate<br>functions  | Functions selected                                                | d through GPIOx_AFR registers                                                                      |  |  |  |  |

| Additional<br>functions | Eulertions directly selected/enabled through peripheral registers |                                                                                                    |  |  |  |  |

#### Table 9. Legend/abbreviations used in the pinout table

# Table 10. STM32F745xx and STM32F746xx pin and ball definition

|         |          | F        | Pin Nu  | umbei    | r       |         |          |                                                            |          |               |       |                                                                                               |                         |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                           | Additional<br>functions |

| 1       | A3       | D8       | 1       | A2       | 1       | 1       | A3       | PE2                                                        | I/O      | FT            | -     | TRACECLK, SPI4_SCK,<br>SAI1_MCLK_A,<br>QUADSPI_BK1_IO2,<br>ETH_MII_TXD3,<br>FMC_A23, EVENTOUT | -                       |

| 2       | В3       | C10      | 2       | A1       | 2       | 2       | A2       | PE3                                                        | I/O      | FT            | -     | TRACED0, SAI1_SD_B,<br>FMC_A19, EVENTOUT                                                      | -                       |

| 3       | C3       | B11      | 3       | B1       | 3       | 3       | A1       | PE4                                                        | I/O      | FT            | -     | TRACED1, SPI4_NSS,<br>SAI1_FS_A, FMC_A20,<br>DCMI_D4, LCD_B0,<br>EVENTOUT                     | -                       |

|         |          |          |         | umber    |         |         |          |                                                            |          |               |       |                                                                                                                       |                         |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure | Notes | Alternate functions                                                                                                   | Additional<br>functions |

| -       | -        | G2       | 93      | H14      | 112     | 135     | H14      | PG8                                                        | I/O      | FT            | -     | SPI6_NSS,<br>SPDIFRX_IN2,<br>USART6_RTS,<br>ETH_PPS_OUT,<br>FMC_SDCLK,<br>EVENTOUT                                    | -                       |

| -       | -        | D2       | 94      | G12      | 113     | 136     | G10      | VSS                                                        | S        | -             | -     | -                                                                                                                     | -                       |

| -       | F6       | G1       | 95      | H13      | 114     | 137     | G11      | VDDUSB                                                     | S        | -             | -     | -                                                                                                                     | -                       |

| 63      | F10      | F2       | 96      | H15      | 115     | 138     | H15      | PC6                                                        | I/O      | FT            | -     | TIM3_CH1, TIM8_CH1,<br>I2S2_MCK, USART6_TX,<br>SDMMC1_D6, DCMI_D0,<br>LCD_HSYNC,<br>EVENTOUT                          | -                       |

| 64      | E10      | F3       | 97      | G15      | 116     | 139     | G15      | PC7                                                        | I/O      | FT            | -     | TIM3_CH2, TIM8_CH2,<br>I2S3_MCK, USART6_RX,<br>SDMMC1_D7, DCMI_D1,<br>LCD_G6, EVENTOUT                                | -                       |

| 65      | F9       | E4       | 98      | G14      | 117     | 140     | G14      | PC8                                                        | I/O      | FT            | -     | TRACED1, TIM3_CH3,<br>TIM8_CH3, UART5_RTS,<br>USART6_CK,<br>SDMMC1_D0, DCMI_D2,<br>EVENTOUT                           | -                       |

| 66      | E9       | E3       | 99      | F14      | 118     | 141     | F14      | PC9                                                        | I/O      | FT            | -     | MCO2, TIM3_CH4,<br>TIM8_CH4, I2C3_SDA,<br>I2S_CKIN, UART5_CTS,<br>QUADSPI_BK1_IO0,<br>SDMMC1_D1, DCMI_D3,<br>EVENTOUT | -                       |

| 67      | D9       | F1       | 100     | F15      | 119     | 142     | F15      | PA8                                                        | I/O      | FT            | -     | MCO1, TIM1_CH1,<br>TIM8_BKIN2, I2C3_SCL,<br>USART1_CK,<br>OTG_FS_SOF, LCD_R6,<br>EVENTOUT                             | -                       |

| 68      | C9       | E2       | 101     | E15      | 120     | 143     | E15      | PA9                                                        | I/O      | FT            | -     | TIM1_CH2, I2C3_SMBA,<br>SPI2_SCK/I2S2_CK,<br>USART1_TX, DCMI_D0,<br>EVENTOUT                                          | OTG_FS_VB<br>US         |

# Table 10. STM32F745xx and STM32F746xx pin and ball definition (continued)

| 5 |

|---|

|---|

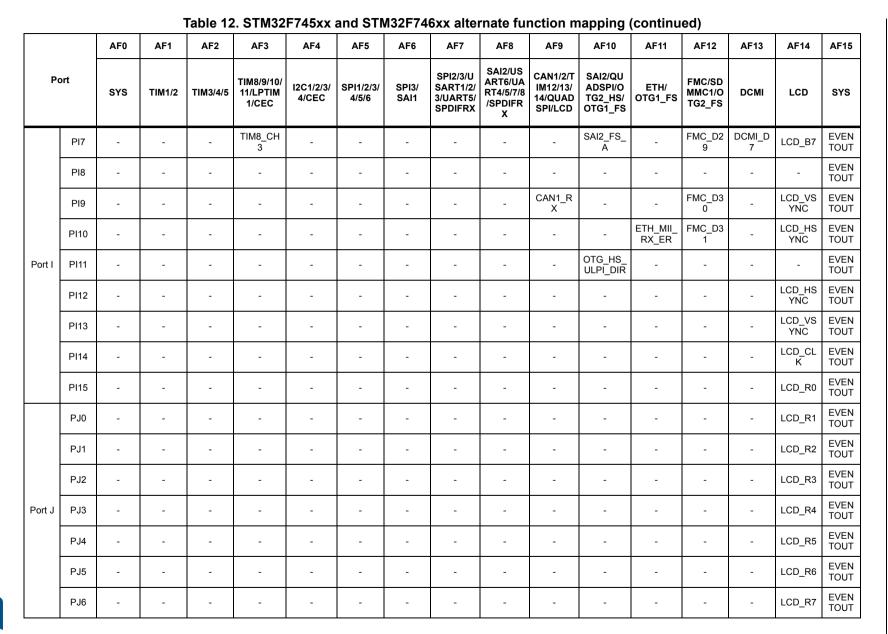

#### Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

| Table 12. STW32F745XX and STW32F746XX alternate function mapping (continued) |      |             |        |              |                                 |                    |                    |                           |                                             |                                                 |                                            |                                          |                                        |                            |             |               |              |

|------------------------------------------------------------------------------|------|-------------|--------|--------------|---------------------------------|--------------------|--------------------|---------------------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|----------------------------------------|----------------------------|-------------|---------------|--------------|

|                                                                              |      | AF0         | AF1    | AF2          | AF3                             | AF4                | AF5                | AF6                       | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11                                   | AF12                       | AF13        | AF14          | AF15         |

| Po                                                                           | ort  | SYS         | TIM1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1             | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS                        | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI        | LCD           | SYS          |

|                                                                              | PC4  | -           | -      | -            | -                               | -                  | I2S1_M<br>CK       | -                         | -                                           | SPDIFRX<br>_IN2                                 | -                                          | -                                        | ETH_MII_<br>RXD0/ET<br>H_RMII_<br>RXD0 | FMC_SD<br>NE0              | -           | -             | EVEN<br>TOUT |

|                                                                              | PC5  | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | SPDIFRX<br>_IN3                                 | -                                          | -                                        | ETH_MII_<br>RXD1/ET<br>H_RMII_<br>RXD1 | FMC_SD<br>CKE0             | -           | -             | EVEN<br>TOUT |

|                                                                              | PC6  | -           | -      | TIM3_C<br>H1 | TIM8_CH<br>1                    | -                  | I2S2_M<br>CK       | -                         | -                                           | USART6<br>_TX                                   | -                                          | -                                        | -                                      | SDMMC<br>1_D6              | DCMI_D<br>0 | LCD_HS<br>YNC | EVEN<br>TOUT |

|                                                                              | PC7  | -           | -      | TIM3_C<br>H2 | TIM8_<br>CH2                    | -                  | -                  | I2S3_M<br>CK              | -                                           | USART6<br>_RX                                   | -                                          | -                                        | -                                      | SDMMC<br>1_D7              | DCMI_D<br>1 | LCD_G6        | EVEN<br>TOUT |

|                                                                              | PC8  | TRACE<br>D1 | -      | TIM3_C<br>H3 | TIM8_<br>CH3                    | -                  | -                  | -                         | UART5_<br>RTS                               | USART6<br>_CK                                   | -                                          | -                                        | -                                      | SDMMC<br>1_D0              | DCMI_D<br>2 | -             | EVEN<br>TOUT |

| Port C                                                                       | PC9  | MCO2        | -      | TIM3_C<br>H4 | TIM8_<br>CH4                    | I2C3_SD<br>A       | I2S_CKI<br>N       | -                         | UART5_<br>CTS                               | -                                               | QUADSP<br>I_BK1_IO<br>0                    | -                                        | -                                      | SDMMC<br>1_D1              | DCMI_D<br>3 | -             | EVEN<br>TOUT |

|                                                                              | PC10 | -           | -      | -            | -                               | -                  | -                  | SPI3_SC<br>K/I2S3_<br>CK  | USART3<br>_TX                               | UART4_T<br>X                                    | QUADSP<br>I_BK1_IO<br>1                    | -                                        | -                                      | SDMMC<br>1_D2              | DCMI_D<br>8 | LCD_R2        | EVEN<br>TOUT |

|                                                                              | PC11 | -           | -      | -            | -                               | -                  | -                  | SPI3_MI<br>SO             | USART3<br>_RX                               | UART4_<br>RX                                    | QUADSP<br>I_BK2_N<br>CS                    | -                                        | -                                      | SDMMC<br>1_D3              | DCMI_D<br>4 | -             | EVEN<br>TOUT |

|                                                                              | PC12 | TRACE<br>D3 | -      | -            | -                               | -                  | -                  | SPI3_M<br>OSI/I2S3<br>_SD | USART3<br>_CK                               | UART5_T<br>X                                    | -                                          | -                                        | -                                      | SDMMC<br>1_CK              | DCMI_D<br>9 | -             | EVEN<br>TOUT |

|                                                                              | PC13 | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | -           | -             | EVEN<br>TOUT |

|                                                                              | PC14 | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | -           | -             | EVEN<br>TOUT |

|                                                                              | PC15 | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | -           | -             | EVEN<br>TOUT |

STM32F745xx STM32F746xx

79/227

Pinouts and pin description

86/227

DocID027590 Rev 4

# Pinouts and pin description

STM32F745xx STM32F746xx

# 5 Electrical characteristics

# 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

# 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

# 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.3$  V (for the 1.7 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

# 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 5.1.4 Loading capacitor

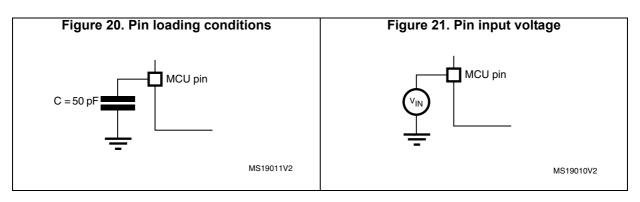

The loading conditions used for pin parameter measurement are shown in *Figure 20*.

# 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 21*.

## STM32F745xx STM32F746xx

- 2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

- 3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

- 4. Guaranteed by test in production.

#### Table 25. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART ON except prefetch / L1-cache ON) or SRAM on AXI (L1-cache ON), regulator ON

| Sympol          | Doromotor              | Conditions                                   | £ (MILI-)               | Turn |                        | Unit                   |                         |      |

|-----------------|------------------------|----------------------------------------------|-------------------------|------|------------------------|------------------------|-------------------------|------|

| Symbol          | Parameter              | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур  | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                 |                        |                                              | 216                     | 186  | 213                    | 234                    | -                       |      |

|                 |                        |                                              | 200                     | 172  | 197                    | 217                    | 235                     |      |

|                 |                        |                                              | 180                     | 152  | 175                    | 189                    | 202                     |      |

|                 |                        | All peripherals<br>enabled <sup>(2)(3)</sup> | 168                     | 135  | 155                    | 168                    | 180                     |      |

|                 |                        |                                              | 144                     | 104  | 119                    | 130                    | 140                     | mA   |

|                 |                        |                                              | 60                      | 46   | 53                     | 64                     | 74                      |      |

|                 | Supply                 |                                              | 25                      | 22   | 25                     | 36                     | 47                      |      |

| I <sub>DD</sub> | current in<br>RUN mode | All peripherals<br>disabled <sup>(3)</sup>   | 216                     | 108  | 124                    | 146                    | -                       | ШA   |

|                 |                        |                                              | 200                     | 100  | 115                    | 135                    | 154                     | -    |

|                 |                        |                                              | 180                     | 89   | 102                    | 116                    | 129                     |      |

|                 |                        |                                              | 168                     | 79   | 90                     | 103                    | 115                     |      |

|                 |                        |                                              | 144                     | 61   | 69                     | 80                     | 90                      |      |

|                 |                        |                                              | 60                      | 27   | 31                     | 42                     | 52                      |      |

|                 |                        |                                              | 25 12 15 2              |      |                        | 26                     | 36                      |      |

1. Guaranteed by characterization results.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

| Symbol            | Parameter                | Conditions                                                                           | I/O toggling<br>frequency (fsw)<br>MHz | Typ<br>V <sub>DD</sub> = 3.3 V | Typ<br>V <sub>DD</sub> = 1.8 V | Unit |

|-------------------|--------------------------|--------------------------------------------------------------------------------------|----------------------------------------|--------------------------------|--------------------------------|------|

|                   |                          |                                                                                      | 2                                      | 0.3                            | 0.1                            |      |

|                   |                          |                                                                                      | 8                                      | 1.0                            | 0.5                            |      |

|                   |                          | C <sub>EXT</sub> = 22 pF<br>C = C <sub>INT</sub> + C <sub>S</sub> + C <sub>EXT</sub> | 25                                     | 3.5                            | 1.6                            |      |

|                   | I/O switching<br>Current |                                                                                      | 50                                     | 5.9                            | 4.2                            | - mA |

|                   |                          |                                                                                      | 60                                     | 10.0                           | 4.4                            |      |

|                   |                          |                                                                                      | 84                                     | 19.12                          | 5.8                            |      |

| I <sub>DDIO</sub> |                          |                                                                                      | 90                                     | 19.6                           | -                              |      |

|                   |                          |                                                                                      | 2                                      | 0.3                            | 0.2                            |      |

|                   |                          |                                                                                      | 8                                      | 1.3                            | 0.7                            |      |

|                   |                          | $C_{EXT} = 33 \text{ pF}$<br>$C = C_{INT} + C_S + C_{EXT}$                           | 25                                     | 3.5                            | 2.3                            |      |

|                   |                          |                                                                                      | 50                                     | 10.26                          | 5.19                           |      |

|                   |                          |                                                                                      | 60                                     | 16.53                          | -                              |      |

# Table 34. Switching output I/O current consumption<sup>(1)</sup> (continued)

1. CINT + C<sub>S.</sub> PCB board capacitance including the pad pin is estimated to15 pF.

# On-chip peripheral current consumption

The MCU is placed under the following conditions:

- At startup, all I/O pins are in analog input configuration.

- All peripherals are disabled unless otherwise mentioned.

- I/O compensation cell enabled.

- The ART/L1-cache is ON.

- Scale 1 mode selected, internal digital voltage V12 = 1.32 V.

- HCLK is the system clock. f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2.

The given value is calculated by measuring the difference of current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- f<sub>HCLK</sub> = 216 MHz (Scale 1 + over-drive ON), f<sub>HCLK</sub> = 168 MHz (Scale 2), f<sub>HCLK</sub> = 144 MHz (Scale 3)

- Ambient operating temperature is 25 °C and V<sub>DD</sub>=3.3 V.

| Symbol | Parameter                    | Test conditions                                                     | Тур | Max <sup>(1)</sup> | Unit |

|--------|------------------------------|---------------------------------------------------------------------|-----|--------------------|------|

| ET     | Total unadjusted error       |                                                                     | ±4  | ±7                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,       | ±2  | ±3                 |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REF</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                         | ±2  | ±3                 |      |

| EL     | Integral linearity error     |                                                                     | ±3  | ±6                 |      |

Table 65. ADC static accuracy at f<sub>ADC</sub> = 36 MHz

1. Guaranteed by characterization results.

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =18 MHz     | 10.3 | 10.4 | -   | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+} = 1.7 V$ | 64   | 64.2 | -   |      |

| SNR    | Signal-to-noise ratio                | Input Frequency = 20 KHz     | 64   | 65   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 67 | - 72 | -   |      |

1. Guaranteed by characterization results.

# Table 67. ADC dynamic accuracy at $f_{ADC}$ = 36 MHz - limited test conditions<sup>(1)</sup>

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =36 MHz     | 10.6 | 10.8 | -   | bits |

| SINAD  | Signal-to noise and distortion ratio | $V_{DDA} = V_{REF+} = 3.3 V$ | 66   | 67   | -   |      |

| SNR    | Signal-to noise ratio                | Input Frequency = 20 KHz     | 64   | 68   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 70 | - 72 | -   |      |

1. Guaranteed by characterization results.

Note: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.17 does not affect the ADC accuracy.

| Symbol                  | Parameter                                                                          |            | Min    | Тур | Мах    | Unit |  |  |  |

|-------------------------|------------------------------------------------------------------------------------|------------|--------|-----|--------|------|--|--|--|

| -                       | f <sub>HCLK</sub> value to guarantee proper operation of USB HS interface          |            | 30     | -   | -      | MHz  |  |  |  |

| F <sub>START_8BIT</sub> | Frequency (first transition) 8-bit ±10%                                            |            | 54     | 60  | 66     | MHz  |  |  |  |

| F <sub>STEADY</sub>     | Frequency (steady state) ±500 ppm                                                  |            | 59.97  | 60  | 60.03  | MHz  |  |  |  |

| D <sub>START_8BIT</sub> | Duty cycle (first transition) 8-bit ±10%                                           |            | 40     | 50  | 60     | %    |  |  |  |

| D <sub>STEADY</sub>     | Duty cycle (steady state) ±500 ppm                                                 |            | 49.975 | 50  | 50.025 | %    |  |  |  |

| t <sub>STEADY</sub>     | Time to reach the steady state frequency and duty cycle after the first transition |            | -      | -   | 1.4    | ms   |  |  |  |

| t <sub>START_DEV</sub>  | Clock startup time after the                                                       | Peripheral | -      | -   | 5.6    | me   |  |  |  |

| t <sub>START_HOST</sub> | de-assertion of SuspendM                                                           | Host       | -      | -   | -      | ms   |  |  |  |

| t <sub>PREP</sub>       | PHY preparation time after the first transition of the input clock                 |            | -      | -   | -      | μs   |  |  |  |

| Table 83. USB HS | clock timina | parameters <sup>(1)</sup> |

|------------------|--------------|---------------------------|

|------------------|--------------|---------------------------|

1. Guaranteed by design.

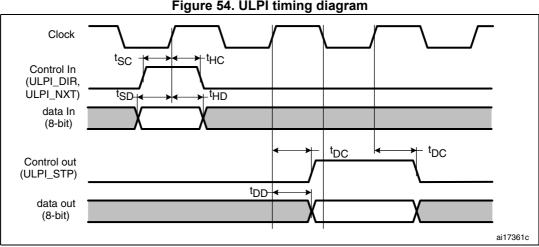

# Figure 54. ULPI timing diagram

| Symbol                    | Symbol Parameter                          |                         | Max                     | Unit |  |  |  |  |  |

|---------------------------|-------------------------------------------|-------------------------|-------------------------|------|--|--|--|--|--|

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> -0.5 | 8T <sub>HCLK</sub> +1.5 |      |  |  |  |  |  |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 6T <sub>HCLK</sub> -0.5 | 6T <sub>HCLK</sub> +1   | ns   |  |  |  |  |  |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> −1   | -                       | 115  |  |  |  |  |  |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +2   | -                       |      |  |  |  |  |  |

Table 91. Asynchronous non-multiplexed SRAM/PSRAM/NOR write - NWAIT timings<sup>(1)</sup>

1. Guaranteed by characterization results.

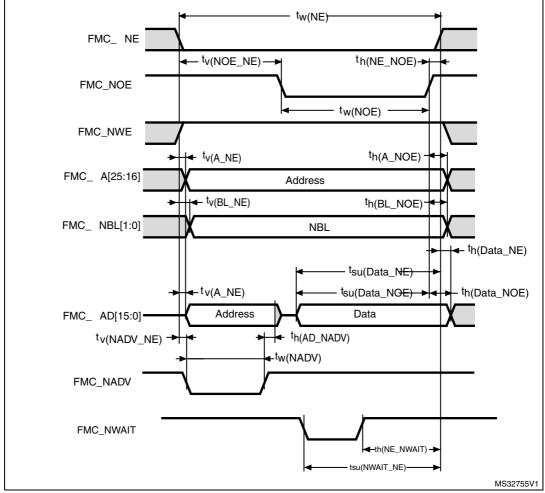

# Figure 60. Asynchronous multiplexed PSRAM/NOR read waveforms

| Symbol  | Parameter               | Conditions                        | Min        | Тур | Max       | Unit |

|---------|-------------------------|-----------------------------------|------------|-----|-----------|------|

| tw(CKH) | Quad-SPI clock high and |                                   | t(CK)/2 -1 | -   | t(CK)/2   |      |

| tw(CKL) | low time                | -                                 | t(CK)/2    | -   | t(CK)/2+1 |      |

| ts(IN)  | Data input setup time   |                                   | 1          | -   | -         |      |

| th(IN)  | Data input hold time    | -                                 | 3          | -   | -         | ns   |

|         | Data output valid time  | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>  | -          | 1.5 | 3         |      |

| tv(OUT) |                         | 1.71 V <v<sub>DD&lt;3.6 V</v<sub> | -          | 1.5 | 4         |      |

| th(OUT) | Data output hold time   | -                                 | 0          | -   | -         |      |

Table 106. Quad-SPI characteristics (continued)in SDR mode<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

| Symbol                | Parameter                | Conditions                                     | Min             | Тур              | Max              | Unit |  |

|-----------------------|--------------------------|------------------------------------------------|-----------------|------------------|------------------|------|--|

|                       |                          | 2.7 V <v<sub>DD&lt;3.6 V<br/>CL=20 pF</v<sub>  | -               | -                | 80               |      |  |

| Fck1/t(CK)            | Quad-SPI clock frequency | 1.8 V <v<sub>DD&lt;3.6 V<br/>CL=15 pF</v<sub>  |                 | -                | 80               | MHz  |  |

|                       |                          | 1.71 V <v<sub>DD&lt;3.6 V<br/>CL=10 pF</v<sub> | -               | -                | 80               |      |  |

| tw(CKH)               | Quad-SPI clock high and  |                                                | t(CK)/2<br>-1   | -                | t(CK)/2          |      |  |

| tw(CKL)               | low time                 |                                                | t(CK)/2         | -                | t(CK)/2+<br>1    |      |  |

| ts(IN),               | Data input setup time    | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>               | 1.5             |                  |                  |      |  |

| tsf(IN)               | Data input setup time    | 1.71 V <v<sub>DD&lt;2 V</v<sub>                | 0.75            | -                | -                |      |  |

| thr(IN),              | Data input hold time     | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>               | 3.5             | -                | -                |      |  |

| thf(IN)               | Data input noid time     | 1.71 V <v<sub>DD&lt;2 V</v<sub>                | 4.5             |                  |                  | ns   |  |

|                       |                          | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>               | -               | 8                | 10.5             | 115  |  |

| tvr(OUT),<br>tvf(OUT) | Data output valid time   | 1.71 V <v<sub>DD&lt;3.6 V<br/>DHHC=0</v<sub>   | -               | 8                | 14.5             |      |  |

|                       |                          | DHHC=1<br>Pres=1, 2                            | -               | Thclk/2<br>+1.75 | Thclk/2<br>+2.25 |      |  |

|                       |                          | DHHC=0                                         | 7.5             | -                | -                |      |  |

| thr(OUT),<br>thf(OUT) | Data output hold time    | DHHC=1<br>Pres=1, 2                            | Thclk/2<br>+1.5 | -                | -                |      |  |

1. Guaranteed by characterization results.

| data   |        |             |        |                       |        |        |  |  |

|--------|--------|-------------|--------|-----------------------|--------|--------|--|--|

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |  |  |

| Symbol | Min    | Тур         | Мах    | Min                   | Тур    | Мах    |  |  |

| А      | -      | -           | 1.600  | -                     | -      | 0.0630 |  |  |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |  |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |  |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |  |  |

| D      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

| D3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |  |

| E      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |  |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |  |

| E3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |  |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |  |  |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |  |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |  |  |

| k      | 0°     | 3.5°        | 7°     | 0°                    | 3.5°   | 7°     |  |  |

| CCC    | -      | -           | 0.080  | -                     | -      | 0.0031 |  |  |

| Table 112. LQPF100, | 14 x 14 mm | 100-pin low-profile | quad flat package mechanical |

|---------------------|------------|---------------------|------------------------------|

|                     |            | data                |                              |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

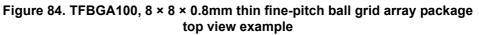

| Table 114. If BOATOUTECOMmended FOB design fulles (0.0 mm pitch BOA) |                                                                 |  |  |  |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| Dimension                                                            | Recommended values                                              |  |  |  |  |

| Pitch                                                                | 0.8                                                             |  |  |  |  |

| Dpad                                                                 | 0.400 mm                                                        |  |  |  |  |

| Dsm                                                                  | 0.470 mm typ (depends on the soldermask registration tolerance) |  |  |  |  |

| Stencil opening                                                      | 0.400 mm                                                        |  |  |  |  |

| Stencil thickness                                                    | Between 0.100 mm and 0.125 mm                                   |  |  |  |  |

| Pad trace width                                                      | 0.120 mm                                                        |  |  |  |  |

Table 114. TFBGA100 recommended PCB design rules (0.8 mm pitch BGA)

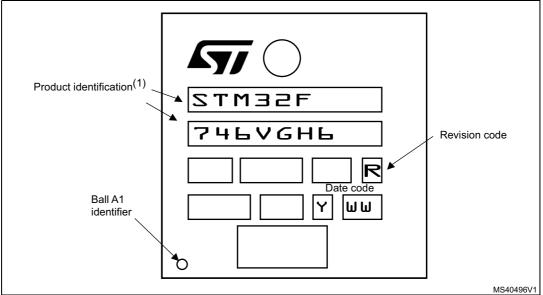

# Marking of engineering samples

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 7 Part numbering

| Table 125. Ordering information                                                                                              | on schem | e |       |   |   |       |

|------------------------------------------------------------------------------------------------------------------------------|----------|---|-------|---|---|-------|

| Example:                                                                                                                     | STM32    | F | 746 V | G | Т | 6 xxx |

| Device family                                                                                                                |          |   |       |   |   |       |

| STM32 = ARM-based 32-bit microcontroller                                                                                     |          |   |       |   |   |       |

| Product type                                                                                                                 |          |   |       |   |   |       |

| F = general-purpose                                                                                                          |          |   |       |   |   |       |

| Device subfamily                                                                                                             |          |   |       |   |   |       |

| 745= STM32F745xx, USB OTG FS/HS, camera interface Ethernet<br>746= STM32F746xx, USB OTG FS/HS, camera interface, Ethernet, L | _CD-TFT  |   |       |   |   |       |

| Pin count                                                                                                                    |          |   |       |   |   |       |

| V = 100 pins                                                                                                                 |          |   |       |   |   |       |

| Z = 143 and 144 pins                                                                                                         |          |   |       |   |   |       |

| I = 176 pins                                                                                                                 |          |   |       |   |   |       |

| B = 208 pins                                                                                                                 |          |   |       |   |   |       |

| N = 216 pins                                                                                                                 |          |   |       |   |   |       |

| Flash memory size                                                                                                            |          |   |       |   |   |       |

| E = 512 Kbytes of Flash memory                                                                                               |          |   |       |   |   |       |

| G = 1024 Kbytes of Flash memory                                                                                              |          |   |       |   |   |       |

| Package                                                                                                                      |          |   |       |   |   |       |

| T = LQFP                                                                                                                     |          |   |       |   |   |       |

| K = UFBGA                                                                                                                    |          |   |       |   |   |       |

| H = TFBGA                                                                                                                    |          |   |       |   |   |       |

| Y = WLCSP                                                                                                                    |          |   |       |   |   |       |

| Temperature range                                                                                                            |          |   |       |   |   |       |

| $6 =$ Industrial temperature range, $-40$ to $85 \degree$ C.                                                                 |          |   |       |   |   |       |

| 7 = Industrial temperature range, $-40$ to 105 °C.                                                                           |          |   |       |   |   |       |

| Options                                                                                                                      |          |   |       |   |   |       |

xxx = programmed parts

TR = tape and reel

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.