#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 114                                                                                                    |

| Program Memory Size        | 1MB (1M x 8)                                                                                           |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320K x 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                      |

| Mounting Type              | Surface Mount                                                                                          |

| Package / Case             | 144-LQFP                                                                                               |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f746zgt6e                                 |

|                            |                                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

consumption. The over-drive mode allows operating at a higher frequency than the normal mode for a given voltage scaling.

In Stop modes

The MR can be configured in two ways during Stop mode: MR operates in normal mode (default mode of MR in Stop mode) MR operates in under-drive mode (reduced leakage mode).

LPR is used in the Stop modes:

The LP regulator mode is configured by software when entering Stop mode.

Like the MR mode, the LPR can be configured in two ways during Stop mode:

- LPR operates in normal mode (default mode when LPR is ON)

- LPR operates in under-drive mode (reduced leakage mode).

- Power-down is used in Standby mode.

The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost.

Refer to *Table 3* for a summary of voltage regulator modes versus device operating modes.

Two external ceramic capacitors should be connected on  $V_{CAP\_1}$  and  $V_{CAP\_2}$  pin.

All packages have the regulator ON feature.

| Voltage regulator configuration   | Run mode | Sleep mode | Stop mode | Standby mode |

|-----------------------------------|----------|------------|-----------|--------------|

| Normal mode                       | MR       | MR         | MR or LPR | -            |

| Over-drive<br>mode <sup>(2)</sup> | MR       | MR         | -         | -            |

| Under-drive mode                  | -        | -          | MR or LPR | -            |

| Power-down mode                   | -        | -          | -         | Yes          |

Table 3. Voltage regulator configuration mode versus device operating mode<sup>(1)</sup>

1. '-' means that the corresponding configuration is not available.

2. The over-drive mode is not available when V<sub>DD</sub> = 1.7 to 2.1 V.

# 2.18.2 Regulator OFF

This feature is available only on packages featuring the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a V<sub>12</sub> voltage source through V<sub>CAP 1</sub> and V<sub>CAP 2</sub> pins.

Since the internal voltage scaling is not managed internally, the external voltage value must be aligned with the targeted maximum frequency. The two 2.2  $\mu$ F ceramic capacitors should be replaced by two 100 nF decoupling capacitors.

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

#### Pinouts and pin description

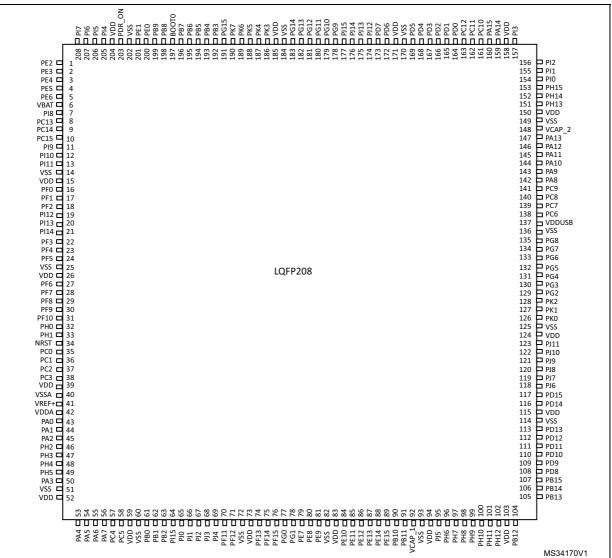

Figure 16. STM32F74xBx LQFP208 pinout

1. The above figure shows the package top view.

|         |          |          |         | umber    |         |         |          |                                                            |                                                                                                       |               |           | ball definition (continue                                                                                                              |                         |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type                                                                                              | I/O structure | Notes     | Alternate functions                                                                                                                    | Additional<br>functions |

| 31      | КЗ       | L8       | 43      | R3       | 53      | 56      | R3       | PA7                                                        | I/O                                                                                                   | FT            | (4)       | TIM1_CH1N, TIM3_CH2,<br>TIM8_CH1N,<br>SPI1_MOSI/I2S1_SD,<br>TIM14_CH1,<br>ETH_MII_RX_DV/ETH_R<br>MII_CRS_DV,<br>FMC_SDNWE,<br>EVENTOUT | ADC12_IN7               |

| 32      | G4       | M8       | 44      | N5       | 54      | 57      | N5       | PC4                                                        | I/O                                                                                                   | FT            | (4)       | I2S1_MCK,<br>SPDIFRX_IN2,<br>ETH_MII_RXD0/ETH_RM<br>II_RXD0, FMC_SDNE0,<br>EVENTOUT                                                    | ADC12_IN14              |

| 33      | H4       | N9       | 45      | P5       | 55      | 58      | P5       | PC5                                                        | I/O                                                                                                   | FT            | (4)       | SPDIFRX_IN3,<br>ETH_MII_RXD1/ETH_RM<br>II_RXD1, FMC_SDCKE0,<br>EVENTOUT                                                                | ADC12_IN15              |

| -       | -        | J7       | -       | -        | -       | 59      | L7       | VDD                                                        | S                                                                                                     | -             | -         | -                                                                                                                                      | -                       |

| -       | -        | -        | -       | -        | -       | 60      | L6       | VSS                                                        | S                                                                                                     | -             | -         | -                                                                                                                                      | -                       |

| 34      | J4       | N8       | 46      | R5       | 56      | 61      | R5       | PB0                                                        | I/O                                                                                                   | FT            | (4)       | TIM1_CH2N, TIM3_CH3,<br>TIM8_CH2N,<br>UART4_CTS, LCD_R3,<br>OTG_HS_ULPI_D1,<br>ETH_MII_RXD2,<br>EVENTOUT                               | ADC12_IN8               |

| 35      | K4       | K7       | 47      | R4       | 57      | 62      | R4       | PB1                                                        | I/O FT (4) TIM1_CH3N, TIM3_CH4,<br>TIM8_CH3N, LCD_R6,<br>OTG_HS_ULPI_D2,<br>ETH_MII_RXD3,<br>EVENTOUT |               | ADC12_IN9 |                                                                                                                                        |                         |

| 36      | G5       | L7       | 48      | M6       | 58      | 63      | M5       | PB2                                                        | I/O                                                                                                   | FT            | -         | SAI1_SD_A,<br>SPI3_MOSI/I2S3_SD,<br>QUADSPI_CLK,<br>EVENTOUT                                                                           | -                       |

| -       | -        | -        | -       | -        | -       | 64      | G4       | PI15                                                       | I/O                                                                                                   | FT            | -         | LCD_R0, EVENTOUT                                                                                                                       | -                       |

| -       | -        | -        | -       | -        | -       | 65      | R6       | PJ0                                                        | I/O                                                                                                   | FT            | -         | LCD_R1, EVENTOUT                                                                                                                       | -                       |

| -       | -        | -        | -       | -        | -       | 66      | R7       | PJ1                                                        | I/O                                                                                                   | FT            | -         | LCD_R2, EVENTOUT                                                                                                                       | -                       |

# Table 10. STM32F745xx and STM32F746xx pin and ball definition (continued)

|         |          |          |         | umbei    |         |         |          |                                                            |          |                                                                                  |       | ball definition (continue                                                         |                         |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|----------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------|-------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure                                                                    | Notes | Alternate functions                                                               | Additional<br>functions |

| 69      | D10      | D5       | 102     | D15      | 121     | 144     | D15      | PA10                                                       | I/O      | FT                                                                               | -     | TIM1_CH3, USART1_RX,<br>OTG_FS_ID, DCMI_D1,<br>EVENTOUT                           | -                       |

| 70      | C10      | D4       | 103     | C15      | 122     | 145     | C15      | PA11                                                       | I/O      | FT                                                                               | -     | TIM1_CH4,<br>USART1_CTS,<br>CAN1_RX, OTG_FS_DM,<br>LCD_R4, EVENTOUT               | -                       |

| 71      | B10      | E1       | 104     | B15      | 123     | 146     | B15      | PA12                                                       | I/O      | FT                                                                               | -     | TIM1_ETR,<br>USART1_RTS,<br>SAI2_FS_B, CAN1_TX,<br>OTG_FS_DP, LCD_R5,<br>EVENTOUT | -                       |

| 72      | A10      | D3       | 105     | A15      | 124     | 147     | A15      | PA13(JT<br>MS-<br>SWDIO)                                   | I/O      | FT                                                                               | -     | JTMS-SWDIO,<br>EVENTOUT                                                           | -                       |

| 73      | E7       | D1       | 106     | F13      | 125     | 148     | E11      | VCAP_2                                                     | S        | -                                                                                | -     | -                                                                                 | -                       |

| 74      | E5       | D2       | 107     | F12      | 126     | 149     | F10      | VSS                                                        | S        | 1                                                                                | -     | -                                                                                 | -                       |

| 75      | F5       | C1       | 108     | G13      | 127     | 150     | F11      | VDD                                                        | S        | -                                                                                | -     | -                                                                                 | -                       |

| -       | -        | -        | -       | E12      | 128     | 151     | E12      | PH13                                                       | I/O      | FT                                                                               | -     | TIM8_CH1N, CAN1_TX,<br>FMC_D21, LCD_G2,<br>EVENTOUT                               | -                       |

| -       | -        | -        | -       | E13      | 129     | 152     | E13      | PH14                                                       | I/O      | FT                                                                               | -     | TIM8_CH2N, FMC_D22,<br>DCMI_D4, LCD_G3,<br>EVENTOUT                               | -                       |

| -       | -        | -        | -       | D13      | 130     | 153     | D13      | PH15                                                       | I/O      | FT                                                                               | -     | TIM8_CH3N, FMC_D23,<br>DCMI_D11, LCD_G4,<br>EVENTOUT                              | -                       |

| -       | -        | -        | -       | E14      | 131     | 154     | E14      | P10                                                        | I/O      | /O FT - TIM5_CH4,<br>SPI2_NSS/I2S2_WS,<br>FMC_D24, DCMI_D13,<br>LCD_G5, EVENTOUT |       | -                                                                                 |                         |

| -       | -        | -        | -       | D14      | 132     | 155     | D14      | PI1                                                        | I/O      | FT                                                                               | -     | TIM8_BKIN2,<br>SPI2_SCK/I2S2_CK,<br>FMC_D25, DCMI_D8,<br>LCD_G6, EVENTOUT         | -                       |

5

AF1

AF0

AF2

AF3

DocID027590 Rev 4

81/227

| Po     | ort  | SYS          | TIM1/2         | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1   | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS  | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI        | LCD    |

|--------|------|--------------|----------------|--------------|---------------------------------|--------------------|--------------------|-----------------|---------------------------------------------|--------------------------------------|--------------------------------------------|------------------------------------------|------------------|----------------------------|-------------|--------|

| Port D | PD14 | -            | -              | TIM4_C<br>H3 | -                               | -                  | -                  | -               | -                                           | UART8_<br>CTS                        | -                                          | -                                        | -                | FMC_D0                     | -           | -      |

| FUILD  | PD15 | -            | -              | TIM4_C<br>H4 | -                               | -                  | -                  | -               | -                                           | UART8_<br>RTS                        | -                                          | -                                        | -                | FMC_D1                     | -           | -      |

|        | PE0  | -            | -              | TIM4_ET<br>R | LPTIM1_E<br>TR                  | -                  | -                  | -               | -                                           | UART8_<br>Rx                         | -                                          | SAI2_MC<br>K_A                           | -                | FMC_NB<br>L0               | DCMI_D<br>2 | -      |

|        | PE1  | -            | -              | -            | LPTIM1_I<br>N2                  | -                  | -                  | -               | -                                           | UART8_T<br>x                         | -                                          | -                                        | -                | FMC_NB<br>L1               | DCMI_D<br>3 | -      |

|        | PE2  | TRACE<br>CLK | -              | -            | -                               | -                  | SPI4_SC<br>K       | SAI1_M<br>CLK_A | -                                           | -                                    | QUADSP<br>I_BK1_IO<br>2                    | -                                        | ETH_MII_<br>TXD3 | FMC_A2<br>3                | -           | -      |

|        | PE3  | TRACE<br>D0  | -              | -            | -                               | -                  | -                  | SAI1_SD<br>_B   | -                                           | -                                    | -                                          | -                                        | -                | FMC_A1<br>9                | -           | -      |

|        | PE4  | TRACE<br>D1  | -              | -            | -                               | -                  | SPI4_NS<br>S       | SAI1_FS<br>_A   | -                                           | -                                    | -                                          | -                                        | -                | FMC_A2<br>0                | DCMI_D<br>4 | LCD_B0 |

|        | PE5  | TRACE<br>D2  | -              | -            | TIM9_CH<br>1                    | -                  | SPI4_MI<br>SO      | SAI1_SC<br>K_A  | -                                           | -                                    | -                                          | -                                        | -                | FMC_A2<br>1                | DCMI_D<br>6 | LCD_G0 |

| Port E | PE6  | TRACE<br>D3  | TIM1_B<br>KIN2 | -            | TIM9_CH<br>2                    | -                  | SPI4_M<br>OSI      | SAI1_SD<br>_A   | -                                           | -                                    | -                                          | SAI2_MC<br>K_B                           | -                | FMC_A2<br>2                | DCMI_D<br>7 | LCD_G1 |

|        | PE7  | -            | TIM1_ET<br>R   | -            | -                               | -                  | -                  | -               | -                                           | UART7_<br>Rx                         | -                                          | QUADSPI<br>_BK2_IO0                      | -                | FMC_D4                     | -           | -      |

|        | PE8  | -            | TIM1_C<br>H1N  | -            | -                               | -                  | -                  | -               | -                                           | UART7_T<br>x                         | -                                          | QUADSPI<br>_BK2_IO1                      | -                | FMC_D5                     | -           | -      |

|        | PE9  | -            | TIM1_C<br>H1   | -            | -                               | -                  | -                  | -               | -                                           | UART7_<br>RTS                        | -                                          | QUADSPI<br>_BK2_IO2                      | -                | FMC_D6                     | -           | -      |

|        | PE10 | -            | TIM1_C<br>H2N  | -            | -                               | -                  | -                  | -               | -                                           | UART7_<br>CTS                        | -                                          | QUADSPI<br>_BK2_IO3                      | -                | FMC_D7                     | -           | -      |

|        | PE11 | -            | TIM1_C<br>H2   | -            | -                               | -                  | SPI4_NS<br>S       | -               | -                                           | -                                    | -                                          | SAI2_SD_<br>B                            | -                | FMC_D8                     | -           | LCD_G3 |

|        | PE12 | -            | TIM1_C<br>H3N  | -            | -                               | -                  | SPI4_SC<br>K       | -               | -                                           | -                                    | -                                          | SAI2_SC<br>K_B                           | -                | FMC_D9                     | -           | LCD_B4 |

|        | PE13 | -            | TIM1_C<br>H3   | -            | -                               | -                  | SPI4_MI<br>SO      | -               | -                                           | -                                    | -                                          | SAI2_FS_<br>B                            | -                | FMC_D1<br>0                | -           | LCD_DE |

Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

AF7

SPI2/3/U

AF8

SAI2/US

AF9

CAN1/2/T

AF11

AF10

AF12

AF13

AF6

AF5

AF4

AF14

AF15

SYS

EVEN TOUT

EVEN TOUT EVEN TOUT EVEN TOUT EVEN TOUT

EVEN TOUT EVEN TOUT EVEN TOUT EVEN TOUT

EVEN TOUT EVEN

TOUT EVEN TOUT EVEN TOUT EVEN TOUT EVEN TOUT

EVEN TOUT

| 8 <u>3</u> |  |

|------------|--|

| Ñ          |  |

| 22         |  |

DocID027590 Rev 4

577

|        |      | AF0 | AF1    | AF2      | AF3                             | AF4                | AF5                | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11            | AF12                       | AF13           | AF14        | AF15         |

|--------|------|-----|--------|----------|---------------------------------|--------------------|--------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|-----------------|----------------------------|----------------|-------------|--------------|

| Po     | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI           | LCD         | SYS          |

|        | PF13 | -   | -      | -        | -                               | I2C4_SM<br>BA      | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A7                     | -              | -           | EVEN<br>TOUT |

| Port F | PF14 | -   | -      | -        | -                               | I2C4_SC<br>L       | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A8                     | -              | -           | EVEN<br>TOUT |

|        | PF15 | -   | -      | -        | -                               | I2C4_SD<br>A       | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A9                     | -              | -           | EVEN<br>TOUT |

|        | PG0  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>0                | -              | -           | EVEN<br>TOUT |

|        | PG1  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>1                | -              | -           | EVEN<br>TOUT |

|        | PG2  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>2                | -              | -           | EVEN<br>TOUT |

|        | PG3  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>3                | -              | -           | EVEN<br>TOUT |

|        | PG4  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>4/FMC_<br>BA0    | -              | -           | EVEN<br>TOUT |

| Port G | PG5  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_A1<br>5/FMC_<br>BA1    | -              | -           | EVEN<br>TOUT |

|        | PG6  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | DCMI_D<br>12   | LCD_R7      | EVEN<br>TOUT |

|        | PG7  | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | USART6<br>_CK                                   | -                                          | -                                        | -               | FMC_IN<br>T                | DCMI_D<br>13   | LCD_CL<br>K | EVEN<br>TOUT |

|        | PG8  | -   | -      | -        | -                               | -                  | SPI6_NS<br>S       | -             | SPDIFRX<br>_IN2                             | USART6<br>_RTS                                  | -                                          | -                                        | ETH_PPS<br>_OUT | FMC_SD<br>CLK              | -              | -           | EVEN<br>TOUT |

|        | PG9  | -   | -      | -        | -                               | -                  | -                  | -             | SPDIFRX<br>_IN3                             | USART6<br>_RX                                   | QUADSP<br>I_BK2_IO<br>2                    | SAI2_FS_<br>B                            | -               | FMC_NE<br>2/FMC_<br>NCE    | DCMI_V<br>SYNC | -           | EVEN<br>TOUT |

|        | PG10 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | LCD_G3                                     | SAI2_SD_<br>B                            | -               | FMC_NE<br>3                | DCMI_D<br>2    | LCD_B2      | EVEN<br>TOUT |

Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

# 5.3 Operating conditions

# 5.3.1 General operating conditions

| Symbol                          | Parameter                                                  | Conditions <sup>(1)</sup>                                                              |                       | Min                | Тур | Max                | Unit |  |

|---------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------|--------------------|-----|--------------------|------|--|

|                                 |                                                            | Power Scale 3 (VOS[1:0] bits in<br>PWR_CR register = 0x01), Regu<br>ON, over-drive OFF | ulator                | 0                  | -   | 144                |      |  |

|                                 |                                                            | Power Scale 2 (VOS[1:0] bits in                                                        | Over-<br>drive<br>OFF |                    | -   | 168                |      |  |

| f <sub>HCLK</sub>               | Internal AHB clock frequency                               | PWR_CR register = 0x10),<br>Regulator ON                                               | Over-<br>drive<br>ON  | 0                  | -   | 180                |      |  |

|                                 |                                                            | Power Scale 1 (VOS[1:0] bits in<br>PWR CR register= 0x11),                             | Over-<br>drive<br>OFF | 0                  | -   | 180                | MHz  |  |

|                                 |                                                            | Regulator ON                                                                           | Over-<br>drive<br>ON  |                    | -   | 216 <sup>(2)</sup> |      |  |

| f                               | Internal APB1 clock frequency                              | Over-drive OFF                                                                         |                       | 0                  | -   | 45                 |      |  |

| f <sub>PCLK1</sub>              | Internal AFBT Clock frequency                              | Over-drive ON                                                                          |                       | 0                  | -   | 54                 |      |  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                              | Over-drive OFF                                                                         |                       | 0                  | -   | 90                 |      |  |

| 'PCLK2                          |                                                            | Over-drive ON                                                                          |                       | 0                  | -   | 108                |      |  |

| $V_{DD}$                        | Standard operating voltage                                 | -                                                                                      |                       | 1.7 <sup>(3)</sup> | -   | 3.6                |      |  |

| V <sub>DDA</sub> <sup>(4)</sup> | Analog operating voltage<br>(ADC limited to 1.2 M samples) | Must be the same potential as V                                                        | (6)                   | 1.7 <sup>(3)</sup> | -   | 2.4                |      |  |

| (5)                             | Analog operating voltage<br>(ADC limited to 2.4 M samples) | Must be the same potential as $V_{DD}{}^{(6)}$                                         |                       | 2.4                | -   | 3.6                | v    |  |

|                                 | USB supply voltage (supply                                 | USB not used                                                                           | 1.7                   | 3.3                | 3.6 | 1                  |      |  |

| V <sub>DDUSB</sub>              | voltage for PA11,PA12, PB14<br>and PB15 pins)              | USB used                                                                               |                       | 3.0                | -   | 3.6                |      |  |

| $V_{BAT}$                       | Backup operating voltage                                   | -                                                                                      |                       | 1.65               | -   | 3.6                |      |  |

# Table 17. General operating conditions

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted both to f<sub>HCLK</sub> frequency and V<sub>DD</sub> range (see *Table 18: Limitations depending on the operating power supply range*).

- When the regulator is ON, the voltage scaling and over-drive mode are adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for  $f_{HCLK} \le 144$  MHz

- Scale 2 for 144 MHz <  $f_{HCLK} \le 168$  MHz

- Scale 1 for 168 MHz <  $f_{HCLK} \le 216$  MHz. The over-drive is only ON at 216 MHz.

- When the regulator is OFF, the V12 is provided externally as described in *Table 17: General operating conditions*:

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/4$ , and  $f_{PCLK2} = f_{HCLK}/2$ .

- External clock frequency is 25 MHz and PLL is ON when f<sub>HCLK</sub> is higher than 25 MHz.

- The typical current consumption values are obtained for 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range and for T<sub>A</sub>= 25 °C unless otherwise specified.

- The maximum values are obtained for 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range and a maximum ambient temperature (T<sub>A</sub>) unless otherwise specified.

- For the voltage range 1.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V, the maximum frequency is 180 MHz.

# Table 24. Typical and maximum current consumption in Run mode, code with data processingrunning from ITCM RAM, regulator ON

| Symbol          | Doromotor              | Conditions                                   | £ (MILI-)               | Turn                       |                    | Max <sup>(1)</sup>     |                         | Unit               |                    |  |

|-----------------|------------------------|----------------------------------------------|-------------------------|----------------------------|--------------------|------------------------|-------------------------|--------------------|--------------------|--|

| I <sub>DD</sub> | Parameter              | Conditions                                   | f <sub>HCLK</sub> (MHz) | (MHz) Typ T <sub>A</sub> = |                    | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit               |                    |  |

|                 |                        | All peripherals<br>enabled <sup>(2)(3)</sup> | 216                     | 178                        | 208 <sup>(4)</sup> | 230 <sup>(4)</sup>     | -                       |                    |                    |  |

|                 |                        |                                              |                         |                            | 200                | 165                    | 193                     | 212                | 230                |  |

|                 |                        |                                              |                         |                            | 180                | 147                    | 171 <sup>(4)</sup>      | 185 <sup>(4)</sup> | 198 <sup>(4)</sup> |  |

|                 |                        |                                              | 168                     | 130                        | 152                | 164                    | 177                     |                    |                    |  |

|                 | Supply                 |                                              | 144                     | 100                        | 116                | 127                    | 137                     |                    |                    |  |

|                 |                        |                                              | 60                      | 44                         | 52                 | 63                     | 73                      |                    |                    |  |

|                 |                        |                                              | 25                      | 21                         | 25                 | 36 46                  |                         |                    |                    |  |

| 'DD             | current in<br>RUN mode |                                              | 216                     | 102                        | 120 <sup>(4)</sup> | 141 <sup>(4)</sup>     | -                       | mA                 |                    |  |

|                 |                        |                                              | 200                     | 95                         | 111                | 131                    | 149                     |                    |                    |  |

|                 |                        |                                              | 180                     | 84                         | 98 <sup>(4)</sup>  | 112 <sup>(4)</sup>     | 125 <sup>(4)</sup>      |                    |                    |  |

|                 |                        | All peripherals<br>disabled <sup>(3)</sup>   | 168                     | 75                         | 87                 | 100                    | 112                     |                    |                    |  |

|                 |                        |                                              | 144                     | 58                         | 67                 | 77                     | 88                      |                    |                    |  |

|                 |                        |                                              | 60 25                   |                            | 30                 | 41                     | 51                      |                    |                    |  |

|                 |                        |                                              | 25                      | 12                         | 15                 | 25                     | 36                      |                    |                    |  |

1. Guaranteed by characterization results.

#### STM32F745xx STM32F746xx

- 2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

- 3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

- 4. Guaranteed by test in production.

#### Table 25. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART ON except prefetch / L1-cache ON) or SRAM on AXI (L1-cache ON), regulator ON

| Sympol          | Doromotor            | Conditions                                   | £ (MILI-)               | Turn |                        | Max <sup>(1)</sup>     |                         | Unit |  |

|-----------------|----------------------|----------------------------------------------|-------------------------|------|------------------------|------------------------|-------------------------|------|--|

| Symbol          | Parameter            | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур  | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |  |

|                 |                      |                                              | 216                     | 186  | 213                    | 234                    | -                       |      |  |

|                 |                      |                                              |                         | 200  | 172                    | 197                    | 217                     | 235  |  |

|                 |                      |                                              | 180                     | 152  | 175                    | 189                    | 202                     |      |  |

|                 |                      | All peripherals<br>enabled <sup>(2)(3)</sup> | 168                     | 135  | 155                    | 168                    | 180                     |      |  |

|                 |                      | enabled                                      | 144                     | 104  | 119                    | 130                    | 140                     |      |  |

|                 |                      |                                              | 60                      | 46   | 53                     | 64                     | 74                      |      |  |

|                 | Supply<br>current in |                                              | 25                      | 22   | 25                     | 36                     | 47                      | mA   |  |

| I <sub>DD</sub> | RUN mode             |                                              | 216                     | 108  | 124                    | 146                    | -                       | ШA   |  |

|                 |                      |                                              | 200                     | 100  | 115                    | 135                    | 154                     |      |  |

|                 |                      |                                              | 180                     | 89   | 102                    | 116                    | 129                     |      |  |

|                 |                      | All peripherals<br>disabled <sup>(3)</sup>   | 168                     | 79   | 90                     | 103                    | 115                     |      |  |

|                 |                      |                                              | 144                     | 61   | 69                     | 80                     | 90                      |      |  |

|                 |                      |                                              | 60                      | 27   | 31                     | 42                     | 52                      |      |  |

|                 |                      |                                              | 25                      | 12   | 15                     | 15 26 36               |                         | 1    |  |

1. Guaranteed by characterization results.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

|          |                           |                                                                 |                            | Typ <sup>(1)</sup>         |                            |                           | Max <sup>(2)</sup>        |                                 |      |     |     |                  |                   |                   |  |

|----------|---------------------------|-----------------------------------------------------------------|----------------------------|----------------------------|----------------------------|---------------------------|---------------------------|---------------------------------|------|-----|-----|------------------|-------------------|-------------------|--|

| Symbol   | Parameter                 | Conditions                                                      | Т                          | <sub>A</sub> = 25 °        | С                          | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C      | Unit |     |     |                  |                   |                   |  |

|          |                           |                                                                 | V <sub>DD</sub> =<br>1.7 V | V <sub>DD</sub> =<br>2.4 V | V <sub>DD</sub> =<br>3.3 V | v                         | v <sub>DD</sub> = 3.3     | v                               |      |     |     |                  |                   |                   |  |

|          |                           | Backup SRAM OFF, RTC and LSE OFF                                | 1.7                        | 1.9                        | 2.3                        | 5 <sup>(3)</sup>          | 15 <sup>(3)</sup>         | 31 <sup>(3)</sup>               |      |     |     |                  |                   |                   |  |

|          |                           |                                                                 |                            |                            |                            |                           |                           | Backup SRAM ON, RTC and LSE OFF | 2.4  | 2.6 | 3.0 | 6 <sup>(3)</sup> | 20 <sup>(3)</sup> | 40 <sup>(3)</sup> |  |

|          |                           | Backup SRAM OFF, RTC ON<br>and LSE in low drive mode            | 2.1                        | 2.4                        | 2.9                        | 6                         | 19                        | 39                              |      |     |     |                  |                   |                   |  |

|          |                           | Backup SRAM OFF, RTC ON<br>and LSE in medium low drive<br>mode  | 2.1                        | 2.4                        | 2.9                        | 6                         | 19                        | 39                              |      |     |     |                  |                   |                   |  |

|          | Supply current in Standby | Backup SRAM OFF, RTC ON<br>and LSE in medium high drive<br>mode | 2.2                        | 2.5                        | 3.0                        | 7                         | 20                        | 40                              |      |     |     |                  |                   |                   |  |

| IDD_STBY | mode                      | Backup SRAM OFF, RTC ON<br>and LSE in high drive mode           | 2.3                        | 2.6                        | 3.1                        | 7                         | 20                        | 42                              | μA   |     |     |                  |                   |                   |  |

|          |                           | Backup SRAM ON, RTC ON<br>and LSE in low drive mode             | 2.7                        | 3.0                        | 3.6                        | 8                         | 23                        | 49                              |      |     |     |                  |                   |                   |  |

|          |                           | Backup SRAM ON, RTC ON<br>and LSE in Medium low drive<br>mode   | 2.7                        | 3.0                        | 3.6                        | 8                         | 23                        | 49                              |      |     |     |                  |                   |                   |  |

|          | a<br>r<br>E               | Backup SRAM ON, RTC ON<br>and LSE in Medium high drive<br>mode  | 2.8                        | 3.1                        | 3.7                        | 8                         | 24                        | 50                              |      |     |     |                  |                   |                   |  |

|          |                           | Backup SRAM ON, RTC ON<br>and LSE in High drive mode            | 2.9                        | 3.2                        | 3.8                        | 8                         | 25                        | 51                              |      |     |     |                  |                   |                   |  |

| Table 32. Typical and maximum current consumptions in Standby mode |

|--------------------------------------------------------------------|

|--------------------------------------------------------------------|

1. PDR is OFF for  $V_{DD}$ =1.7V. When the PDR is OFF (internal reset OFF), the typical current consumption is reduced by additional 1.2  $\mu$ A.

2. Guaranteed by characterization results.

3. Based on characterization, tested in production.

# Low-speed internal (LSI) RC oscillator

| Table 42. LSI oscillator characteristics <sup>(1)</sup> | ) |

|---------------------------------------------------------|---|

|---------------------------------------------------------|---|

| Symbol                              | Parameter                        | Min | Тур | Мах | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = –40 to 105  $^\circ C$  unless otherwise specified.

2. Guaranteed by characterization results.

3. Guaranteed by design.

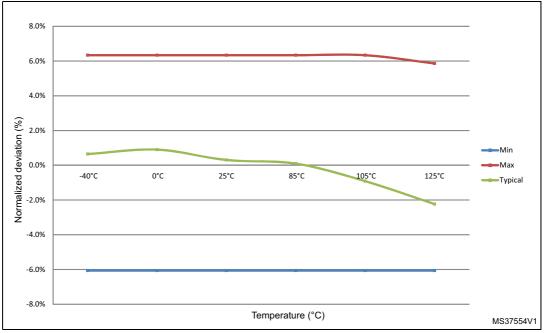

#### Figure 35. LSI deviation versus temperature

# 5.3.11 PLL characteristics

The parameters given in *Table 43* and *Table 44* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Table 43. | Main | PLL | characteristics |

|-----------|------|-----|-----------------|

|-----------|------|-----|-----------------|

| Symbol                 | Parameter                             | Conditions | Min                 | Тур | Max  | Unit |

|------------------------|---------------------------------------|------------|---------------------|-----|------|------|

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(1)</sup>        | -          | 0.95 <sup>(2)</sup> | 1   | 2.10 |      |

| f <sub>PLL_OUT</sub>   | PLL multiplier output clock           | -          | 24                  | -   | 216  |      |

| f <sub>PLL48_OUT</sub> | 48 MHz PLL multiplier output<br>clock | -          | -                   | 48  | 75   | MHz  |

| f <sub>VCO_ОUT</sub>   | PLL VCO output                        | -          | 100                 | -   | 432  | 1    |

| Symbol                  | Parameter                  | Conditions                                  | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|---------------------------------------------|--------------------|-----|--------------------|------|

| t <sub>erase256kb</sub> |                            | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 2.1 | 4                  |      |

|                         | Sector (256 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 1.5 | 2.6                | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 1   | 2                  |      |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 8   | 16                 |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 5.6 | 11.2               | s    |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 4   | 8                  |      |

|                         |                            | 32-bit program operation                    | 2.7                | -   | 3                  | V    |

| V <sub>prog</sub>       | Programming voltage        | 16-bit program operation                    | 2.1                | -   | 3.6                | V    |

|                         |                            | 8-bit program operation                     | 1.7                | -   | 3.6                | V    |

Table 48. Flash memory programming (continued)

2. The maximum programming time is measured after 100K erase operations.

| Symbol                                                                                     | Parameter                                    | Conditions          | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|--------------------------------------------------------------------------------------------|----------------------------------------------|---------------------|--------------------|-----|--------------------|------|

| t <sub>prog</sub>                                                                          | Double word programming                      |                     | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE32KB</sub>                                                                     | Sector (32 KB) erase time                    | $T_A = 0$ to +40 °C | -                  | 180 | -                  |      |

| t <sub>ERASE128KB</sub>                                                                    |                                              |                     | -                  | 450 | -                  | ms   |

| t <sub>ERASE256KB</sub>                                                                    | ASE256KB Sector (256 KB) erase time VPP      |                     | -                  | 900 | -                  |      |

| t <sub>ME</sub>                                                                            | Mass erase time                              |                     | -                  | 6.9 | -                  | S    |

| V <sub>prog</sub>                                                                          | Programming voltage                          | -                   | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                                                                            | V <sub>PP</sub> voltage range                | -                   | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                                                                            | Minimum current sunk on the $V_{\rm PP}$ pin | -                   | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> Cumulative time during<br>which V <sub>PP</sub> is applied |                                              | -                   | -                  | -   | 1                  | hour |

#### Table 49. Flash memory programming with V<sub>PP</sub>

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol | Parameter                    | Test conditions                                                     | Тур | Max <sup>(1)</sup> | Unit |  |

|--------|------------------------------|---------------------------------------------------------------------|-----|--------------------|------|--|

| ET     | Total unadjusted error       |                                                                     | ±4  | ±7                 |      |  |

| EO     | Offset error                 | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,       | ±2  | ±3                 |      |  |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REF</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                         | ±2  | ±3                 |      |  |

| EL     | Integral linearity error     |                                                                     | ±3  | ±6                 |      |  |

Table 65. ADC static accuracy at f<sub>ADC</sub> = 36 MHz

| Symbol | Parameter Test conditions            |                              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =18 MHz     | 10.3 | 10.4 | -   | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+} = 1.7 V$ | 64   | 64.2 | -   |      |

| SNR    | Signal-to-noise ratio                | Input Frequency = 20 KHz     | 64   | 65   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 67 | - 72 | -   |      |

1. Guaranteed by characterization results.

# Table 67. ADC dynamic accuracy at $f_{ADC}$ = 36 MHz - limited test conditions<sup>(1)</sup>

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =36 MHz     | 10.6 | 10.8 | -   | bits |

| SINAD  | Signal-to noise and distortion ratio | $V_{DDA} = V_{REF+} = 3.3 V$ | 66   | 67   | -   |      |

| SNR    | Signal-to noise ratio                | Input Frequency = 20 KHz     | 64   | 68   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 70 | - 72 | -   |      |

1. Guaranteed by characterization results.

Note: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.17 does not affect the ADC accuracy.

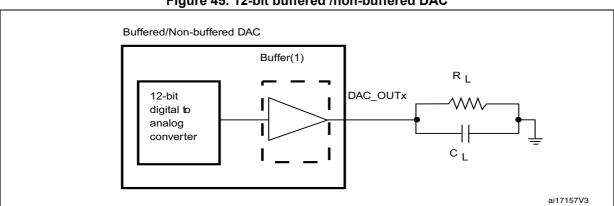

Figure 45. 12-bit buffered /non-buffered DAC

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

#### **Communications interfaces** 5.3.26

# I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s.

- Fast-mode Plus (Fm+): with a bit rate up to 1Mbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0385 reference manual) and when the I2CCLK frequency is greater than the minimum shown in the table below:

| Symbol    | Parameter           | Con            | dition                     | Min  | Unit |

|-----------|---------------------|----------------|----------------------------|------|------|

|           |                     | Standard-mode  |                            | 2    |      |

|           | I2CCLK<br>frequency | Fast-mode      | Analog Filtre ON<br>DNF=0  | 10   |      |

| f(I2CCLK) |                     |                | Analog Filtre OFF<br>DNF=1 | 9    | MHz  |

|           |                     | Fast-mode Plus | Analog Filtre ON<br>DNF=0  | 22.5 |      |

|           |                     | Fast-mode Flus | Analog Filtre OFF<br>DNF=1 | 16   |      |

#### Table 74. Minimum I2CCLK frequency in all I2C modes

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

## 5.3.27 FMC characteristics

Unless otherwise specified, the parameters given in *Table 88* to *Table 101* for the FMC interface are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 5.3.17: I/O port characteristics for more details on the input/output characteristics.

#### Asynchronous waveforms and timings

*Figure 58* through *Figure 61* represent asynchronous waveforms and *Table 88* through *Table 95* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- AddressSetupTime = 0x1

- AddressHoldTime = 0x1

- DataSetupTime = 0x1 (except for asynchronous NWAIT mode , DataSetupTime = 0x5)

- BusTurnAroundDuration = 0x0

- Capcitive load CL = 30 pF

In all timing tables, the  $T_{\mbox{HCLK}}$  is the HCLK clock period

| Table 00. Asynemonous multiplexed i ortain/rort write remainings |                                                                  |                         |                              |      |  |  |

|------------------------------------------------------------------|------------------------------------------------------------------|-------------------------|------------------------------|------|--|--|

| Symbol                                                           | Parameter                                                        | Min                     | Max                          | Unit |  |  |

| t <sub>w(NE)</sub>                                               | FMC_NE low time 9T <sub>HCLK</sub> 9T <sub>HCLK</sub> +1         |                         | 9T <sub>HCLK</sub> +1.5      |      |  |  |

| t <sub>w(NWE)</sub>                                              | FMC_NWE low time                                                 | 7T <sub>HCLK</sub> –0.5 | -0.5 7T <sub>HCLK</sub> +0.5 |      |  |  |

| t <sub>su(NWAIT_NE)</sub>                                        | FMC_NWAIT valid before FMC_NEx high 6T <sub>HCLK</sub> +2 -      |                         | -                            |      |  |  |

| t <sub>h(NE_NWAIT)</sub>                                         | NWAIT) FMC_NEx hold time after FMC_NWAIT 4T <sub>HCLK</sub> -1 - |                         | -                            |      |  |  |

1. Guaranteed by characterization results.

## Synchronous waveforms and timings

*Figure 62* through *Figure 65* represent synchronous waveforms and *Table 96* through *Table 99* provide the corresponding timings. The results shown in these tables are obtained with the following FMC configuration:

- BurstAccessMode = FMC\_BurstAccessMode\_Enable;

- MemoryType = FMC\_MemoryType\_CRAM;

- WriteBurst = FMC\_WriteBurst\_Enable;

- CLKDivision = 1;

- DataLatency = 1 for NOR Flash; DataLatency = 0 for PSRAM

- CL = 30 pF on data and address lines. CL = 10 pF on FMC\_CLK unless otherwise specified.

In all timing tables, the  $T_{HCLK}$  is the HCLK clock period.

- For 2.7 V $\leq$ V<sub>DD</sub> $\leq$ 3.6 V, maximum FMC\_CLK = 108 MHz at CL=20 pF or 90 MHz at CL=30 pF (on FMC\_CLK).

- For 1.71 V $\leq$ V<sub>DD</sub><2.7 V, maximum FMC\_CLK = 70 MHz at CL=10 pF (on FMC\_CLK).

| Symbol                      | Parameter                                  | Min                        | Max | Unit |

|-----------------------------|--------------------------------------------|----------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                             | 2T <sub>HCLK</sub> -0.5    | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)          | -                          | 1.5 |      |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)       | T <sub>HCLK</sub> +0.5     | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                | -                          | 1.5 |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high               | 0                          | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)       | -                          | 2   |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)    | (x=1625) T <sub>HCLK</sub> |     |      |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low                 | -                          | 1.5 |      |

| t <sub>(CLKH-NWEH)</sub>    | FMC_CLK high to FMC_NWE high               | T <sub>HCLK</sub> -0.5     | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid          | -                          | 3   |      |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid        | 0                          | -   |      |

| t <sub>d(CLKL-DATA)</sub>   | FMC_A/D[15:0] valid data after FMC_CLK low | -                          | 3.5 |      |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low                 | 1                          | -   |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high               | T <sub>HCLK</sub> +0.5     | -   | ]    |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high        | 2                          | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high         | 3.5                        | -   |      |

Table 97. Synchronous multiplexed PSRAM write timings<sup>(1)</sup>

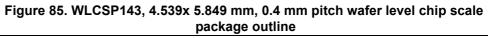

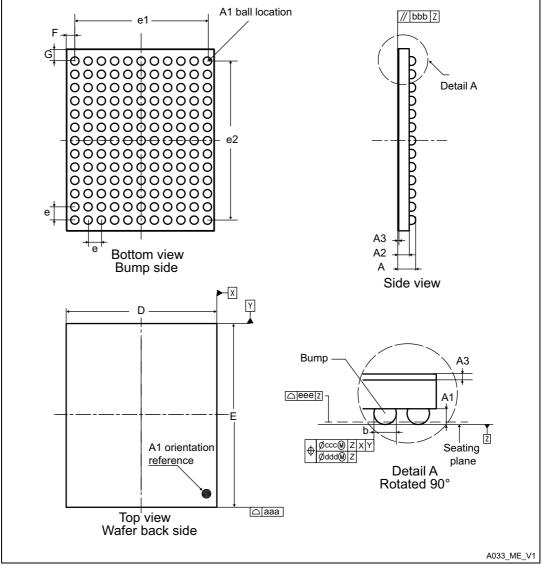

# 6.3 WLCSP143, 4.539x 5.849 mm, 0.4 mm pitch wafer level chip scale package information

1. Drawing is not to scale.

| Symbol | millimeters |       | inches <sup>(1)</sup> |        |        |        |

|--------|-------------|-------|-----------------------|--------|--------|--------|

| Min    | Min         | Тур   | Max                   | Min    | Тур    | Мах    |

| A      | 0.525       | 0.555 | 0.585                 | 0.0207 | 0.0219 | 0.0230 |

| A1     | -           | 0.175 | -                     | -      | 0.0069 | -      |

| Figure 98. UFBGA176+25, 10 x 10 x 0.65 mm, ultra fine-pitch ball grid array |

|-----------------------------------------------------------------------------|

| package recommended footprint                                               |

| 000000000000000000000000000000000000 |

|--------------------------------------|

|--------------------------------------|

#### Table 121. UFBGA176+25 recommended PCB design rules (0.65 mm pitch BGA)

| Dimension         | Recommended values                                                    |

|-------------------|-----------------------------------------------------------------------|

| Pitch             | 0.65 mm                                                               |

| Dpad              | 0.300 mm                                                              |

| Dsm               | 0.400 mm typ. (depends on the soldermask reg-<br>istration tolerance) |

| Stencil opening   | 0.300 mm                                                              |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                         |

| Pad trace width   | 0.100 mm                                                              |

| Table 127. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|--------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Date                                             | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |