Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                                        |

|----------------------------|--------------------------------------------------------------------------------------------------------|

|                            |                                                                                                        |

| Product Status             | Active                                                                                                 |

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 114                                                                                                    |

| Program Memory Size        | 1MB (1M x 8)                                                                                           |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320K x 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                      |

| Mounting Type              | Surface Mount                                                                                          |

| Package / Case             | 144-LQFP                                                                                               |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f746zgt6g                                 |

# **Contents**

| 1 | Desc | ription                                                        | 12 |

|---|------|----------------------------------------------------------------|----|

|   | 1.1  | Full compatibility throughout the family                       | 15 |

| 2 | Fund | tional overview                                                | 17 |

|   | 2.1  | ARM <sup>®</sup> Cortex <sup>®</sup> -M7 with FPU              | 17 |

|   | 2.2  | Memory protection unit                                         | 17 |

|   | 2.3  | Embedded Flash memory                                          | 18 |

|   | 2.4  | CRC (cyclic redundancy check) calculation unit                 | 18 |

|   | 2.5  | Embedded SRAM                                                  | 18 |

|   | 2.6  | AXI-AHB bus matrix                                             | 18 |

|   | 2.7  | DMA controller (DMA)                                           | 19 |

|   | 2.8  | Flexible memory controller (FMC)                               | 20 |

|   | 2.9  | Quad-SPI memory interface (QUADSPI)                            | 21 |

|   | 2.10 | LCD-TFT controller                                             | 21 |

|   | 2.11 | Chrom-ART Accelerator™ (DMA2D)                                 | 21 |

|   | 2.12 | Nested vectored interrupt controller (NVIC)                    | 22 |

|   | 2.13 | External interrupt/event controller (EXTI)                     | 22 |

|   | 2.14 | Clocks and startup                                             | 22 |

|   | 2.15 | Boot modes                                                     | 23 |

|   | 2.16 | Power supply schemes                                           | 23 |

|   | 2.17 | Power supply supervisor                                        | 24 |

|   |      | 2.17.1 Internal reset ON                                       | 24 |

|   |      | 2.17.2 Internal reset OFF                                      | 25 |

|   | 2.18 | Voltage regulator                                              | 26 |

|   |      | 2.18.1 Regulator ON                                            | 26 |

|   |      | 2.18.2 Regulator OFF                                           |    |

|   |      | 2.18.3 Regulator ON/OFF and internal reset ON/OFF availability |    |

|   | 2.19 | Real-time clock (RTC), backup SRAM and backup registers        |    |

|   | 2.20 | Low-power modes                                                | 31 |

|   | 2.21 | V <sub>BAT</sub> operation                                     |    |

|   | 2.22 | Timers and watchdogs                                           |    |

|   |      | 2.22.1 Advanced-control timers (TIM1, TIM8)                    | 34 |

# 2.3 Embedded Flash memory

The STM32F745xx and STM32F746xx devices embed a Flash memory of up to 1 Mbyte available for storing programs and data.

# 2.4 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify the data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a mean of verifying the Flash memory integrity. The CRC calculation unit helps to compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 2.5 Embedded SRAM

All the devices features:

- System SRAM up to 320 Kbytes:

- SRAM1 on AHB bus Matrix: 240 Kbytes

- SRAM2 on AHB bus Matrix: 16 Kbytes

- DTCM-RAM on TCM interface (Tighly Coupled Memory interface): 64 Kbytes for critical real-time data.

- Instruction RAM (ITCM-RAM) 16 Kbytes:

- It is mapped on TCM interface and reserved only for CPU Execution/Instruction useful for critical real-time routines.

The Data TCM RAM is accessible by the GP-DMAs and peripherals DMAs through specific AHB slave of the CPU. The TCM RAM instruction is reserved only for CPU. It is accessed at CPU clock speed with 0-wait states.

4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

# 2.6 AXI-AHB bus matrix

18/227

The STM32F745xx and STM32F746xx system architecture is based on 2 sub-systems:

- An AXI to multi AHB bridge converting AXI4 protocol to AHB-Lite protocol:

- 3x AXI to 32-bit AHB bridges connected to AHB bus matrix

- 1x AXI to 64-bit AHB bridge connected to the embedded flash

- A multi-AHB Bus-Matrix:

- The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS, LCD-TFT, and DMA2D) and the slaves (Flash memory, RAM, FMC, Quad-SPI, AHB and APB peripherals) and ensures a seamless and an efficient operation even when several high-speed peripherals work simultaneously.

DocID027590 Rev 4

# 2.15 Boot modes

At startup, the boot memory space is selected by the BOOT pin and BOOT\_ADDx option bytes, allowing to program any boot memory address from 0x0000 0000 to 0x3FFF FFFF which includes:

- All Flash address space mapped on ITCM or AXIM interface

- All RAM address space: ITCM, DTCM RAMs and SRAMs mapped on AXIM interface

- The System memory bootloader

The boot loader is located in system memory. It is used to reprogram the Flash memory through a serial interface.

# 2.16 Power supply schemes

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

- V<sub>DD</sub> = 1.7 to 3.6 Vexternal power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.7 to 3.6 V: external analog power supplies for ADC, DAC, reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

Note:

$V_{DD}/V_{DDA}$  minimum value of 1.7 V is obtained when the internal reset is OFF (refer to Section 2.17.2: Internal reset OFF). Refer to Table 3: Voltage regulator configuration mode versus device operating mode to identify the packages supporting this option.

- V<sub>DDUSB</sub> can be connected either to V<sub>DD</sub> or an external independent power supply (3.0 to 3.6V) for USB transceivers (refer to *Figure 4* and *Figure 5*). For example, when device is powered at 1.8V, an independent power supply 3.3V can be connected to V<sub>DDUSB</sub>. When the V<sub>DDUSB</sub> is connected to a separated power supply, it is independent from V<sub>DD</sub> or V<sub>DDA</sub> but it must be the last supply to be provided and the first to disappear. The following conditions V<sub>DDUSB</sub> must be respected:

- During power-on phase ( $V_{DD} < V_{DD\_MIN}$ ),  $V_{DDUSB}$  should be always lower than  $V_{DD}$

- During power-down phase ( $V_{DD} < V_{DD\_MIN}$ ),  $V_{DDUSB}$  should be always lower than  $V_{DD}$

- V<sub>DDSUB</sub> rising and falling time rate specifications must be respected (see *Table 20* and *Table 21*)

- In operating mode phase, V<sub>DDUSB</sub> could be lower or higher than V<sub>DD</sub>.

- If USB (USB OTG\_HS/OTG\_FS) is used, the associated GPIOs powered by  $V_{DDUSB}$  are operating between  $V_{DDUSB\ MIN}$  and  $V_{DDUSB\ MAX}.$

- The  $V_{DDUSB}$  supply both USB transceiver (USB OTG\_HS and USB OTG\_FS). If only one USB transceiver is used in the application, the GPIOs associated to the other USB transceiver are still supplied by  $V_{DDUSB}$ .

- If USB (USB OTG\_HS/OTG\_FS) is not used, the associated GPIOs powered by  $V_{DDUSB}$  are operating between  $V_{DD\_MIN}$  and  $V_{DD\_MAX}.$

#### 2.22.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

# 2.22.4 Low-power timer (LPTIM1)

The low-power timer has an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one-shot mode

- Selectable software / hardware input trigger

- Selectable clock source:

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

# 2.22.5 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

# 2.22.6 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

# 2.22.7 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

O PE2 132 □PI1 PE3 □ PE4 □ PE5 □ 131 □PI0 2 3 4 5 6 7 PH15 130 129 PE6 □ □PH13 VBAT | □V<sub>DD</sub>

□V<sub>SS</sub>

□V<sub>CAP\_2</sub>

□PA13

□PA12 127 126 PC13□ 8 9 124 10 123 □PA11 PI10 | PI11 | □PA10 □PA9 12 121 13 120 14 vss⊏ 119 □PA8 VDD □ PF0 □ PF1 □ 16 17 PF2□ PF3□ PF4□ 18 19 20 PF5 □ VSS □ VDD □ 21 LQFP176 22 23 PF6 ☐ 24 PF7 ☐ 25 26 27 PF8 □ PF9 PF10 28 PH0 29 PH1 ☐ NRST ☐ 30 31 PC0 🗆 32 PC1 □ PC2 □ PC3 □ 33 34 35 VDD | 36 VSSA 🗆 VREF+ 🗀 37 38 95 PB15 94 PB14 93 PB13 92 PB12 91 PD 90 V<sub>SS</sub> 89 PH12 VDDA 🗆 39 40 41 PA0 □ PA1 □ PA2□ PH2□ PH3□ 42 43 BYPASS MS31878V2

Figure 15. STM32F74xIx LQFP176 pinout

1. The above figure shows the package top view.

Table 10. STM32F745xx and STM32F746xx pin and ball definition (continued)

|         |          |          |         | umber    |         |         |          |                                                            |          | , , , , , , , , , , , , , , , , , , , |            | ball definition (continue                                                                                          |                                            |

|---------|----------|----------|---------|----------|---------|---------|----------|------------------------------------------------------------|----------|---------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| LQFP100 | TFBGA100 | WLCSP143 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | Pin<br>name<br>(function<br>after<br>reset) <sup>(1)</sup> | Pin type | I/O structure                         | Notes      | Alternate functions                                                                                                | Additional<br>functions                    |

| 4       | D3       | D9       | 4       | B2       | 4       | 4       | B1       | PE5                                                        | I/O      | FT                                    | -          | TRACED2, TIM9_CH1,<br>SPI4_MISO,<br>SAI1_SCK_A, FMC_A21,<br>DCMI_D6, LCD_G0,<br>EVENTOUT                           | -                                          |

| 5       | E3       | E8       | 5       | В3       | 5       | 5       | B2       | PE6                                                        | I/O      | FT                                    | -          | TRACED3, TIM1_BKIN2,<br>TIM9_CH2, SPI4_MOSI,<br>SAI1_SD_A,<br>SAI2_MCK_B, FMC_A22,<br>DCMI_D7, LCD_G1,<br>EVENTOUT | -                                          |

| -       | ı        | -        | 1       | -        | 1       | -       | G6       | VSS                                                        | S        | ı                                     | -          | -                                                                                                                  | -                                          |

| -       | -        | -        | 1       | _        | -       | -       | F5       | VDD                                                        | S        | -                                     | -          | -                                                                                                                  | -                                          |

| 6       | B2       | C11      | 6       | C1       | 6       | 6       | C1       | VBAT                                                       | S        | -                                     | -          | -                                                                                                                  | -                                          |

| -       | -        | 1        | -       | D2       | 7       | 7       | C2       | PI8                                                        | I/O      | FT                                    | (2)<br>(3) | EVENTOUT                                                                                                           | RTC_TAMP2/<br>RTC_TS,WK<br>UP5             |

| 7       | A2       | D10      | 7       | D1       | 8       | 8       | D1       | PC13                                                       | I/O      | FT                                    | (2)        | EVENTOUT                                                                                                           | RTC_TAMP1/<br>RTC_TS/RTC<br>_OUT,WKUP<br>4 |

| 8       | A1       | D11      | 8       | E1       | 9       | 9       | E1       | PC14-<br>OSC32_I<br>N(PC14)                                | I/O      | FT                                    | (2)<br>(3) | EVENTOUT                                                                                                           | OSC32_IN                                   |

| 9       | B1       | E11      | 9       | F1       | 10      | 10      | F1       | PC15-<br>OSC32_<br>OUT(PC<br>15)                           | I/O      | FT                                    | (2)        | EVENTOUT                                                                                                           | OSC32_OUT                                  |

| -       | -        | -        | -       | -        | -       | -       | G5       | VDD                                                        | S        | -                                     | -          | -                                                                                                                  | -                                          |

| -       | ı        | 1        | -       | D3       | 11      | 11      | E4       | PI9                                                        | I/O      | FT                                    | -          | CAN1_RX, FMC_D30,<br>LCD_VSYNC,<br>EVENTOUT                                                                        | -                                          |

| -       | -        | -        | -       | E3       | 12      | 12      | D5       | PI10                                                       | I/O      | FT                                    | -          | ETH_MII_RX_ER,<br>FMC_D31, LCD_HSYNC,<br>EVENTOUT                                                                  | -                                          |

Pin Number Pin /O structure name Pin type Notes FFBGA100 WLCSP143 UFBGA176 FFBGA216 Additional LQFP176 LQFP100 LQFP144 LQFP208 (function **Alternate functions functions** after reset)<sup>(1)</sup> TIM8\_CH2, SAI2\_SD\_A, I/O C3 175 207 D6 PI6 FT FMC\_D28, DCMI\_D6, LCD\_B6, EVENTOUT TIM8 CH3, SAI2 FS A, FT FMC\_D29, DCMI\_D7, C2 176 208 D4 PI7 I/O LCD\_B7, EVENTOUT

Table 10. STM32F745xx and STM32F746xx pin and ball definition (continued)

- 1. Function availability depends on the chosen device.

- 2. PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited:

- The speed should not exceed 2 MHz with a maximum load of 30 pF.

- These I/Os must not be used as a current source (e.g. to drive an LED).

- Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F75xxx and STM32F74xxx reference manual.

- 4. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

- If the device is delivered in an WLCSP143, UFBGA176, LQFP176, TFBGA100 or TFBGA216 package, and the BYPASS\_REG pin is set to VDD (Regulator OFF/internal reset ON mode), then PA0 is used as an internal Reset (active low).

57

Table 11. FMC pin definition (continued)

| ver restance   ver restance |                    |                  |        |       |  |  |  |  |  |

|-----------------------------|--------------------|------------------|--------|-------|--|--|--|--|--|

| Pin name                    | NOR/PSRAM/SR<br>AM | NOR/PSRAM<br>Mux | NAND16 | SDRAM |  |  |  |  |  |

| PE11                        | D8                 | DA8              | D8     | D8    |  |  |  |  |  |

| PE12                        | D9                 | DA9              | D9     | D9    |  |  |  |  |  |

| PE13                        | D10                | DA10             | D10    | D10   |  |  |  |  |  |

| PE14                        | D11                | DA11             | D11    | D11   |  |  |  |  |  |

| PE15                        | D12                | DA12             | D12    | D12   |  |  |  |  |  |

| PD8                         | D13                | DA13             | D13    | D13   |  |  |  |  |  |

| PD9                         | D14                | DA14             | D14    | D14   |  |  |  |  |  |

| PD10                        | D15                | DA15             | D15    | D15   |  |  |  |  |  |

| PH8                         | D16                | -                | -      | D16   |  |  |  |  |  |

| PH9                         | D17                | -                | -      | D17   |  |  |  |  |  |

| PH10                        | D18                | -                | -      | D18   |  |  |  |  |  |

| PH11                        | D19                | -                | -      | D19   |  |  |  |  |  |

| PH12                        | D20                | -                | -      | D20   |  |  |  |  |  |

| PH13                        | D21                | -                | -      | D21   |  |  |  |  |  |

| PH14                        | D22                | -                | -      | D22   |  |  |  |  |  |

| PH15                        | D23                | -                | -      | D23   |  |  |  |  |  |

| PI0                         | D24                | -                | -      | D24   |  |  |  |  |  |

| PI1                         | D25                | -                | -      | D25   |  |  |  |  |  |

| PI2                         | D26                | -                | -      | D26   |  |  |  |  |  |

| PI3                         | D27                | -                | -      | D27   |  |  |  |  |  |

| PI6                         | D28                | -                | -      | D28   |  |  |  |  |  |

| PI7                         | D29                | -                | -      | D29   |  |  |  |  |  |

| PI9                         | D30                | -                | -      | D30   |  |  |  |  |  |

| PI10                        | D31                | -                | -      | D31   |  |  |  |  |  |

| PD7                         | NE1                | NE1              | -      | -     |  |  |  |  |  |

| PG9                         | NE2                | NE2              | NCE    | -     |  |  |  |  |  |

| PG10                        | NE3                | NE3              | -      | -     |  |  |  |  |  |

| PG11                        | -                  | -                | -      | -     |  |  |  |  |  |

| PG12                        | NE4                | NE4              | -      | -     |  |  |  |  |  |

| PD3                         | CLK                | CLK              | -      | -     |  |  |  |  |  |

| PD4                         | NOE                | NOE              | NOE    | -     |  |  |  |  |  |

| PD5                         | NWE                | NWE              | NWE    | -     |  |  |  |  |  |

| PD6                         | NWAIT              | NWAIT            | NWAIT  | -     |  |  |  |  |  |

| PB7                         | NADV               | NADV             | -      | -     |  |  |  |  |  |

Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

|        |      | AF0 | AF1    | AF2          | AF3                             | AF4                | AF5                       | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11            | AF12                       | AF13           | AF14   | AF15         |

|--------|------|-----|--------|--------------|---------------------------------|--------------------|---------------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|-----------------|----------------------------|----------------|--------|--------------|

| Po     | ort  | sys | TIM1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6        | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI           | LCD    | sys          |

|        | PH8  | -   | -      | -            | -                               | I2C3_SD<br>A       | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D1                     | DCMI_H<br>SYNC | LCD_R2 | EVEN<br>TOUT |

|        | PH9  | -   | -      | -            | -                               | I2C3_SM<br>BA      | -                         | -             | -                                           | -                                               | TIM12_C<br>H2                              | -                                        | -               | FMC_D1                     | DCMI_D<br>0    | LCD_R3 | EVEN<br>TOUT |

|        | PH10 | ı   | -      | TIM5_C<br>H1 | -                               | I2C4_SM<br>BA      | -                         | -             | -                                           | -                                               | -                                          | ı                                        | ı               | FMC_D1                     | DCMI_D<br>1    | LCD_R4 | EVEN<br>TOUT |

| Port H | PH11 | -   | -      | TIM5_C<br>H2 | -                               | I2C4_SC<br>L       | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D1                     | DCMI_D<br>2    | LCD_R5 | EVEN<br>TOUT |

| POILE  | PH12 | -   | -      | TIM5_C<br>H3 | -                               | I2C4_SD<br>A       | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2                     | DCMI_D<br>3    | LCD_R6 | EVEN<br>TOUT |

|        | PH13 | -   | -      | -            | TIM8_CH<br>1N                   | -                  | -                         | -             | -                                           | -                                               | CAN1_T<br>X                                | -                                        | -               | FMC_D2                     | -              | LCD_G2 | EVEN<br>TOUT |

|        | PH14 | -   | -      | -            | TIM8_CH<br>2N                   | -                  | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2                     | DCMI_D<br>4    | LCD_G3 | EVEN<br>TOUT |

|        | PH15 | -   | -      | -            | TIM8_CH<br>3N                   | -                  | -                         | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2                     | DCMI_D<br>11   | LCD_G4 | EVEN<br>TOUT |

|        | PI0  | -   | -      | TIM5_C<br>H4 | -                               | -                  | SPI2_NS<br>S/I2S2_<br>WS  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2                     | DCMI_D<br>13   | LCD_G5 | EVEN<br>TOUT |

|        | PI1  | -   | -      | -            | TIM8_BKI<br>N2                  | -                  | SPI2_SC<br>K/I2S2_<br>CK  | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2<br>5                | DCMI_D<br>8    | LCD_G6 | EVEN<br>TOUT |

|        | PI2  | -   | -      | -            | TIM8_CH<br>4                    | -                  | SPI2_MI<br>SO             | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2                     | DCMI_D<br>9    | LCD_G7 | EVEN<br>TOUT |

| Port I | PI3  | -   | -      | -            | TIM8_ET<br>R                    | -                  | SPI2_M<br>OSI/I2S2<br>_SD | -             | -                                           | -                                               | -                                          | -                                        | -               | FMC_D2                     | DCMI_D<br>10   | -      | EVEN<br>TOUT |

|        | PI4  | -   | -      | -            | TIM8_BKI<br>N                   | -                  | -                         | -             | -                                           | -                                               | -                                          | SAI2_MC<br>K_A                           | -               | FMC_NB<br>L2               | DCMI_D<br>5    | LCD_B4 | EVEN<br>TOUT |

|        | PI5  | -   | -      | -            | TIM8_CH<br>1                    | -                  | -                         | -             | -                                           | -                                               | -                                          | SAI2_SC<br>K_A                           | -               | FMC_NB<br>L3               | DCMI_V<br>SYNC | LCD_B5 | EVEN<br>TOUT |

|        | PI6  | -   | -      | -            | TIM8_CH<br>2                    | -                  | -                         | -             | -                                           | -                                               | -                                          | SAI2_SD_<br>A                            | -               | FMC_D2<br>8                | DCMI_D<br>6    | LCD_B6 | EVEN<br>TOUT |

Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

|        |      |     |        |          | 2. 3 I WI32                     |                    |                    |               |                                             |                                                 |                                            |                                          | (               | /                          |      |        |              |

|--------|------|-----|--------|----------|---------------------------------|--------------------|--------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|-----------------|----------------------------|------|--------|--------------|

|        |      | AF0 | AF1    | AF2      | AF3                             | AF4                | AF5                | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11            | AF12                       | AF13 | AF14   | AF15         |

| Po     | ort  | sys | TIM1/2 | TIM3/4/5 | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI | LCD    | sys          |

|        | PJ7  | -   | -      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_G0 | EVEN<br>TOUT |

|        | PJ8  | -   | -      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_G1 | EVEN<br>TOUT |

|        | PJ9  | -   | -      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_G2 | EVEN<br>TOUT |

|        | PJ10 | -   | ı      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | 1                                          | -                                        | -               | -                          | -    | LCD_G3 | EVEN<br>TOUT |

| Port J | PJ11 | -   | -      | -        | -                               | -                  | -                  | i             | -                                           | -                                               | ı                                          | -                                        | -               | -                          | -    | LCD_G4 | EVEN<br>TOUT |

|        | PJ12 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B0 | EVEN<br>TOUT |

|        | PJ13 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B1 | EVEN<br>TOUT |

|        | PJ14 | -   | -      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B2 | EVEN<br>TOUT |

|        | PJ15 | -   | -      | -        | -                               | -                  | -                  | ı             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B3 | EVEN<br>TOUT |

Pinouts and pin description

Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

|        |     |     |        |          | 2. O I WIJZ                     |                    |                    |               |                                             |                                                 |                                            | p                                        | (               | /                          |      |        |              |

|--------|-----|-----|--------|----------|---------------------------------|--------------------|--------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|-----------------|----------------------------|------|--------|--------------|

|        |     | AF0 | AF1    | AF2      | AF3                             | AF4                | AF5                | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11            | AF12                       | AF13 | AF14   | AF15         |

| Po     | ort | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI | LCD    | sys          |

|        | PK0 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_G5 | EVEN<br>TOUT |

|        | PK1 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_G6 | EVEN<br>TOUT |

|        | PK2 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_G7 | EVEN<br>TOUT |

| Port K | PK3 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B4 | EVEN<br>TOUT |

| POILK  | PK4 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B5 | EVEN<br>TOUT |

|        | PK5 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B6 | EVEN<br>TOUT |

|        | PK6 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_B7 | EVEN<br>TOUT |

|        | PK7 | -   | -      | -        | -                               | -                  | -                  | 1             | -                                           | -                                               | -                                          | -                                        | -               | -                          | -    | LCD_DE | EVEN<br>TOUT |

# 5 Electrical characteristics

### 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A$ max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean±3 $\sigma$ ).

## 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A$  = 25 °C,  $V_{DD}$  = 3.3 V (for the 1.7 V  $\leq$ V<sub>DD</sub>  $\leq$ 3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean±2σ).

# 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

# 5.1.4 Loading capacitor

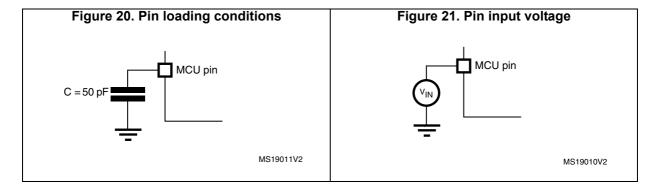

The loading conditions used for pin parameter measurement are shown in Figure 20.

## 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 21*.

577

Table 19. VCAP1/VCAP2 operating conditions<sup>(1)</sup>

| Symbol | Parameter                         | Conditions |

|--------|-----------------------------------|------------|

| CEXT   | Capacitance of external capacitor | 2.2 μF     |

| ESR    | ESR of external capacitor         | < 2 Ω      |

<sup>1.</sup> When bypassing the voltage regulator, the two 2.2  $\mu$ F V<sub>CAP</sub> capacitors are not required and should be replaced by two 100 nF decoupling capacitors.

# 5.3.3 Operating conditions at power-up / power-down (regulator ON)

Subject to general operating conditions for T<sub>A</sub>.

Table 20. Operating conditions at power-up / power-down (regulator ON)

| Symbol           | Parameter                      | Min | Max | Unit  |

|------------------|--------------------------------|-----|-----|-------|

| +                | V <sub>DD</sub> rise time rate | 20  | 8   | µs/V  |

| t <sub>VDD</sub> | V <sub>DD</sub> fall time rate | 20  | 8   | μ5/ ν |

# 5.3.4 Operating conditions at power-up / power-down (regulator OFF)

Subject to general operating conditions for T<sub>A</sub>.

Table 21. Operating conditions at power-up / power-down (regulator OFF)<sup>(1)</sup>

| Symbol            | Parameter                                                | Conditions | Min | Max | Unit  |

|-------------------|----------------------------------------------------------|------------|-----|-----|-------|

| t                 | V <sub>DD</sub> rise time rate                           | Power-up   | 20  | ∞   |       |

| t <sub>VDD</sub>  | V <sub>DD</sub> fall time rate                           | Power-down | 20  | ∞   | μs/V  |

| +                 | V <sub>CAP_1</sub> and V <sub>CAP_2</sub> rise time rate | Power-up   | 20  | ∞   | μ5/ ν |

| t <sub>VCAP</sub> | V <sub>CAP_1</sub> and V <sub>CAP_2</sub> fall time rate | Power-down | 20  | 8   |       |

To reset the internal logic at power-down, a reset must be applied on pin PA0 when V<sub>DD</sub> reach below 1.08 V

# 5.3.5 Reset and power control block characteristics

The parameters given in *Table 22* are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 17*.

| Symbol                                  | Parameter                                    | Conditions                                                     |                    | Min          | Тур  | Max          | Unit |

|-----------------------------------------|----------------------------------------------|----------------------------------------------------------------|--------------------|--------------|------|--------------|------|

|                                         |                                              | Cycle to cycle at                                              | RMS                | -            | 90   | -            |      |

|                                         | Master SAI clock jitter                      | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                   | peak<br>to<br>peak | 1            | ±280 | ı            | ps   |

| Jitter <sup>(3)</sup>                   | madel of a diook just                        | Average frequency of 12.288 MHz N = 432, R = 5 on 1000 samples | -                  | 90           | -    | ps           |      |

|                                         | FS clock jitter                              | Cycle to cycle at 48 h<br>on 1000 samples                      | КНz                | -            | 400  | -            | ps   |

| I <sub>DD(PLLSAI)</sub> <sup>(4)</sup>  | PLLSAI power consumption on $V_{\rm DD}$     | VCO freq = 100 MHz<br>VCO freq = 432 MHz                       |                    | 0.15<br>0.45 | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLSAI)</sub> <sup>(4)</sup> | PLLSAI power consumption on V <sub>DDA</sub> | VCO freq = 100 MHz<br>VCO freq = 432 MHz                       |                    | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA   |

Table 45. PLLISAI characteristics (continued)

# 5.3.12 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 52: EMI characteristics*). It is available only on the main PLL.

Table 46. SSCG parameters constraint

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup>  | Unit |

|-------------------|-----------------------|------|-----|---------------------|------|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                  | KHz  |

| md                | Peak modulation depth | 0.25 | -   | 2                   | %    |

| MODEPER * INCSTEP | -                     | -    | -   | 2 <sup>15</sup> - 1 | -    |

Guaranteed by design.

#### Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

MODEPER = round[

$$f_{PLL \ IN} / \ (4 \times f_{Mod})$$

]

$f_{PLL\ IN}$  and  $f_{Mod}$  must be expressed in Hz.

As an example:

If  $f_{PLL\_IN}$  = 1 MHz, and  $f_{MOD}$  = 1 kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round[

$$10^6 / (4 \times 10^3)$$

] = 250

<sup>1.</sup> Take care of using the appropriate division factor M to have the specified PLL input clock values.

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> Value given with main PLL running.

<sup>4.</sup> Guaranteed by characterization results.

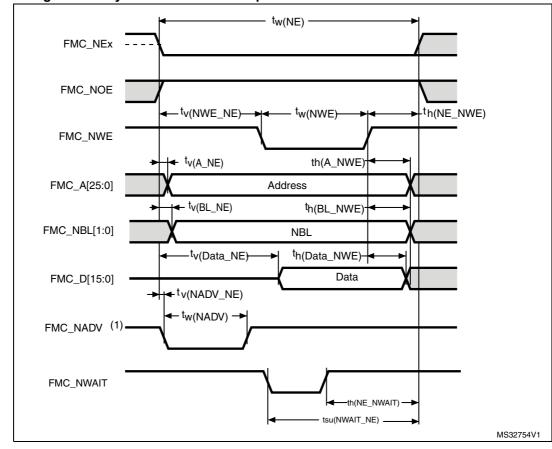

Figure 59. Asynchronous non-multiplexed SRAM/PSRAM/NOR write waveforms

1. Mode 2/B, C and D only. In Mode 1, FMC\_NADV is not used.

Table 90. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings<sup>(1)</sup>

| Symbol                   | Parameter                             | Min                     | Max                     | Unit |

|--------------------------|---------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>       | FMC_NE low time                       | 3T <sub>HCLK</sub> -0.5 | 3T <sub>HCLK</sub> +1.5 |      |

| t <sub>v(NWE_NE)</sub>   | FMC_NEx low to FMC_NWE low            | T <sub>HCLK</sub> -0.5  | T <sub>HCLK</sub> + 1   |      |

| t <sub>w(NWE)</sub>      | FMC_NWE low time                      | T <sub>HCLK</sub> -0.5  | T <sub>HCLK</sub> + 1   |      |

| t <sub>h(NE_NWE)</sub>   | FMC_NWE high to FMC_NE high hold time | T <sub>HCLK</sub> -0.5  | -                       |      |

| t <sub>v(A_NE)</sub>     | FMC_NEx low to FMC_A valid            | -                       | 0                       |      |

| t <sub>h(A_NWE)</sub>    | Address hold time after FMC_NWE high  | T <sub>HCLK</sub> -0.5  | -                       | ns   |

| t <sub>v(BL_NE)</sub>    | FMC_NEx low to FMC_BL valid           | -                       | 0                       | 113  |

| t <sub>h(BL_NWE)</sub>   | FMC_BL hold time after FMC_NWE high   | T <sub>HCLK</sub> -0.5  | -                       |      |

| t <sub>v(Data_NE)</sub>  | Data to FMC_NEx low to Data valid     | -                       | T <sub>HCLK</sub> + 3   |      |

| t <sub>h(Data_NWE)</sub> | Data hold time after FMC_NWE high     | T <sub>HCLK</sub> +0.5  | -                       |      |

| t <sub>v(NADV_NE)</sub>  | FMC_NEx low to FMC_NADV low           | -                       | 0                       |      |

| t <sub>w(NADV)</sub>     | FMC_NADV low time                     | -                       | T <sub>HCLK</sub> + 0.5 |      |

1. Guaranteed by characterization results.

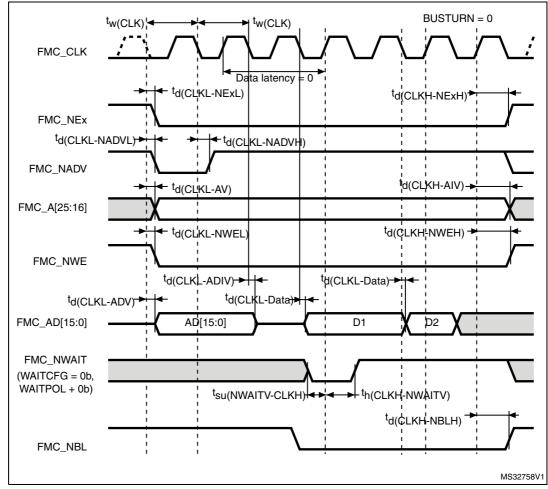

Table 96. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)</sup>

| Symbol                      | Parameter                                    | Min                     | Max | Unit |

|-----------------------------|----------------------------------------------|-------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                               | 2T <sub>HCLK</sub> -0.5 | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)            | -                       | 2   |      |

| t <sub>d(CLKH_NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)         | T <sub>HCLK</sub> +0.5  | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                  | -                       | 1.5 |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high                 | 0                       | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)         | -                       | 2   |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)      | T <sub>HCLK</sub>       | -   |      |

| t <sub>d(CLKL-NOEL)</sub>   | FMC_CLK low to FMC_NOE low                   | -                       | 2   | ns   |

| t <sub>d(CLKH-NOEH)</sub>   | FMC_CLK high to FMC_NOE high                 | T <sub>HCLK</sub> -0.5  | -   |      |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid            | -                       | 3   |      |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid          | 0                       | -   |      |

| t <sub>su(ADV-CLKH)</sub>   | FMC_A/D[15:0] valid data before FMC_CLK high | 1.5                     | -   |      |

| t <sub>h(CLKH-ADV)</sub>    | FMC_A/D[15:0] valid data after FMC_CLK high  | 1                       | -   | 1    |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high          | 2                       | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high           | 3.5                     | -   |      |

<sup>1.</sup> Guaranteed by characterization results.

Figure 63. Synchronous multiplexed PSRAM write timings

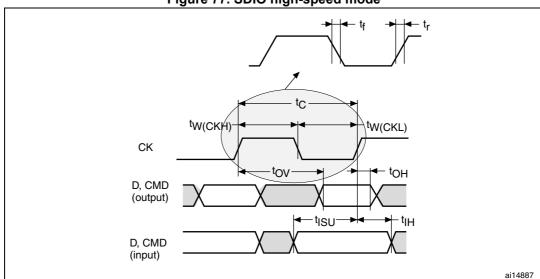

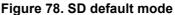

# 5.3.31 SD/SDIO MMC card host interface (SDMMC) characteristics

Unless otherwise specified, the parameters given in *Table 110* for the SDIO/MMC interface are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 5.3.17: I/O port characteristics for more details on the input/output characteristics.

Figure 77. SDIO high-speed mode

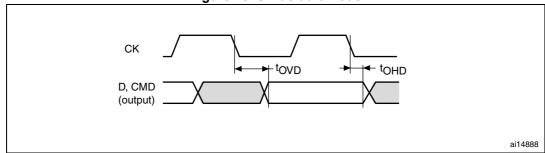

# 6.3 WLCSP143, 4.539x 5.849 mm, 0.4 mm pitch wafer level chip scale package information

Figure 85. WLCSP143, 4.539x 5.849 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

Table 115. WLCSP143, 4.539x 5.849 mm, 0.4 mm pitch wafer level chip scale package mechanical data

| Symbol | millimeters |       |       | ers inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|---------------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                       | Тур    | Max    |

| А      | 0.525       | 0.555 | 0.585 | 0.0207                    | 0.0219 | 0.0230 |

| A1     | -           | 0.175 | -     | -                         | 0.0069 | -      |

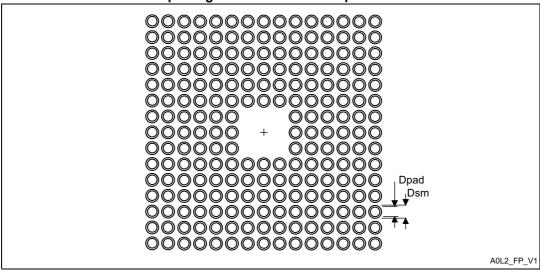

Table 122. TFBGA216, 13 × 13 × 0.8 mm thin fine-pitch ball grid array package mechanical data (continued)

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol | Min         | Тур   | Max   | Min                   | Тур    | Max    |

| G      | -           | 0.900 | -     | -                     | 0.0354 | -      |

| ddd    | -           | -     | 0.100 | -                     | -      | 0.0039 |

| eee    | -           | -     | 0.150 | -                     | -      | 0.0059 |

| fff    | -           | -     | 0.080 | -                     | -      | 0.0031 |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

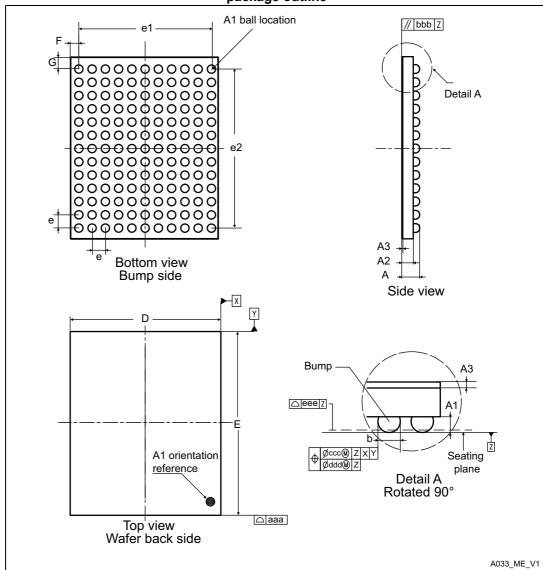

Figure 101. TFBGA216, 13 x 13 x 0.8 mm thin fine-pitch ball grid array package recommended footprint

Table 123. TFBGA216 recommended PCB design rules (0.8 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.8                                                              |

| Dpad              | 0.400 mm                                                         |

| Dsm               | 0.470 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.400 mm                                                         |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |

| Pad trace width   | 0.120 mm                                                         |