#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                                 |

|----------------------------|--------------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 114                                                                                                    |

| Program Memory Size        | 1MB (1M × 8)                                                                                           |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320K x 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                                     |

| Mounting Type              | Surface Mount                                                                                          |

| Package / Case             | 144-LQFP                                                                                               |

| Supplier Device Package    | 144-LQFP (20x20)                                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f746zgt7                                  |

|                            |                                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

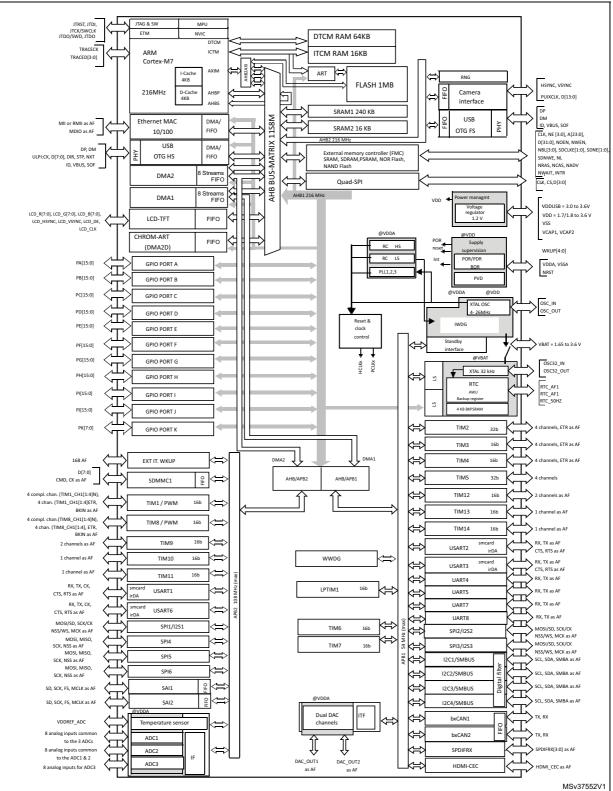

# 1 Description

The STM32F745xx and STM32F746xx devices are based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M7 32-bit RISC core operating at up to 216 MHz frequency. The Cortex<sup>®</sup>-M7 core features a single floating point unit (SFPU) precision which supports all ARM<sup>®</sup> single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances the application security.

The STM32F745xx and STM32F746xx devices incorporate high-speed embedded memories with a Flash memory up to 1 Mbyte, 320 Kbytes of SRAM (including 64 Kbytes of Data TCM RAM for critical real-time data), 16 Kbytes of instruction TCM RAM (for critical real-time routines), 4 Kbytes of backup SRAM available in the lowest power modes, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, two AHB buses, a 32-bit multi-AHB bus matrix and a multi layer AXI interconnect supporting internal and external memories access.

All the devices offer three 12-bit ADCs, two DACs, a low-power RTC, thirteen generalpurpose 16-bit timers including two PWM timers for motor control and one low-power timer available in Stop mode, two general-purpose 32-bit timers, a true random number generator (RNG). They also feature standard and advanced communication interfaces.

- Up to four I<sup>2</sup>Cs

- Six SPIs, three I<sup>2</sup>Ss in duplex mode. To achieve the audio class accuracy, the I<sup>2</sup>S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Four USARTs plus four UARTs

- An USB OTG full-speed and a USB OTG high-speed with full-speed capability (with the ULPI),

- Two CANs

- Two SAI serial audio interfaces

- An SDMMC host interface

- Ethernet and camera interfaces

- LCD-TFT display controller

- Chrom-ART Accelerator™

- SPDIFRX interface

- HDMI-CEC

Advanced peripherals include an SDMMC interface, a flexible memory control (FMC) interface, a Quad-SPI Flash memory interface, a camera interface for CMOS sensors. Refer to *Table 2: STM32F745xx and STM32F746xx features and peripheral counts* for the list of peripherals available on each part number.

The STM32F745xx and STM32F746xx devices operate in the –40 to +105 °C temperature range from a 1.7 to 3.6 V power supply. A dedicated supply input for USB (OTG\_FS and OTG\_HS) is available on all the packages except LQFP100 for a greater power supply choice.

The supply voltage can drop to 1.7 V with the use of an external power supply supervisor (refer to *Section 2.17.2: Internal reset OFF*). A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F745xx and STM32F746xx devices offer devices in 8 packages ranging from 100 pins to 216 pins. The set of included peripherals changes with the device chosen.

Figure 2. STM32F745xx and STM32F746xx block diagram

1. The timers connected to APB2 are clocked from TIMxCLK up to 216 MHz, while the timers connected to APB1 are clocked from TIMxCLK either up to 108 MHz or 216 MHz depending on TIMPRE bit configuration in the RCC\_DCKCFGR register.

## 2.22.1 Advanced-control timers (TIM1, TIM8)

The advanced-control timers (TIM1, TIM8) can be seen as three-phase PWM generators multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead times. They can also be considered as complete general-purpose timers. Their 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge- or center-aligned modes)

- One-pulse mode output

If configured as standard 16-bit timers, they have the same features as the general-purpose TIMx timers. If configured as 16-bit PWM generators, they have full modulation capability (0-100%).

The advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

TIM1 and TIM8 support independent DMA request generation.

#### 2.22.2 General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F74xxx devices (see *Table 6* for differences).

#### • TIM2, TIM3, TIM4, TIM5

The STM32F74xxx include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### • TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

| features <sup>(1)</sup>               | USART1/2/3/6 | UART4/5/7/8 |

|---------------------------------------|--------------|-------------|

| Smartcard mode                        | Х            | -           |

| Single-wire half-duplex communication | Х            | Х           |

| IrDA SIR ENDEC block                  | Х            | Х           |

| LIN mode                              | Х            | Х           |

| Dual clock domain                     | Х            | Х           |

| Receiver timeout interrupt            | Х            | Х           |

| Modbus communication                  | Х            | Х           |

| Auto baud rate detection              | Х            | Х           |

| Driver Enable                         | Х            | х           |

Table 8. USART implementation (continued)

1. X: supported.

# 2.25 Serial peripheral interface (SPI)/inter- integrated sound interfaces (I2S)

The devices feature up to six SPIs in slave and master modes in full-duplex and simplex communication modes. SPI1, SPI4, SPI5, and SPI6 can communicate at up to 50 Mbits/s, SPI2 and SPI3 can communicate at up to 25 Mbit/s. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable from 4 to 16 bits. The SPI interfaces support NSS pulse mode, TI mode and Hardware CRC calculation. All SPIs can be served by the DMA controller.

Three standard  $I^2S$  interfaces (multiplexed with SPI1, SPI2 and SPI3) are available. They can be operated in master or slave mode, in simplex communication modes, and can be configured to operate with a 16-/32-bit resolution as an input or output channel. Audio sampling frequencies from 8 kHz up to 192 kHz are supported. When either or both of the  $I^2S$  interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency.

All I2Sx can be served by the DMA controller.

# 2.26 Serial audio interface (SAI)

The devices embed two serial audio interfaces.

The serial audio interface is based on two independent audio subblocks which can operate as transmitter or receiver with their FIFO. Many audio protocols are supported by each block: I2S standards, LSB or MSB-justified, PCM/DSP, TDM, AC'97 and SPDIF output, supporting audio sampling frequencies from 8 kHz up to 192 kHz. Both subblocks can be

configured in master or in slave mode.

In master mode, the master clock can be output to the external DAC/CODEC at 256 times of the sampling frequency.

The two sub-blocks can be configured in synchronous mode when full-duplex mode is required.

DocID027590 Rev 4

5

DocID027590 Rev 4

77/227

|        |      |                       |                           | Table 12     | 2. STM32                        | F/45XX             | and SI                    | VI32F/4                   | bxx alte                                    | rnate fui                                       | nction in                                  | apping                                   | (continu         | ea)                        |                |        |              |

|--------|------|-----------------------|---------------------------|--------------|---------------------------------|--------------------|---------------------------|---------------------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|------------------|----------------------------|----------------|--------|--------------|

|        |      | AF0                   | AF1                       | AF2          | AF3                             | AF4                | AF5                       | AF6                       | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11             | AF12                       | AF13           | AF14   | AF15         |

| Po     | ort  | SYS                   | TIM1/2                    | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6        | SPI3/<br>SAI1             | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS  | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI           | LCD    | SYS          |

|        | PA12 | -                     | TIM1_ET<br>R              | -            | -                               | -                  | -                         | -                         | USART1<br>_RTS                              | SAI2_FS<br>_B                                   | CAN1_T<br>X                                | OTG_FS_<br>DP                            | -                | -                          | -              | LCD_R5 | EVEN<br>TOUT |

|        | PA13 | JTMS-<br>SWDIO        | -                         | -            | -                               | -                  | -                         | -                         | -                                           | -                                               | -                                          | -                                        | -                | -                          | -              | -      | EVEN<br>TOUT |

| Port A | PA14 | JTCK-<br>SWCLK        | -                         | -            | -                               | -                  | -                         | -                         | -                                           | -                                               | -                                          | -                                        | -                | -                          | -              | -      | EVEN<br>TOUT |

|        | PA15 | JTDI                  | TIM2_C<br>H1/TIM2<br>_ETR | -            | -                               | HDMI-<br>CEC       | SPI1_NS<br>S/I2S1_<br>WS  | SPI3_NS<br>S/I2S3_<br>WS  | -                                           | UART4_<br>RTS                                   | -                                          | -                                        | -                | -                          | -              | -      | EVEN<br>TOUT |

|        | PB0  | -                     | TIM1_C<br>H2N             | TIM3_C<br>H3 | TIM8_CH<br>2N                   | -                  | -                         | -                         | -                                           | UART4_<br>CTS                                   | LCD_R3                                     | OTG_HS_<br>ULPI_D1                       | ETH_MII_<br>RXD2 | -                          | -              | -      | EVEN<br>TOUT |

|        | PB1  | -                     | TIM1_C<br>H3N             | TIM3_C<br>H4 | TIM8_CH<br>3N                   | -                  | -                         | -                         | -                                           | -                                               | LCD_R6                                     | OTG_HS_<br>ULPI_D2                       | ETH_MII_<br>RXD3 | -                          | -              | -      | EVEN<br>TOUT |

|        | PB2  | -                     | -                         | -            | -                               | -                  | -                         | SAI1_SD<br>_A             | SPI3_MO<br>SI/I2S3_<br>SD                   |                                                 | QUADSP<br>I_CLK                            | -                                        | -                | -                          | -              | -      | EVEN<br>TOUT |

|        | PB3  | JTDO/T<br>RACES<br>WO | TIM2_C<br>H2              | -            | -                               | -                  | SPI1_SC<br>K/I2S1_<br>CK  | SPI3_SC<br>K/I2S3_<br>CK  | -                                           | -                                               | -                                          | -                                        | -                | -                          | -              | -      | EVEN<br>TOUT |

| Port B | PB4  | NJTRST                | -                         | TIM3_C<br>H1 | -                               | -                  | SPI1_MI<br>SO             | SPI3_MI<br>SO             | SPI2_NS<br>S/I2S2_<br>WS                    | -                                               | -                                          | -                                        | -                | -                          | -              | -      | EVEN<br>TOUT |

|        | PB5  | -                     | -                         | TIM3_C<br>H2 | -                               | I2C1_SM<br>BA      | SPI1_M<br>OSI/I2S1<br>_SD | SPI3_M<br>OSI/I2S3<br>_SD | -                                           | -                                               | CAN2_R<br>X                                | OTG_HS_<br>ULPI_D7                       | ETH_PPS<br>_OUT  | FMC_SD<br>CKE1             | DCMI_D<br>10   | -      | EVEN<br>TOUT |

|        | PB6  | -                     | -                         | TIM4_C<br>H1 | HDMI-<br>CEC                    | I2C1_SC<br>L       | -                         | -                         | USART1<br>_TX                               | -                                               | CAN2_T<br>X                                | QUADSPI<br>_BK1_NC<br>                   | -                | FMC_SD<br>NE1              | DCMI_D<br>5    | -      | EVEN<br>TOUT |

|        | PB7  | -                     | -                         | TIM4_C<br>H2 | -                               | I2C1_SD<br>A       | -                         | -                         | USART1<br>_RX                               | -                                               | -                                          | -                                        | -                | FMC_NL                     | DCMI_V<br>SYNC | -      | EVEN<br>TOUT |

|        | PB8  | -                     | -                         | TIM4_C<br>H3 | TIM10_C<br>H1                   | I2C1_SC<br>L       | -                         | -                         | -                                           | -                                               | CAN1_R<br>X                                |                                          | ETH_MII_<br>TXD3 | SDMMC<br>1_D4              | DCMI_D<br>6    | LCD_B6 | EVEN<br>TOUT |

Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

80/227

DocID027590 Rev 4

|        |      |             |        | Table 12     | 2. STM32                        | F/45XX             | and ST                    | VI32F/4       | oxx alle                                    | nate iui                                        | iction n                                   | apping                                   | (continu        | ea)                        |              |        |              |

|--------|------|-------------|--------|--------------|---------------------------------|--------------------|---------------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|-----------------|----------------------------|--------------|--------|--------------|

|        |      | AF0         | AF1    | AF2          | AF3                             | AF4                | AF5                       | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11            | AF12                       | AF13         | AF14   | AF15         |

| P      | ort  | SYS         | TIM1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6        | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI         | LCD    | SYS          |

|        | PD0  | -           | -      | -            | -                               | -                  | -                         | -             | -                                           | -                                               | CAN1_R<br>X                                | -                                        | -               | FMC_D2                     | -            | -      | EVEN<br>TOUT |

|        | PD1  | -           | -      | -            | -                               | -                  | -                         | -             | -                                           | -                                               | CAN1_T<br>X                                | -                                        | -               | FMC_D3                     | -            | -      | EVEN<br>TOUT |

|        | PD2  | TRACE<br>D2 | -      | TIM3_ET<br>R | -                               | -                  | -                         | -             | -                                           | UART5_<br>RX                                    | -                                          | -                                        | -               | SDMMC<br>1_CMD             | DCMI_D<br>11 | -      | EVEN<br>TOUT |

|        | PD3  | -           | -      | -            | -                               | -                  | SPI2_SC<br>K/I2S2_<br>CK  | -             | USART2<br>_CTS                              | -                                               | -                                          | -                                        | -               | FMC_CL<br>K                | DCMI_D<br>5  | LCD_G7 | EVEN<br>TOUT |

|        | PD4  | -           | -      | -            | -                               | -                  | -                         | -             | USART2<br>_RTS                              | -                                               | -                                          | -                                        | -               | FMC_N<br>OE                | -            | -      | EVEN<br>TOUT |

|        | PD5  | -           | -      | -            | -                               | -                  | -                         | -             | USART2<br>_TX                               | -                                               | -                                          | -                                        | -               | FMC_N<br>WE                | -            | -      | EVEN<br>TOUT |

|        | PD6  | -           | -      | -            | -                               | -                  | SPI3_M<br>OSI/I2S3<br>_SD | SAI1_SD<br>_A | USART2<br>_RX                               | -                                               | -                                          | -                                        | -               | FMC_N<br>WAIT              | DCMI_D<br>10 | LCD_B2 | EVEN<br>TOUT |

| Port D | PD7  | -           | -      | -            | -                               | -                  | -                         | -             | USART2<br>_CK                               | SPDIFRX<br>_IN0                                 | -                                          | -                                        | -               | FMC_NE<br>1                | -            | -      | EVEN<br>TOUT |

|        | PD8  | -           | -      | -            | -                               | -                  | -                         | -             | USART3<br>_TX                               | SPDIFRX<br>_IN1                                 | -                                          | -                                        | -               | FMC_D1<br>3                | -            | -      | EVEN<br>TOUT |

|        | PD9  | -           | -      | -            | -                               | -                  | -                         | -             | USART3<br>_RX                               | -                                               | -                                          | -                                        | -               | FMC_D1<br>4                | -            | -      | EVEN<br>TOUT |

|        | PD10 | -           | -      | -            | -                               | -                  | -                         | -             | USART3<br>_CK                               | -                                               | -                                          | -                                        | -               | FMC_D1<br>5                | -            | LCD_B3 | EVEN<br>TOUT |

|        | PD11 | -           | -      | -            | -                               | I2C4_SM<br>BA      | -                         | -             | USART3<br>_CTS                              | -                                               | QUADSP<br>I_BK1_IO<br>0                    | SAI2_SD_<br>A                            | -               | FMC_A1<br>6/FMC_<br>CLE    | -            | -      | EVEN<br>TOUT |

|        | PD12 | -           | -      | TIM4_C<br>H1 | LPTIM1_I<br>N1                  | I2C4_SC<br>L       | -                         | -             | USART3<br>_RTS                              | -                                               | QUADSP<br>I_BK1_IO<br>1                    | SAI2_FS_<br>A                            | -               | FMC_A1<br>7/FMC_<br>ALE    | -            | -      | EVEN<br>TOUT |

|        | PD13 | -           | -      | TIM4_C<br>H2 | LPTIM1_<br>OUT                  | I2C4_SD<br>A       | -                         | -             | -                                           | -                                               | QUADSP<br>I_BK1_IO<br>3                    | SAI2_SC<br>K_A                           | -               | FMC_A1<br>8                | -            | -      | EVEN<br>TOUT |

#### Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

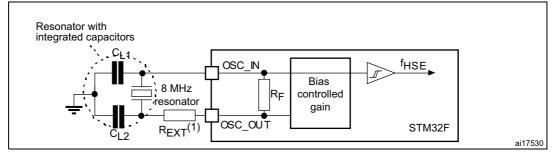

For C<sub>L1</sub> and C<sub>L2</sub>, it is recommended to use high-quality external ceramic capacitors in the 5 pF to 25 pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 32*). C<sub>L1</sub> and C<sub>L2</sub> are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C<sub>L1</sub> and C<sub>L2</sub>. PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C<sub>L1</sub> and C<sub>L2</sub>.

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 40*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol          | Parameter               | Conditions                                     | Min | Тур | Мах | Unit |  |  |

|-----------------|-------------------------|------------------------------------------------|-----|-----|-----|------|--|--|

|                 | LSE current consumption | LSEDRV[1:0]=00<br>Low drive capability         | -   | 250 | -   |      |  |  |

| 1               |                         | LSEDRV[1:0]=10<br>Medium low drive capability  | -   | 300 | -   | nA   |  |  |

| I <sub>DD</sub> |                         | LSEDRV[1:0]=01<br>Medium high drive capability | -   | 370 | -   | ΠA   |  |  |

|                 |                         | LSEDRV[1:0]=11<br>High drive capability        | -   | 480 | -   |      |  |  |

Table 40. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup>

|                                         |                                              |                                                                        |                    | ,            | Ŧ            |              |      |

|-----------------------------------------|----------------------------------------------|------------------------------------------------------------------------|--------------------|--------------|--------------|--------------|------|

| Symbol                                  | Parameter                                    | Conditions                                                             |                    | Min          | Тур          | Мах          | Unit |

|                                         |                                              | Cycle to cycle at                                                      | RMS                | -            | 90           | -            |      |

| Jitter <sup>(3)</sup>                   | Master I2S clock jitter                      | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                           | peak<br>to<br>peak | -            | ±280         | -            | ps   |

|                                         |                                              | Average frequency o<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | -                  | 90           | -            | ps           |      |

|                                         | WS I2S clock jitter                          | Cycle to cycle at 48 k<br>on 1000 samples                              | -                  | 400          | -            | ps           |      |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$         | VCO freq = 100 MHz<br>VCO freq = 432 MHz                               | 0.15<br>0.45       | -            | 0.40<br>0.75 | mA           |      |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on V <sub>DDA</sub> | VCO freq = 100 MHz<br>VCO freq = 432 MHz                               |                    | 0.30<br>0.55 | _            | 0.40<br>0.85 | mA   |

#### Table 44. PLLI2S characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

#### Table 45. PLLISAI characteristics

| Symbol                   | Parameter                                     | Conditions         | Min                 | Тур | Max  | Unit |

|--------------------------|-----------------------------------------------|--------------------|---------------------|-----|------|------|

| f <sub>PLLSAI_IN</sub>   | PLLSAI input clock <sup>(1)</sup>             | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 |      |

| f <sub>PLLSAIP_OUT</sub> | PLLSAI multiplier output clock for 48 MHz     | -                  | -                   | 48  | 75   |      |

| f <sub>PLLSAIQ_OUT</sub> | PLLSAI multiplier output clock<br>for SAI     | -                  | -                   | -   | 216  | MHz  |

| f <sub>PLLSAIR_OUT</sub> | PLLSAI multiplier output clock<br>for LCD-TFT | -                  | -                   | 216 |      |      |

| f <sub>VCO_OUT</sub>     | PLLSAI VCO output                             | -                  | 100                 | -   | 432  |      |

| +                        | PLLSAI lock time                              | VCO freq = 100 MHz | 75                  | -   | 200  |      |

| t <sub>LOCK</sub>        |                                               | VCO freq = 432 MHz | 100                 | -   | 300  | μs   |

| Symbol | Parameter                    | Test conditions                                                     | Тур | Max <sup>(1)</sup> | Unit |  |

|--------|------------------------------|---------------------------------------------------------------------|-----|--------------------|------|--|

| ET     | Total unadjusted error       |                                                                     | ±4  | ±7                 |      |  |

| EO     | Offset error                 | f <sub>ADC</sub> =36 MHz,<br>V <sub>DDA</sub> = 2.4 to 3.6 V,       | ±2  | ±3                 |      |  |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REF</sub> = 1.7 to 3.6 V | ±3  | ±6                 | LSB  |  |

| ED     | Differential linearity error | $V_{DDA} - V_{REF} < 1.2 V$                                         | ±2  | ±3                 |      |  |

| EL     | Integral linearity error     |                                                                     | ±3  | ±6                 |      |  |

Table 65. ADC static accuracy at f<sub>ADC</sub> = 36 MHz

1. Guaranteed by characterization results.

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =18 MHz     | 10.3 | 10.4 | -   | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+} = 1.7 V$ | 64   | 64.2 | -   |      |

| SNR    | Signal-to-noise ratio                | Input Frequency = 20 KHz     | 64   | 65   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 67 | - 72 | -   |      |

1. Guaranteed by characterization results.

## Table 67. ADC dynamic accuracy at $f_{ADC}$ = 36 MHz - limited test conditions<sup>(1)</sup>

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =36 MHz     | 10.6 | 10.8 | -   | bits |

| SINAD  | Signal-to noise and distortion ratio | $V_{DDA} = V_{REF+} = 3.3 V$ | 66   | 67   | -   |      |

| SNR    | Signal-to noise ratio                | Input Frequency = 20 KHz     | 64   | 68   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 70 | - 72 | -   |      |

1. Guaranteed by characterization results.

Note: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.17 does not affect the ADC accuracy.

| Symbol                               | Parameter                                                                                                                                                          | Min | Тур  | Max  | Unit | Comments                                                                                               |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|------|--------------------------------------------------------------------------------------------------------|

|                                      |                                                                                                                                                                    |     | - 76 |      |      | With no load, middle code (0x800) on the                                                               |

|                                      | DAC DC V <sub>DDA</sub> current                                                                                                                                    | -   | 280  | 380  | μA   | inputs                                                                                                 |

| I <sub>DDA</sub> <sup>(4)</sup>      | consumption in quiescent<br>mode <sup>(3)</sup>                                                                                                                    | -   | 475  | 625  | μA   | With no load, worst code (0xF1C) at $V_{REF+}$ = 3.6 V in terms of DC consumption on the inputs        |

| DNL <sup>(4)</sup>                   | Differential non linearity<br>Difference between two                                                                                                               | -   | -    | ±0.5 | LSB  | Given for the DAC in 10-bit configuration.                                                             |

|                                      | consecutive code-1LSB)                                                                                                                                             | -   | -    | ±2   | LSB  | Given for the DAC in 12-bit configuration.                                                             |

|                                      | Integral non linearity                                                                                                                                             | -   | -    | ±1   | LSB  | Given for the DAC in 10-bit configuration.                                                             |

| INL <sup>(4)</sup>                   | (difference between<br>measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023)                                | -   | -    | ±4   | LSB  | Given for the DAC in 12-bit configuration.                                                             |

|                                      | Offset error                                                                                                                                                       | -   | -    | ±10  | mV   | Given for the DAC in 12-bit configuration                                                              |

| Offset <sup>(4)</sup>                | (difference between<br>measured value at Code                                                                                                                      | -   | -    | ±3   | LSB  | Given for the DAC in 10-bit at V <sub>REF+</sub> =<br>3.6 V                                            |

|                                      | (0x800) and the ideal value =<br>V <sub>REF+</sub> /2)                                                                                                             | -   | -    | ±12  | LSB  | Given for the DAC in 12-bit at V <sub>REF+</sub> =<br>3.6 V                                            |

| Gain<br>error <sup>(4)</sup>         | Gain error                                                                                                                                                         | -   | -    | ±0.5 | %    | Given for the DAC in 12-bit configuration                                                              |

| t <sub>SETTLING</sub> <sup>(4)</sup> | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±4LSB | -   | 3    | 6    | μs   | C <sub>LOAD</sub> ≤ 50 pF,<br>R <sub>LOAD</sub> ≥ 5 kΩ                                                 |

| THD <sup>(4)</sup>                   | Total Harmonic Distortion<br>Buffer ON                                                                                                                             | -   | -    | -    | dB   | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                      |

| Update<br>rate <sup>(2)</sup>        | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | -   | -    | 1    | MS/s | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                      |

| t <sub>WAKEUP</sub> <sup>(4)</sup>   | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | -   | 6.5  | 10   | μs   | $C_{LOAD} \le 50$ pF, $R_{LOAD} \ge 5$ k $\Omega$ input code between lowest and highest possible ones. |

| PSRR+ <sup>(2)</sup>                 | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement)                                                                                  | -   | -67  | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                       |

Table 73. DAC characteristics (continued)

1. V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to *Section 2.17.2: Internal reset OFF*).

2. Guaranteed by design.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed by characterization results.

Г

Т

#### SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 76* for the SPI interface are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 5.3.17: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

Т

| Symbol                                    | Parameter             | Conditions                                                       | Min     | Тур   | Max               | Unit |

|-------------------------------------------|-----------------------|------------------------------------------------------------------|---------|-------|-------------------|------|

|                                           |                       | Master mode<br>SPI1,4,5,6<br>2.7≤VDD≤3.6                         |         |       | 54 <sup>(2)</sup> |      |

|                                           |                       | Master mode<br>SPI1,4,5,6<br>1.71≤VDD≤3.6                        |         |       | 27                |      |

|                                           |                       | Master transmitter mode<br>SPI1,4,5,6<br>1.71≤VDD≤3.6            |         |       | 54                |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub> | SPI clock frequency   | Slave receiver mode<br>SPI1,4,5,6<br>1.71≤VDD≤3.6                | -       | -     | 54                | MHz  |

|                                           |                       | Slave mode transmitter/full duplex<br>SPI1,4,5,6<br>2.7≤VDD≤3.6  |         |       | 50 <sup>(3)</sup> |      |

|                                           |                       | Slave mode transmitter/full duplex<br>SPI1,4,5,6<br>1.71≤VDD≤3.6 |         |       | 38 <sup>(3)</sup> |      |

|                                           |                       | Master & Slave mode<br>SPI2,3<br>1.71≤VDD≤3.6                    |         |       | 27                |      |

| tsu(NSS)                                  | NSS setup time        | Slave mode, SPI presc = 2                                        | 4*Tpclk | -     | -                 |      |

| th(NSS)                                   | NSS hold time         | Slave mode, SPI presc = 2                                        | 2*Tpclk | -     | -                 | ns   |

| tw(SCKH)<br>tw(SCKL)                      | SCK high and low time | Master mode                                                      | Tpclk-2 | Tpclk | Tpclk+2           |      |

### USB OTG full speed (FS) characteristics

This interface is present in both the USB OTG HS and USB OTG FS controllers.

| Symbol                              | Parameter                                   | Мах | Unit |

|-------------------------------------|---------------------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB OTG full speed transceiver startup time | 1   | μs   |

### Table 79. USB OTG full speed startup time

1. Guaranteed by design.

| Syn                            | nbol                           | Parameter                                                 | Conditions                                                     | Min.<br>(1)        | Тур. | Max.<br>(1) | Unit |

|--------------------------------|--------------------------------|-----------------------------------------------------------|----------------------------------------------------------------|--------------------|------|-------------|------|

| V <sub>DDUSB</sub>             |                                | USB OTG full speed<br>transceiver operating<br>voltage    | -                                                              | 3.0 <sup>(2)</sup> | -    | 3.6         | V    |

| Input<br>levels                | V <sub>DI</sub> <sup>(3)</sup> | Differential input sensitivity                            | I(USB_FS_DP/DM,<br>USB_HS_DP/DM)                               | 0.2                | -    | -           |      |

| levels                         | V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range                            | Includes V <sub>DI</sub> range                                 | 0.8                | -    | 2.5         | V    |

| V <sub>SE</sub> <sup>(3)</sup> |                                | Single ended receiver threshold                           | -                                                              | 1.3                | -    | 2.0         |      |

| Output V <sub>OL</sub>         |                                | Static output level low                                   | ${\sf R}_{\sf L}$ of 1.5 k\Omega to 3.6 ${\sf V}^{(4)}$        | -                  | -    | 0.3         | v    |

| levels V <sub>OH</sub>         |                                | Static output level high                                  | ${\sf R}_{\sf L}$ of 15 k $\Omega$ to ${\sf V}_{\sf SS}^{(4)}$ | 2.8                | -    | 3.6         | v    |

| R <sub>PD</sub>                |                                | PA11, PA12, PB14, PB15<br>(USB_FS_DP/DM,<br>USB_HS_DP/DM) | V <sub>IN</sub> = V <sub>DD</sub>                              | 17                 | 21   | 24          |      |

|                                |                                | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | VIN - VDD                                                      | 0.65               | 1.1  | 2.0         | kΩ   |

|                                |                                | PA12, PB15 (USB_FS_DP,<br>USB_HS_DP)                      | V <sub>IN</sub> = V <sub>SS</sub>                              | 1.5                | 1.8  | 2.1         |      |

| R                              | PU                             | PA9, PB13<br>(OTG_FS_VBUS,<br>OTG_HS_VBUS)                | V <sub>IN</sub> = V <sub>SS</sub>                              | 0.25               | 0.37 | 0.55        |      |

#### Table 80. USB OTG full speed DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. The USB OTG full speed transceiver functionality is ensured down to 2.7 V but not the full USB full speed electrical characteristics which are degraded in the 2.7-to-3.0 V V<sub>DDUSB</sub> voltage range.

- 3. Guaranteed by design.

- 4.  $R_L$  is the load connected on the USB OTG full speed drivers.

Note:

When VBUS sensing feature is enabled, PA9 and PB13 should be left at their default state (floating input), not as alternate function. A typical 200  $\mu$ A current consumption of the sensing block (current to voltage conversion to determine the different sessions) can be observed on PA9 and PB13 when the feature is enabled.

1. Guaranteed by characterization results.

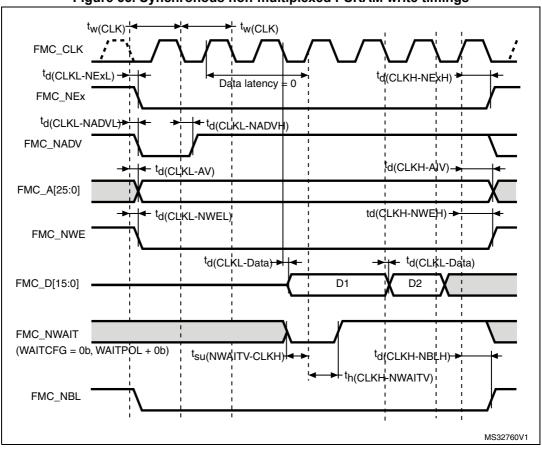

Figure 65. Synchronous non-multiplexed PSRAM write timings

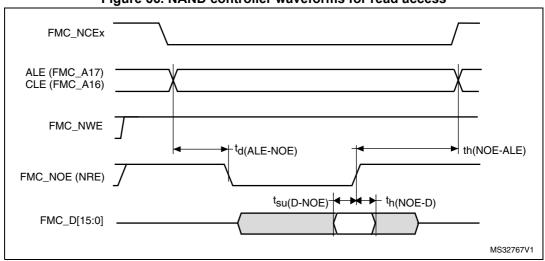

Figure 66. NAND controller waveforms for read access

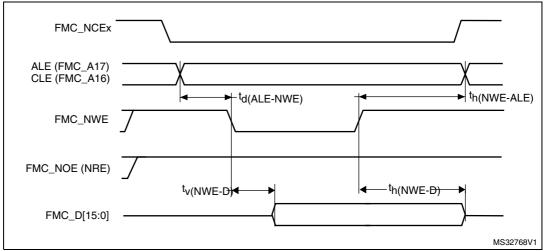

Figure 67. NAND controller waveforms for write access

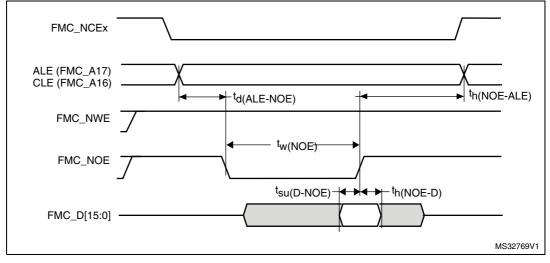

Figure 68. NAND controller waveforms for common memory read access

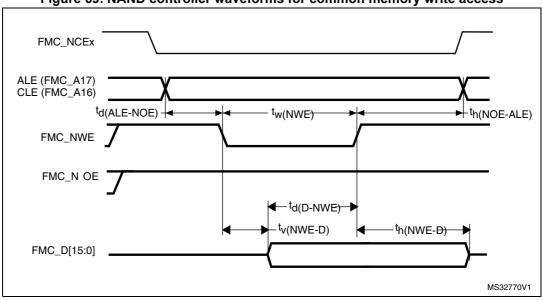

#### Figure 69. NAND controller waveforms for common memory write access

Table 100. Switching characteristics for NAND Flash read cycles<sup>(1)</sup>

| Symbol                  | Parameter                                  | Min                     | Max                     | Unit |

|-------------------------|--------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(N0E)</sub>     | FMC_NOE low width                          | 4T <sub>HCLK</sub> -0.5 | 4T <sub>HCLK</sub>      |      |

| t <sub>su(D-NOE)</sub>  | FMC_D[15-0] valid data before FMC_NOE high | 13                      | -                       |      |

| t <sub>h(NOE-D)</sub>   | FMC_D[15-0] valid data after FMC_NOE high  | 3                       | -                       | ns   |

| t <sub>d(ALE-NOE)</sub> | FMC_ALE valid before FMC_NOE low           | -                       | 3T <sub>HCLK</sub> -0.5 |      |

| t <sub>h(NOE-ALE)</sub> | FMC_NWE high to FMC_ALE invalid            | 3T <sub>HCLK</sub> -2   | -                       |      |

1. Guaranteed by characterization results.

| Table 101. Switching characteristics for NAND Flash write cycles <sup>(1)</sup> |

|---------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------|

| Symbol                  | Parameter                             | Min                     | Мах                     | Unit |

|-------------------------|---------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NWE)</sub>     | FMC_NWE low width                     | 4T <sub>HCLK</sub> -0.5 | 4T <sub>HCLK</sub>      |      |

| t <sub>v(NWE-D)</sub>   | FMC_NWE low to FMC_D[15-0] valid      | 0                       | -                       |      |

| t <sub>h(NWE-D)</sub>   | FMC_NWE high to FMC_D[15-0] invalid   | 3T <sub>HCLK</sub> -1   | -                       | ns   |

| t <sub>d(D-NWE)</sub>   | FMC_D[15-0] valid before FMC_NWE high | 5T <sub>HCLK</sub> -3   | -                       | 115  |

| t <sub>d(ALE-NWE)</sub> | FMC_ALE valid before FMC_NWE low      | -                       | 3T <sub>HCLK</sub> -0.5 |      |

| t <sub>h(NWE-ALE)</sub> | FMC_NWE high to FMC_ALE invalid       | 3T <sub>HCLK</sub> -2   | -                       |      |

1. Guaranteed by characterization results.

| Symbol                         | Parameter              | Min                     | Мах                     | Unit |

|--------------------------------|------------------------|-------------------------|-------------------------|------|

| t <sub>w(SDCLK)</sub>          | FMC_SDCLK period       | 2T <sub>HCLK</sub> -0.5 | 2T <sub>HCLK</sub> +0.5 |      |

| t <sub>d(SDCLKL_Data</sub> )   | Data output valid time | -                       | 4                       |      |

| t <sub>h(SDCLKL</sub> _Data)   | Data output hold time  | 0                       | -                       |      |

| $t_{d(SDCLKL_Add)}$            | Address valid time     | -                       | 3.5                     |      |

| t <sub>d(SDCLKL-SDNWE)</sub>   | SDNWE valid time       | -                       | 0.5                     |      |

| t <sub>h(SDCLKL-SDNWE)</sub>   | SDNWE hold time        | 0                       | -                       | ns   |

| t <sub>d(SDCLKL</sub> - SDNE)  | Chip select valid time | -                       | 0.5                     | 115  |

| t <sub>h(SDCLKL</sub> - SDNE)  | Chip select hold time  | 0                       | -                       |      |

| t <sub>d</sub> (SDCLKL-SDNRAS) | SDNRAS valid time      | -                       | 0.5                     |      |

| t <sub>h(SDCLKL-SDNRAS)</sub>  | SDNRAS hold time       | 0                       | -                       |      |

| t <sub>d(SDCLKL</sub> -SDNCAS) | SDNCAS valid time      | -                       | 0.5                     |      |

| t <sub>d(SDCLKL-SDNCAS)</sub>  | SDNCAS hold time       | 0                       | -                       |      |

Table 105. LPSDR SDRAM write timings<sup>(1)</sup>

1. Guaranteed by characterization results.

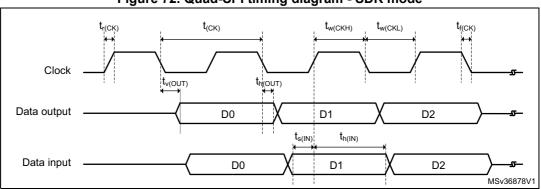

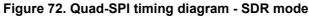

## 5.3.28 Quad-SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 106* and *Table 107* for Quad-SPI are derived from tests performed under the ambient temperature,  $f_{AHB}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 20 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 5.3.17: I/O port characteristics for more details on the input/output alternate function characteristics.

| Symbol     | Parameter      | Conditions                                     | Min | Тур | Max | Unit |

|------------|----------------|------------------------------------------------|-----|-----|-----|------|

| Eck1/t(CK) | Quad-SPI clock | 2.7 V⊴V <sub>DD</sub> <3.6 V<br>CL=20 pF       | -   | -   | 108 | MHz  |

| Fck1/t(CK) | frequency      | 1.71 V <v<sub>DD&lt;3.6 V<br/>CL=15 pF</v<sub> | -   | -   | 100 |      |

Table 106. Quad-SPI characteristics in SDR mode<sup>(1)</sup>

# 5.3.29 Camera interface (DCMI) timing specifications

Unless otherwise specified, the parameters given in *Table 108* for DCMI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage summarized in *Table 17*, with the following configuration:

- DCMI\_PIXCLK polarity: falling

- DCMI\_VSYNC and DCMI\_HSYNC polarity: high

- Data formats: 14 bits

| Table 108. DCMI characteristics <sup>(1)</sup> |

|------------------------------------------------|

|------------------------------------------------|

| Symbol                                           | Parameter                                     | Min | Max | Unit |

|--------------------------------------------------|-----------------------------------------------|-----|-----|------|

| -                                                | Frequency ratio DCMI_PIXCLK/f <sub>HCLK</sub> |     | 0.4 |      |

| DCMI_PIXCLK                                      | CLK Pixel clock input                         |     | 54  | MHz  |

| D <sub>Pixel</sub>                               | Pixel Clock input duty cycle                  |     | 70  | %    |

| t <sub>su(DATA)</sub>                            | Data input setup time                         | 3.5 | -   |      |

| t <sub>h(DATA)</sub>                             | Data input hold time                          | 0   | -   |      |

| t <sub>su(HSYNC)</sub><br>t <sub>su(VSYNC)</sub> | DCMI_HSYNC/DCMI_VSYNC input setup time        | 2.5 | -   | ns   |

| t <sub>h(HSYNC)</sub><br>t <sub>h(VSYNC)</sub>   | DCMI_HSYNC/DCMI_VSYNC input hold time         | 0   | -   |      |

1. Guaranteed by characterization results.

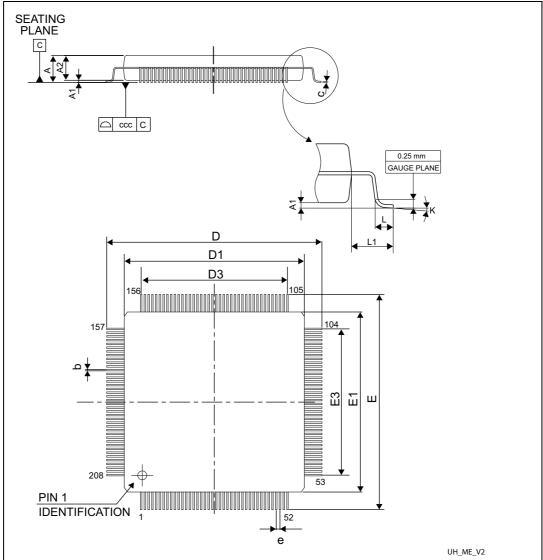

|        |        |             | data   |                       |        |        |  |

|--------|--------|-------------|--------|-----------------------|--------|--------|--|

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |  |

| Symbol | Min    | Тур         | Мах    | Min                   | Тур    | Мах    |  |

| А      | -      | -           | 1.600  | -                     | -      | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| С      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |  |

| D      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| D3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |

| E      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| E3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |  |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |  |

| k      | 0°     | 3.5°        | 7°     | 0°                    | 3.5°   | 7°     |  |

| CCC    | -      | -           | 0.080  | -                     | -      | 0.0031 |  |

| Table 112. LQPF100, | 14 x 14 mm | 100-pin low-profile | quad flat package mechanical |

|---------------------|------------|---------------------|------------------------------|

|                     |            | data                |                              |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

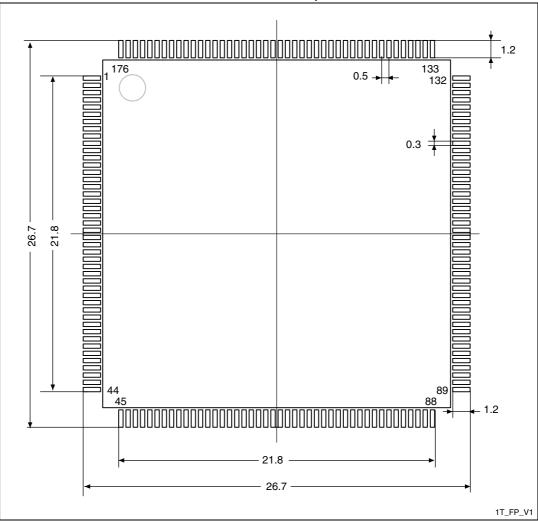

Figure 92. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.

# 6.6 LQFP208, 28 x 28 mm low-profile quad flat package information

Figure 94. LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 119. LQFP208, 2 | 28 x 28 mm, 208-pin low-profile quad flat package |

|-----------------------|---------------------------------------------------|

|                       | mechanical data                                   |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| A      | -           | -     | 1.600 |                       | -      | 0.0630 |

| A1     | 0.050       | -     | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400 | 1.450 | 0.0531                | 0.0551 | 0.0571 |

DocID027590 Rev 4