Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                                        |

|----------------------------|--------------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                                 |

| Core Processor             | ARM® Cortex®-M7                                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                                     |

| Speed                      | 216MHz                                                                                                 |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SAI, SD, SPDIF-Rx, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                      |

| Number of I/O              | 114                                                                                                    |

| Program Memory Size        | 1MB (1M × 8)                                                                                           |

| Program Memory Type        | FLASH                                                                                                  |

| EEPROM Size                | -                                                                                                      |

| RAM Size                   | 320K x 8                                                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                            |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                  |

| Oscillator Type            | Internal                                                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                      |

| Mounting Type              | Surface Mount                                                                                          |

| Package / Case             | 143-UFBGA, WLCSP                                                                                       |

| Supplier Device Package    | -                                                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f746zgy6tr                                |

|                            |                                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.3 Embedded Flash memory

The STM32F745xx and STM32F746xx devices embed a Flash memory of up to 1 Mbyte available for storing programs and data.

# 2.4 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify the data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a mean of verifying the Flash memory integrity. The CRC calculation unit helps to compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

# 2.5 Embedded SRAM

All the devices features:

- System SRAM up to 320 Kbytes:

- SRAM1 on AHB bus Matrix: 240 Kbytes

- SRAM2 on AHB bus Matrix: 16 Kbytes

- DTCM-RAM on TCM interface (Tighly Coupled Memory interface): 64 Kbytes for critical real-time data.

- Instruction RAM (ITCM-RAM) 16 Kbytes:

- It is mapped on TCM interface and reserved only for CPU Execution/Instruction useful for critical real-time routines.

The Data TCM RAM is accessible by the GP-DMAs and peripherals DMAs through specific AHB slave of the CPU. The TCM RAM instruction is reserved only for CPU. It is accessed at CPU clock speed with 0-wait states.

• 4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

# 2.6 AXI-AHB bus matrix

The STM32F745xx and STM32F746xx system architecture is based on 2 sub-systems:

- An AXI to multi AHB bridge converting AXI4 protocol to AHB-Lite protocol:

- 3x AXI to 32-bit AHB bridges connected to AHB bus matrix

- 1x AXI to 64-bit AHB bridge connected to the embedded flash

- A multi-AHB Bus-Matrix:

- The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS, LCD-TFT, and DMA2D) and the slaves (Flash memory, RAM, FMC, Quad-SPI, AHB and APB peripherals) and ensures a seamless and an efficient operation even when several high-speed peripherals work simultaneously.

DocID027590 Rev 4

### 2.18.3 Regulator ON/OFF and internal reset ON/OFF availability

| Table                                                       | Table 4. Regulator ON/OFF and Internal reset ON/OFF availability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                             |                                         |                             |  |  |  |  |  |  |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------------------|-----------------------------|--|--|--|--|--|--|--|

| Package                                                     | Regulator ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Regulator OFF                               | Internal reset ON                       | Internal reset OFF          |  |  |  |  |  |  |  |

| LQFP100                                                     | Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | No                                          | Yes                                     | No                          |  |  |  |  |  |  |  |

| LQFP144,<br>LQFP208                                         | The second secon | No                                          |                                         |                             |  |  |  |  |  |  |  |

| TFBGA100,<br>LQFP176,<br>WLCSP143,<br>UFBGA176,<br>TFBGA216 | Yes<br>BYPASS_REG set<br>to V <sub>SS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Yes<br>BYPASS_REG set<br>to V <sub>DD</sub> | Yes<br>PDR_ON set to<br>V <sub>DD</sub> | Yes<br>PDR_ON set to<br>VSS |  |  |  |  |  |  |  |

Table 4. Regulator ON/OFF and internal reset ON/OFF availability

# 2.19 Real-time clock (RTC), backup SRAM and backup registers

The RTC is an independent BCD timer/counter. It supports the following features:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28, 29 (leap year), 30, and 31 days of the month.

- Two programmable alarms.

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 0.95 ppm resolution, to compensate for quartz crystal inaccuracy.

- Three anti-tamper detection pins with programmable filter.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event, or by a switch to V<sub>BAT</sub> mode.

- 17-bit auto-reload wakeup timer (WUT) for periodic events with programmable resolution and period.

The RTC and the 32 backup registers are supplied through a switch that takes power either from the  $V_{\text{DD}}$  supply when present or from the  $V_{\text{BAT}}$  pin.

The backup registers are 32-bit registers used to store 128 bytes of user application data when VDD power is not present. They are not reset by a system or power reset, or when the device wakes up from Standby mode.

The RTC clock sources can be:

- A 32.768 kHz external crystal (LSE)

- An external resonator or oscillator(LSE)

- The internal low-power RC oscillator (LSI, with typical frequency of 32 kHz)

- The high-speed external clock (HSE) divided by 32.

#### 2.22.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

#### 2.22.4 Low-power timer (LPTIM1)

The low-power timer has an independent clock and is running also in Stop mode if it is clocked by LSE, LSI or an external clock. It is able to wakeup the devices from Stop mode.

This low-power timer supports the following features:

- 16-bit up counter with 16-bit autoreload register

- 16-bit compare register

- Configurable output: pulse, PWM

- Continuous / one-shot mode

- Selectable software / hardware input trigger

- Selectable clock source:

- Internal clock source: LSE, LSI, HSI or APB clock

- External clock source over LPTIM input (working even with no internal clock source running, used by the Pulse Counter Application)

- Programmable digital glitch filter

- Encoder mode

#### 2.22.5 Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

#### 2.22.6 Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 2.22.7 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard downcounter. It features:

- A 24-bit downcounter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0

- Programmable clock source.

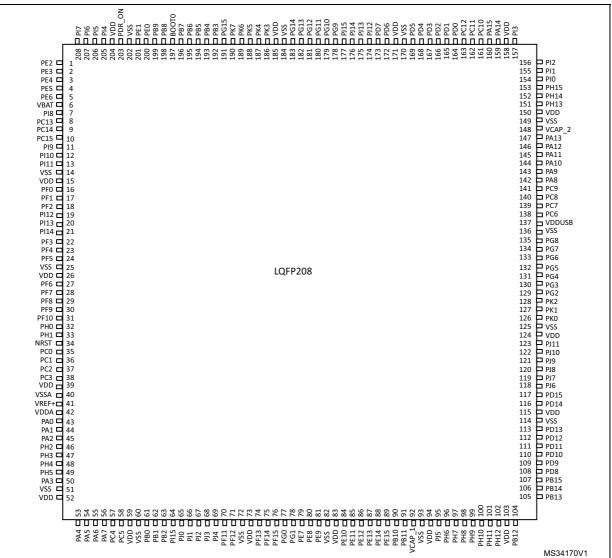

#### Pinouts and pin description

Figure 16. STM32F74xBx LQFP208 pinout

1. The above figure shows the package top view.

#### STM32F745xx STM32F746xx

|          |                    | 11. FMC pin defin |        |       |

|----------|--------------------|-------------------|--------|-------|

| Pin name | NOR/PSRAM/SR<br>AM | NOR/PSRAM<br>Mux  | NAND16 | SDRAM |

| PF0      | A0                 | -                 | -      | A0    |

| PF1      | A1                 | -                 | -      | A1    |

| PF2      | A2                 | -                 | -      | A2    |

| PF3      | A3                 | -                 | -      | A3    |

| PF4      | A4                 | -                 | -      | A4    |

| PF5      | A5                 | -                 | -      | A5    |

| PF12     | A6                 | -                 | -      | A6    |

| PF13     | A7                 | -                 | -      | A7    |

| PF14     | A8                 | -                 | -      | A8    |

| PF15     | A9                 | -                 | -      | A9    |

| PG0      | A10                | -                 | -      | A10   |

| PG1      | A11                | -                 | -      | A11   |

| PG2      | A12                | -                 | -      | A12   |

| PG3      | A13                | -                 | -      | -     |

| PG4      | A14                | -                 | -      | BA0   |

| PG5      | A15                | -                 | -      | BA1   |

| PD11     | A16                | A16               | CLE    | -     |

| PD12     | A17                | A17               | ALE    | -     |

| PD13     | A18                | A18               | -      | -     |

| PE3      | A19                | A19               | -      | -     |

| PE4      | A20                | A20               | -      | -     |

| PE5      | A21                | A21               | -      | -     |

| PE6      | A22                | A22               | -      | -     |

| PE2      | A23                | A23               | -      | -     |

| PG13     | A24                | A24               | -      | -     |

| PG14     | A25                | A25               | -      | -     |

| PD14     | D0                 | DA0               | D0     | D0    |

| PD15     | D1                 | DA1               | D1     | D1    |

| PD0      | D2                 | DA2               | D2     | D2    |

| PD1      | D3                 | DA3               | D3     | D3    |

| PE7      | D4                 | DA4               | D4     | D4    |

| PE8      | D5                 | DA5               | D5     | D5    |

| PE9      | D6                 | DA6               | D6     | D6    |

| PE10     | D7                 | DA7               | D7     | D7    |

#### Table 11. FMC pin definition

78/227

DocID027590 Rev 4

# Pinouts and pin description

STM32F745xx STM32F746xx

| 5 |

|---|

|---|

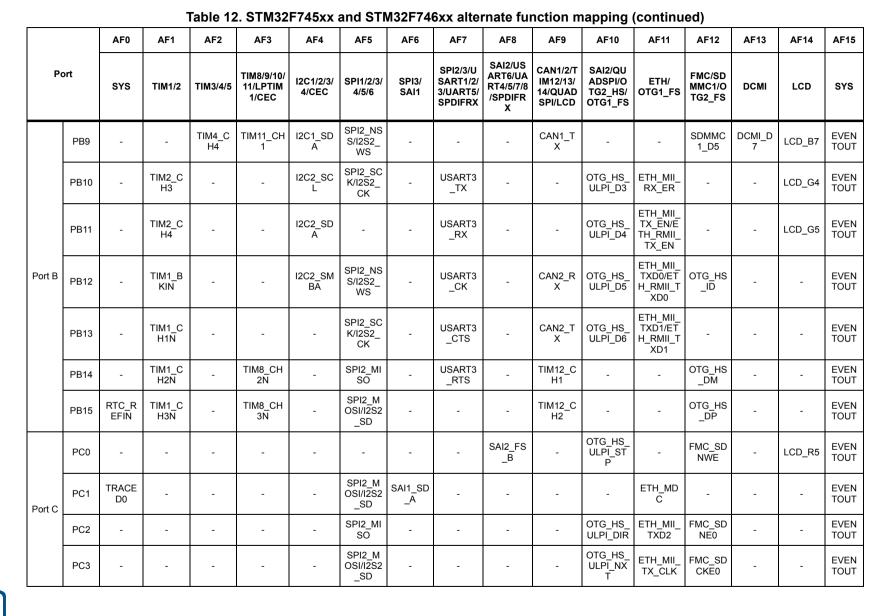

#### Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

| Table 12. STMS2F745XX and STMS2F746XX alternate function mapping (continued) |      |             |        |              |                                 |                    |                    |                           |                                             |                                                 |                                            |                                          |                                        |                            |             |               |              |

|------------------------------------------------------------------------------|------|-------------|--------|--------------|---------------------------------|--------------------|--------------------|---------------------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|------------------------------------------|----------------------------------------|----------------------------|-------------|---------------|--------------|

|                                                                              |      | AF0         | AF1    | AF2          | AF3                             | AF4                | AF5                | AF6                       | AF7                                         | AF8                                             | AF9                                        | AF10                                     | AF11                                   | AF12                       | AF13        | AF14          | AF15         |

| Po                                                                           | ort  | SYS         | TIM1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1             | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | SAI2/QU<br>ADSPI/O<br>TG2_HS/<br>OTG1_FS | ETH/<br>OTG1_FS                        | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI        | LCD           | SYS          |

|                                                                              | PC4  | -           | -      | -            | -                               | -                  | I2S1_M<br>CK       | -                         | -                                           | SPDIFRX<br>_IN2                                 | -                                          | -                                        | ETH_MII_<br>RXD0/ET<br>H_RMII_<br>RXD0 | FMC_SD<br>NE0              | -           | -             | EVEN<br>TOUT |

|                                                                              | PC5  | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | SPDIFRX<br>_IN3                                 | -                                          | -                                        | ETH_MII_<br>RXD1/ET<br>H_RMII_<br>RXD1 | FMC_SD<br>CKE0             | -           | -             | EVEN<br>TOUT |

|                                                                              | PC6  | -           | -      | TIM3_C<br>H1 | TIM8_CH<br>1                    | -                  | I2S2_M<br>CK       | -                         | -                                           | USART6<br>_TX                                   | -                                          | -                                        | -                                      | SDMMC<br>1_D6              | DCMI_D<br>0 | LCD_HS<br>YNC | EVEN<br>TOUT |

|                                                                              | PC7  | -           | -      | TIM3_C<br>H2 | TIM8_<br>CH2                    | -                  | -                  | I2S3_M<br>CK              | -                                           | USART6<br>_RX                                   | -                                          | -                                        | -                                      | SDMMC<br>1_D7              | DCMI_D<br>1 | LCD_G6        | EVEN<br>TOUT |

|                                                                              | PC8  | TRACE<br>D1 | -      | TIM3_C<br>H3 | TIM8_<br>CH3                    | -                  | -                  | -                         | UART5_<br>RTS                               | USART6<br>_CK                                   | -                                          | -                                        | -                                      | SDMMC<br>1_D0              | DCMI_D<br>2 | -             | EVEN<br>TOUT |

| Port C                                                                       | PC9  | MCO2        | -      | TIM3_C<br>H4 | TIM8_<br>CH4                    | I2C3_SD<br>A       | I2S_CKI<br>N       | -                         | UART5_<br>CTS                               | -                                               | QUADSP<br>I_BK1_IO<br>0                    | -                                        | -                                      | SDMMC<br>1_D1              | DCMI_D<br>3 | -             | EVEN<br>TOUT |

|                                                                              | PC10 | -           | -      | -            | -                               | -                  | -                  | SPI3_SC<br>K/I2S3_<br>CK  | USART3<br>_TX                               | UART4_T<br>X                                    | QUADSP<br>I_BK1_IO<br>1                    | -                                        | -                                      | SDMMC<br>1_D2              | DCMI_D<br>8 | LCD_R2        | EVEN<br>TOUT |

|                                                                              | PC11 | -           | -      | -            | -                               | -                  | -                  | SPI3_MI<br>SO             | USART3<br>_RX                               | UART4_<br>RX                                    | QUADSP<br>I_BK2_N<br>CS                    | -                                        | -                                      | SDMMC<br>1_D3              | DCMI_D<br>4 | -             | EVEN<br>TOUT |

|                                                                              | PC12 | TRACE<br>D3 | -      | -            | -                               | -                  | -                  | SPI3_M<br>OSI/I2S3<br>_SD | USART3<br>_CK                               | UART5_T<br>X                                    | -                                          | -                                        | -                                      | SDMMC<br>1_CK              | DCMI_D<br>9 | -             | EVEN<br>TOUT |

|                                                                              | PC13 | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | -           | -             | EVEN<br>TOUT |

|                                                                              | PC14 | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | -           | -             | EVEN<br>TOUT |

|                                                                              | PC15 | -           | -      | -            | -                               | -                  | -                  | -                         | -                                           | -                                               | -                                          | -                                        | -                                      | -                          | -           | -             | EVEN<br>TOUT |

STM32F745xx STM32F746xx

79/227

Pinouts and pin description

88/227

DocID027590 Rev 4

|        |     |     |        |          |                                 |                    |                    |               |                                             | indic id                                        |                                            |         | (               |                            |      |        |              |

|--------|-----|-----|--------|----------|---------------------------------|--------------------|--------------------|---------------|---------------------------------------------|-------------------------------------------------|--------------------------------------------|---------|-----------------|----------------------------|------|--------|--------------|

|        |     | AF0 | AF1    | AF2      | AF3                             | AF4                | AF5                | AF6           | AF7                                         | AF8                                             | AF9                                        | AF10    | AF11            | AF12                       | AF13 | AF14   | AF15         |

| P      | ort | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10/<br>11/LPTIM<br>1/CEC | I2C1/2/3/<br>4/CEC | SPI1/2/3/<br>4/5/6 | SPI3/<br>SAI1 | SPI2/3/U<br>SART1/2/<br>3/UART5/<br>SPDIFRX | SAI2/US<br>ART6/UA<br>RT4/5/7/8<br>/SPDIFR<br>X | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/LCD | ADSPI/O | ETH/<br>OTG1_FS | FMC/SD<br>MMC1/O<br>TG2_FS | DCMI | LCD    | SYS          |

|        | PK0 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -       | -               | -                          | -    | LCD_G5 | EVEN<br>TOUT |

|        | PK1 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -       | -               | -                          | -    | LCD_G6 | EVEN<br>TOUT |

|        | PK2 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -       | -               | -                          | -    | LCD_G7 | EVEN<br>TOUT |

| Port K | PK3 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -       | -               | -                          | -    | LCD_B4 | EVEN<br>TOUT |

| POILK  | PK4 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -       | -               | -                          | -    | LCD_B5 | EVEN<br>TOUT |

|        | PK5 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -       | -               | -                          | -    | LCD_B6 | EVEN<br>TOUT |

|        | PK6 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -       | -               | -                          | -    | LCD_B7 | EVEN<br>TOUT |

|        | PK7 | -   | -      | -        | -                               | -                  | -                  | -             | -                                           | -                                               | -                                          | -       | -               | -                          | -    | LCD_DE | EVEN<br>TOUT |

#### Table 12. STM32F745xx and STM32F746xx alternate function mapping (continued)

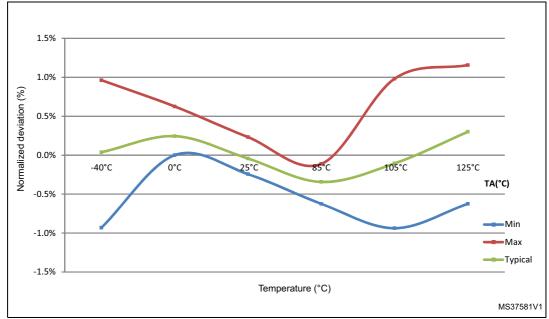

#### 5.3.10 Internal clock source characteristics

The parameters given in *Table 41* and *Table 42* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

#### High-speed internal (HSI) RC oscillator

|                                     |                                       |                                      | -   |     |     |      |

|-------------------------------------|---------------------------------------|--------------------------------------|-----|-----|-----|------|

| Symbol                              | Parameter                             | Conditions                           | Min | Тур | Max | Unit |

| f <sub>HSI</sub>                    | Frequency                             | -                                    | -   | 16  | -   | MHz  |

|                                     | HSI user trimming step <sup>(2)</sup> | -                                    | -   | -   | 1   | %    |

| 100                                 | Accuracy of the HSI oscillator        | $T_A = -40$ to 105 °C <sup>(3)</sup> | - 8 | -   | 4.5 | %    |

| ACC <sub>HSI</sub>                  |                                       | $T_A = -10$ to 85 °C <sup>(3)</sup>  | - 4 | -   | 4   | %    |

|                                     |                                       | $T_A = 25 \ ^{\circ}C^{(4)}$         | - 1 | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                    | -   | 2.2 | 4   | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power consumption      | -                                    | -   | 60  | 80  | μA   |

| Table 41. HS | loscillator | characteristics | (1) |

|--------------|-------------|-----------------|-----|

|--------------|-------------|-----------------|-----|

1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Factory calibrated, parts not soldered.

#### Figure 34. HSI deviation versus temperature

1. Guaranteed by characterization results.

|                                         |                                              |                                                                        | ,                  | -            |      |              |      |

|-----------------------------------------|----------------------------------------------|------------------------------------------------------------------------|--------------------|--------------|------|--------------|------|

| Symbol                                  | Parameter                                    | Conditions                                                             |                    | Min          | Тур  | Мах          | Unit |

|                                         |                                              | Cycle to cycle at                                                      | RMS                | -            | 90   | -            |      |

| Jitter <sup>(3)</sup>                   | Master I2S clock jitter                      | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                           | peak<br>to<br>peak | -            | ±280 | -            | ps   |

|                                         |                                              | Average frequency o<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | -                  | 90           | -    | ps           |      |

|                                         | WS I2S clock jitter                          | Cycle to cycle at 48 k<br>on 1000 samples                              | -                  | 400          | -    | ps           |      |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$         | VCO freq = 100 MHz<br>VCO freq = 432 MHz                               |                    | 0.15<br>0.45 | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on V <sub>DDA</sub> | VCO freq = 100 MHz<br>VCO freq = 432 MHz                               |                    | 0.30<br>0.55 | _    | 0.40<br>0.85 | mA   |

#### Table 44. PLLI2S characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

#### Table 45. PLLISAI characteristics

| Symbol                   | Parameter                                     | Conditions         | Min                 | Тур | Max  | Unit |

|--------------------------|-----------------------------------------------|--------------------|---------------------|-----|------|------|

| f <sub>PLLSAI_IN</sub>   | PLLSAI input clock <sup>(1)</sup>             | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 |      |

| f <sub>PLLSAIP_OUT</sub> | PLLSAI multiplier output clock for 48 MHz     | -                  | -                   | 48  | 75   |      |

| f <sub>PLLSAIQ_OUT</sub> | PLLSAI multiplier output clock<br>for SAI     | -                  | -                   | -   | 216  | MHz  |

| f <sub>PLLSAIR_OUT</sub> | PLLSAI multiplier output clock<br>for LCD-TFT | -                  | -                   | -   | 216  |      |

| f <sub>VCO_OUT</sub>     | PLLSAI VCO output                             | -                  | 100                 | -   | 432  |      |

| +                        | PLLSAI lock time                              | VCO freq = 100 MHz | 75                  | -   | 200  |      |

| t <sub>LOCK</sub>        |                                               | VCO freq = 432 MHz | 100                 | -   | 300  | μs   |

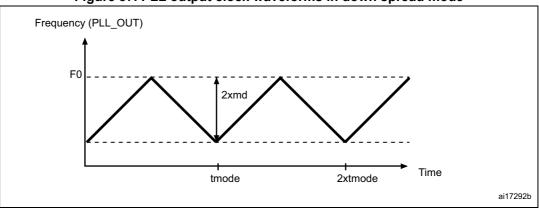

Figure 37. PLL output clock waveforms in down spread mode

## 5.3.13 Memory characteristics

#### Flash memory

The characteristics are given at TA = -40 to 105 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

| Symbol          | Parameter                      | Conditions                                  | Min | Тур | Max | Unit |  |  |  |

|-----------------|--------------------------------|---------------------------------------------|-----|-----|-----|------|--|--|--|

|                 | I <sub>DD</sub> Supply current | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V  | -   | 14  | -   |      |  |  |  |

| I <sub>DD</sub> |                                | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 17  | -   | mA   |  |  |  |

|                 |                                | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 24  | -   |      |  |  |  |

Table 47. Flash memory characteristics

| Symbol                  | Parameter                  | Parameter Conditions                             |   |      | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|--------------------------------------------------|---|------|--------------------|------|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | - | 16   | 100 <sup>(2)</sup> | μs   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | - | 400  | 800                |      |

| t <sub>erase32kb</sub>  | Sector (32 KB) erase time  | Program/erase parallelism<br>(PSIZE) = x 16      | - | 250  | 600                | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | - | 200  | 500                |      |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 8       | - | 1100 | 2400               |      |

| t <sub>erase128kb</sub> | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | - | 800  | 1400               | ms   |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32      | - | 500  | 1100               |      |

#### STM32F745xx STM32F746xx

| Symbol                                                      | Para                                                                 | neter                                                                | Conditions                                                       | Min                                     | Тур | Мах  | Unit |

|-------------------------------------------------------------|----------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------|-----|------|------|

|                                                             | FT, TTa and NF                                                       |                                                                      | 17/10/ 26/                                                       | 0.45V <sub>DD</sub> +0.3 <sup>(1)</sup> |     |      |      |

|                                                             | high level volta                                                     | ge <sup>(5)</sup>                                                    | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                     | 0.7V <sub>DD</sub> <sup>(2)</sup>       | -   | -    |      |

| V <sub>IH</sub>                                             | BOOT I/O inpu                                                        | t high level                                                         | 1.75 V≤V <sub>DD</sub> ≤3.6 V, –<br>40 °C≤T <sub>A</sub> ≤105 °C | 0.17V <sub>DD</sub> +0.7 <sup>(1)</sup> |     |      | V    |

|                                                             | voltage                                                              |                                                                      | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C     | 0.17 V <sub>DD</sub> +0.7 V             | -   | -    |      |

|                                                             | FT, TTa and NF hysteresis                                            | RST I/O input                                                        | 1.7 V≤V <sub>DD</sub> ≤3.6 V                                     | 10%V <sub>DD</sub> <sup>(3)</sup>       | -   | -    |      |

| V <sub>HYS</sub>                                            |                                                                      | thystoropia                                                          | 1.75 V≤V <sub>DD</sub> ≤3.6 V, –<br>40 °C≤T <sub>A</sub> ≤105 °C | 0.1                                     |     |      | v    |

| BOOT I/O input                                              | rysteresis                                                           | 1.7 V≤V <sub>DD</sub> ≤3.6 V,<br>0 °C≤T <sub>A</sub> ≤105 °C         | 0.1                                                              | -                                       | -   |      |      |

|                                                             | I/O input leakage current <sup>(4)</sup>                             |                                                                      | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub>                | -                                       | -   | ±1   |      |

| l <sub>lkg</sub>                                            | I/O FT input leakage current <sup>(5)</sup>                          |                                                                      | $V_{IN} = 5 V$                                                   | -                                       | -   | 3    | μA   |

| Weak pull-up<br>R <sub>PU</sub> equivalent                  | R <sub>PU</sub>                                                      | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_ID<br>,OTG_HS_ID<br>) | V <sub>IN</sub> = V <sub>SS</sub>                                | 30                                      | 40  | 50   |      |

|                                                             | resistor <sup>(6)</sup>                                              | PA10/PB12<br>(OTG_FS_ID<br>,OTG_HS_ID<br>)                           |                                                                  | 7                                       | 10  | 14   | ko   |

| Weak pull-<br>down<br>equivalent<br>resistor <sup>(7)</sup> | All pins<br>except for<br>PA10/PB12<br>(OTG_FS_ID<br>,OTG_HS_ID<br>) | V <sub>IN</sub> = V <sub>DD</sub>                                    | 30                                                               | 40                                      | 50  | - kΩ |      |

|                                                             | resistor <sup>(7)</sup>                                              | PA10/PB12<br>(OTG_FS_ID<br>,OTG_HS_ID<br>)                           |                                                                  | 7                                       | 10  | 14   |      |

| C <sub>IO</sub> <sup>(8)</sup>                              | I/O pin capacita                                                     | ince                                                                 | -                                                                | -                                       | 5   | -    | pF   |

#### Table 56. I/O static characteristics (continued)

1. Guaranteed by design.

2. Tested in production.

3. With a minimum of 200 mV.

4. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins, Refer to Table 55: I/O current injection susceptibility

- To sustain a voltage higher than VDD +0.3 V, the internal pull-up/pull-down resistors must be disabled. Leakage could be higher than the maximum value, if negative current is injected on adjacent pins. Refer to Table 55: I/O current injection susceptibility

- 6. Pull-up resistors are designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimum (~10% order).

DocID027590 Rev 4

- Pull-down resistors are designed with a true resistance in series with a switchable NMOS. This NMOS contribution to the series resistance is minimum (~10% order).

- 8. Hysteresis voltage between Schmitt trigger switching levels. Guaranteed by characterization results.

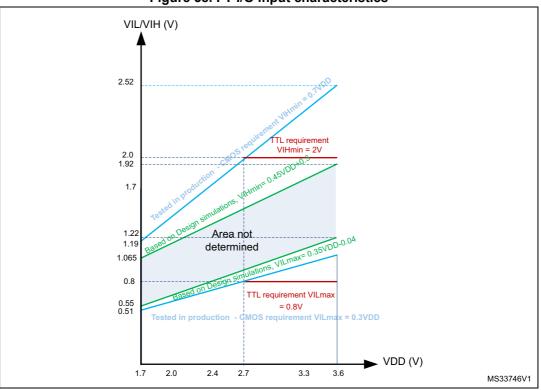

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements for FT I/Os is shown in *Figure 38*.

Figure 38. FT I/O input characteristics

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14, PC15 and PI8 which can sink or source up to  $\pm 3$ mA. When using the PC13 to PC15 and PI8 GPIOs in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*. In particular:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 15*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 15*).

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                  | Parameter                                                               | Conditions                                      | Min | Тур | Мах                | Unit |  |

|-----------------------------------------------|-------------------------|-------------------------------------------------------------------------|-------------------------------------------------|-----|-----|--------------------|------|--|

|                                               |                         | Maximum frequency <sup>(3)</sup>                                        | $C_L = 30 \text{ pF}, V_{DD} \ge 2.7 \text{ V}$ | -   | -   | 100 <sup>(4)</sup> |      |  |

|                                               |                         |                                                                         | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 50                 |      |  |

|                                               | f                       |                                                                         | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 42.5               | MHz  |  |

|                                               | t <sub>max(IO)out</sub> |                                                                         | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 180 <sup>(4)</sup> |      |  |

|                                               |                         |                                                                         | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.8 V | -   | -   | 100                |      |  |

| 11                                            |                         |                                                                         | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 1.7 V | -   | -   | 72.5               |      |  |

| 11                                            |                         |                                                                         | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 4                  |      |  |

|                                               |                         |                                                                         | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.8 V  | -   | -   | 6                  |      |  |

|                                               | t <sub>f(IO)out</sub> / |                                                                         | C <sub>L</sub> = 30 pF, V <sub>DD</sub> ≥1.7 V  | -   | -   | 7                  | ns   |  |

|                                               | t <sub>r(IO)out</sub>   |                                                                         | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥ 2.7 V | -   | -   | 2.5                |      |  |

|                                               |                         |                                                                         | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.8 V  | -   | -   | 3.5                |      |  |

|                                               |                         |                                                                         | C <sub>L</sub> = 10 pF, V <sub>DD</sub> ≥1.7 V  | -   | -   | 4                  |      |  |

| -                                             | tEXTIpw                 | Pulse width of external signals<br>detected by the EXTI -<br>controller |                                                 | 10  | -   | -                  | ns   |  |

| Table 58. I/O AC characteristics <sup>(1)(2)</sup> | (continued) |

|----------------------------------------------------|-------------|

|----------------------------------------------------|-------------|

1. Guaranteed by design.

2. The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F75xxx and STM32F74xxx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

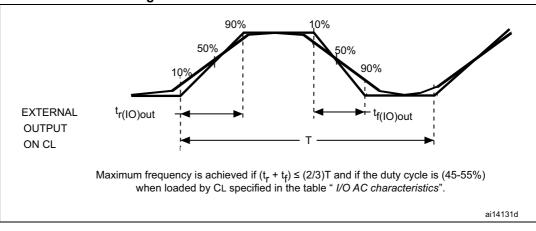

3. The maximum frequency is defined in *Figure 39*.

4. For maximum frequencies above 50 MHz and  $V_{DD}$  > 2.4 V, the compensation cell should be used.

#### Figure 39. I/O AC characteristics definition

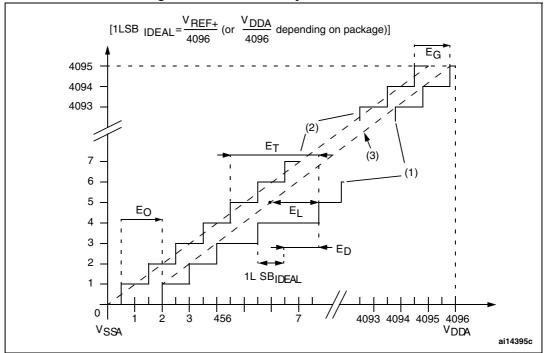

Figure 41. ADC accuracy characteristics

- 1. See also Table 64.

- 2. Example of an actual transfer curve.

- 3. Ideal transfer curve.

- 4 End point correlation line.

$E_T$  = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. 5.

EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

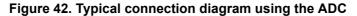

- 1. Refer to Table 62 for the values of RAIN, RADC and CADC.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

| Symbol                      | Parameter                                                 | Min                      | Max | Unit |

|-----------------------------|-----------------------------------------------------------|--------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FMC_CLK period                                            | 2T <sub>HCLK</sub> -0.5  | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)                         | -                        | 1.5 |      |

| t <sub>d(CLKH-NExH)</sub>   | FMC_CLK high to FMC_NEx high (x= 02)                      | T <sub>HCLK</sub> +0.5   | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low                               | -                        | 1.5 |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high                              | 0                        | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)                      | -                        | 2   |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625) T <sub>HCLK</sub> |                          | -   |      |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low -                              |                          | 1.5 |      |

| t <sub>(CLKH-NWEH)</sub>    | FMC_CLK high to FMC_NWE high                              | T <sub>HCLK</sub> -0.5   | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FMC_CLK low to FMC_AD[15:0] valid                         | - 3                      |     |      |

| t <sub>d(CLKL-ADIV)</sub>   | FMC_CLK low to FMC_AD[15:0] invalid                       | 0                        | -   |      |

| t <sub>d(CLKL-DATA)</sub>   | FMC_A/D[15:0] valid data after FMC_CLK low                | -                        | 3.5 |      |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low                                | 1                        | -   |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high                              | T <sub>HCLK</sub> +0.5 - |     | ]    |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high                       | 2                        | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high                        | 3.5                      | -   |      |

Table 97. Synchronous multiplexed PSRAM write timings<sup>(1)</sup>

1. Guaranteed by characterization results.

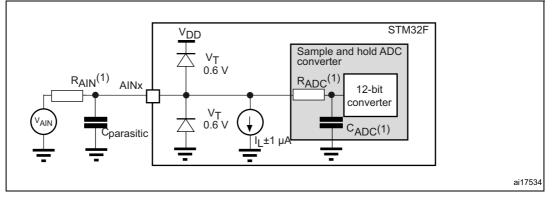

|        |        |             | data   |        |                       |        |

|--------|--------|-------------|--------|--------|-----------------------|--------|

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |

| Symbol | Min    | Тур         | Max    | Min    | Тур                   | Мах    |

| А      | -      | -           | 1.600  | -      | -                     | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |

| D      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

| D3     | -      | 12.000      | -      | -      | 0.4724                | -      |

| Е      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

| E3     | -      | 12.000      | -      | -      | 0.4724                | -      |

| е      | -      | 0.500       | -      | -      | 0.0197                | -      |

| L      | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236                | 0.0295 |

| L1     | -      | 1.000       | -      | -      | 0.0394                | -      |

| k      | 0°     | 3.5°        | 7°     | 0°     | 3.5°                  | 7°     |

| CCC    | -      | -           | 0.080  | -      | -                     | 0.0031 |

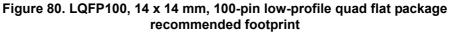

| Table 112. LQPF100, | 14 x 14 mm | 100-pin low-profile | quad flat package mechanical |

|---------------------|------------|---------------------|------------------------------|

|                     |            | data                |                              |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

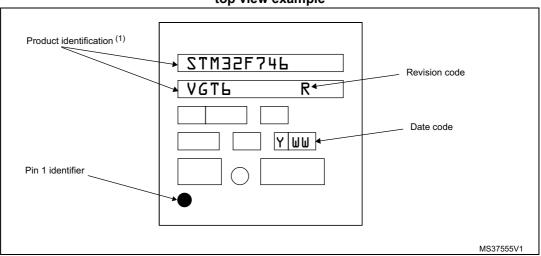

#### Marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Figure 81. LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package top view example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

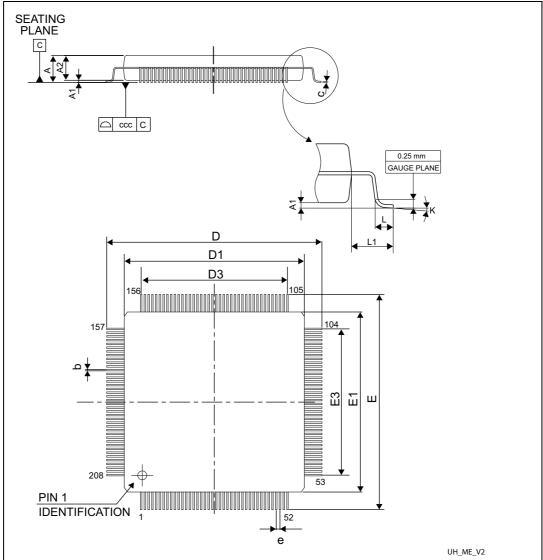

# 6.6 LQFP208, 28 x 28 mm low-profile quad flat package information

Figure 94. LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Table 119. LQFP208, 2 | 28 x 28 mm, 208-pin low-profile quad flat package |

|-----------------------|---------------------------------------------------|

|                       | mechanical data                                   |

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|-------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Мах   | Min    | Тур                   | Max    |

| A      | -     | -           | 1.600 |        | -                     | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |

DocID027590 Rev 4

| Dut         | <b>D</b> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 10-Dec-2015 | 3        | Updated <i>Table 10: STM32F745xx and STM32F746xx pin and ball</i><br><i>definition</i> additional functions column: WKUP1, 2, 3, 4, 5, 6 must be<br>respectively PA0, PA2, PC1, PC13, PI8, PI11.<br>Updated <i>Table 62: ADC characteristics</i> adding V <sub>REF-</sub> negative voltage<br>reference.<br>Update <i>Table 14: Voltage characteristics</i> adding table note 3.<br>Updated <i>Table 69: Temperature sensor calibration values</i> memory<br>addresses.<br>Updated <i>Table 72: Internal reference voltage calibration values</i><br>memory addresses.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 18-Feb-2016 | 4        | <ul> <li>Updated Table 52: EMI characteristics modifying 25/180 MHz by 25/200 MHz.</li> <li>Updated Figure 13: STM32F74xZx WLCSP143 ballout.</li> <li>Added TFBGA100 8 x 8 mm package: <ul> <li>Updated Cover page.</li> <li>Updated Section 1: Description.</li> <li>Updated Table 2: STM32F745xx and STM32F746xx features and peripheral counts.</li> <li>Updated Table 4: Regulator ON/OFF and internal reset ON/OFF availability.</li> <li>Updated Section 3: Pinouts and pin description adding Figure 12: STM32F74xVx TFBGA100 ballout and adding TFBGA100 ball description in Table 10: STM32F745xx and STM32F746xx pin and ball definition.</li> <li>Updated Table 53: ESD absolute maximum ratings.</li> <li>Updated Table 53: ESD absolute maximum ratings.</li> <li>Updated Section 6: Package information adding TFBGA100 package information and adding thermal resistance in Table 124: Package thermal characteristics.</li> <li>Updated Table 10: STM32F745xx and STM32F746xx pin and ball definition note 5.</li> <li>Updated Table 10: STM32F745xx and STM32F746xx pin and ball definition note 5.</li> <li>Updated Table 10: STM32F745xx and STM32F746xx pin and ball definition note 5.</li> <li>Updated Table 10: STM32F745xx and STM32F746xx pin and ball definition note 5.</li> </ul> </li> </ul> |