# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | -                                                                        |

| Core Size                  | -                                                                        |

| Speed                      | -                                                                        |

| Connectivity               | -                                                                        |

| Peripherals                | -                                                                        |

| Number of I/O              | -                                                                        |

| Program Memory Size        | -                                                                        |

| Program Memory Type        | -                                                                        |

| EEPROM Size                | -                                                                        |

| RAM Size                   | -                                                                        |

| Voltage - Supply (Vcc/Vdd) | -                                                                        |

| Data Converters            | -                                                                        |

| Oscillator Type            | -                                                                        |

| Operating Temperature      | -                                                                        |

| Mounting Type              | -                                                                        |

| Package / Case             | -                                                                        |

| Supplier Device Package    | -                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc908gr4cfae |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

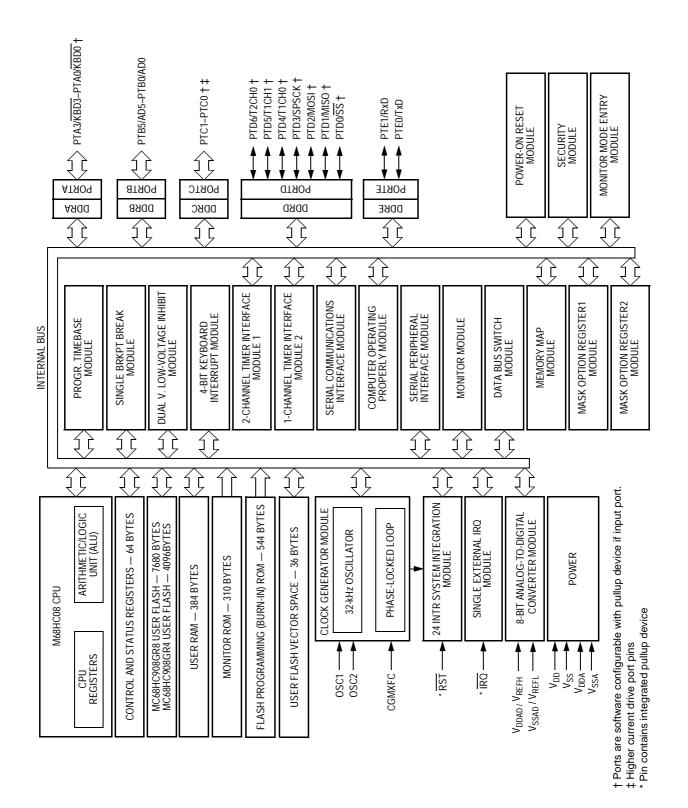

General Description MCU Block Diagram

#### Figure 1-1. MCU Block Diagram

MOTOROLA

General Description

#### 3.7.2 Stop Mode

Stop mode turns off the CGMXCLK input to the COP and clears the COP prescaler. Service the COP immediately before entering or after exiting stop mode to ensure a full COP timeout period after entering or exiting stop mode.

The STOP bit in the configuration register (CONFIG) enables the STOP instruction. To prevent inadvertently turning off the COP with a STOP instruction, disable the STOP instruction by clearing the STOP bit.

# 3.8 External Interrupt Module (IRQ)

#### 3.8.1 Wait Mode

The IRQ module remains active in wait mode. Clearing the IMASK1 bit in the IRQ status and control register enables IRQ CPU interrupt requests to bring the MCU out of wait mode.

#### 3.8.2 Stop Mode

The IRQ module remains active in stop mode. Clearing the IMASK1 bit in the IRQ status and control register enables IRQ CPU interrupt requests to bring the MCU out of stop mode.

# 3.9 Keyboard Interrupt Module (KBI)

#### 3.9.1 Wait Mode

The keyboard module remains active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

MC68HC908GR8 — Rev 4.0

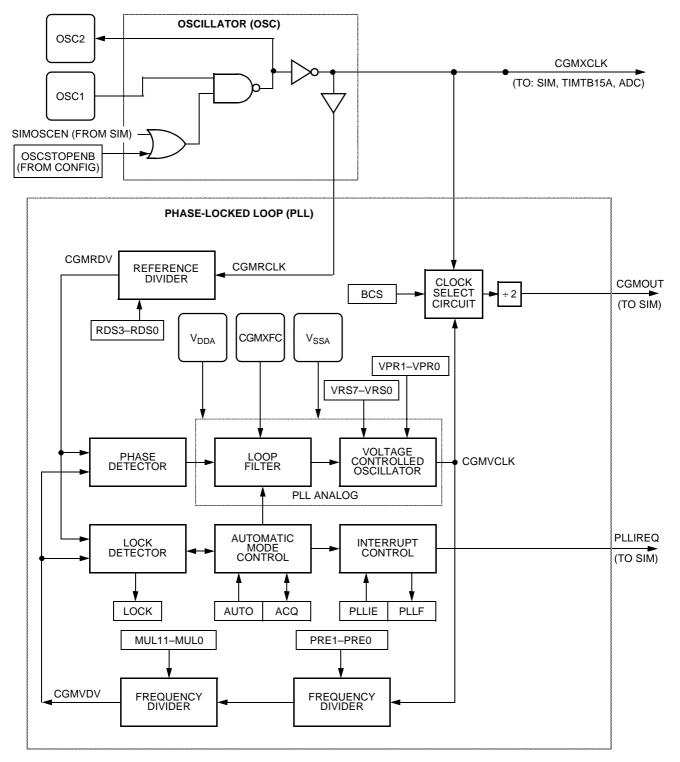

# Section 7. Clock Generator Module (CGMC)

## 7.1 Contents

| 7.2 | Introduction                         |

|-----|--------------------------------------|

| 7.3 | Features                             |

| 7.4 | Functional Description100            |

| 7.5 | I/O Signals                          |

| 7.6 | CGMC Registers                       |

| 7.7 | Interrupts                           |

| 7.8 | Special Modes                        |

| 7.9 | Acquisition/Lock Time Specifications |

## 7.2 Introduction

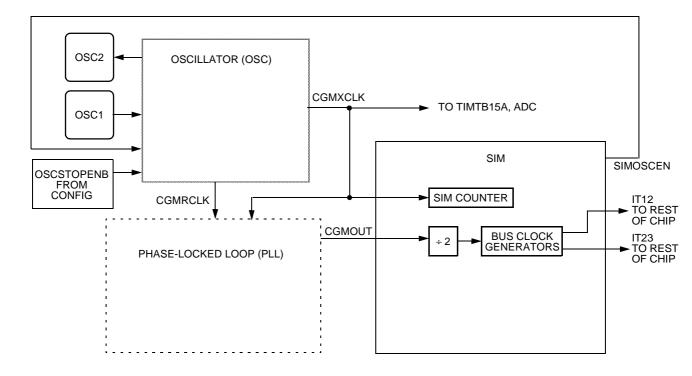

This section describes the clock generator module. The CGMC generates the crystal clock signal, CGMXCLK, which operates at the frequency of the crystal. The CGMC also generates the base clock signal, CGMOUT, which is based on either the crystal clock divided by two or the phase-locked loop (PLL) clock, CGMVCLK, divided by two. In user mode, CGMOUT is the clock from which the SIM derives the system clocks, including the bus clock, which is at a frequency of CGMOUT/2. In monitor mode, PTC3 determines the bus clock. The PLL is a fully functional frequency generator designed for use with crystals or ceramic resonators. The PLL can generate an 8-MHz bus frequency using a 32-kHz crystal.

MOTOROLA

MOTOROLA

Technical Data

101

is set, and BCS cannot be set when PLLON is clear. If the PLL is off (PLLON = 0), selecting CGMVCLK requires two writes to the PLL control register. (See Base Clock Selector Circuit.)

PRE1 and PRE0 — Prescaler Program Bits

These read/write bits control a prescaler that selects the prescaler power-of-two multiplier, P. (See PLL Circuits and Programming the PLL.) PRE1 and PRE0 cannot be written when the PLLON bit is set. Reset clears these bits.

**NOTE:** The value of P is normally 0 when using a 32.768-kHz crystal as the reference.

| PRE1 and PRE0 | Р | Prescaler Multiplier |

|---------------|---|----------------------|

| 00            | 0 | 1                    |

| 01            | 1 | 2                    |

| 10            | 2 | 4                    |

| 11            | 3 | 8                    |

Table 7-2. PRE 1 and PRE0 Programming

VPR1 and 0 — VCO Power-of-Two Range Select Bits

These read/write bits control the VCO's hardware power-of-two range multiplier E that, in conjunction with L (See PLL Circuits, Programming the PLL, and PLL VCO Range Select Register.) controls the hardware center-of-range frequency, f<sub>VRS</sub>. VPR1:VPR0 cannot be written when the PLLON bit is set. Reset clears these bits.

Table 7-3. VPR1 and VPR0 Programming

| VPR1 and VPR0 | E                | VCO Power-of-Two<br>Range Multiplier |

|---------------|------------------|--------------------------------------|

| 00            | 0                | 1                                    |

| 01            | 1                | 2                                    |

| 10            | 2                | 4                                    |

| 11            | 3 <sup>(1)</sup> | 8                                    |

1. Do not program E to a value of 3.

MC68HC908GR8 — Rev 4.0

MOTOROLA

# **Clock Generator Module (CGMC)**

**NOTE:** The multiplier select bits have built-in protection such that they cannot be written when the PLL is on (PLLON = 1).

PMSH[7:4] — Unimplemented Bits

These bits have no function and always read as logic 0s.

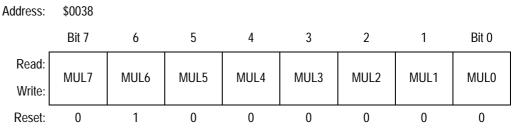

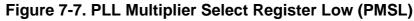

#### 7.6.4 PLL Multiplier Select Register Low

The PLL multiplier select register low (PMSL) contains the programming information for the low byte of the modulo feedback divider.

#### MUL7-MUL0 — Multiplier Select Bits

These read/write bits control the low byte of the modulo feedback divider that selects the VCO frequency multiplier, N. (See PLL Circuits and Programming the PLL.) MUL7–MUL0 cannot be written when the PLLON bit in the PCTL is set. A value of \$0000 in the multiplier select registers configures the modulo feedback divider the same as a value of \$0001. Reset initializes the register to \$40 for a default multiply value of 64.

**NOTE:** The multiplier select bits have built-in protection such that they cannot be written when the PLL is on (PLLON = 1).

#### 15.4.4 Baud Rate

The communication baud rate is controlled by the crystal frequency upon entry into monitor mode. The divide by ratio is 1024.

If monitor mode was entered with  $V_{DD}$  on  $\overline{IRQ}$ , then the divide by ratio is also set at 1024. If monitor mode was entered with  $V_{SS}$  on  $\overline{IRQ}$ , then the internal PLL steps up the external frequency, presumed to be 32.768 kHz, to 2.4576 MHz. These latter two conditions for monitor mode entry require that the reset vector is blank.

Table 15-3 lists external frequencies required to achieve a standard baud rate of 9600 BPS. Other standard baud rates can be accomplished using proportionally higher or lower frequency generators. If using a crystal as the clock source, be aware of the upper frequency limit that the internal clock module can handle. See 5.0 V Control Timing and 3.0 V Control Timing for this limit.

| Table 15-3 | . Monitor | Baud | Rate | Selection |

|------------|-----------|------|------|-----------|

|------------|-----------|------|------|-----------|

| External<br>Frequency | IRQ              | Internal<br>Frequency | Baud Rate<br>(BPS) |

|-----------------------|------------------|-----------------------|--------------------|

| 9.8304 MHz            | V <sub>TST</sub> | 2.4576 MHz            | 9600               |

| 9.8304 MHz            | V <sub>DD</sub>  | 2.4576 MHz            | 9600               |

| 32.768 kHz            | $V_{SS}$         | 2.4576 MHz            | 9600               |

#### 15.4.5 Commands

The monitor ROM firmware uses these commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

# Input/Output Ports (I/O)

#### 16.5 Port C

Port C is a 2-bit, general-purpose bidirectional I/O port. Port C also has software configurable pullup devices if configured as an input port.

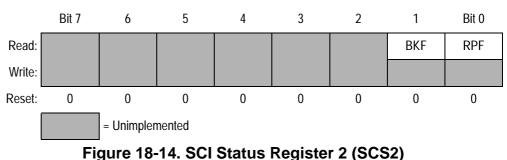

#### 16.5.1 Port C Data Register

The port C data register (PTC) contains a data latch for each of the two port C pins.

PTC1-PTC0 - Port C Data Bits

These read/write bits are software-programmable. Data direction of each port C pin is under the control of the corresponding bit in data direction register C. Reset has no effect on port C data.

NOTE: PTC is not available in a 28-pin DIP and SOIC package

MC68HC908GR8 - Rev 4.0

216

## Serial Communications Interface (SCI)

tolerance is much more than the degree of misalignment that is likely to occur.

As the receiver samples an incoming character, it resynchronizes the RT clock on any valid falling edge within the character. Resynchronization within characters corrects misalignments between transmitter bit times and receiver bit times.

#### 18.5.3.6 Slow Data Tolerance

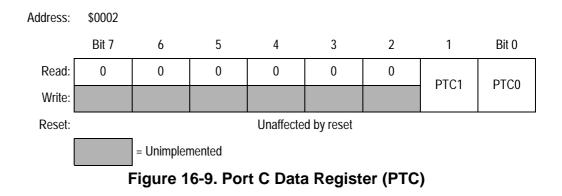

Figure 18-7 shows how much a slow received character can be misaligned without causing a noise error or a framing error. The slow stop bit begins at RT8 instead of RT1 but arrives in time for the stop bit data samples at RT8, RT9, and RT10.

Figure 18-7. Slow Data

For an 8-bit character, data sampling of the stop bit takes the receiver 9 bit times  $\times$  16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 18-7, the receiver counts 154 RT cycles at the point when the count of the transmitting device is 9 bit times  $\times$  16 RT cycles + 3 RT cycles = 147 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a slow 8-bit character with no errors is

$$\left|\frac{154 - 147}{154}\right| \times 100 = 4.54\%$$

For a 9-bit character, data sampling of the stop bit takes the receiver 10 bit times  $\times$  16 RT cycles + 10 RT cycles = 170 RT cycles.

Technical Data

MC68HC908GR8 — Rev 4.0

## Serial Communications Interface (SCI)

- 1 = 9-bit SCI characters

- 0 = 8-bit SCI characters

- WAKE Wakeup Condition Bit

This read/write bit determines which condition wakes up the SCI: a logic 1 (address mark) in the most significant bit position of a received character or an idle condition on the PE1/RxD pin. Reset clears the WAKE bit.

1 = Address mark wakeup

0 = Idle line wakeup

ILTY — Idle Line Type Bit

This read/write bit determines when the SCI starts counting logic 1s as idle character bits. The counting begins either after the start bit or after the stop bit. If the count begins after the start bit, then a string of logic 1s preceding the stop bit may cause false recognition of an idle character. Beginning the count after the stop bit avoids false idle character recognition, but requires properly synchronized transmissions. Reset clears the ILTY bit.

- 1 = Idle character bit count begins after stop bit

- 0 = Idle character bit count begins after start bit

- PEN Parity Enable Bit

This read/write bit enables the SCI parity function. See Table 18-5. When enabled, the parity function inserts a parity bit in the most significant bit position. See Figure 18-3. Reset clears the PEN bit.

- 1 = Parity function enabled

- 0 = Parity function disabled

PTY - Parity Bit

This read/write bit determines whether the SCI generates and checks for odd parity or even parity. See Table 18-5. Reset clears the PTY bit.

- 1 = Odd parity

- 0 = Even parity

Technical Data

# Serial Communications Interface (SCI)

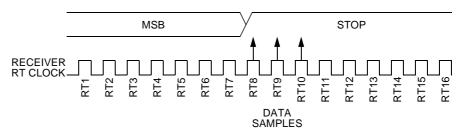

#### 18.9.5 SCI Status Register 2

SCI status register 2 contains flags to signal the following conditions:

- Break character detected

- Incoming data

Address: \$0017

BKF — Break Flag Bit

This clearable, read-only bit is set when the SCI detects a break character on the PE1/RxD pin. In SCS1, the FE and SCRF bits are also set. In 9-bit character transmissions, the R8 bit in SCC3 is cleared. BKF does not generate a CPU interrupt request. Clear BKF by reading SCS2 with BKF set and then reading the SCDR. Once cleared, BKF can become set again only after logic 1s again appear on the PE1/RxD pin followed by another break character. Reset clears the BKF bit.

- 1 = Break character detected

- 0 = No break character detected

RPF — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a logic 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch) or when the receiver detects an idle character. Polling RPF before disabling the SCI module or entering stop mode can show whether a reception is in progress.

1 = Reception in progress

0 = No reception in progress

Technical Data

MC68HC908GR8 — Rev 4.0

# **19.3 SIM Bus Clock Control and Generation**

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, CGMOUT, as shown in Figure 19-3. This clock can come from either an external oscillator or from the on-chip PLL. See Clock Generator Module (CGMC).

## 19.3.1 Bus Timing

In user mode, the internal bus frequency is either the crystal oscillator output (CGMXCLK) divided by four or the PLL output (CGMVCLK) divided by four. See External Interrupt (IRQ).

MC68HC908GR8 — Rev 4.0

Timebase Module (TBM)

Technical Data

MC68HC908GR8 — Rev 4.0

# **Timer Interface Module (TIM)**

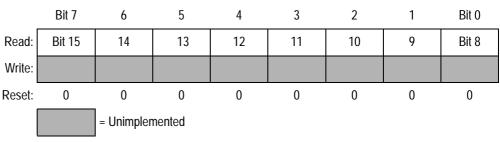

#### 22.10.2 TIM Counter Registers

The two read-only TIM counter registers contain the high and low bytes of the value in the TIM counter. Reading the high byte (TCNTH) latches the contents of the low byte (TCNTL) into a buffer. Subsequent reads of TCNTH do not affect the latched TCNTL value until TCNTL is read. Reset clears the TIM counter registers. Setting the TIM reset bit (TRST) also clears the TIM counter registers.

**NOTE:** If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL retains the value latched during the break.

Address: T1CNTH, \$0021 and T2CNTH, \$002C

Address: T1CNTL, \$0022 and T2CNTL, \$002D

|        | Bit 7      | 6          | 5      | 4 | 3 | 2 | 1 | Bit 0 |

|--------|------------|------------|--------|---|---|---|---|-------|

| Read:  | Bit 7      | 6          | 5      | 4 | 3 | 2 | 1 | Bit 0 |

| Write: |            |            |        |   |   |   |   |       |

| Reset: | 0          | 0          | 0      | 0 | 0 | 0 | 0 | 0     |

|        |            | = Unimpler | nented |   |   |   |   |       |

|        | <b>F</b> : |            |        |   |   |   |   |       |

Technical Data

# **Electrical Specifications**

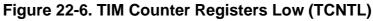

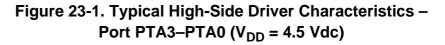

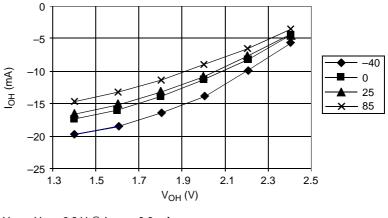

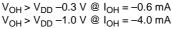

# 23.9 Output High-Voltage Characteristics

Semiconductor, Inc.

Freescale

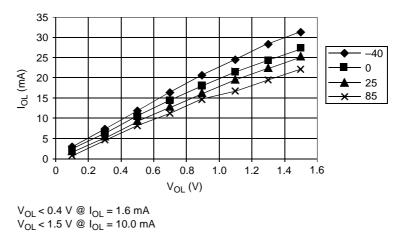

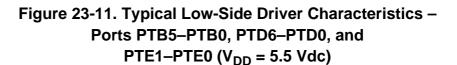

Electrical Specifications Output Low-Voltage Characteristics

$V_{OL} < 0.3 V @ I_{OL} = 0.5 mA$  $V_{OL} < 1.0 V @ I_{OL} = 6.0 mA$

Figure 23-12. Typical Low-Side Driver Characteristics – Ports PTB5–PTB0, PTD6–PTD0, and PTE1–PTE0 (V<sub>DD</sub> = 2.7 Vdc)

# **Electrical Specifications**

## 23.14 3.0 V SPI Characteristics

| Diagram<br>Number <sup>(1)</sup> | Characteristic <sup>(2)</sup>                                        | Symbol                                       | Min                                              | Мах                                   | Unit                                 |

|----------------------------------|----------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------|---------------------------------------|--------------------------------------|

|                                  | Operating frequency<br>Master<br>Slave                               | f <sub>OP(M)</sub><br>f <sub>OP(S)</sub>     | f <sub>OP</sub> /128<br>DC                       | f <sub>OP</sub> /2<br>f <sub>OP</sub> | MHz<br>MHz                           |

| 1                                | Cycle time<br>Master<br>Slave                                        | t <sub>CYC(M)</sub><br>t <sub>CYC(S)</sub>   | 2<br>1                                           | 128<br>—                              | t <sub>cyc</sub><br>t <sub>cyc</sub> |

| 2                                | Enable lead time                                                     | t <sub>Lead(s)</sub>                         | 1                                                | _                                     | t <sub>cyc</sub>                     |

| 3                                | Enable lag time                                                      | t <sub>Lag(s)</sub>                          | 1                                                |                                       | t <sub>cyc</sub>                     |

| 4                                | Clock (SPSCK) high time<br>Master<br>Slave                           | t <sub>SCKH(M)</sub><br>t <sub>SCKH(S)</sub> | t <sub>cyc</sub> –35<br>1/2 t <sub>cyc</sub> –35 | 64 t <sub>cyc</sub>                   | ns<br>ns                             |

| 5                                | Clock (SPSCK) low time<br>Master<br>Slave                            | t <sub>SCKL(M)</sub><br>t <sub>SCKL(S)</sub> | t <sub>cyc</sub> –35<br>1/2 t <sub>cyc</sub> –35 | ±<br>64 t <sub>cyc</sub>              | ns<br>ns                             |

| 6                                | Data setup time (inputs)<br>Master<br>Slave                          | t <sub>SU(M)</sub><br>t <sub>SU(S)</sub>     | 40<br>40                                         |                                       | ns<br>ns                             |

| 7                                | Data hold time (inputs)<br>Master<br>Slave                           | t <sub>H(M)</sub><br>t <sub>H(S)</sub>       | 40<br>40                                         |                                       | ns<br>ns                             |

| 8                                | Access time, slave <sup>(3)</sup><br>CPHA = 0<br>CPHA = 1            | t <sub>A(CP0)</sub><br>t <sub>A(CP1)</sub>   | 0<br>0                                           | 50<br>50                              | ns<br>ns                             |

| 9                                | Disable time, slave <sup>(4)</sup>                                   | t <sub>DIS(S)</sub>                          | _                                                | 50                                    | ns                                   |

| 10                               | Data valid time, after enable edge<br>Master<br>Slave <sup>(5)</sup> | t <sub>V(M)</sub><br>t <sub>V(S)</sub>       |                                                  | 60<br>60                              | ns<br>ns                             |

| 11                               | Data hold time, outputs, after enable edge<br>Master<br>Slave        | t <sub>HO(M)</sub><br>t <sub>HO(S)</sub>     | 0<br>0                                           |                                       | ns<br>ns                             |

Notes:

Semiconductor, Inc.

Freescale

1. Numbers refer to dimensions in Figure 23-16 and Figure 23-17.

2. All timing is shown with respect to 20%  $V_{DD}$  and 70%  $V_{DD},$  unless noted; 100 pF load on all SPI pins.

3. Time to data active from high-impedance state

4. Hold time to high-impedance state

5. With 100 pF on all SPI pins

- serial communications interface module (SCI) A module in the M68HC08 Family that supports asynchronous communication.

- serial peripheral interface module (SPI) A module in the M68HC08 Family that supports synchronous communication.

- set To change a bit from logic 0 to logic 1; opposite of clear.

- shift register A chain of circuits that can retain the logic levels (logic 1 or logic 0) written to them and that can shift the logic levels to the right or left through adjacent circuits in the chain.

- signed A binary number notation that accommodates both positive and negative numbers. The most significant bit is used to indicate whether the number is positive or negative, normally logic 0 for positive and logic 1 for negative. The other seven bits indicate the magnitude of the number.

- software Instructions and data that control the operation of a microcontroller.

- **software interrupt (SWI)** An instruction that causes an interrupt and its associated vector fetch.

- SPI See "serial peripheral interface module (SPI)."

- **stack** A portion of RAM reserved for storage of CPU register contents and subroutine return addresses.

- stack pointer (SP) A 16-bit register in the CPU08 containing the address of the next available storage location on the stack.

- start bit A bit that signals the beginning of an asynchronous serial transmission.

- status bit A register bit that indicates the condition of a device.

- stop bit A bit that signals the end of an asynchronous serial transmission.

- subroutine A sequence of instructions to be used more than once in the course of a program. The last instruction in a subroutine is a return from subroutine (RTS) instruction. At each place in the main program where the subroutine instructions are needed, a jump or branch to subroutine (JSR or BSR) instruction is used to call the subroutine. The CPU leaves the flow of the main program to execute the instructions in the subroutine. When the RTS instruction is executed, the CPU returns to the main program where it left off.

- **synchronous** Refers to logic circuits and operations that are synchronized by a common reference signal.

- TIM See "timer interface module (TIM)."

MC68HC908GR8 — Rev 4.0

#### Glossary

- timer interface module (TIM) A module used to relate events in a system to a point in time.

- timer A module used to relate events in a system to a point in time.

- toggle To change the state of an output from a logic 0 to a logic 1 or from a logic 1 to a logic 0.

- tracking mode Mode of low-jitter PLL operation during which the PLL is locked on a frequency. Also see "acquisition mode."

- two's complement A means of performing binary subtraction using addition techniques. The most significant bit of a two's complement number indicates the sign of the number (1 indicates negative). The two's complement negative of a number is obtained by inverting each bit in the number and then adding 1 to the result.

- **unbuffered** Utilizes only one register for data; new data overwrites current data.

- unimplemented memory location A memory location that is not used. Writing to an unimplemented location has no effect. Reading an unimplemented location returns an unpredictable value. Executing an opcode at an unimplemented location causes an illegal address reset.

- V The overflow bit in the condition code register of the CPU08. The CPU08 sets the V bit when a two's complement overflow occurs. The signed branch instructions BGT, BGE, BLE, and BLT use the overflow bit.

- **variable** A value that changes during the course of program execution.

- VCO See "voltage-controlled oscillator."

- **vector** A memory location that contains the address of the beginning of a subroutine written to service an interrupt or reset.

- **voltage-controlled oscillator (VCO)** A circuit that produces an oscillating output signal of a frequency that is controlled by a dc voltage applied to a control input.

- waveform A graphical representation in which the amplitude of a wave is plotted against time.

- **wired-OR** Connection of circuit outputs so that if any output is high, the connection point is high.

- **word** A set of two bytes (16 bits).

- write The transfer of a byte of data from the CPU to a memory location.

- X The lower byte of the index register (H:X) in the CPU08.

- Z The zero bit in the condition code register of the CPU08. The CPU08 sets the zero bit when an arithmetic operation, logical operation, or data manipulation produces a result of \$00.

Technical Data

MC68HC908GR8 — Rev 4.0

# Technical Data — MC68HC908GR8

# **Revision History**

## Contents

| Introduction                                                                         |

|--------------------------------------------------------------------------------------|

| Changes from Rev 3.0 published in February 2002 to Rev 4.0 published in June 2002    |

| Changes from Rev 2.0 published in January 2002 to Rev 3.0 published in February 2002 |

| Changes from Rev 1.0 published in April 2001 to Rev 2.0 published in December 2001   |

# Introduction

This section contains the revision history for the MC68HC908GR8 technical data book.

# Changes from Rev 3.0 published in February 2002 to Rev 4.0 published in June 2002

| Section                 | Page (in Rev 3.0)                                                  | Description of change                                                                                                          |  |  |  |

|-------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| All references to the F | All references to the ROM MC68HC08GR8 removed. Appendix A removed. |                                                                                                                                |  |  |  |

|                         | 363                                                                | Maximum junction temperature increased to 140°C                                                                                |  |  |  |

| Electrical              | 364                                                                | Input High Voltage for OSC1 changed<br>Stop I <sub>DD</sub> for temperatures >85°C added                                       |  |  |  |

| Specifications          | 366                                                                | Input High Voltage for OSC1 changed<br>Input Low Voltage for OSC1 changed<br>Stop I <sub>DD</sub> for temperatures >85°C added |  |  |  |

MOTOROLA

**Technical Data**

Semiconductor, Inc.