Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                       |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | HC08                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 8MHz                                                         |

| Connectivity               | SCI, SPI                                                     |

| Peripherals                | LVD, POR, PWM                                                |

| Number of I/O              | 17                                                           |

| Program Memory Size        | 7.5KB (7.5K x 8)                                             |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 384 x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                  |

| Data Converters            | A/D 6x8b                                                     |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                               |

| Supplier Device Package    | 28-SOIC                                                      |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68hc908gr8cdw |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Memory Map Input/Output (I/O) Section

| Addr.  | Register Name                           |                                             | Bit 7                      | 6     | 5     | 4         | 3          | 2     | 1     | Bit 0 |  |

|--------|-----------------------------------------|---------------------------------------------|----------------------------|-------|-------|-----------|------------|-------|-------|-------|--|

|        |                                         | Read:                                       | 0                          | 0     | 0     | 0         |            |       |       |       |  |

| \$0000 | Port A Data Register<br>(PTA)           | Write:                                      |                            |       |       |           | PTA3       | PTA2  | PTA1  | PTA0  |  |

|        | (177)                                   | Reset:                                      | Reset: Unaffected by reset |       |       |           |            |       |       |       |  |

|        |                                         | Read:                                       | 0                          | 0     | DTDE  |           | רחדם       | רחדם  |       |       |  |

| \$0001 | Port B Data Register<br>(PTB)           | Write:                                      |                            |       | PTB5  | PTB4      | PTB3       | PTB2  | PTB1  | PTB0  |  |

|        | (110)                                   | Reset:                                      |                            |       | •     | Unaffecte | d by reset |       |       |       |  |

|        |                                         | Read:                                       | 0                          | 0     | 0     | 0         | 0          | 0     | DTC1  | DTCO  |  |

| \$0002 | Port C Data Register<br>(PTC)           | Write:                                      |                            |       |       |           |            |       | PTC1  | PTC0  |  |

|        | (110)                                   | Reset:                                      |                            |       | •     | Unaffecte | d by reset |       |       |       |  |

|        |                                         | Read:                                       | 0                          | PTD6  | PTD5  | PTD4      | PTD3       | PTD2  | PTD1  |       |  |

| \$0003 | Port D Data Register<br>(PTD)           | Write:                                      |                            | PIDO  | PID5  | PID4      | PID3       | PIDZ  | PIDI  | PTD0  |  |

|        | ( )                                     | Reset:                                      |                            |       |       | Unaffecte | d by reset |       |       |       |  |

|        |                                         | Read:                                       | 0                          | 0     | 0     | 0         | DDRA3      | DDRA2 | DDRA1 | DDRA0 |  |

| \$0004 | Data Direction Register A<br>(DDRA)     | Write:                                      |                            |       |       |           | DDKA3      | DDRAZ |       | DDRAU |  |

|        |                                         | Reset:                                      | 0                          | 0     | 0     | 0         | 0          | 0     | 0     | 0     |  |

|        |                                         | Read:                                       | 0                          | 0     | DDRB5 | DDRB4     | DDRB3      | DDRB2 | DDRB1 | DDRB0 |  |

| \$0005 | Data Direction Register B<br>(DDRB)     | Write:                                      |                            |       | DDRDJ | DDKD4     | υυκός      | DDRDZ |       | DDRBU |  |

|        | (2212)                                  | Reset:                                      | 0                          | 0     | 0     | 0         | 0          | 0     | 0     | 0     |  |

|        |                                         | Read:                                       | 0                          | 0     | 0     | 0         | 0          | 0     |       | DDRC0 |  |

| \$0006 | Data Direction Register C<br>(DDRC)     | Write:                                      |                            |       |       |           |            | DDRC1 |       | DDRCU |  |

|        | (221.0)                                 | Reset:                                      | 0                          | 0     | 0     | 0         | 0          | 0     | 0     | 0     |  |

|        |                                         | Read:                                       | 0                          | DDRD6 | DDRD5 | DDRD4     | DDRD3      | DDRD2 | DDRD1 | חססח  |  |

| \$0007 | Data Direction Register D<br>(DDRD)     | Write:                                      |                            | DDRDU | DDRDJ | DDRD4     | DDKD3      | DDRDZ | DDRDT | DDRD0 |  |

|        | ( , , , , , , , , , , , , , , , , , , , | Reset:                                      | 0                          | 0     | 0     | 0         | 0          | 0     | 0     | 0     |  |

|        |                                         | Read:                                       | 0                          | 0     | 0     | 0         | 0          | 0     | PTE1  | PTE0  |  |

| \$0008 | Port E Data Register<br>(PTE)           | Write:                                      |                            |       |       |           |            |       |       | FILU  |  |

|        | (                                       | Reset:                                      |                            |       |       | Unaffecte | d by reset |       |       |       |  |

|        |                                         | Read:                                       |                            |       |       |           |            |       |       |       |  |

| \$0009 | Unimplemented                           | Write:                                      |                            |       |       |           |            |       |       |       |  |

|        |                                         | Reset:                                      | 0                          | 0     | 0     | 0         | 0          | 0     | 0     | 0     |  |

|        |                                         | = Unimplemented R = Reserved U = Unaffected |                            |       |       |           |            |       |       |       |  |

Figure 2-2. Control, Status, and Data Registers (Sheet 1 of 8)

MC68HC908GR8 — Rev 4.0

# **Section 4. Resets and Interrupts**

### 4.1 Contents

| 4.2 |            | 61 |

|-----|------------|----|

| 4.3 | Resets     | 61 |

| 4.4 | Interrupts | 66 |

### 4.2 Introduction

Resets and interrupts are responses to exceptional events during program execution. A reset re-initializes the MCU to its startup condition. An interrupt vectors the program counter to a service routine.

## 4.3 Resets

A reset immediately returns the MCU to a known startup condition and begins program execution from a user-defined memory location.

#### 4.3.1 Effects

A reset:

- Immediately stops the operation of the instruction being executed

- Initializes certain control and status bits

- Loads the program counter with a user-defined reset vector address from locations \$FFFE and \$FFFF

- Selects CGMXCLK divided by four as the bus clock

The operating range of the VCO is programmable for a wide range of frequencies and for maximum immunity to external noise, including supply and CGM/XFC noise. The VCO frequency is bound to a range from roughly one-half to twice the center-of-range frequency,  $f_{VRS}$ . Modulating the voltage on the CGM/XFC pin changes the frequency within this range. By design,  $f_{VRS}$  is equal to the nominal center-of-range frequency,  $f_{NOM}$ , (38.4 kHz) times a linear factor, L, and a power-of-two factor, E, or (L × 2<sup>E</sup>) $f_{NOM}$ .

CGMRCLK is the PLL reference clock, a buffered version of CGMXCLK. CGMRCLK runs at a frequency,  $f_{RCLK}$ , and is fed to the PLL through a programmable modulo reference divider, which divides  $f_{RCLK}$  by a factor, R. The divider's output is the final reference clock, CGMRDV, running at a frequency,  $f_{RDV} = f_{RCLK}/R$ . With an external crystal (30 kHz–100 kHz), always set R = 1 for specified performance. With an external high-frequency clock source, use R to divide the external frequency to between 30 kHz and 100 kHz.

The VCO's output clock, CGMVCLK, running at a frequency,  $f_{VCLK}$ , is fed back through a programmable prescale divider and a programmable modulo divider. The prescaler divides the VCO clock by a power-of-two factor P and the modulo divider reduces the VCO clock by a factor, N. The dividers' output is the VCO feedback clock, CGMVDV, running at a frequency,  $f_{VDV} = f_{VCLK}/(N \times 2^{P})$ . (See Programming the PLL for more information.)

The phase detector then compares the VCO feedback clock, CGMVDV, with the final reference clock, CGMRDV. A correction pulse is generated based on the phase difference between the two signals. The loop filter then slightly alters the DC voltage on the external capacitor connected to CGM/XFC based on the width and direction of the correction pulse. The filter can make fast or slow corrections depending on its mode, described in Acquisition and Tracking Modes. The value of the external capacitor and the reference frequency determine the speed of the corrections and the stability of the PLL.

The lock detector compares the frequencies of the VCO feedback clock, CGMVDV, and the final reference clock, CGMRDV. Therefore, the speed of the lock detector is directly proportional to the final reference

### **Clock Generator Module (CGMC)**

this table:

| Frequency Range                             | Е |

|---------------------------------------------|---|

| 0 < f <sub>VCLK</sub> < 9,830,400           | 0 |

| 9,830,400 ≤ f <sub>VCLK</sub> < 19,660,800  | 1 |

| 19,660,800 ≤ f <sub>VCLK</sub> < 39,321,600 | 2 |

NOTE: Do not program E to a value of 3.

8. Select a VCO linear range multiplier, L, where f<sub>NOM</sub> = 38.4 kHz

$$L = round \left(\frac{f_{VCLK}}{2^{E} \times f_{NOM}}\right)$$

Calculate and verify the adequacy of the VCO programmed center-of-range frequency, f<sub>VRS</sub>. The center-of-range frequency is the midpoint between the minimum and maximum frequencies attainable by the PLL.

$$f_{VRS} = (L \times 2^E) f_{NOM}$$

For proper operation,

$$|f_{VRS} - f_{VCLK}| \leq \frac{f_{NOM} \times 2^{E}}{2}$$

- 10. Verify the choice of P, R, N, E, and L by comparing  $f_{VCLK}$  to  $f_{VRS}$  and  $f_{VCLKDES}$ . For proper operation,  $f_{VCLK}$  must be within the application's tolerance of  $f_{VCLKDES}$ , and  $f_{VRS}$  must be as close as possible to  $f_{VCLK}$ .

- **NOTE:** Exceeding the recommended maximum bus frequency or VCO frequency can crash the MCU.

- 11. Program the PLL registers accordingly:

- a. In the PRE bits of the PLL control register (PCTL), program the binary equivalent of P.

- b. In the VPR bits of the PLL control register (PCTL), program the binary equivalent of E.

Technical Data

MC68HC908GR8 — Rev 4.0

## **Clock Generator Module (CGMC)**

**NOTE:** The multiplier select bits have built-in protection such that they cannot be written when the PLL is on (PLLON = 1).

PMSH[7:4] — Unimplemented Bits

These bits have no function and always read as logic 0s.

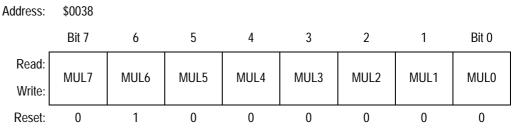

#### 7.6.4 PLL Multiplier Select Register Low

The PLL multiplier select register low (PMSL) contains the programming information for the low byte of the modulo feedback divider.

#### MUL7-MUL0 — Multiplier Select Bits

These read/write bits control the low byte of the modulo feedback divider that selects the VCO frequency multiplier, N. (See PLL Circuits and Programming the PLL.) MUL7–MUL0 cannot be written when the PLLON bit in the PCTL is set. A value of \$0000 in the multiplier select registers configures the modulo feedback divider the same as a value of \$0001. Reset initializes the register to \$40 for a default multiply value of 64.

**NOTE:** The multiplier select bits have built-in protection such that they cannot be written when the PLL is on (PLLON = 1).

MOTOROLA

Computer Operating Properly (COP) I/O Signals

In monitor mode, the COP is disabled if the RST pin or the IRQ1 is held at  $V_{TST}$ . During the break state,  $V_{TST}$  on the RST pin disables the COP.

NOTE: Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

#### 9.4 I/O Signals

The following paragraphs describe the signals shown in Figure 9-1.

#### 9.4.1 CGMXCLK

CGMXCLK is the crystal oscillator output signal. CGMXCLK frequency is equal to the crystal frequency.

#### 9.4.2 STOP Instruction

The STOP instruction clears the COP prescaler.

#### 9.4.3 COPCTL Write

Writing any value to the COP control register (COPCTL) (see COP Control Register) clears the COP counter and clears bits 12 through 5 of the prescaler. Reading the COP control register returns the low byte of the reset vector.

#### 9.4.4 Power-On Reset

The power-on reset (POR) circuit clears the COP prescaler 4096 CGMXCLK cycles after power-up.

#### 9.4.5 Internal Reset

An internal reset clears the COP prescaler and the COP counter.

| MC68HC908GR8 — Rev 4.0 |                                       | Technical Data |

|------------------------|---------------------------------------|----------------|

| MOTOROLA               | Computer Operating Properly (COP)     | 135            |

|                        | For More Information On This Product. |                |

Go to: www.freescale.com

N — Negative flag

The CPU sets the negative flag when an arithmetic operation, logic operation, or data manipulation produces a negative result, setting bit 7 of the result.

- 1 = Negative result

- 0 = Non-negative result

- Z Zero flag

The CPU sets the zero flag when an arithmetic operation, logic operation, or data manipulation produces a result of \$00.

1 = Zero result

0 = Non-zero result

C — Carry/borrow flag

The CPU sets the carry/borrow flag when an addition operation produces a carry out of bit 7 of the accumulator or when a subtraction operation requires a borrow. Some instructions - such as bit test and branch, shift, and rotate - also clear or set the carry/borrow flag.

1 = Carry out of bit 7

0 = No carry out of bit 7

## 10.5 Arithmetic/logic unit (ALU)

The ALU performs the arithmetic and logic operations defined by the instruction set.

Refer to the *CPU08 Reference Manual* (Motorola document number CPU08RM/AD) for a description of the instructions and addressing modes and more detail about CPU architecture.

## **10.6 Low-power modes**

The WAIT and STOP instructions put the MCU in low--power consumption standby modes.

## **Central Processing Unit (CPU)**

#### Table 10-1. Instruction Set Summary (Continued)

| Source                                                                                         | Operation Description                                |                                                                     |   | Ef | fect on<br>CCR |    |    |   | Address<br>Mode                                                                              | Opcode                                           | Operand                                            | les                             |

|------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------|---|----|----------------|----|----|---|----------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|---------------------------------|

| Form                                                                                           |                                                      |                                                                     | v | Η  | I              | Ν  | z  | С | Addre<br>Mode                                                                                | Opc                                              | Ope                                                | Cycles                          |

| BCLR n, opr                                                                                    | Clear Bit n in M                                     | Mn ← 0                                                              | _ | _  | _              |    | _  | _ | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd | 4 4 4 4 4 4 4 4                 |

| BCS rel                                                                                        | Branch if Carry Bit Set (Same as BLO)                | PC ← (PC) + 2 + <i>rel</i> ? (C) = 1                                | - | -  | -              | -  | -  | - | REL                                                                                          | 25                                               | rr                                                 | 3                               |

| BEQ rel                                                                                        | Branch if Equal                                      | PC ← (PC) + 2 + <i>rel</i> ? (Z) = 1                                | - | -  | -              | -  | -  | - | REL                                                                                          | 27                                               | rr                                                 | 3                               |

| BGE opr                                                                                        | Branch if Greater Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 0$          | _ | -  | _              | -  | -  | - | REL                                                                                          | 90                                               | rr                                                 | 3                               |

| BGT opr                                                                                        | Branch if Greater Than (Signed<br>Operands)          | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 0$ | _ | _  | -              | -  | -  | - | REL                                                                                          | 92                                               | rr                                                 | 3                               |

| BHCC rel                                                                                       | Branch if Half Carry Bit Clear                       | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (H) = 0$                   | - | -  | -              | -  | -  | - | REL                                                                                          | 28                                               | rr                                                 | 3                               |

| BHCS rel                                                                                       | Branch if Half Carry Bit Set                         | PC ← (PC) + 2 + <i>rel</i> ? (H) = 1                                | - | -  | -              | -  | -  | - | REL                                                                                          | 29                                               | rr                                                 | 3                               |

| BHI rel                                                                                        | Branch if Higher                                     | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 0$          | - | -  | -              | -  | -  | - | REL                                                                                          | 22                                               | rr                                                 | 3                               |

| BHS rel                                                                                        | Branch if Higher or Same<br>(Same as BCC)            | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 0$                   | _ | -  | -              | -  | -  | - | REL                                                                                          | 24                                               | rr                                                 | 3                               |

| BIH rel                                                                                        | Branch if IRQ Pin High                               | $PC \leftarrow (PC) + 2 + \mathit{rel} ? \overline{IRQ} = 1$        | - | -  | -              | -  | -  | - | REL                                                                                          | 2F                                               | rr                                                 | 3                               |

| BIL rel                                                                                        | Branch if IRQ Pin Low                                | $PC \leftarrow (PC) + 2 + rel ? \overline{IRQ} = 0$                 | - | -  | -              | -  | -  | - | REL                                                                                          | 2E                                               | rr                                                 | 3                               |

| BIT #opr<br>BIT opr<br>BIT opr<br>BIT opr,X<br>BIT opr,X<br>BIT ,X<br>BIT opr,SP<br>BIT opr,SP | Bit Test                                             | (A) & (M)                                                           | 0 | _  | _              | \$ | \$ | _ | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A5<br>B5<br>C5<br>D5<br>E5<br>F5<br>9EE5<br>9ED5 |                                                    | 2<br>3<br>4<br>3<br>2<br>4<br>5 |

| BLE opr                                                                                        | Branch if Less Than or Equal To<br>(Signed Operands) | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (Z) \mid (N \oplus V) = 1$ | - | -  | -              | -  | 1  | - | REL                                                                                          | 93                                               | rr                                                 | 3                               |

| BLO rel                                                                                        | Branch if Lower (Same as BCS)                        | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) = 1$                   | - | -  | -              | -  | -  | - | REL                                                                                          | 25                                               | rr                                                 | 3                               |

| BLS rel                                                                                        | Branch if Lower or Same                              | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (C) \mid (Z) = 1$          | - | -  | -              | -  | -  | - | REL                                                                                          | 23                                               | rr                                                 | 3                               |

| BLT opr                                                                                        | Branch if Less Than (Signed Operands)                | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (N \oplus V) = 1$          | - | -  | -              | -  | -  | - | REL                                                                                          | 91                                               | rr                                                 | 3                               |

| BMC rel                                                                                        | Branch if Interrupt Mask Clear                       | $PC \leftarrow (PC) + 2 + \mathit{rel} ? (I) = 0$                   | - | -  | -              | -  | -  | - | REL                                                                                          | 2C                                               | rr                                                 | 3                               |

| BMI rel                                                                                        | Branch if Minus                                      | PC ← (PC) + 2 + <i>rel</i> ? (N) = 1                                | - | -  | -              | -  | -  | - | REL                                                                                          | 2B                                               | rr                                                 | 3                               |

| BMS rel                                                                                        | Branch if Interrupt Mask Set                         | PC ← (PC) + 2 + <i>rel</i> ? (I) = 1                                | - | -  | -              | -  | -  | - | REL                                                                                          | 2D                                               | rr                                                 | 3                               |

#### Technical Data

MOTOROLA

The IRQF bit in the INTSCR register can be used to check for pending interrupts. The IRQF bit is not affected by the IMASK bit, which makes it useful in applications where polling is preferred.

Use the BIH or BIL instruction to read the logic level on the IRQ1 pin.

**NOTE:** When using the level-sensitive interrupt trigger, avoid false interrupts by masking interrupt requests in the interrupt routine.

### 12.6 IRQ Module During Break Interrupts

The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear the latch during the break state. See Break Module (BRK).

To allow software to clear the IRQ latch during a break interrupt, write a logic 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect CPU interrupt flags during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), writing to the ACK bit in the IRQ status and control register during the break state has no effect on the IRQ interrupt flags.

MC68HC908GR8 - Rev 4.0

External Interrupt (IRQ)

Technical Data

MC68HC908GR8 — Rev 4.0

MOTOROLA

### **Keyboard Interrupt (KBI)**

#### **13.4 Functional Description**

Writing to the KBIE3–KBIE0 bits in the keyboard interrupt enable register independently enables or disables each port A pin as a keyboard interrupt pin. Enabling a keyboard interrupt pin also enables its internal pullup device. A logic 0 applied to an enabled keyboard interrupt pin latches a keyboard interrupt request.

A keyboard interrupt is latched when one or more keyboard pins goes low after all were high. The MODEK bit in the keyboard status and control register controls the triggering mode of the keyboard interrupt.

- If the keyboard interrupt is edge-sensitive only, a falling edge on a keyboard pin does not latch an interrupt request if another keyboard pin is already low. To prevent losing an interrupt request on one pin because another pin is still low, software can disable the latter pin while it is low.

- If the keyboard interrupt is falling-edge and low-level sensitive, an interrupt request is present as long as any keyboard interrupt pin is low and the pin is keyboard interrupt enabled.

**Technical Data**

MOTOROLA

|                              | DECET                                     | \$FFFE/       | DU  | DTDA | DTD1 | External             | COMOUT        | Bus COP       |            | Bus  |      | Co                              | For Se                                                              | Commont |

|------------------------------|-------------------------------------------|---------------|-----|------|------|----------------------|---------------|---------------|------------|------|------|---------------------------------|---------------------------------------------------------------------|---------|

| IRQ                          | RESET                                     | \$FFFF        | PLL | PTB0 | PTB1 | Clock <sup>(1)</sup> | CGMOUT        | Freq          | COP        | PTA0 | PTA1 | Baud<br>Rate <sup>(2) (3)</sup> | Comment                                                             |         |

| Х                            | GND                                       | Х             | Х   | Х    | Х    | Х                    | 0             | 0             | Disabled   | Х    | Х    | 0                               | No operation until reset goes high                                  |         |

|                              | V <sub>DD</sub>                           |               |     |      |      |                      | 4.0450        | 0 4574        |            | 1    | 0    | 9600                            | PTB0 and PTB1                                                       |         |

| V <sub>TST</sub>             | or<br>V <sub>TST</sub>                    | Х             | OFF | 1    | 0    | 9.8304<br>MHz        | 4.9152<br>MHz | 2.4576<br>MHz | Disabled   | х    | 1    | DNA                             | voltages only<br><u>req</u> uired if<br>IRQ = V <sub>TST</sub>      |         |

| V                            | V                                         | * <b>-</b>    | 055 | V    | V    | 9.8304               | 4.9152        | 2.4576        | D's shired | 1    | 0    | 9600                            | External frequency<br>always divided by<br>4                        |         |

| V <sub>DD</sub>              | V <sub>DD</sub>                           | \$FFFF        | OFF | Х    | Х    | MHz                  | MHz           | MHz           | Disabled   | Х    | 1    | DNA                             |                                                                     |         |

|                              | N                                         | *===          | 0.1 | N    | N    | 32.768               | 4.9152        | 2.4576        | <b>D</b>   | 1    | 0    | 9600                            | PLL enabled (BCS                                                    |         |

| GND                          | V <sub>DD</sub>                           | \$FFFF        | ON  | Х    | Х    | kHz                  | MHz           | MHz           | Disabled   | Х    | 1    | DNA                             | set) in monitor<br>code                                             |         |

| V <sub>DD</sub><br>or<br>GND | V <sub>TST</sub>                          | \$FFFF        | OFF | х    | х    | Х                    | _             | _             | Enabled    | х    | х    | _                               | Enters user mode<br>— will encounter<br>an illegal address<br>reset |         |

| V <sub>DD</sub><br>or<br>GND | V <sub>DD</sub><br>or<br>V <sub>TST</sub> | Not<br>\$FFFF | OFF | Х    | Х    | х                    | _             | _             | Enabled    | х    | Х    | _                               | Enters user mode                                                    |         |

#### Table 15-1. Monitor Mode Signal Requirements and Options

Notes:

1. External clock is derived by a 32.768 kHz crystal or a 9.8304 MHz off-chip oscillator

2. PTA0 = 1 if serial communication; PTA0 = X if parallel communication

3. PTA1 = 0  $\rightarrow$  serial, PTA1 = 1  $\rightarrow$  parallel communication for security code entry

4. DNA = does not apply, X = don't care

If entering monitor mode with  $V_{TST}$  applied on IRQ (condition set 1), the CGMOUT frequency is equal to the CGMXCLK frequency and the OSC1 input directly generates internal bus clocks. In this case, the OSC1 signal must have a 50% duty cycle at maximum bus frequency.

If entering monitor mode without high voltage applied on IRQ (condition set 2 or 3, where applied voltage is either  $V_{DD}$  or  $V_{SS}),$  then all port B pin

MC68HC908GR8 - Rev 4.0

MOTOROLA

#### 15.4.4 Baud Rate

The communication baud rate is controlled by the crystal frequency upon entry into monitor mode. The divide by ratio is 1024.

If monitor mode was entered with  $V_{DD}$  on  $\overline{IRQ}$ , then the divide by ratio is also set at 1024. If monitor mode was entered with  $V_{SS}$  on  $\overline{IRQ}$ , then the internal PLL steps up the external frequency, presumed to be 32.768 kHz, to 2.4576 MHz. These latter two conditions for monitor mode entry require that the reset vector is blank.

Table 15-3 lists external frequencies required to achieve a standard baud rate of 9600 BPS. Other standard baud rates can be accomplished using proportionally higher or lower frequency generators. If using a crystal as the clock source, be aware of the upper frequency limit that the internal clock module can handle. See 5.0 V Control Timing and 3.0 V Control Timing for this limit.

| Table 15-3 | . Monitor | Baud | Rate | Selection |

|------------|-----------|------|------|-----------|

|------------|-----------|------|------|-----------|

| External<br>Frequency | IRQ              | Internal<br>Frequency | Baud Rate<br>(BPS) |

|-----------------------|------------------|-----------------------|--------------------|

| 9.8304 MHz            | V <sub>TST</sub> | 2.4576 MHz            | 9600               |

| 9.8304 MHz            | V <sub>DD</sub>  | 2.4576 MHz            | 9600               |

| 32.768 kHz            | $V_{SS}$         | 2.4576 MHz            | 9600               |

#### 15.4.5 Commands

The monitor ROM firmware uses these commands:

- READ (read memory)

- WRITE (write memory)

- IREAD (indexed read)

- IWRITE (indexed write)

- READSP (read stack pointer)

- RUN (run user program)

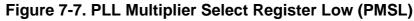

#### 16.5.3 Port C Input Pullup Enable Register

The port C input pullup enable register (PTCPUE) contains a software configurable pullup device for each of the two port C pins. Each bit is individually configurable and requires that the data direction register, DDRC, bit be configured as an input. Each pullup is automatically and dynamically disabled when a port bit's DDRC is configured for output mode.

#### Figure 16-12. Port C Input Pullup Enable Register (PTCPUE)

PTCPUE1-PTCPUE0 — Port C Input Pullup Enable Bits

These writeable bits are software programmable to enable pullup devices on an input port bit.

- 1 = Corresponding port C pin configured to have internal pullup

- 0 = Corresponding port C pin internal pullup disconnected

MC68HC908GR8 - Rev 4.0

# Section 17. RAM

### 17.1 Contents

| 17.2 | Introduction           | <u>'9</u> |

|------|------------------------|-----------|

| 17.3 | Functional Description | 29        |

### **17.2 Introduction**

This section describes the 384 bytes of RAM (random-access memory).

### **17.3 Functional Description**

Addresses \$0040 through \$01BF are RAM locations. The location of the stack RAM is programmable. The 16-bit stack pointer allows the stack to be anywhere in the 64K byte memory space.

**NOTE:** For correct operation, the stack pointer must point only to RAM locations.

Within page zero are 192 bytes of RAM. Because the location of the stack RAM is programmable, all page zero RAM locations can be used for I/O control and user data or code. When the stack pointer is moved from its reset location at \$00FF out of page zero, direct addressing mode instructions can efficiently access all page zero RAM locations. Page zero RAM, therefore, provides ideal locations for frequently accessed global variables.

Before processing an interrupt, the CPU uses five bytes of the stack to save the contents of the CPU registers.

**NOTE:** For M6805 compatibility, the H register is not stacked.

MC68HC908GR8 — Rev 4.0

MOTOROLA

continuously loads break characters into the transmit shift register. After software clears the SBK bit, the shift register finishes transmitting the last break character and then transmits at least one logic 1. The automatic logic 1 at the end of a break character guarantees the recognition of the start bit of the next character.

The SCI recognizes a break character when a start bit is followed by eight or nine logic 0 data bits and a logic 0 where the stop bit should be.

Receiving a break character has these effects on SCI registers:

- Sets the framing error bit (FE) in SCS1

- Sets the SCI receiver full bit (SCRF) in SCS1

- Clears the SCI data register (SCDR)

- Clears the R8 bit in SCC3

- Sets the break flag bit (BKF) in SCS2

- May set the overrun (OR), noise flag (NF), parity error (PE), or reception in progress flag (RPF) bits

#### 18.5.2.4 Idle Characters

An idle character contains all logic 1s and has no start, stop, or parity bit. Idle character length depends on the M bit in SCC1. The preamble is a synchronizing idle character that begins every transmission.

If the TE bit is cleared during a transmission, the PE2/TxD pin becomes idle after completion of the transmission in progress. Clearing and then setting the TE bit during a transmission queues an idle character to be sent after the character currently being transmitted.

**NOTE:** When queueing an idle character, return the TE bit to logic 1 before the stop bit of the current character shifts out to the TxD pin. Setting TE after the stop bit appears on TxD causes data previously written to the SCDR to be lost.

Toggle the TE bit for a queued idle character when the SCTE bit becomes set and just before writing the next byte to the SCDR.

MC68HC908GR8 — Rev 4.0

condition (logic 1). Clearing and then setting TE during a transmission queues an idle character to be sent after the character currently being transmitted. Reset clears the TE bit.

- 1 = Transmitter enabled

- 0 = Transmitter disabled

- **NOTE:** Writing to the TE bit is not allowed when the enable SCI bit (ENSCI) is clear. ENSCI is in SCI control register 1.

- RE Receiver Enable Bit

Setting this read/write bit enables the receiver. Clearing the RE bit disables the receiver but does not affect receiver interrupt flag bits. Reset clears the RE bit.

- 1 = Receiver enabled

- 0 = Receiver disabled

- **NOTE:** Writing to the RE bit is not allowed when the enable SCI bit (ENSCI) is clear. ENSCI is in SCI control register 1.

- RWU Receiver Wakeup Bit

This read/write bit puts the receiver in a standby state during which receiver interrupts are disabled. The WAKE bit in SCC1 determines whether an idle input or an address mark brings the receiver out of the standby state and clears the RWU bit. Reset clears the RWU bit.

- 1 = Standby state

- 0 = Normal operation

- SBK Send Break Bit

Setting and then clearing this read/write bit transmits a break character followed by a logic 1. The logic 1 after the break character guarantees recognition of a valid start bit. If SBK remains set, the transmitter continuously transmits break characters with no logic 1s between them. Reset clears the SBK bit.

- 1 = Transmit break characters

- 0 = No break characters being transmitted

- **NOTE:** Do not toggle the SBK bit immediately after setting the SCTE bit. Toggling SBK before the preamble begins causes the SCI to send a break character instead of a preamble.

MC68HC908GR8 - Rev 4.0

operation, clear the SCTE bit by reading SCS1 with SCTE set and then writing to SCDR. Reset sets the SCTE bit.

- 1 = SCDR data transferred to transmit shift register

- 0 = SCDR data not transferred to transmit shift register

- TC Transmission Complete Bit

This read-only bit is set when the SCTE bit is set, and no data, preamble, or break character is being transmitted. TC generates an SCI transmitter CPU interrupt request if the TCIE bit in SCC2 is also set. TC is automatically cleared when data, preamble or break is queued and ready to be sent. There may be up to 1.5 transmitter clocks of latency between queueing data, preamble, and break and the transmission actually starting. Reset sets the TC bit.

1 = No transmission in progress

0 = Transmission in progress

SCRF — SCI Receiver Full Bit

This clearable, read-only bit is set when the data in the receive shift register transfers to the SCI data register. SCRF can generate an SCI receiver CPU interrupt request. When the SCRIE bit in SCC2 is set, SCRF generates a CPU interrupt request. In normal operation, clear the SCRF bit by reading SCS1 with SCRF set and then reading the SCDR. Reset clears SCRF.

1 = Received data available in SCDR

0 = Data not available in SCDR

IDLE — Receiver Idle Bit

This clearable, read-only bit is set when 10 or 11 consecutive logic 1s appear on the receiver input. IDLE generates an SCI error CPU interrupt request if the ILIE bit in SCC2 is also set. Clear the IDLE bit by reading SCS1 with IDLE set and then reading the SCDR. After the receiver is enabled, it must receive a valid character that sets the SCRF bit before an idle condition can set the IDLE bit. Also, after the IDLE bit has been cleared, a valid character must again set the SCRF bit before an idle condition can set the IDLE bit. Reset clears the IDLE bit.

- 1 = Receiver input idle

- 0 = Receiver input active (or idle since the IDLE bit was cleared)

# Section 22. Timer Interface Module (TIM)

#### 22.1 Contents

| 22.2  | Introduction                                         | 5                                                                                                                                                                                                          |

|-------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22.3  | Features                                             | 6                                                                                                                                                                                                          |

| 22.4  | Pin Name Conventions                                 | 6                                                                                                                                                                                                          |

| 22.5  | Functional Description                               | 7                                                                                                                                                                                                          |

| 22.6  | Interrupts                                           | 6                                                                                                                                                                                                          |

| 22.7  | Low-Power Modes                                      | 7                                                                                                                                                                                                          |

| 22.8  | TIM During Break Interrupts                          | 8                                                                                                                                                                                                          |

| 22.9  | I/O Signals                                          | 8                                                                                                                                                                                                          |

| 22.10 | I/O Registers                                        | .9                                                                                                                                                                                                         |

|       | 22.3<br>22.4<br>22.5<br>22.6<br>22.7<br>22.8<br>22.9 | 22.2Introduction.3322.3Features.3322.4Pin Name Conventions.3322.5Functional Description.3322.6Interrupts.3422.7Low-Power Modes.3422.8TIM During Break Interrupts.3422.9I/O Signals.3422.10I/O Registers.34 |

### 22.2 Introduction

This section describes the timer interface (TIM) module. The TIM on this part is a 2-channel and a1-channel timer that provides a timing reference with input capture, output compare, and pulse-width-modulation functions. Figure 22-1 is a block diagram of the TIM. This particular MCU has two timer interface modules which are denoted as TIM1 and TIM2.

For further information regarding timers on M68HC08 family devices, please consult the HC08 Timer Reference Manual, TIM08RM/AD.

MC68HC908GR8 — Rev 4.0

MOTOROLA

### **Timer Interface Module (TIM)**

| MSxB:MSxA | ELSxB:ELSxA | Mode                 | Configuration                                        |

|-----------|-------------|----------------------|------------------------------------------------------|

| X0        | 00          | Output preset        | Pin under port control;<br>initial output level high |

| X1        | 00          | Output preset        | Pin under port control;<br>initial output level low  |

| 00        | 01          |                      | Capture on rising edge only                          |

| 00        | 10          | Input capture        | Capture on falling edge only                         |

| 00        | 11          |                      | Capture on rising or<br>falling edge                 |

| 01        | 01          | Output               | Toggle output on compare                             |

| 01        | 10          | compare or           | Clear output on compare                              |

| 01        | 11          | PWM                  | Set output on compare                                |

| 1X        | 01          | Buffered             | Toggle output on compare                             |

| 1X        | 10          | output<br>compare or | Clear output on compare                              |

| 1X        | 11          | buffered PWM         | Set output on compare                                |

Table 22-3. Mode, Edge, and Level Selection

**NOTE:** Before enabling a TIM channel register for input capture operation, make sure that the PTD/TCHx pin is stable for at least two bus clocks.

TOVx — Toggle On Overflow Bit

When channel x is an output compare channel, this read/write bit controls the behavior of the channel x output when the TIM counter overflows. When channel x is an input capture channel, TOVx has no effect. Reset clears the TOVx bit.

- 1 = Channel x pin toggles on TIM counter overflow.

- 0 = Channel x pin does not toggle on TIM counter overflow.

- **NOTE:** When TOVx is set, a TIM counter overflow takes precedence over a channel x output compare if both occur at the same time.

MC68HC908GR8 — Rev 4.0