# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                   |

|----------------------------|----------------------------------------------------------|

| Core Processor             | HC08                                                     |

| Core Size                  | 8-Bit                                                    |

| Speed                      | 8MHz                                                     |

| Connectivity               | SCI, SPI                                                 |

| Peripherals                | LVD, POR, PWM                                            |

| Number of I/O              | 17                                                       |

| Program Memory Size        | 4KB (4K x 8)                                             |

| Program Memory Type        | FLASH                                                    |

| EEPROM Size                | -                                                        |

| RAM Size                   | 384 x 8                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                              |

| Data Converters            | A/D 6x8b                                                 |

| Oscillator Type            | Internal                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                        |

| Mounting Type              | Through Hole                                             |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                 |

| Supplier Device Package    | 28-PDIP                                                  |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908gr4cpe |

|                            |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| CGMXFC          | 1                | 28   | V <sub>SSA</sub>                     |

|-----------------|------------------|------|--------------------------------------|

| OSC2            | 2                | 27   | V <sub>DDA</sub>                     |

| OSC1            | 3                | 26   | PTA3/KBD3                            |

| RST             | 4                | 25   | PTA2/KBD2                            |

| PTE0/TxD        | 5                | 24   | PTA1/KBD1                            |

| PTE1/RxD        | 6                | 23   | PTA0/KBD0                            |

| ĪRQ             | 7                | 22   | V <sub>SSAD</sub> /V <sub>REFL</sub> |

| PTD0/SS         | 8                | 21   | VDDAD/VREFH                          |

| PTD1/MISO       | 9                | 20   | PTB3/AD3                             |

| PTD2/MOSI       | 1                | D 19 | PTB2/AD2                             |

| PTD3/SPSCK      | [ 1 <sup>·</sup> | 1 18 | PTB1/AD1                             |

| V <sub>SS</sub> | 12               | 2 17 | PTB0/AD0                             |

| V <sub>DD</sub> | 1:               | 3 16 | PTD6/T2CH0                           |

| PTD4/T1CH0      | [ 14             | 4 15 | PTD5/T1CH1                           |

NOTE: Ports PTB4, PTB5, PTC0, and PTC1 are available only with the QFP.

#### Figure 1-3. DIP And SOIC Pin Assignments

#### **1.6 Pin Functions**

Descriptions of the pin functions are provided here.

#### 1.6.1 Power Supply Pins ( $V_{DD}$ and $V_{SS}$ )

$V_{\text{DD}}$  and  $V_{\text{SS}}$  are the power supply and ground pins. The MCU operates from a single power supply.

Fast signal transitions on MCU pins place high, short-duration current demands on the power supply. To prevent noise problems, take special care to provide power supply bypassing at the MCU as Figure 1-4 shows. Place the C1 bypass capacitor as close to the MCU as possible. Use a high-frequency-response ceramic capacitor for C1. C2 is an optional bulk current bypass capacitor for use in applications that require the port pins to source high current levels.

MC68HC908GR8 — Rev 4.0

| Iable 2-1. Vector Addresses |        |         |                                       |  |  |  |  |  |  |  |  |

|-----------------------------|--------|---------|---------------------------------------|--|--|--|--|--|--|--|--|

| Vector Priority             | Vector | Address | Vector                                |  |  |  |  |  |  |  |  |

| Lowest                      | IF16   | \$FFDC  | Timebase Vector (High)                |  |  |  |  |  |  |  |  |

|                             | 11 10  | \$FFDD  | Timebase Vector (Low)                 |  |  |  |  |  |  |  |  |

|                             | IF15   | \$FFDE  | ADC Conversion Complete Vector (High) |  |  |  |  |  |  |  |  |

|                             | 1613   | \$FFDF  | ADC Conversion Complete Vector (Low)  |  |  |  |  |  |  |  |  |

|                             | IF14   | \$FFE0  | Keyboard Vector (High)                |  |  |  |  |  |  |  |  |

|                             | 1614   | \$FFE1  | Keyboard Vector (Low)                 |  |  |  |  |  |  |  |  |

|                             | IF13   | \$FFE2  | SCI Transmit Vector (High)            |  |  |  |  |  |  |  |  |

|                             | 1113   | \$FFE3  | SCI Transmit Vector (Low)             |  |  |  |  |  |  |  |  |

|                             | IF12   | \$FFE4  | SCI Receive Vector (High)             |  |  |  |  |  |  |  |  |

|                             |        | \$FFE5  | SCI Receive Vector (Low)              |  |  |  |  |  |  |  |  |

|                             | IF11   | \$FFE6  | SCI Error Vector (High)               |  |  |  |  |  |  |  |  |

|                             |        | \$FFE7  | SCI Error Vector (Low)                |  |  |  |  |  |  |  |  |

|                             | 1540   | \$FFE8  | SPI Transmit Vector (High)            |  |  |  |  |  |  |  |  |

|                             | IF10   | \$FFE9  | SPI Transmit Vector (Low)             |  |  |  |  |  |  |  |  |

|                             | IF9    | \$FFEA  | SPI Receive Vector (High)             |  |  |  |  |  |  |  |  |

|                             |        | \$FFEB  | SPI Receive Vector (Low)              |  |  |  |  |  |  |  |  |

|                             | IF8    | \$FFEC  | TIM2 Overflow Vector (High)           |  |  |  |  |  |  |  |  |

|                             |        | \$FFED  | TIM2 Overflow Vector (Low)            |  |  |  |  |  |  |  |  |

|                             |        | \$FFEE  | Reserved                              |  |  |  |  |  |  |  |  |

|                             | IF7    | \$FFEF  | Reserved                              |  |  |  |  |  |  |  |  |

|                             |        | \$FFF0  | TIM2 Channel 0 Vector (High)          |  |  |  |  |  |  |  |  |

|                             | IF6    | \$FFF1  | TIM2 Channel 0 Vector (Low)           |  |  |  |  |  |  |  |  |

|                             |        | \$FFF2  | TIM1 Overflow Vector (High)           |  |  |  |  |  |  |  |  |

|                             | IF5    | \$FFF3  | TIM1 Overflow Vector (Low)            |  |  |  |  |  |  |  |  |

|                             |        | \$FFF4  | TIM1 Channel 1 Vector (High)          |  |  |  |  |  |  |  |  |

|                             | IF4    | \$FFF5  | TIM1 Channel 1 Vector (Low)           |  |  |  |  |  |  |  |  |

|                             | 150    | \$FFF6  | TIM1 Channel 0 Vector (High)          |  |  |  |  |  |  |  |  |

|                             | IF3    | \$FFF7  | TIM1 Channel 0 Vector (Low)           |  |  |  |  |  |  |  |  |

|                             | 150    | \$FFF8  | PLL Vector (High)                     |  |  |  |  |  |  |  |  |

|                             | IF2    | \$FFF9  | PLL Vector (Low)                      |  |  |  |  |  |  |  |  |

|                             |        | \$FFFA  | IRQ Vector (High)                     |  |  |  |  |  |  |  |  |

|                             | IF1    | \$FFFB  | IRQ Vector (Low)                      |  |  |  |  |  |  |  |  |

|                             |        | \$FFFC  | SWI Vector (High)                     |  |  |  |  |  |  |  |  |

|                             |        | \$FFFD  | SWI Vector (Low)                      |  |  |  |  |  |  |  |  |

|                             |        | \$FFFE  | Reset Vector (High)                   |  |  |  |  |  |  |  |  |

| Highest                     |        | \$FFFF  | Reset Vector (Low)                    |  |  |  |  |  |  |  |  |

Table 2-1. Vector Addresses

MOTOROLA

# **Section 3. Low Power Modes**

#### 3.1 Contents

| 3.2  | Introduction                                   |

|------|------------------------------------------------|

| 3.3  | Analog-to-Digital Converter (ADC)              |

| 3.4  | Break Module (BRK)51                           |

| 3.5  | Central Processor Unit (CPU)51                 |

| 3.6  | Clock Generator Module (CGM)52                 |

| 3.7  | Computer Operating Properly Module (COP)52     |

| 3.8  | External Interrupt Module (IRQ)53              |

| 3.9  | Keyboard Interrupt Module (KBI)53              |

| 3.10 | Low-Voltage Inhibit Module (LVI)               |

| 3.11 | Serial Communications Interface Module (SCI)54 |

| 3.12 | Serial Peripheral Interface Module (SPI)       |

| 3.13 | Timer Interface Module (TIM1 and TIM2)55       |

| 3.14 | Timebase Module (TBM)56                        |

| 3.15 | Exiting Wait Mode                              |

| 3.16 | Exiting Stop Mode                              |

### 3.2 Introduction

The MCU may enter two low-power modes: wait mode and stop mode. They are common to all HC08 MCUs and are entered through instruction execution. This section describes how each module acts in the lowpower modes.

MC68HC908GR8 — Rev 4.0

Overflow bit (OVRF) — The OVRF bit is set if software does not read the byte in the receive data register before the next full byte enters the shift register. The error interrupt enable bit, ERRIE, enables OVRF CPU interrupt requests. OVRF and ERRIE are in the SPI status and control register.

4.4.2.8 SCI

SCI CPU interrupt sources:

- SCI transmitter empty bit (SCTE) SCTE is set when the SCI data register transfers a character to the transmit shift register. The SCI transmit interrupt enable bit, SCTIE, enables transmitter CPU interrupt requests. SCTE is in SCI status register 1. SCTIE is in SCI control register 2.

- Transmission complete bit (TC) TC is set when the transmit shift register and the SCI data register are empty and no break or idle character has been generated. The transmission complete interrupt enable bit, TCIE, enables transmitter CPU interrupt requests. TC is in SCI status register 1. TCIE is in SCI control register 2.

- SCI receiver full bit (SCRF) SCRF is set when the receive shift register transfers a character to the SCI data register. The SCI receive interrupt enable bit, SCRIE, enables receiver CPU interrupts. SCRF is in SCI status register 1. SCRIE is in SCI control register 2.

- Idle input bit (IDLE) IDLE is set when 10 or 11 consecutive logic 1s shift in from the RxD pin. The idle line interrupt enable bit, ILIE, enables IDLE CPU interrupt requests. IDLE is in SCI status register 1. ILIE is in SCI control register 2.

- Receiver overrun bit (OR) OR is set when the receive shift register shifts in a new character before the previous character was read from the SCI data register. The overrun interrupt enable bit, ORIE, enables OR to generate SCI error CPU interrupt requests. OR is in SCI status register 1. ORIE is in SCI control register 3.

#### 5.8 I/O Registers

These I/O registers control and monitor ADC operation:

- ADC status and control register (ADSCR)

- ADC data register (ADR)

- ADC clock register (ADCLK)

#### 5.8.1 ADC Status and Control Register

Function of the ADC status and control register (ADSCR) is described here.

Address: \$0003C

|                 | Bit 7          | 6    | 5    | 4     | 3     | 2     | 1     | Bit 0 |

|-----------------|----------------|------|------|-------|-------|-------|-------|-------|

| Read:<br>Write: | COCO/<br>IDMAS | AIEN | ADCO | ADCH4 | ADCH3 | ADCH2 | ADCH1 | ADCH0 |

| Reset:          | 0              | 0    | 0    | 1     | 1     | 1     | 1     | 1     |

Figure 5-2. ADC Status and Control Register (ADSCR)

COCO/IDMAS — Conversions Complete/Interrupt DMA Select Bit

When the AIEN bit is a logic 0, the COCO/IDMAS is a read-only bit which is set each time a conversion is completed except in the continuous conversion mode where it is set after the first conversion. This bit is cleared whenever the ADSCR is written or whenever the ADR is read.

If the AIEN bit is a logic 1, the COCO/IDMAS is a read/write bit which selects either CPU or DMA to service the ADC interrupt request. Reset clears this bit.

- 1 = Conversion completed (AIEN = 0)/DMA interrupt (AIEN = 1)

- 0 = Conversion not completed (AIEN = 0)/CPU interrupt (AIEN = 1)

**CAUTION:** Because the MC68HC908GR8 does **NOT** have a DMA module, the IDMAS bit should **NEVER** be set when AIEN is set. Doing so will mask ADC interrupts and cause unwanted results.

MC68HC908GR8 — Rev 4.0

## Analog-to-Digital Converter (ADC)

#### 5.8.3 ADC Clock Register

The ADC clock register (ADCLK) selects the clock frequency for the ADC.

Figure 5-4. ADC Clock Register (ADCLK)

ADIV2-ADIV0 - ADC Clock Prescaler Bits

ADIV2–ADIV0 form a 3-bit field which selects the divide ratio used by the ADC to generate the internal ADC clock. Table 5-2 shows the available clock configurations. The ADC clock should be set to approximately 1 MHz.

Table 5-2. ADC Clock Divide Ratio

| ADIV2 | ADIV1 | ADIV0 | ADC Clock Rate       |

|-------|-------|-------|----------------------|

| 0     | 0     | 0     | ADC input clock ÷ 1  |

| 0     | 0     | 1     | ADC input clock ÷ 2  |

| 0     | 1     | 0     | ADC input clock ÷ 4  |

| 0     | 1     | 1     | ADC input clock ÷ 8  |

| 1     | Х     | Х     | ADC input clock ÷ 16 |

X = don't care

ADICLK — ADC Input Clock Select Bit

ADICLK selects either the bus clock or CGMXCLK as the input clock source to generate the internal ADC clock. Reset selects CGMXCLK as the ADC clock source.

Technical Data

MC68HC908GR8 — Rev 4.0

MOTOROLA

# **Central Processing Unit (CPU)**

| Source<br>Form                                                                                 | Operation                  | Description                                                                                                                                                                                                                     |    | Ef | Effect on<br>CCR |    |    |    | Address<br>Mode                                     | Opcode                                           | Operand        | es                                   |

|------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|------------------|----|----|----|-----------------------------------------------------|--------------------------------------------------|----------------|--------------------------------------|

| FOILI                                                                                          |                            |                                                                                                                                                                                                                                 | ۷  | н  | I                | Ν  | Z  | С  | Addre<br>Mode                                       | Opc                                              | Ope            | Cycles                               |

| NEG opr<br>NEGA<br>NEGX<br>NEG opr,X<br>NEG opr,SP                                             | Negate (Two's Complement)  | $\begin{array}{c} M \leftarrow -(M) = \$00 - (M) \\ A \leftarrow -(A) = \$00 - (A) \\ X \leftarrow -(X) = \$00 - (X) \\ M \leftarrow -(M) = \$00 - (M) \\ M \leftarrow -(M) = \$00 - (M) \end{array}$                           | ¢  | _  | _                | \$ | \$ | \$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 30<br>40<br>50<br>60<br>70<br>9E60               | dd<br>ff<br>ff | 4<br>1<br>4<br>3<br>5                |

| NOP                                                                                            | No Operation               | None                                                                                                                                                                                                                            | -  | -  | -                | -  | -  | -  | INH                                                 | 9D                                               |                | 1                                    |

| NSA                                                                                            | Nibble Swap A              | A ← (A[3:0]:A[7:4])                                                                                                                                                                                                             | -  | -  | -                | -  | -  | -  | INH                                                 | 62                                               |                | 3                                    |

| ORA #opr<br>ORA opr<br>ORA opr<br>ORA opr,X<br>ORA opr,X<br>ORA ,X<br>ORA opr,SP<br>ORA opr,SP | Inclusive OR A and M       | A ← (A)   (M)                                                                                                                                                                                                                   | 0  | _  | _                | \$ | \$ | _  | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | AA<br>BA<br>CA<br>DA<br>EA<br>FA<br>9EEA<br>9EDA |                | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| PSHA                                                                                           | Push A onto Stack          | $Push\:(A);SP\leftarrow(SP)-1$                                                                                                                                                                                                  | -  | -  | -                | -  | -  | -  | INH                                                 | 87                                               |                | 2                                    |

| PSHH                                                                                           | Push H onto Stack          | $Push\ (H);\ SP \leftarrow (SP) - 1$                                                                                                                                                                                            | -  | -  | -                | -  | -  | -  | INH                                                 | 8B                                               |                | 2                                    |

| PSHX                                                                                           | Push X onto Stack          | $Push\ (X);SP\leftarrow(SP)-1$                                                                                                                                                                                                  | -  | -  | -                | -  | -  | -  | INH                                                 | 89                                               |                | 2                                    |

| PULA                                                                                           | Pull A from Stack          | $SP \leftarrow (SP + 1); Pull(A)$                                                                                                                                                                                               | -  | -  | -                | -  | -  | -  | INH                                                 | 86                                               |                | 2                                    |

| PULH                                                                                           | Pull H from Stack          | $SP \leftarrow (SP + 1); Pull (H)$                                                                                                                                                                                              | -  | -  | -                | -  | -  | -  | INH                                                 | 8A                                               |                | 2                                    |

| PULX                                                                                           | Pull X from Stack          | $SP \leftarrow (SP + 1); Pull (X)$                                                                                                                                                                                              | -  | -  | -                | -  | -  | -  | INH                                                 | 88                                               |                | 2                                    |

| ROL opr<br>ROLA<br>ROLX<br>ROL opr,X<br>ROL ,X<br>ROL opr,SP                                   | Rotate Left through Carry  |                                                                                                                                                                                                                                 | ¢  | _  | _                | \$ | \$ | \$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39<br>49<br>59<br>69<br>79<br>9E69               | dd<br>ff<br>ff | 4<br>1<br>4<br>3<br>5                |

| ROR <i>opr</i><br>RORA<br>RORX<br>ROR <i>opr</i> ,X<br>ROR ,X<br>ROR <i>opr</i> ,SP            | Rotate Right through Carry |                                                                                                                                                                                                                                 | ¢  | _  | _                | \$ | \$ | \$ | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36<br>46<br>56<br>66<br>76<br>9E66               | dd<br>ff<br>ff | 4<br>1<br>4<br>3<br>5                |

| RSP                                                                                            | Reset Stack Pointer        | $SP \gets \$FF$                                                                                                                                                                                                                 | -  | -  | -                | -  | -  | -  | INH                                                 | 9C                                               |                | 1                                    |

| RTI                                                                                            | Return from Interrupt      | $\begin{array}{c} SP \leftarrow (SP) + 1;  Pull  (CCR) \\ SP \leftarrow (SP) + 1;  Pull  (A) \\ SP \leftarrow (SP) + 1;  Pull  (X) \\ SP \leftarrow (SP) + 1;  Pull  (PCH) \\ SP \leftarrow (SP) + 1;  Pull  (PCL) \end{array}$ | \$ | \$ | \$               | \$ | \$ | \$ | INH                                                 | 80                                               |                | 7                                    |

| RTS                                                                                            | Return from Subroutine     | $\begin{array}{l} SP \leftarrow SP + 1; Pull \ (PCH) \\ SP \leftarrow SP + 1; \ Pull \ (PCL) \end{array}$                                                                                                                       | -  | -  | -                | -  | -  | -  | INH                                                 | 81                                               |                | 4                                    |

Technical Data

MOTOROLA

The IRQF bit in the INTSCR register can be used to check for pending interrupts. The IRQF bit is not affected by the IMASK bit, which makes it useful in applications where polling is preferred.

Use the BIH or BIL instruction to read the logic level on the IRQ1 pin.

**NOTE:** When using the level-sensitive interrupt trigger, avoid false interrupts by masking interrupt requests in the interrupt routine.

#### 12.6 IRQ Module During Break Interrupts

The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear the latch during the break state. See Break Module (BRK).

To allow software to clear the IRQ latch during a break interrupt, write a logic 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect CPU interrupt flags during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), writing to the ACK bit in the IRQ status and control register during the break state has no effect on the IRQ interrupt flags.

MC68HC908GR8 - Rev 4.0

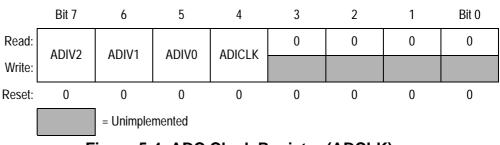

#### 16.5.2 Data Direction Register C

Data direction register C (DDRC) determines whether each port C pin is an input or an output. Writing a logic 1 to a DDRC bit enables the output buffer for the corresponding port C pin; a logic 0 disables the output buffer.

DDRC1–DDRC0 — Data Direction Register C Bits

These read/write bits control port C data direction. Reset clears DDRC1–DDRC0, configuring all port C pins as inputs.

- 1 = Corresponding port C pin configured as output

- 0 = Corresponding port C pin configured as input

- **NOTE:** Avoid glitches on port C pins by writing to the port C data register before changing data direction register C bits from 0 to 1.

Figure 16-11 shows the port C I/O logic.

**NOTE:** For those devices packaged in a 28-pin DIP and SOIC package, PTC1,0 are not connected. Set DDRC1,0 to a 1 to configure PTC1,0 as outputs.

MC68HC908GR8 — Rev 4.0

MOTOROLA

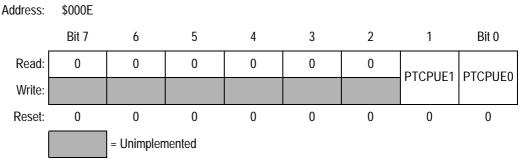

#### 16.5.3 Port C Input Pullup Enable Register

The port C input pullup enable register (PTCPUE) contains a software configurable pullup device for each of the two port C pins. Each bit is individually configurable and requires that the data direction register, DDRC, bit be configured as an input. Each pullup is automatically and dynamically disabled when a port bit's DDRC is configured for output mode.

#### Figure 16-12. Port C Input Pullup Enable Register (PTCPUE)

PTCPUE1-PTCPUE0 — Port C Input Pullup Enable Bits

These writeable bits are software programmable to enable pullup devices on an input port bit.

- 1 = Corresponding port C pin configured to have internal pullup

- 0 = Corresponding port C pin internal pullup disconnected

MC68HC908GR8 - Rev 4.0

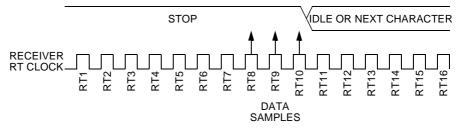

With the misaligned character shown in Figure 18-7, the receiver counts 170 RT cycles at the point when the count of the transmitting device is 10 bit times  $\times$  16 RT cycles + 3 RT cycles = 163 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a slow 9-bit character with no errors is

$$\left|\frac{170 - 163}{170}\right| \times 100 = 4.12\%$$

#### 18.5.3.7 Fast Data Tolerance

Figure 18-8 shows how much a fast received character can be misaligned without causing a noise error or a framing error. The fast stop bit ends at RT10 instead of RT16 but is still there for the stop bit data samples at RT8, RT9, and RT10.

Figure 18-8. Fast Data

For an 8-bit character, data sampling of the stop bit takes the receiver 9 bit times  $\times$  16 RT cycles + 10 RT cycles = 154 RT cycles.

With the misaligned character shown in Figure 18-8, the receiver counts 154 RT cycles at the point when the count of the transmitting device is 10 bit times  $\times$  16 RT cycles = 160 RT cycles.

The maximum percent difference between the receiver count and the transmitter count of a fast 8-bit character with no errors is

$$\left|\frac{154 - 160}{154}\right| \times 100 = 3.90\%$$

MC68HC908GR8 — Rev 4.0

MOTOROLA

### Serial Communications Interface (SCI)

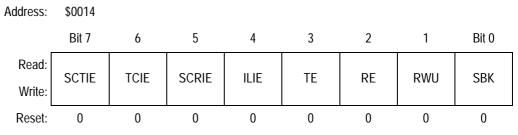

Figure 18-10. SCI Control Register 2 (SCC2)

SCTIE — SCI Transmit Interrupt Enable Bit

This read/write bit enables the SCTE bit to generate SCI transmitter CPU interrupt requests. Reset clears the SCTIE bit.

1 = SCTE enabled to generate CPU interrupt

0 = SCTE not enabled to generate CPU interrupt

TCIE — Transmission Complete Interrupt Enable Bit

This read/write bit enables the TC bit to generate SCI transmitter CPU interrupt requests. Reset clears the TCIE bit.

1 = TC enabled to generate CPU interrupt requests

0 = TC not enabled to generate CPU interrupt requests

SCRIE — SCI Receive Interrupt Enable Bit

This read/write bit enables the SCRF bit to generate SCI receiver CPU interrupt requests. Reset clears the SCRIE bit.

- 1 = SCRF enabled to generate CPU interrupt

- 0 = SCRF not enabled to generate CPU interrupt

ILIE — Idle Line Interrupt Enable Bit

This read/write bit enables the IDLE bit to generate SCI receiver CPU interrupt requests. Reset clears the ILIE bit.

1 = IDLE enabled to generate CPU interrupt requests

0 = IDLE not enabled to generate CPU interrupt requests

TE — Transmitter Enable Bit

Setting this read/write bit begins the transmission by sending a preamble of 10 or 11 logic 1s from the transmit shift register to the PE2/TxD pin. If software clears the TE bit, the transmitter completes any transmission in progress before the PE2/TxD returns to the idle

Technical Data

MC68HC908GR8 — Rev 4.0

# Section 19. System Integration Module (SIM)

#### **19.1 Contents**

| 19.2 | Introduction                         |

|------|--------------------------------------|

| 19.3 | SIM Bus Clock Control and Generation |

| 19.4 | Reset and System Initialization      |

| 19.5 | SIM Counter                          |

| 19.6 | Exception Control                    |

| 19.7 | Low-Power Modes                      |

| 19.8 | SIM Registers                        |

#### **19.2 Introduction**

This section describes the system integration module (SIM). Together with the CPU, the SIM controls all MCU activities. A block diagram of the SIM is shown in Figure 19-1. Table 19-1 is a summary of the SIM input/output (I/O) registers. The SIM is a system state controller that coordinates CPU and exception timing. The SIM is responsible for:

- Bus clock generation and control for CPU and peripherals:

- Stop/wait/reset/break entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and COP timeout

- Interrupt control:

- Acknowledge timing

- Arbitration control timing

#### MC68HC908GR8 - Rev 4.0

The full names of the SPI I/O pins are shown in Table 20-1. The generic pin names appear in the text that follows.

| SPI Generic<br>Pin Names: |     | MISO      | MOSI           | SS            | SPSCK      | CGND     |  |

|---------------------------|-----|-----------|----------------|---------------|------------|----------|--|

| Full SPI<br>Pin Names:    | SPI | PTD1/ATD9 | PTD2/ATD1<br>0 | PTD0/AT<br>D8 | PTD3/ATD11 | $V_{SS}$ |  |

#### Table 20-1. Pin Name Conventions

#### **20.5 Functional Description**

Figure 20-1 summarizes the SPI I/O registers and Figure 20-2 shows the structure of the SPI module.

| Addr.  | Register Name                              |        | Bit 7                  | 6      | 5      | 4    | 3     | 2        | 1     | Bit 0 |

|--------|--------------------------------------------|--------|------------------------|--------|--------|------|-------|----------|-------|-------|

|        | Read:                                      | SPRIE  | DMAS                   | SPMSTR | CPOL   | СРНА | SPWOM | SPE      | SPTIE |       |

| \$0010 | 10 SPI Control Register<br>(SPCR)          | Write: | JERIE                  |        | JEMOIR | CFUL | CELA  | 3F WOIVI | JFL   | SFIL  |

|        |                                            | Reset: | 0                      | 0      | 1      | 0    | 1     | 0        | 0     | 0     |

|        |                                            |        | SPRF                   |        | OVRF   | MODF | SPTE  | MODFEN   | SPR1  | SPR0  |

|        | SPI Status and Control<br>Register (SPSCR) | Write: |                        | ERRIE  |        |      |       |          | JERT  | SPRU  |

|        | 5 ( )                                      | Reset: | 0                      | 0      | 0      | 0    | 1     | 0        | 0     | 0     |

|        |                                            | Read:  | R7                     | R6     | R5     | R4   | R3    | R2       | R1    | R0    |

| \$0012 | \$0012 SPI Data Register<br>(SPDR)         | Write: | T7                     | T6     | T5     | T4   | T3    | T2       | T1    | Т0    |

|        |                                            | Reset: | t: Unaffected by reset |        |        |      |       |          |       |       |

|        |                                            | ſ      | = Unimplemented        |        |        |      |       |          |       |       |

Figure 20-1. SPI I/O Register Summary

# Serial Peripheral Interface (SPI)

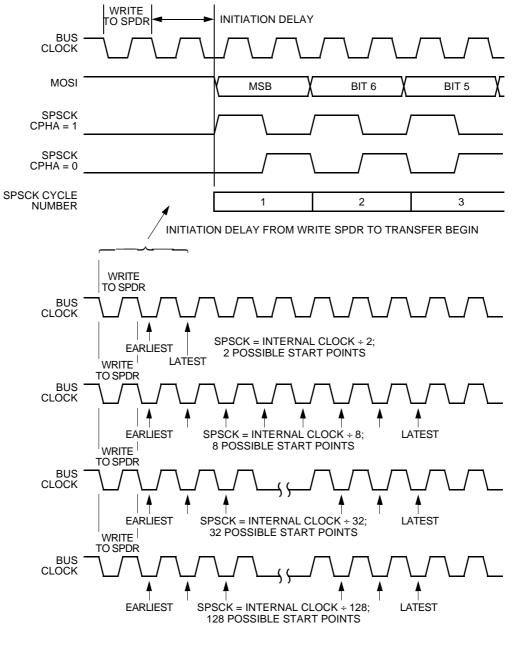

Figure 20-7. Transmission Start Delay (Master)

MOTOROLA

### 20.7 Queuing Transmission Data

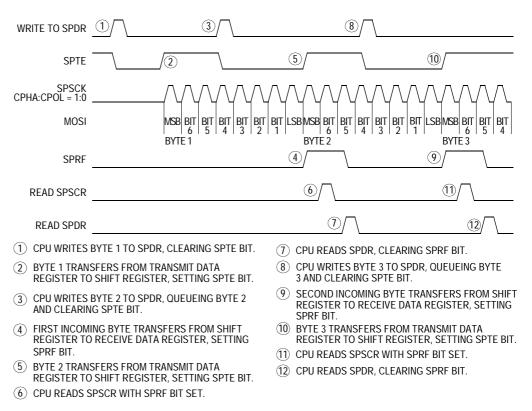

The double-buffered transmit data register allows a data byte to be queued and transmitted. For an SPI configured as a master, a queued data byte is transmitted immediately after the previous transmission has completed. The SPI transmitter empty flag (SPTE) indicates when the transmit data buffer is ready to accept new data. Write to the transmit data register only when the SPTE bit is high. Figure 20-8 shows the timing associated with doing back-to-back transmissions with the SPI (SPSCK has CPHA: CPOL = 1:0).

#### Figure 20-8. .SPRF/SPTE CPU Interrupt Timing

The transmit data buffer allows back-to-back transmissions without the slave precisely timing its writes between transmissions as in a system with a single data buffer. Also, if no new data is written to the data buffer, the last value contained in the shift register is the next data word to be transmitted.

### Serial Peripheral Interface (SPI)

#### 20.12 SPI During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear status bits during the break state. See System Integration Module (SIM).

To allow software to clear status bits during a break interrupt, write a logic 1 to the BCFE bit. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), software can read and write I/O registers during the break state without affecting status bits. Some status bits have a 2-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is at logic 0. After the break, doing the second step clears the status bit.

Since the SPTE bit cannot be cleared during a break with the BCFE bit cleared, a write to the transmit data register in break mode does not initiate a transmission nor is this data transferred into the shift register. Therefore, a write to the SPDR in break mode with the BCFE bit cleared has no effect.

#### 20.13 I/O Signals

The SPI module has five I/O pins and shares four of them with a parallel I/O port. They are:

- MISO Data received

- MOSI Data transmitted

- SPSCK Serial clock

- SS Slave select

- CGND Clock ground (internally connected to V<sub>SS</sub>)

The SPI has limited inter-integrated circuit ( $I^2C$ ) capability (requiring software support) as a master in a single-master environment. To

Technical Data

MC68HC908GR8 — Rev 4.0

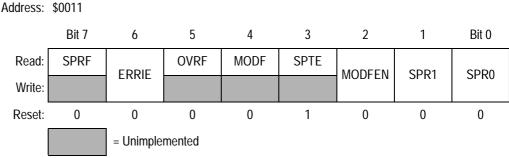

SPRF — SPI Receiver Full Bit

This clearable, read-only flag is set each time a byte transfers from the shift register to the receive data register. SPRF generates a CPU interrupt request if the SPRIE bit in the SPI control register is set also.

During an SPRF CPU interrupt, the CPU clears SPRF by reading the SPI status and control register with SPRF set and then reading the SPI data register.

Reset clears the SPRF bit.

- 1 = Receive data register full

- 0 = Receive data register not full

- ERRIE Error Interrupt Enable Bit

This read/write bit enables the MODF and OVRF bits to generate CPU interrupt requests. Reset clears the ERRIE bit.

- 1 = MODF and OVRF can generate CPU interrupt requests

- 0 = MODF and OVRF cannot generate CPU interrupt requests

OVRF — Overflow Bit

This clearable, read-only flag is set if software does not read the byte in the receive data register before the next full byte enters the shift register. In an overflow condition, the byte already in the receive data register is unaffected, and the byte that shifted in last is lost. Clear the OVRF bit by reading the SPI status and control register with OVRF set and then reading the receive data register. Reset clears the OVRF bit.

- 1 = Overflow

- 0 = No overflow

| Characteristic <sup>(1)</sup>                                                                                              | Symbol                              | Min                  | Тур <sup>(2)</sup> | Max     | Unit |

|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------|--------------------|---------|------|

| Pullup resisto <u>rs (as i</u> nput onl <u>y)</u><br>Ports PTA3/KBD37–PTA <u>0/KBD0</u> , PTC1–PTC0,<br>PTD6/T2CH0–PTD0/SS | R <sub>PU</sub>                     | 20                   | 45                 | 65      | kΩ   |

| Capacitance<br>Ports (as input or output)                                                                                  | C <sub>Out</sub><br>C <sub>In</sub> |                      | _                  | 12<br>8 | pF   |

| Monitor mode entry voltage                                                                                                 | V <sub>TST</sub>                    | V <sub>DD</sub> +2.5 | _                  | 8       | V    |

| Low-voltage inhibit, trip falling voltage – target                                                                         | V <sub>TRIPF</sub>                  | 2.35                 | 2.60               | 2.70    | V    |

| Low-voltage inhibit, trip rising voltage – target                                                                          | V <sub>TRIPR</sub>                  | 2.45                 | 2.66               | 2.80    | V    |

| Low-voltage inhibit reset/recover hysteresis – target $(V_{TRIPF} + V_{HYS} = V_{TRIPR})$                                  | V <sub>HYS</sub>                    | _                    | 60                 | _       | mV   |

| POR rearm voltage <sup>(8)</sup>                                                                                           | V <sub>POR</sub>                    | 0                    | _                  | 100     | mV   |

| POR reset voltage <sup>(9)</sup>                                                                                           | V <sub>PORRST</sub>                 | 0                    | 700                | 800     | mV   |

| POR rise time ramp rate <sup>(10)</sup>                                                                                    | R <sub>POR</sub>                    | 0.02                 | _                  | _       | V/ms |

#### Table 23-5. 3.0 V DC Electrical Characteristics

Notes:

1.  $V_{DD}$  = 3.0 Vdc ± 10%,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted

- 2. Typical values reflect average measurements at midpoint of voltage range, 25 °C only.

- 3. Run (operating) I<sub>DD</sub> measured using external square wave clock source ( $f_{OSC}$  = 16.4 MHz). All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects run I<sub>DD</sub>. Measured with all modules enabled.

- 4. Wait I<sub>DD</sub> measured using external square wave clock source ( $f_{OSC} = 16.4 \text{ MHz}$ ). All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. C<sub>L</sub> = 20 pF on OSC2. All ports configured as inputs. OSC2 capacitance linearly affects wait I<sub>DD</sub>. Measured with PLL and LVI enabled.

5. Stop  $I_{DD}$  is measured with OSC1 =  $V_{SS}$ .

- Stop I<sub>DD</sub> with TBM enabled is measured using an external square wave clock source (f<sub>OSC</sub> = 32.8 KHz). All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. All inputs configured as inputs.

- 7. Pullups and pulldowns are disabled.

- 8. Maximum is highest voltage that POR is guaranteed.

- 9. Maximum is highest voltage that POR is possible.

- 10. If minimum  $V_{DD}$  is not reached before the internal POR reset is released, RST must be driven low externally until minimum  $V_{DD}$  is reached.

MC68HC908GR8 - Rev 4.0

MOTOROLA

#### Glossary

- LVI See "low voltage inhibit module (LVI)."

- M68HC08 A Motorola family of 8-bit MCUs.

- mark/space The logic 1/logic 0 convention used in formatting data in serial communication.

- **mask** 1. A logic circuit that forces a bit or group of bits to a desired state. 2. A photomask used in integrated circuit fabrication to transfer an image onto silicon.

- **mask option** A optional microcontroller feature that the customer chooses to enable or disable.

- **mask option register (MOR)** An EPROM location containing bits that enable or disable certain MCU features.

- MCU Microcontroller unit. See "microcontroller."

- **memory location** Each M68HC08 memory location holds one byte of data and has a unique address. To store information in a memory location, the CPU places the address of the location on the address bus, the data information on the data bus, and asserts the write signal. To read information from a memory location, the CPU places the address of the location on the address bus and asserts the read signal. In response to the read signal, the selected memory location places its data onto the data bus.

- **memory map** A pictorial representation of all memory locations in a computer system.

- **microcontroller** Microcontroller unit (MCU). A complete computer system, including a CPU, memory, a clock oscillator, and input/output (I/O) on a single integrated circuit.

- **modulo counter** A counter that can be programmed to count to any number from zero to its maximum possible modulus.

- **monitor ROM** A section of ROM that can execute commands from a host computer for testing purposes.

- MOR See "mask option register (MOR)."

- most significant bit (MSB) The leftmost digit of a binary number.

- **multiplexer** A device that can select one of a number of inputs and pass the logic level of that input on to the output.

- N The negative bit in the condition code register of the CPU08. The CPU sets the negative bit when an arithmetic operation, logical operation, or data manipulation produces a negative result.

- nibble A set of four bits (half of a byte).

MC68HC908GR8 — Rev 4.0

MOTOROLA