Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | HC08                                                                  |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SCI, SPI                                                              |

| Peripherals                | LVD, POR, PWM                                                         |

| Number of I/O              | 17                                                                    |

| Program Memory Size        | 7.5KB (7.5K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 384 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 6x8b                                                              |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                        |

| Supplier Device Package    | 28-SOIC                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908gr8cdwer |

# MC68HC908GR8 MC68HC908GR4

Technical Data — Rev 4.0

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Motorola and 🔊 are registered trademarks of Motorola, Inc. DigitalDNA is a trademark of Motorola, Inc.

© Motorola, Inc., 2002

MC68HC908GR8 — Rev 4.0

## **Section 11. Flash Memory**

|                        | 11.1  | Contents                             | 157           |

|------------------------|-------|--------------------------------------|---------------|

|                        | 11.2  | Introduction                         | 157           |

|                        | 11.3  | Functional Description               | 157           |

|                        | 11.4  | FLASH Control Register               | 159           |

|                        | 11.5  | FLASH Page Erase Operation           | 160           |

|                        | 11.6  | FLASH Mass Erase Operation           | 161           |

|                        | 11.7  | FLASH Program/Read Operation         | 162           |

|                        | 11.8  | FLASH Block Protection               | 163           |

|                        | 11.9  | Wait Mode                            | 166           |

|                        | 11.10 | STOP Mode                            | 166           |

|                        |       | Section 12. External Interrupt (IRQ) |               |

|                        | 12.1  | Contents                             | 167           |

|                        | 12.2  | Introduction                         |               |

|                        | 12.3  | Features                             |               |

|                        | 12.4  | Functional Description               |               |

|                        | 12.5  | IRQ1 Pin                             |               |

|                        | 12.6  | IRQ Module During Break Interrupts   |               |

|                        | 12.7  | IRQ Status and Control Register      |               |

|                        |       | Cootion 42 Noveboond Intermed (I/DI) |               |

|                        | 10.4  | Section 13. Keyboard Interrupt (KBI) | 475           |

|                        | 13.1  | Contents                             |               |

|                        | 13.2  | Introduction                         | 175           |

|                        | 13.3  | Features                             | 175           |

|                        | 13.4  | Functional Description               | 176           |

|                        | 13.5  | Keyboard Initialization              | 179           |

| MC68HC908GR8 — Rev 4.0 | )     | Т                                    | echnical Data |

## **Resets and Interrupts**

#### 4.3.3.3 Low-Voltage Inhibit Reset

A low-voltage inhibit (LVI) reset is an internal reset caused by a drop in the power supply voltage to the LVI trip voltage, V<sub>TRIPF</sub>.

#### An LVI reset:

- Holds the clocks to the CPU and modules inactive for an oscillator stabilization delay of 4096 CGMXCLK cycles after the power supply voltage rises to V<sub>TRIPF</sub>

- Drives the RST pin low for as long as V<sub>DD</sub> is below V<sub>TRIPF</sub> and during the oscillator stabilization delay

- Releases the RST pin 32 CGMXCLK cycles after the oscillator stabilization delay

- Releases the CPU to begin the reset vector sequence

64 CGMXCLK cycles after the oscillator stabilization delay

- Sets the LVI bit in the SIM reset status register

### 4.3.3.4 Illegal Opcode Reset

An illegal opcode reset is an internal reset caused by an opcode that is not in the instruction set. An illegal opcode reset sets the ILOP bit in the SIM reset status register.

If the stop enable bit, STOP, in the mask option register is a logic 0, the STOP instruction causes an illegal opcode reset.

#### 4.3.3.5 Illegal Address Reset

An illegal address reset is an internal reset caused by opcode fetch from an unmapped address. An illegal address reset sets the ILAD bit in the SIM reset status register.

A data fetch from an unmapped address does not generate a reset.

Analog-to-Digital Converter (ADC)

Clock Generator Module (CGMC)

Functional Description

allows. See Electrical Specifications. Choose the reference divider, R = 1. After choosing N and P, the actual bus frequency can be determined using equation in 2 above.

When the tolerance on the bus frequency is tight, choose  $f_{RCLK}$  to an integer divisor of  $f_{BUSDES}$ , and R = 1. If  $f_{RCLK}$  cannot meet this requirement, use the following equation to solve for R with practical choices of  $f_{RCLK}$ , and choose the  $f_{RCLK}$  that gives the lowest R.

$$R = round \left[ R_{MAX} \times \left\{ \left( \frac{f_{VCLKDES}}{f_{RCLK}} \right) - integer \left( \frac{f_{VCLKDES}}{f_{RCLK}} \right) \right\} \right]$$

4. Select a VCO frequency multiplier, N.

$$N = round \left( \frac{R \times f_{VCLKDES}}{f_{RCLK}} \right)$$

Reduce N/R to the lowest possible R.

5. If N is  $< N_{max}$ , use P = 0. If N  $> N_{max}$ , choose P using this table:

| Current N Value                                           | Р |

|-----------------------------------------------------------|---|

| 0 < N ≤ N <sub>max</sub>                                  | 0 |

| $N_{max} < N \le N_{max} \times 2$                        | 1 |

| $N_{\text{max}} \times 2 < N \le N_{\text{max}} \times 4$ | 2 |

| $N_{\text{max}} \times 4 < N \le N_{\text{max}} \times 8$ | 3 |

Then recalculate N:

$$N = round \left( \frac{R \times f_{VCLKDES}}{f_{RCLK} \times 2^{P}} \right)$$

Calculate and verify the adequacy of the VCO and bus frequencies f<sub>VCLK</sub> and f<sub>BUS</sub>.

$$f_{VCLK} = (2^P \times N/R) \times f_{RCLK}$$

$f_{BUS} = (f_{VCLK})/4$

7. Select the VCO's power-of-two range multiplier E, according to

MC68HC908GR8 — Rev 4.0

**MOTOROLA**

#### Technical Data — MC68HC908GR8

## **Section 11. Flash Memory**

#### 11.1 Contents

| 11.2  | Introduction                 | 15/ |

|-------|------------------------------|-----|

| 11.3  | Functional Description       | 157 |

| 11.4  | FLASH Control Register       | 159 |

| 11.5  | FLASH Page Erase Operation   | 160 |

| 11.6  | FLASH Mass Erase Operation   | 161 |

| 11.7  | FLASH Program/Read Operation | 162 |

| 11.8  | FLASH Block Protection       | 163 |

| 11.9  | Wait Mode                    | 166 |

| 11 10 | STOP Mode                    | 166 |

#### 11.2 Introduction

This section describes the operation of the embedded FLASH memory. This memory can be read, programmed, and erased from a single external supply. The program, erase, and read operations are enabled through the use of an internal charge pump.

## 11.3 Functional Description

The FLASH memory is an array of 7,680 bytes for the MC68HC908GR8 or 4,096 bytes for the MC68HC908GR4 with an additional 36 bytes of user vectors and one byte used for block protection. *An erased bit reads as logic 1 and a programmed bit reads as a logic 0*. The program and erase operations are facilitated through control bits in the Flash Control

MC68HC908GR8 — Rev 4.0

## **Keyboard Interrupt (KBI)**

#### 13.6 Low-Power Modes

The WAIT and STOP instructions put the MCU in low powerconsumption standby modes.

#### 13.6.1 Wait Mode

The keyboard module remains active in wait mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of wait mode.

### 13.6.2 Stop Mode

The keyboard module remains active in stop mode. Clearing the IMASKK bit in the keyboard status and control register enables keyboard interrupt requests to bring the MCU out of stop mode.

### 13.7 Keyboard Module During Break Interrupts

The system integration module (SIM) controls whether the keyboard interrupt latch can be cleared during the break state. The BCFE bit in the SIM break flag control register (SBFCR) enables software to clear status bits during the break state.

To allow software to clear the keyboard interrupt latch during a break interrupt, write a logic 1 to the BCFE bit. If a latch is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect the latch during the break state, write a logic 0 to the BCFE bit. With BCFE at logic 0 (its default state), writing to the keyboard acknowledge bit (ACKK) in the keyboard status and control register during the break state has no effect. See Keyboard Status and Control Register.

A sequence of IREAD or IWRITE commands can access a block of memory sequentially over the full 64K byte memory map.

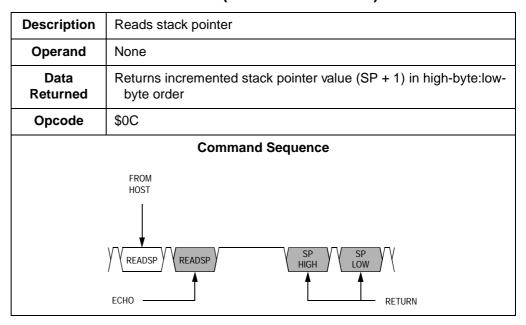

Table 15-8. READSP (Read Stack Pointer) Command

Table 15-9. RUN (Run User Program) Command

| Description      | Executes PULH and RTI instructions |  |  |  |  |

|------------------|------------------------------------|--|--|--|--|

| Operand          | None                               |  |  |  |  |

| Data<br>Returned | None                               |  |  |  |  |

| Opcode           | \$28                               |  |  |  |  |

|                  | Command Sequence                   |  |  |  |  |

| FROM<br>HOST     |                                    |  |  |  |  |

|                  |                                    |  |  |  |  |

|                  | Y V RUN Y RUN V                    |  |  |  |  |

|                  | ECHO                               |  |  |  |  |

MC68HC908GR8 — Rev 4.0

**MOTOROLA**

#### Technical Data — MC68HC908GR8

## Section 16. Input/Output Ports (I/O)

#### 16.1 Contents

| 16.2 | Introduction | )5         |

|------|--------------|------------|

| 16.3 | Port A       | <b>)</b> 9 |

| 16.4 | Port B       | 13         |

| 16.5 | Port C       | 16         |

| 16.6 | Port D       | 20         |

| 16.7 | Port E       | 25         |

#### 16.2 Introduction

Twenty one (21) bidirectional input-output (I/O) pins form five parallel ports. All I/O pins are programmable as inputs or outputs. All individual bits within port A, port C, and port D are software configurable with pullup devices if configured as input port bits. The pullup devices are automatically and dynamically disabled when a port bit is switched to output mode.

#### **NOTE:**

Connect any unused I/O pins to an appropriate logic level, either  $V_{DD}$  or  $V_{SS}$ . Although the I/O ports do not require termination for proper operation, termination reduces excess current consumption and the possibility of electrostatic damage.

MC68HC908GR8 — Rev 4.0

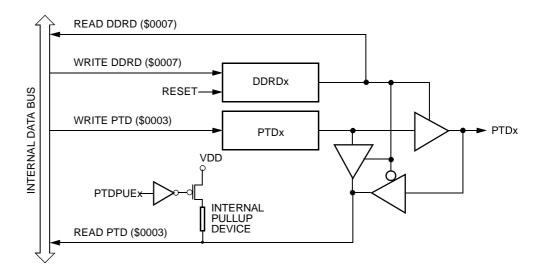

Figure 16-15. Port D I/O Circuit

When bit DDRDx is a logic 1, reading address \$0003 reads the PTDx data latch. When bit DDRDx is a logic 0, reading address \$0003 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 16-5 summarizes the operation of the port D pins.

Table 16-5. Port D Pin Functions

| PTDPUE Bit | DDRD Bit | PTD Bit          | I/O Pin Mode                          | Accesses to DDRD | Access    | es to PTD                |

|------------|----------|------------------|---------------------------------------|------------------|-----------|--------------------------|

| FIDFUE BIL | DDKD BIL | FIDBIL           | I/O PIII WIOGE                        | Read/Write       | Read      | Write                    |

| 1          | 0        | X <sup>(1)</sup> | Input, V <sub>DD</sub> <sup>(4)</sup> | DDRD6-DDRD0      | Pin       | PTD6-PTD0 <sup>(3)</sup> |

| 0          | 0        | Х                | Input, Hi-Z <sup>(2)</sup>            | DDRD6-DDRD0      | Pin       | PTD6-PTD0 <sup>(3)</sup> |

| Х          | 1        | X                | Output                                | DDRD6-DDRD0      | PTD6-PTD0 | PTD6-PTD0                |

#### Notes:

- 1. X = Don't care

- 2. Hi-Z = High impedance

- 3. Writing affects data register, but does not affect input.

- 4. I/O pin pulled up to V<sub>DD</sub> by internal pullup device.

**Serial Communications Interface (SCI)**

Semiconductor, Inc.

reescale

### Freescale Semiconductor, Inc.

## **Serial Peripheral Interface (SPI)**

#### 20.3 Features

Features of the SPI module include:

- Full-duplex operation

- Master and slave modes

- Double-buffered operation with separate transmit and receive registers

- Four master mode frequencies (maximum = bus frequency ÷ 2)

- Maximum slave mode frequency = bus frequency

- Serial clock with programmable polarity and phase

- Two separately enabled interrupts:

- SPRF (SPI receiver full)

- SPTE (SPI transmitter empty)

- Mode fault error flag with CPU interrupt capability

- Overflow error flag with CPU interrupt capability

- Programmable wired-OR mode

- I<sup>2</sup>C (inter-integrated circuit) compatibility

- I/O (input/output) port bit(s) software configurable with pullup device(s) if configured as input port bit(s)

## 20.4 Pin Name Conventions and I/O Register Addresses

The text that follows describes the SPI. The SPI I/O pin names are SS (slave select), SPSCK (SPI serial clock), CGND (clock ground), MOSI (master out slave in), and MISO (master in/slave out). The SPI shares four I/O pins with four parallel I/O ports.

Serial Peripheral Interface (SPI) Functional Description

The full names of the SPI I/O pins are shown in Table 20-1. The generic pin names appear in the text that follows.

**Table 20-1. Pin Name Conventions**

| SPI Generio<br>Pin Names | I IVIISO |           | MOSI                  | SS | SPSCK      | CGND            |

|--------------------------|----------|-----------|-----------------------|----|------------|-----------------|

| Full SPI<br>Pin Names:   | SPI      | PTD1/ATD9 | PTD1/ATD9 PTD2/ATD1 0 |    | PTD3/ATD11 | V <sub>SS</sub> |

## 20.5 Functional Description

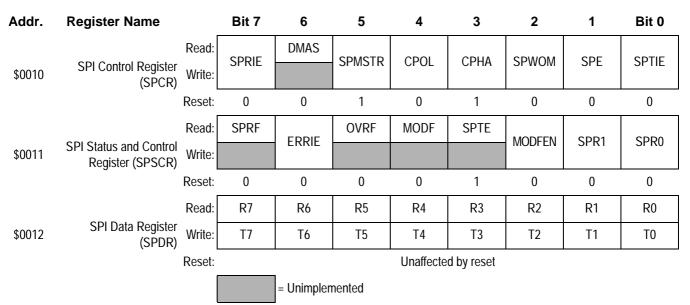

Figure 20-1 summarizes the SPI I/O registers and Figure 20-2 shows the structure of the SPI module.

Figure 20-1. SPI I/O Register Summary

MC68HC908GR8 — Rev 4.0

**Technical Data**

Go to: www.freescale.com

Serial Peripheral Interface (SPI)

Transmission Formats

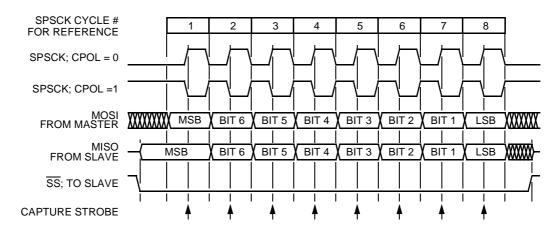

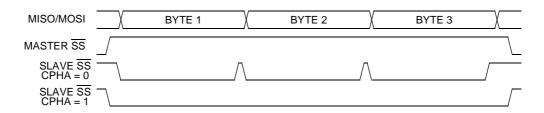

Figure 20-4. Transmission Format (CPHA = 0)

Figure 20-5. CPHA/SS Timing

When CPHA = 0 for a slave, the falling edge of  $\overline{SS}$  indicates the beginning of the transmission. This causes the SPI to leave its idle state and begin driving the MISO pin with the MSB of its data. Once the transmission begins, no new data is allowed into the shift register from the transmit data register. Therefore, the SPI data register of the slave must be loaded with transmit data before the falling edge of  $\overline{SS}$ . Any data written after the falling edge is stored in the transmit data register and transferred to the shift register after the current transmission.

#### 20.6.3 Transmission Format When CPHA = 1

Figure 20-6 shows an SPI transmission in which CPHA is logic 1. The figure should not be used as a replacement for data sheet parametric information. Two waveforms are shown for SPSCK: one for CPOL = 0 and another for CPOL = 1. The diagram may be interpreted as a master or slave timing diagram since the serial clock (SPSCK), master in/slave

MC68HC908GR8 — Rev 4.0

### **Timebase Module (TBM)**

**NOTE:** Do not change TBR2–TBR0 bits while the timebase is enabled (TBON = 1).

TACK— Timebase ACKnowledge

The TACK bit is a write-only bit and always reads as 0. Writing a logic 1 to this bit clears TBIF, the timebase interrupt flag bit. Writing a logic 0 to this bit has no effect.

- 1 = Clear timebase interrupt flag

- 0 = No effect

#### TBIE — Timebase Interrupt Enabled

This read/write bit enables the timebase interrupt when the TBIF bit becomes set. Reset clears the TBIE bit.

- 1 = Timebase interrupt enabled

- 0 = Timebase interrupt disabled

#### TBON — Timebase Enabled

This read/write bit enables the timebase. Timebase may be turned off to reduce power consumption when its function is not necessary. The counter can be initialized by clearing and then setting this bit. Reset clears the TBON bit.

- 1 = Timebase enabled

- 0 = Timebase disabled and the counter initialized to 0s

## 21.6 Interrupts

The timebase module can interrupt the CPU on a regular basis with a rate defined by TBR2:TBR0. When the timebase counter chain rolls over, the TBIF flag is set. If the TBIE bit is set, enabling the timebase interrupt, the counter chain overflow will generate a CPU interrupt request.

Interrupts must be acknowledged by writing a logic 1 to the TACK bit.

### **Timer Interface Module (TIM)**

| Addr.  | Register Name                                    |                 | Bit 7  | 6         | 5      | 4                  | 3              | 2     | 1    | Bit 0  |

|--------|--------------------------------------------------|-----------------|--------|-----------|--------|--------------------|----------------|-------|------|--------|

|        | Times 2 Country Desister                         | Read:           | Bit 7  | 6         | 5      | 4                  | 3              | 2     | 1    | Bit 0  |

| \$002D | OO2D Timer 2 Counter Register<br>Low (T2CNTL)    |                 |        |           |        |                    |                |       |      |        |

|        | LOW (TZCIVIL)                                    | Reset:          | 0      | 0         | 0      | 0                  | 0              | 0     | 0    | 0      |

| \$002E | Timer 2 Counter Modulo<br>Register High (T2MODH) | Read:<br>Write: | Bit 15 | 14        | 13     | 12                 | 11             | 10    | 9    | Bit 8  |

|        | Register High (12MODH)                           | Reset:          | 1      | 1         | 1      | 1                  | 1              | 1     | 1    | 1      |

| \$002F | Timer 2 Counter Modulo<br>Register Low (T2MODL)  | Read:<br>Write: | Bit 7  | 6         | 5      | 4                  | 3              | 2     | 1    | Bit 0  |

|        | Register Low (121110DL)                          | Reset:          | 1      | 1         | 1      | 1                  | 1              | 1     | 1    | 1      |

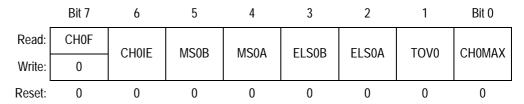

|        | Timer 2 Channel 0 Status                         | Read:           | CH0F   | CH0IE     | MS0B   | MS0A               | ELS0B          | ELS0A | TOV0 | CHOMAX |

| \$0030 | and Control Register                             |                 | 0      | CITOIL    | IVIOUD | IVIJUA             | LLJUD          | LLJUA | 1000 | CHOWAX |

|        | (T2SC0)                                          | Reset:          | 0      | 0         | 0      | 0                  | 0              | 0     | 0    | 0      |

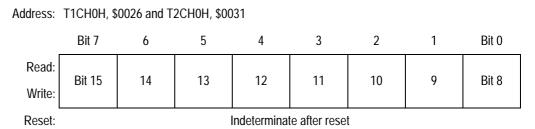

| \$0031 | Timer 2 Channel 0<br>Register High (T2CH0H)      | Read:<br>Write: | Bit 15 | 14        | 13     | 12                 | 11             | 10    | 9    | Bit 8  |

|        | Register High (120Hoff)                          | Reset:          |        |           |        | Indetermina        | te after reset |       |      |        |

| \$0032 | Timer 2 Channel 0<br>Register Low (T2CH0L)       | Read:<br>Write: | Bit 7  | 6         | 5      | 4                  | 3              | 2     | 1    | Bit 0  |

|        | Register Low (12C110L)                           | Reset:          |        |           |        | Indetermina        | te after reset |       |      |        |

|        |                                                  | Read:           |        |           |        |                    |                |       |      |        |

| \$0033 | Unimplemented                                    | Write:          |        |           |        |                    |                |       |      |        |

|        |                                                  | Reset:          | 0      | 0         | 0      | 0                  | 0              | 0     | 0    | 0      |

|        |                                                  | Read:           |        |           |        |                    |                |       |      |        |

| \$0034 | Unimplemented                                    | Write:          |        |           |        |                    |                |       |      |        |

|        |                                                  | Reset:          |        |           |        | <u>Indetermina</u> | te after reset |       |      |        |

|        |                                                  | Read:           |        |           |        |                    |                |       |      |        |

| \$0035 | Unimplemented                                    |                 |        |           |        |                    |                |       |      |        |

|        |                                                  | Reset:          |        | ı         |        | Indetermina        | te after reset |       |      |        |

|        |                                                  |                 |        | = Unimple | mented |                    |                |       |      |        |

Figure 22-2. TIM I/O Register Summary (Sheet 2 of 2)

#### 22.5.1 TIM Counter Prescaler

The TIM clock source can be one of the seven prescaler outputs or the TIM clock pin, TCLK. The prescaler generates seven clock rates from the internal bus clock. The prescaler select bits, PS[2:0], in the TIM status and control register select the TIM clock source.

Timer Interface Module (TIM)

I/O Registers

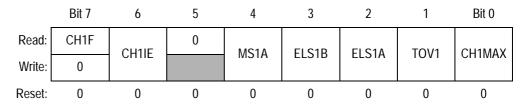

### 22.10.5 TIM Channel Status and Control Registers

Each of the TIM channel status and control registers:

- Flags input captures and output compares

- Enables input capture and output compare interrupts

- Selects input capture, output compare, or PWM operation

- Selects high, low, or toggling output on output compare

- Selects rising edge, falling edge, or any edge as the active input capture trigger

- Selects output toggling on TIM overflow

- Selects 0% and 100% PWM duty cycle

- Selects buffered or unbuffered output compare/PWM operation

Address: T1SC0, \$0025 and T2SC0, \$0030

Figure 22-11. TIM Channel 0 Status and Control Register (TSC0)

Address: T1SC1, \$0028

Figure 22-12. TIM Channel 1 Status and Control Register (TSC1)

MC68HC908GR8 — Rev 4.0

## **Timer Interface Module (TIM)**

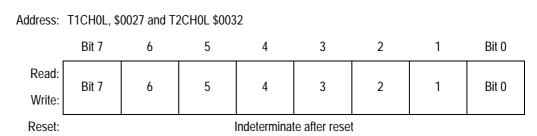

Figure 22-14. TIM Channel 0 Register High (TCH0H)

Figure 22-15. TIM Channel 0 Register Low (TCH0L)

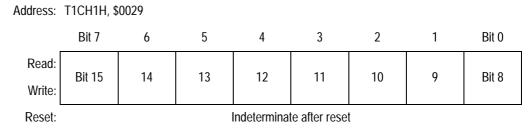

Figure 22-16. TIM Channel 1 Register High (TCH1H)

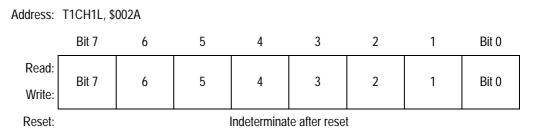

Figure 22-17. TIM Channel 1 Register Low (TCH1L)

## **Ordering Information**

### 25.3 MC Order Numbers

**Table 25-1. MC Order Numbers**

|                  | MC Order Number <sup>(1)</sup>                                                                                                                               | Operating<br>Temperature Range<br>(°C)                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Production Parts | MC68HC908GR8CP MC68HC908GR8CFA MC68HC908GR8CDW MC68HC908GR8VFA MC68HC908GR8VP MC68HC908GR8VDW MC68HC908GR8MFA MC68HC908GR8MP MC68HC908GR8MDW                 | - 40 to + 85<br>- 40 to + 85<br>- 40 to + 85<br>- 40 to + 105<br>- 40 to + 105<br>- 40 to + 105<br>- 40 to + 125<br>- 40 to + 125<br>- 40 to + 125 |

|                  | MC68HC908GR4CP MC68HC908GR4CFA MC68HC908GR4CDW MC68HC908GR4VFA MC68HC908GR4VP MC68HC908GR4VDW MC68HC908GR4WFA MC68HC908GR4MFA MC68HC908GR4MP MC68HC908GR4MDW | - 40 to + 85<br>- 40 to + 85<br>- 40 to + 85<br>- 40 to + 105<br>- 40 to + 105<br>- 40 to + 105<br>- 40 to + 125<br>- 40 to + 125<br>- 40 to + 125 |

| Tape and Reel    | MC908GR8CFAR2<br>MC908GR8CDWR2<br>MC908GR8VFAR2<br>MC908GR8VDWR2<br>MC908GR8MFAR2<br>MC908GR8MDWR2                                                           | - 40 to + 85<br>- 40 to + 85<br>- 40 to + 105<br>- 40 to + 105<br>- 40 to + 125<br>- 40 to + 125                                                   |

| Tapo ana ricor   | MC908GR4CFAR2<br>MC908GR4CDWR2<br>MC908GR4VFAR2<br>MC908GR4VDWR2<br>MC908GR4MFAR2<br>MC908GR4MDWR2                                                           | - 40 to + 85<br>- 40 to + 85<br>- 40 to + 105<br>- 40 to + 105<br>- 40 to + 125<br>- 40 to + 125                                                   |

<sup>1.</sup> FA = quad flat pack

P = plastic dual in line package

DW = Small outline integrated circuit (SOIC) package