Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                      |

|----------------------------|-------------------------------------------------------------|

| Core Processor             | HC08                                                        |

| Core Size                  | 8-Bit                                                       |

| Speed                      | 8MHz                                                        |

| Connectivity               | SCI, SPI                                                    |

| Peripherals                | LVD, POR, PWM                                               |

| Number of I/O              | 21                                                          |

| Program Memory Size        | 7.5KB (7.5K x 8)                                            |

| Program Memory Type        | FLASH                                                       |

| EEPROM Size                | -                                                           |

| RAM Size                   | 384 x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                 |

| Data Converters            | A/D 6x8b                                                    |

| Oscillator Type            | Internal                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                          |

| Mounting Type              | Surface Mount                                               |

| Package / Case             | 32-LQFP                                                     |

| Supplier Device Package    | 32-LQFP (7x7)                                               |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mchc908gr8mfae |

|                            |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Technical Data — MC68HC908GR8

# **Table of Contents**

## **List of Paragraphs**

### **Table of Contents**

## **List of Tables**

## **List of Figures**

## **Section 1. General Description**

| 1.1 | Contents          |

|-----|-------------------|

| 1.2 | Introduction      |

| 1.3 | Features          |

| 1.4 | MCU Block Diagram |

| 1.5 | Pin Assignments   |

| 1.6 | Pin Functions     |

## Section 2. Memory Map

| 2.1 | Contents                       |

|-----|--------------------------------|

| 2.2 | Introduction                   |

| 2.3 | Unimplemented Memory Locations |

| 2.4 | Reserved Memory Locations      |

| 2.5 | Input/Output (I/O) Section     |

## **Table of Contents**

| 23.16 | Clock Generation Module Characteristics |  |

|-------|-----------------------------------------|--|

| 23.17 | Memory Characteristics                  |  |

## Section 24. Mechanical Specifications

| 24.1 | Contents                   | 37             |

|------|----------------------------|----------------|

| 24.2 |                            | 37             |

| 24.3 | 32-Pin LQFP (Case #873A)38 | 38             |

| 24.4 | 28-Pin PDIP (Case #710)    | 39             |

| 24.5 | 28-Pin SOIC (Case #751F)   | <del>3</del> 0 |

## Section 25. Ordering Information

| 25.1 | Contents          |

|------|-------------------|

| 25.2 | Introduction      |

| 25.3 | MC Order Numbers  |

| 25.4 | Development Tools |

### Glossary

## **Revision History**

| Contents                                                                             |

|--------------------------------------------------------------------------------------|

| Introduction                                                                         |

| Changes from Rev 3.0 published in February 2002 to Rev 4.0 published in June 2002    |

| Changes from Rev 2.0 published in January 2002 to Rev 3.0 published in February 2002 |

| Changes from Rev 1.0 published in April 2001 to Rev 2.0 published in December 2001   |

MOTOROLA

- 7680 bytes of on-chip FLASH memory on the MC68HC908GR8 and 4096 bytes of on-chip FLASH memory on the MC68HC908GR4 with in-circuit programming capabilities of FLASH program memory

- 384 bytes of on-chip random-access memory (RAM)

- Serial peripheral interface module (SPI)

- Serial communications interface module (SCI)

- One 16-bit, 2-channel timer (TIM1) and one 16-bit, 1-channel timer (TIM2) interface modules with selectable input capture, output compare, and PWM capability on each channel

- 6-channel, 8-bit successive approximation analog-to-digital converter (ADC)

- BREAK module (BRK) to allow single breakpoint setting during incircuit debugging

- Internal pullups on IRQ and RST to reduce customer system cost

- Clock generator module with on-chip 32-kHz crystal compatible PLL (phase-lock loop)

- Up to 21 general-purpose input/output (I/O) pins, including:

- 19 shared-function I/O pins

- Up to two dedicated I/O pins, depending on package choice

- Selectable pullups on inputs only on ports A, C, and D. Selection is on an individual port bit basis. During output mode, pullups are disengaged.

- High current 10-mA sink/10-mA source capability on all port pins

- Higher current 15-mA sink/source capability on PTC0–PTC1

- Timebase module with clock prescaler circuitry for eight user selectable periodic real-time interrupts with optional active clock source during stop mode for periodic wakeup from stop using an external 32-kHz crystal

- Oscillator stop mode enable bit (OSCSTOPENB) in the CONFIG register to allow user selection of having the oscillator enabled or disabled during stop mode

## Low Power Modes

- Low-voltage inhibit (LVI) reset A power supply voltage below the LVI<sub>tripf</sub> voltage resets the MCU and loads the program counter with the contents of locations \$FFFE and \$FFFF.

- Break interrupt A break interrupt loads the program counter with the contents of locations \$FFFC and \$FFFD.

- Timebase module (TBM) interrupt A TBM interrupt loads the program counter with the contents of locations \$FFDC and \$FFDD when the timebase counter has rolled over. This allows the TBM to generate a periodic wakeup from stop mode.

Upon exit from stop mode, the system clocks begin running after an oscillator stabilization delay. A 12-bit stop recovery counter inhibits the system clocks for 4096 CGMXCLK cycles after the reset or external interrupt.

The short stop recovery bit, SSREC, in the configuration register controls the oscillator stabilization delay during stop recovery. Setting SSREC reduces stop recovery time from 4096 CGMXCLK cycles to 32 CGMXCLK cycles.

**NOTE:** Use the full stop recovery time (SSREC = 0) in applications that use an external crystal.

**Technical Data**

MC68HC908GR8 — Rev 4.0

MOTOROLA

## **Resets and Interrupts**

#### 4.3.3.3 Low-Voltage Inhibit Reset

A low-voltage inhibit (LVI) reset is an internal reset caused by a drop in the power supply voltage to the LVI trip voltage, V<sub>TRIPF</sub>.

An LVI reset:

- Holds the clocks to the CPU and modules inactive for an oscillator stabilization delay of 4096 CGMXCLK cycles after the power supply voltage rises to V<sub>TRIPF</sub>

- Drives the  $\overline{RST}$  pin low for as long as  $V_{DD}$  is below  $V_{TRIPF}$  and during the oscillator stabilization delay

- Releases the RST pin 32 CGMXCLK cycles after the oscillator stabilization delay

- Releases the CPU to begin the reset vector sequence

64 CGMXCLK cycles after the oscillator stabilization delay

- Sets the LVI bit in the SIM reset status register

### 4.3.3.4 Illegal Opcode Reset

An illegal opcode reset is an internal reset caused by an opcode that is not in the instruction set. An illegal opcode reset sets the ILOP bit in the SIM reset status register.

If the stop enable bit, STOP, in the mask option register is a logic 0, the STOP instruction causes an illegal opcode reset.

### 4.3.3.5 Illegal Address Reset

An illegal address reset is an internal reset caused by opcode fetch from an unmapped address. An illegal address reset sets the ILAD bit in the SIM reset status register.

A data fetch from an unmapped address does not generate a reset.

Technical Data

MC68HC908GR8 — Rev 4.0

MOTOROLA

# Section 5. Analog-to-Digital Converter (ADC)

## 5.1 Contents

| 5.2 | Introduction             |

|-----|--------------------------|

| 5.3 | Features                 |

| 5.4 | Functional Description80 |

| 5.5 | Interrupts               |

| 5.6 | Low-Power Modes          |

| 5.7 | I/O Signals              |

| 5.8 | I/O Registers            |

## 5.2 Introduction

This section describes the 8-bit analog-to-digital converter (ADC).

For further information regarding analog-to-digital converters on Motorola microcontrollers, please consult the HC08 ADC Reference Manual, ADCRM/AD.

**Technical Data**

BW — Break Wait Bit

This read/write bit is set when a break interrupt causes an exit from wait mode. Clear BW by writing a logic 0 to it. Reset clears BW.

- 1 = Break interrupt during wait mode

- 0 = No break interrupt during wait mode

BW can be read within the break interrupt routine. The user can modify the return address on the stack by subtracting 1 from it. The following code is an example.

This code works if the H register was stacked in the break interrupt routine. Execute this code at the end of the break interrupt routine.

|   | HIBYTE | EQU         | 5              |                                                           |

|---|--------|-------------|----------------|-----------------------------------------------------------|

|   | LOBYTE | EQU         | 6              |                                                           |

| ; |        | If not      | BW, do RTI     |                                                           |

|   |        | BRCLR       | BW,BSR, RETURN | ; See if wait mode or stop mode<br>; was exited by break. |

|   |        | TST         | LOBYTE, SP     | ; If RETURNLO is not 0,                                   |

|   |        | BNE         | DOLO           | ; then just decrement low byte.                           |

|   |        | DEC         | HIBYTE,SP      | ; Else deal with high byte also.                          |

|   | DOLO   | DEC         | LOBYTE, SP     | ; Point to WAIT/STOP opcode.                              |

|   | RETURN | PULH<br>RTI |                | ; Restore H register.                                     |

MC68HC908GR8 - Rev 4.0

Technical Data

## **Computer Operating Properly (COP)**

### 9.4.6 Reset Vector Fetch

A reset vector fetch occurs when the vector address appears on the data bus. A reset vector fetch clears the COP prescaler.

### 9.4.7 COPD (COP Disable)

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register. See Configuration Register (CONFIG).

### 9.4.8 COPRS (COP Rate Select)

The COPRS signal reflects the state of the COP rate select bit (COPRS) in the configuration register. See Configuration Register (CONFIG).

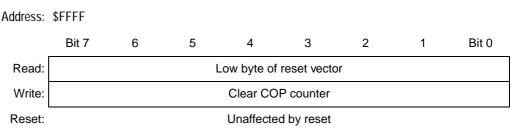

### 9.5 COP Control Register

The COP control register is located at address \$FFFF and overlaps the reset vector. Writing any value to \$FFFF clears the COP counter and starts a new timeout period. Reading location \$FFFF returns the low byte of the reset vector.

### 9.6 Interrupts

The COP does not generate CPU interrupt requests.

Technical Data

|                              | DECET                                     | \$FFFE/       | DU            | DTDA          | DTD1  | External             |               | Bus           | СОР      | For Serial<br>Communication |      |                                 |                                                                     |          |   |   |

|------------------------------|-------------------------------------------|---------------|---------------|---------------|-------|----------------------|---------------|---------------|----------|-----------------------------|------|---------------------------------|---------------------------------------------------------------------|----------|---|---|

| IRQ                          | RESET                                     | \$FFFF        | PLL           | PTB0          | PTB1  | Clock <sup>(1)</sup> | CGMOUT        | Freq          |          | PTA0                        | PTA1 | Baud<br>Rate <sup>(2) (3)</sup> | Comment                                                             |          |   |   |

| Х                            | GND                                       | Х             | Х             | Х             | Х     | Х                    | 0             | 0             | Disabled | Х                           | Х    | 0                               | No operation until reset goes high                                  |          |   |   |

|                              | V <sub>DD</sub>                           |               |               |               |       |                      | 4 9 4 5 9     | 0 4574        |          | 1                           | 0    | 9600                            | PTB0 and PTB1                                                       |          |   |   |

| V <sub>TST</sub>             | or<br>V <sub>TST</sub>                    | Х             | OFF           | 1             | 0     | 9.8304<br>MHz        | 4.9152<br>MHz | 2.4576<br>MHz | Disabled | х                           | 1    | DNA                             | voltages only<br><u>req</u> uired if<br>IRQ = V <sub>TST</sub>      |          |   |   |

| V                            | V <sub>DD</sub>                           | \$FFFF        | 055           |               | х     | 9.8304               | 4.9152        | 2.4576        | D: 11 1  | 1                           | 0    | 9600                            | External frequency                                                  |          |   |   |

| V <sub>DD</sub>              |                                           |               | <b>⊅</b> гггг | <b>Э</b> ГГГГ | эгггг | <b>Э</b> ГГГГ        | φΓΓΓΓ         | OFF           | Х        | ^                           | MHz  | MHz                             | MHz                                                                 | Disabled | Х | 1 |

|                              | N                                         | *===          | 0.1           | N             | N     | 32.768               | 4.9152        | 2.4576        | <b>D</b> | 1                           | 0    | 9600                            | PLL enabled (BCS                                                    |          |   |   |

| GND                          | V <sub>DD</sub>                           | \$FFFF        | ON            | Х             | Х     | kHz                  | MHz           | MHz           | Disabled | Х                           | 1    | DNA                             | set) in monitor<br>code                                             |          |   |   |

| V <sub>DD</sub><br>or<br>GND | V <sub>TST</sub>                          | \$FFFF        | OFF           | х             | х     | Х                    | _             | _             | Enabled  | х                           | х    | _                               | Enters user mode<br>— will encounter<br>an illegal address<br>reset |          |   |   |

| V <sub>DD</sub><br>or<br>GND | V <sub>DD</sub><br>or<br>V <sub>TST</sub> | Not<br>\$FFFF | OFF           | Х             | Х     | х                    | _             | _             | Enabled  | х                           | Х    | _                               | Enters user mode                                                    |          |   |   |

### Table 15-1. Monitor Mode Signal Requirements and Options

Notes:

1. External clock is derived by a 32.768 kHz crystal or a 9.8304 MHz off-chip oscillator

2. PTA0 = 1 if serial communication; PTA0 = X if parallel communication

3. PTA1 = 0  $\rightarrow$  serial, PTA1 = 1  $\rightarrow$  parallel communication for security code entry

4. DNA = does not apply, X = don't care

If entering monitor mode with  $V_{TST}$  applied on IRQ (condition set 1), the CGMOUT frequency is equal to the CGMXCLK frequency and the OSC1 input directly generates internal bus clocks. In this case, the OSC1 signal must have a 50% duty cycle at maximum bus frequency.

If entering monitor mode without high voltage applied on IRQ (condition set 2 or 3, where applied voltage is either  $V_{DD}$  or  $V_{SS}),$  then all port B pin

MC68HC908GR8 - Rev 4.0

MOTOROLA

**Technical Data**

## Input/Output Ports (I/O)

| Addr.  | Register Name                       |        | Bit 7                      | 6     | 5     | 4         | 3           | 2     | 1     | Bit 0 |  |  |

|--------|-------------------------------------|--------|----------------------------|-------|-------|-----------|-------------|-------|-------|-------|--|--|

|        |                                     | Read:  | 0                          | 0     | 0     | 0         | PTA3        | PTA2  | PTA1  | PTA0  |  |  |

| \$0000 | Port A Data Register<br>(PTA)       | Write: |                            |       |       |           | FTAJ        | FTAZ  | PIAI  | FTAU  |  |  |

|        |                                     | Reset: | eset: Unaffected by reset  |       |       |           |             |       |       |       |  |  |

|        |                                     | Read:  | 0                          | 0     | PTB5  | PTB4      | PTB3        | PTB2  | PTB1  | PTB0  |  |  |

| \$0001 | Port B Data Register<br>(PTB)       | Write: |                            |       | FIDJ  | FTD4      | PID3        | FIDZ  | 1101  | FIDU  |  |  |

|        |                                     | Reset: |                            |       |       | Unaffecte |             |       |       |       |  |  |

|        |                                     | Read:  | 0                          | 0     | 0     | 0         | 0           | 0     | PTC1  | PTC0  |  |  |

| \$0002 | Port C Data Register<br>(PTC)       | Write: |                            |       |       |           |             |       | FICI  | FICU  |  |  |

|        | · · ·                               | Reset: |                            |       |       | Unaffecte | d by reset  |       |       |       |  |  |

|        |                                     | Read:  | 0                          | PTD6  | PTD5  | PTD4      | PTD3        | PTD2  | PTD1  | PTD0  |  |  |

| \$0003 | Port D Data Register<br>(PTD)       | Write: |                            |       |       |           |             |       |       |       |  |  |

|        | ( )                                 |        | Reset: Unaffected by reset |       |       |           |             |       |       |       |  |  |

|        | Data Direction Register A<br>(DDRA) | Read:  | 0                          | 0     | 0     | 0         | DDRA3       | DDRA2 | DDRA1 | DDRA0 |  |  |

| \$0004 |                                     | Write: |                            |       |       |           | DDKAJ       | DUKAZ | DUKAT | DDRAU |  |  |

|        |                                     | Reset: | 0                          | 0     | 0     | 0         | 0           | 0     | 0     | 0     |  |  |

|        |                                     | Read:  | 0                          | 0     | DDRB5 | עססס      | נסטט        | נפסחס | DDRB1 | ספטטט |  |  |

| \$0005 | Data Direction Register B<br>(DDRB) | Write: |                            |       | DDKR2 | DDRB4     | DDRB3       | DDRB2 | DUKBI | DDRB0 |  |  |

|        | · · · ·                             | Reset: | 0                          | 0     | 0     | 0         | 0           | 0     | 0     | 0     |  |  |

|        |                                     | Read:  | 0                          | 0     | 0     | 0         | 0           | 0     | DDRC1 | DDRC0 |  |  |

| \$0006 | Data Direction Register C<br>(DDRC) | Write: |                            |       |       |           |             |       | DDRCI | DDRCU |  |  |

|        | ()                                  | Reset: | 0                          | 0     | 0     | 0         | 0           | 0     | 0     | 0     |  |  |

|        |                                     | Read:  | 0                          |       | DDDDF |           | 00001       | DDRD2 |       |       |  |  |

| \$0007 | Data Direction Register D<br>(DDRD) | Write: |                            | DDRD6 | DDRD5 | 100KU4    | DDRD4 DDRD3 |       | DDRD1 | DDRD0 |  |  |

|        | (2210)                              | Reset: | 0                          | 0     | 0     | 0         | 0           | 0     | 0     | 0     |  |  |

|        | = Unimplemented                     |        |                            |       |       |           |             |       |       |       |  |  |

|        |                                     |        | 10                         |       |       |           |             |       |       |       |  |  |

Figure 16-1. I/O Port Register Summary

## Input/Output Ports (I/O)

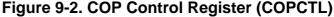

## 16.5 Port C

Port C is a 2-bit, general-purpose bidirectional I/O port. Port C also has software configurable pullup devices if configured as an input port.

#### 16.5.1 Port C Data Register

The port C data register (PTC) contains a data latch for each of the two port C pins.

PTC1-PTC0 - Port C Data Bits

These read/write bits are software-programmable. Data direction of each port C pin is under the control of the corresponding bit in data direction register C. Reset has no effect on port C data.

NOTE: PTC is not available in a 28-pin DIP and SOIC package

MC68HC908GR8 - Rev 4.0

216

### T1CH1 and T1CH0 — Timer 1 Channel I/O Bits

The PTD5/T1CH1–PTD4/T1CH0 pins are the TIM1 input capture/output compare pins. The edge/level select bits, ELSxB and ELSxA, determine whether the PTD5/T1CH1–PTD4/T1CH0 pins are timer channel I/O pins or general-purpose I/O pins. See Timer Interface Module (TIM).

### SPSCK — SPI Serial Clock

The PTD3/SPSCK pin is the serial clock input of the SPI module. When the SPE bit is clear, the PTD3/SPSCK pin is available for general-purpose I/O.

### MOSI - Master Out/Slave In

The PTD2/MOSI pin is the master out/slave in terminal of the SPI module. When the SPE bit is clear, the PTD2/MOSI pin is available for general-purpose I/O.

### MISO — Master In/Slave Out

The PTD1/MISO pin is the master in/slave out terminal of the SPI module. When the SPI enable bit, SPE, is clear, the SPI module is disabled, and the PTD0/ $\overline{SS}$  pin is available for general-purpose I/O.

Data direction register D (DDRD) does not affect the data direction of port D pins that are being used by the SPI module. However, the DDRD bits always determine whether reading port D returns the states of the latches or the states of the pins. See Table 16-5.

## SS — Slave Select

The PTD0/SS pin is the slave select input of the SPI module. When the SPE bit is clear, or when the SPI master bit, SPMSTR, is set, the PTD0/SS pin is available for general-purpose I/O. When the SPI is enabled, the DDRB0 bit in data direction register B (DDRB) has no effect on the PTD0/SS pin.

## Input/Output Ports (I/O)

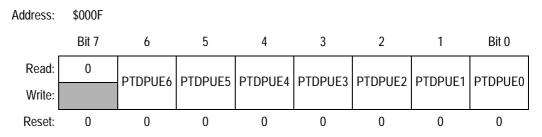

#### 16.6.3 Port D Input Pullup Enable Register

The port D input pullup enable register (PTDPUE) contains a software configurable pullup device for each of the seven port D pins. Each bit is individually configurable and requires that the data direction register, DDRD, bit be configured as an input. Each pullup is automatically and dynamically disabled when a port bit's DDRD is configured for output mode.

Figure 16-16. Port D Input Pullup Enable Register (PTDPUE)

PTDPUE6-PTDPUE0 - Port D Input Pullup Enable Bits

These writeable bits are software programmable to enable pullup devices on an input port bit.

- 1 = Corresponding port D pin configured to have internal pullup

- 0 = Corresponding port D pin has internal pullup disconnected

**Technical Data**

## Serial Communications Interface (SCI)

### 18.5.2.5 Inversion of Transmitted Output

The transmit inversion bit (TXINV) in SCI control register 1 (SCC1) reverses the polarity of transmitted data. All transmitted values, including idle, break, start, and stop bits, are inverted when TXINV is at logic 1. See SCI Control Register 1.

### 18.5.2.6 Transmitter Interrupts

These conditions can generate CPU interrupt requests from the SCI transmitter:

- SCI transmitter empty (SCTE) The SCTE bit in SCS1 indicates that the SCDR has transferred a character to the transmit shift register. SCTE can generate a transmitter CPU interrupt request. Setting the SCI transmit interrupt enable bit, SCTIE, in SCC2 enables the SCTE bit to generate transmitter CPU interrupt requests.

- Transmission complete (TC) The TC bit in SCS1 indicates that the transmit shift register and the SCDR are empty and that no break or idle character has been generated. The transmission complete interrupt enable bit, TCIE, in SCC2 enables the TC bit to generate transmitter CPU interrupt requests.

### 18.5.3 Receiver

Figure 18-5 shows the structure of the SCI receiver.

### 18.5.3.1 Character Length

The receiver can accommodate either 8-bit or 9-bit data. The state of the M bit in SCI control register 1 (SCC1) determines character length. When receiving 9-bit data, bit R8 in SCI control register 2 (SCC2) is the ninth bit (bit 8). When receiving 8-bit data, bit R8 is a copy of the eighth bit (bit 7).

MC68HC908GR8 — Rev 4.0

reescale

## System Integration Module (SIM)

#### 19.8.1 SIM Break Status Register

The SIM break status register (SBSR) contains a flag to indicate that a break caused an exit from stop mode or wait mode.

Address: \$FE00

|        | Bit 7 | 6          | 5 | 4 | 3 | 2 | 1                   | Bit 0 |  |  |

|--------|-------|------------|---|---|---|---|---------------------|-------|--|--|

| Read:  | R     | R          | R | R | R | R | SBSW                | R     |  |  |

| Write: | ĸ     |            | ĸ | ĸ | ĸ | K | Note <sup>(1)</sup> | N     |  |  |

| Reset: | 0     | 0          | 0 | 0 | 0 | 0 | 0                   | 0     |  |  |

|        | R     | = Reserved |   |   |   |   |                     |       |  |  |

Note: 1. Writing a logic 0 clears SBSW.

### Figure 19-20. SIM Break Status Register (SBSR)

SBSW - SIM Break Stop/Wait

This status bit is useful in applications requiring a return to wait or stop mode after exiting from a break interrupt. Clear SBSW by writing a logic 0 to it. Reset clears SBSW.

- 1 = Stop mode or wait mode was exited by break interrupt.

- 0 = Stop mode or wait mode was not exited by break interrupt.

SBSW can be read within the break state SWI routine. The user can modify the return address on the stack by subtracting one from it. The following code is an example of this. Writing 0 to the SBSW bit clears it.

This code works if the H register has been pushed onto the stack in the break service routine software. This code should be executed at the end of the break service routine software.

| HIBYTE | EQU                 | 5                 | ;                                                    |

|--------|---------------------|-------------------|------------------------------------------------------|

| LOBYTE | EQU                 | 6                 | ;                                                    |

|        | If not SBSW, do RTI |                   | ;                                                    |

|        | BRCLR               | SBSW,SBSR, RETURN | ;See if wait mode or stop mode was exited by ;break. |

|        | TST                 | LOBYTE, SP        | ;If RETURNLO is not zero,                            |

|        | BNE                 | DOLO              | ;then just decrement low byte.                       |

# Section 20. Serial Peripheral Interface (SPI)

### 20.1 Contents

| 20.2  | Introduction                                    |

|-------|-------------------------------------------------|

| 20.3  | Features                                        |

| 20.4  | Pin Name Conventions and I/O Register Addresses |

| 20.5  | Functional Description                          |

| 20.6  | Transmission Formats                            |

| 20.7  | Queuing Transmission Data                       |

| 20.8  | Error Conditions                                |

| 20.9  | Interrupts                                      |

| 20.10 | Resetting the SPI                               |

| 20.11 | Low-Power Modes                                 |

| 20.12 | SPI During Break Interrupts                     |

| 20.13 | I/O Signals                                     |

| 20.14 | I/O Registers                                   |

### 20.2 Introduction

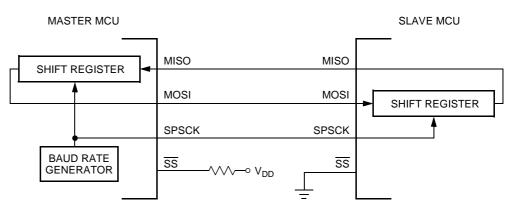

This section describes the serial peripheral interface (SPI) module, which allows full-duplex, synchronous, serial communications with peripheral devices.

The following paragraphs describe the operation of the SPI module.

### 20.5.1 Master Mode

The SPI operates in master mode when the SPI master bit, SPMSTR, is set.

**NOTE:** Configure the SPI modules as master or slave before enabling them. Enable the master SPI before enabling the slave SPI. Disable the slave SPI before disabling the master SPI. See SPI Control Register.

Only a master SPI module can initiate transmissions. Software begins the transmission from a master SPI module by writing to the transmit data register. If the shift register is empty, the byte immediately transfers to the shift register, setting the SPI transmitter empty bit, SPTE. The byte begins shifting out on the MOSI pin under the control of the serial clock. See Figure 20-3.

Figure 20-3. Full-Duplex Master-Slave Connections

### SPR1 and SPR0 — SPI Baud Rate Select Bits

In master mode, these read/write bits select one of four baud rates as shown in Table 20-4. SPR1 and SPR0 have no effect in slave mode. Reset clears SPR1 and SPR0.

### Table 20-4. SPI Master Baud Rate Selection

| SPR1 and SPR0 | Baud Rate Divisor (BD) |

|---------------|------------------------|

| 00            | 2                      |

| 01            | 8                      |

| 10            | 32                     |

| 11            | 128                    |

Use this formula to calculate the SPI baud rate:

Baud rate =

$$\frac{CGMOUT}{2 \times BD}$$

where:

CGMOUT = base clock output of the clock generator module (CGM) BD = baud rate divisor

MC68HC908GR8 - Rev 4.0

**Technical Data**

| Addr.                            | Register Name                                        |                  | Bit 7                     | 6               | 5           | 4         | 3     | 2            | 1    | Bit 0  |  |

|----------------------------------|------------------------------------------------------|------------------|---------------------------|-----------------|-------------|-----------|-------|--------------|------|--------|--|

| \$0020 Timer 1 Status and Contro |                                                      | Read:<br>Write:  | TOF<br>0                  | TOIE            | TSTOP       | 0<br>TRST | 0     | PS2          | PS1  | PS0    |  |

|                                  | Register (T1SC)                                      |                  | 0                         | 0               | 1           | 0         | 0     | 0            | 0    | 0      |  |

|                                  | T'                                                   | Read:            | Bit 15                    | 14              | 13          | 12        | 11    | 10           | 9    | Bit 8  |  |

| \$0021 IIr                       | Timer 1 Counter Register<br>High (T1CNTH)            | Write:           |                           |                 |             |           |       |              |      |        |  |

|                                  | nigir (Trowin)                                       | Reset:           | 0                         | 0               | 0           | 0         | 0     | 0            | 0    | 0      |  |

|                                  | Timer 1 Counter Register                             | Read:            | Bit 7                     | 6               | 5           | 4         | 3     | 2            | 1    | Bit 0  |  |

| \$0022                           | \$0022 Low (T1CNTL                                   | Write:           |                           |                 |             |           |       |              |      |        |  |

|                                  |                                                      | Reset:           | 0                         | 0               | 0           | 0         | 0     | 0            | 0    | 0      |  |

| \$0023                           | Timer 1 Counter Modulo<br>Register High (T1MODH)     | Read:<br>Write:  | Bit 15                    | 14              | 13          | 12        | 11    | 10           | 9    | Bit 8  |  |

|                                  |                                                      | Reset:           | 1                         | 1               | 1           | 1         | 1     | 1            | 1    | 1      |  |

| \$0024                           | Timer 1 Counter Modulo<br>Register Low (T1MODL)      | Read:<br>Write:  | Bit 7                     | 6               | 5           | 4         | 3     | 2            | 1    | Bit 0  |  |

|                                  | Register Low (T INODL)                               | Reset:           | 1                         | 1               | 1           | 1         | 1     | 1            | 1    | 1      |  |

| \$0025                           | Timer 1 Channel 0 Status<br>and Control Register     | Read:<br>Write:  | CH0F<br>0                 | CHOIE           | MS0B        | MS0A      | ELSOB | <b>ELSOA</b> | TOV0 | CHOMAX |  |

|                                  | (T1SC0)                                              | Reset:           | 0                         | 0               | 0           | 0         | 0     | 0            | 0    | 0      |  |

| \$0026                           | Timer 1 Channel 0                                    | Read:<br>Write:  | Bit 15                    | 14              | 13          | 12        | 11    | 10           | 9    | Bit 8  |  |

|                                  | Register High (T1CH0H)                               |                  | Indeterminate after reset |                 |             |           |       |              |      |        |  |

| \$0027                           | Timer 1 Channel 0                                    | Read:<br>Write:  | Bit 7                     | 6               | 5           | 4         | 3     | 2            | 1    | Bit 0  |  |

|                                  | Register Low (T1CH0L)                                | Reset:           | Indeterminate after reset |                 |             |           |       |              |      |        |  |

|                                  | Timer 1 Channel 1 Status                             | Read:            | CH1F                      | CH1IE           | 0           | MS1A      | ELS1B | ELS1A        | TOV1 | CH1MAX |  |

| \$0028                           | and Control Register                                 |                  | 0                         |                 |             |           |       |              |      |        |  |

|                                  | (T1SC1)                                              |                  | 0                         | 0               | 0           | 0         | 0     | 0            | 0    | 0      |  |

| \$0029                           | Timer 1 Channel 1<br>Register High (T1CH1H)          | Read:<br>Write:  | Bit 15                    | 14              | 13          | 12        | 11    | 10           | 9    | Bit 8  |  |

|                                  |                                                      | Reset:           | Indeterminate after reset |                 |             |           |       |              |      |        |  |

| \$002A                           | Timer 1 Channel 1<br>Register Low (T1CH1L)           | Read:<br>Write:  | Bit 7                     | 6               | 5           | 4         | 3     | 2            | 1    | Bit 0  |  |

|                                  |                                                      | Reset:           | Indeterminate after reset |                 |             |           |       |              |      |        |  |

|                                  | \$002B Timer 2 Status and Control<br>Register (T2SC) | Read:            | TOF                       | TOIE            | TSTOP       | 0         | 0     | PS2          | PS1  | PS0    |  |

| \$002B                           |                                                      | Write:<br>Reset: | 0                         |                 |             | TRST      |       |              |      |        |  |

|                                  | 10915101 (1200)                                      |                  | 0                         | 0               | 1           | 0         | 0     | 0            | 0    | 0      |  |

| #0000                            | Timer 2 Counter Register                             | Read:            | Bit 15                    | 14              | 13          | 12        | 11    | 10           | 9    | Bit 8  |  |

| \$002C                           | High (T2CNTH)                                        | Write:           | 0                         |                 |             |           |       | 0            |      |        |  |

|                                  |                                                      | Reset:           | 0                         | 0<br>I Linimpia | 0<br>montod | 0         | 0     | 0            | 0    | 0      |  |

| = Unimplemented                  |                                                      |                  |                           |                 |             |           |       |              |      |        |  |

### Figure 22-2 summarizes the timer registers.

Figure 22-2. TIM I/O Register Summary (Sheet 1 of 2)

## **Electrical Specifications**

## 23.5 5.0 V DC Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                         | Symbol           | Min                                            | Тур <sup>(2)</sup>  | Мах                   | Unit                 |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------|---------------------|-----------------------|----------------------|

| Output high voltage                                                                                                                   |                  |                                                |                     |                       |                      |

| $(I_{Load} = -2.0 \text{ mA})$ all I/O pins                                                                                           | V <sub>OH</sub>  | V <sub>DD</sub> – 0.8                          |                     |                       | V                    |

| (I <sub>Load</sub> = -10.0 mA) all I/O pins                                                                                           | V <sub>OH</sub>  | V <sub>DD</sub> – 1.5                          |                     |                       | V                    |

| (I <sub>Load</sub> = -10.0 mA) pins PTC0-PTC1 only                                                                                    | V <sub>OH</sub>  | V <sub>DD</sub> – 0.8                          | _                   |                       | V                    |

| Maximum combined I <sub>OH</sub> for port C, port E,<br>port PTD0–PTD3                                                                | I <sub>OH1</sub> | _                                              | —                   | 50                    | mA                   |

| Maximum combined I <sub>OH</sub> for port PTD4–PTD6,                                                                                  | I <sub>OH2</sub> | —                                              | —                   | 50                    | mA                   |

| port A, port B<br>Maximum total I <sub>OH</sub> for all port pins                                                                     | I <sub>OHT</sub> | _                                              | —                   | 100                   | mA                   |

| Output low voltage                                                                                                                    |                  |                                                |                     |                       |                      |

| (I <sub>Load</sub> = 1.6 mA) all I/O pins                                                                                             | V <sub>OL</sub>  | _                                              |                     | 0.4                   | V                    |

| (I <sub>Load</sub> = 10 mA) all I/O pins                                                                                              | V <sub>OL</sub>  | _                                              |                     | 1.5                   | v                    |

| (I <sub>Load</sub> = 15 mA) pins PTC0–PTC1 only                                                                                       | V <sub>OL</sub>  | —                                              | _                   | 1.0                   | V                    |

| Maximum combined I <sub>OL</sub> for port C, port E,<br>port PTD0–PTD3                                                                | I <sub>OL1</sub> | —                                              | _                   | 50                    | mA                   |

| Maximum combined I <sub>OL</sub> for port PTD4–PTD6,                                                                                  | I <sub>OL2</sub> | —                                              | —                   | 50                    | mA                   |

| port A, port B<br>Maximum total I <sub>OL</sub> for all port pins                                                                     | I <sub>OLT</sub> | _                                              | —                   | 100                   | mA                   |

| Input high voltage<br>All ports, IRQs, RESET<br>OSC1                                                                                  | V <sub>IH</sub>  | 0.7 x V <sub>DD</sub><br>0.8 x V <sub>DD</sub> | _                   | V <sub>DD</sub>       | V                    |

| Input low voltage<br>All ports, IRQs, RESET, OSC1                                                                                     | V <sub>IL</sub>  | V <sub>SS</sub>                                | _                   | 0.2 x V <sub>DD</sub> | V                    |

| V <sub>DD</sub> supply current<br>Run <sup>(3)</sup><br>Wait <sup>(4)</sup>                                                           | I <sub>DD</sub>  |                                                | 15<br>4             | 20<br>8               | mA<br>mA             |

| Stop <sup>(5)</sup> (<85 °C)<br>Stop (>85 °C)<br>Stop with TBM enabled <sup>(6)</sup><br>Stop with LVI and TBM enabled <sup>(6)</sup> | I <sub>DD</sub>  | <br>                                           | 3<br>5<br>20<br>300 | 5<br>10<br>35<br>500  | μΑ<br>μΑ<br>μΑ<br>μΑ |

| I/O ports Hi-Z leakage current <sup>(7)</sup>                                                                                         | IIL              | —                                              | _                   | ±10                   | μA                   |

| Input current                                                                                                                         | I <sub>In</sub>  | —                                              | _                   | 1                     | μA                   |

#### Table 23-4. 5.0V DC Electrical Characteristics