# E·) / Fenesas Electronics America Inc - <u>R7FS7G27H2A01CBG#AC0 Datasheet</u>

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                                          |

|----------------------------|-------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                 |

| Core Size                  | 32-Bit Single-Core                                                                              |

| Speed                      | 240MHz                                                                                          |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, MMC/SD, QSPI, SCI, SPI, SSI, UART/USART, USB |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                                                                    |

| Number of I/O              | 126                                                                                             |

| Program Memory Size        | 4MB (4M x 8)                                                                                    |

| Program Memory Type        | FLASH                                                                                           |

| EEPROM Size                | 64K x 8                                                                                         |

| RAM Size                   | 640K x 8                                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                                                     |

| Data Converters            | A/D 21x12b; D/A 2x12b                                                                           |

| Oscillator Type            | Internal                                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                               |

| Mounting Type              | Surface Mount                                                                                   |

| Package / Case             | 176-LFBGA                                                                                       |

| Supplier Device Package    | 176-LFBGA (13x13)                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r7fs7g27h2a01cbg-ac0           |

|                            |                                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 1.3System (2/2)                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Feature                                               | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Resets                                                | <ul> <li>14 resets:</li> <li>RES pin reset</li> <li>Power-on reset</li> <li>Voltage monitor reset 0</li> <li>Voltage monitor reset 1</li> <li>Voltage monitor reset 2</li> <li>Independent Watchdog Timer reset</li> <li>Watchdog Timer reset</li> <li>Deep Software Standby reset</li> <li>SRAM parity error reset</li> <li>SRAM DED error reset</li> <li>Bus master MPU error reset</li> <li>Bus slave MPU error reset</li> <li>Stack pointer error reset</li> <li>Software reset.</li> <li>See section 6, Resets in User's Manual.</li> </ul>                                                                                                         |  |  |  |  |  |  |  |  |

| Low Voltage Detection (LVD)                           | The Low Voltage Detection (LVD) function monitors the voltage level input to the VCC pin, and the detection level can be selected in the software program. See section 8, Low Voltage Detection (LVD) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Clocks                                                | <ul> <li>Main clock oscillator (MOSC)</li> <li>Sub-clock oscillator (SOSC)</li> <li>High-speed on-chip oscillator (HOCO)</li> <li>Middle-speed on-chip oscillator (MOCO)</li> <li>Low-speed on-chip oscillator (LOCO)</li> <li>PLL frequency synthesizer</li> <li>Independent Watchdog Timer (WDT) on-chip oscillator</li> <li>Clock out supports.</li> <li>See section 9, Clock Generation Circuit in User's Manual.</li> </ul>                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |

| Clock Frequency Accuracy<br>Measurement Circuit (CAC) | The CAC checks the system clock frequency with a reference clock signal by counting the number of pulses of the system clock to be measured. The reference clock can be provided externally through a CACREF pin or internally from various on-chip oscillators. Event signals can be generated when the clock does not match or measurement ends. This feature is particularly useful in implementing a fail-safe mechanism for home and industrial automation applications. See section 10, Clock Frequency Accuracy Measurement Circuit (CAC) in User's Manual.                                                                                       |  |  |  |  |  |  |  |  |

| Low-power modes                                       | Power consumption can be reduced in multiple ways, including by setting clock dividers, controlling EBCLK output, controlling SDCLK output, stopping modules, selecting power control mode in normal operation, and transitioning to low-power modes. See section 11, Low-Power Modes in User's Manual.                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |  |

| Battery backup function                               | A battery backup function is provided for partial powering by a battery. The battery-powered area includes the RTC, SOSC, backup memory, and switch between VCC and VBATT. See section 12, Battery Backup Function in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Register write protection                             | The register write protection function protects important registers from being overwritten because of software errors. See section 13, Register Write Protection in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Memory Protection Unit (MPU)                          | Two MPUs and a CPU stack pointer monitor functions are provided for memory protection.<br>See section 16, Memory Protection Unit (MPU) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |  |

| Watchdog Timer (WDT)                                  | The WDT is a 14-bit down-counter. It can be used to reset the MCU when the counter underflows because the system has run out of control and is unable to refresh the WDT. In addition, a non-maskable interrupt or interrupt can be generated by an underflow. A refresh-permitted period can be set to refresh the counter and be used as the condition for detecting when the system runs out of control. See section 27, Watchdog Timer (WDT) in User's Manual.                                                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Independent Watchdog Timer (IWDT)                     | The IWDT consists of a 14-bit down-counter that must be serviced periodically to prevent counter underflow. The IWDT provides functionality to reset the MCU or to generate a non-maskable interrupt or interrupt for a timer underflow. Because the timer operates with an independent, dedicated clock source, it is particularly useful in returning the MCU to a known state as a fail safe mechanism when the system runs out of control. The IWDT can be triggered automatically on a reset, underflow, or refresh error, or by a refresh of the count value in the registers. See section 28, Independent Watchdog Timer (IWDT) in User's Manual. |  |  |  |  |  |  |  |  |

| Feature                                    | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Serial Communications Interface<br>(SCI)   | <ul> <li>The SCI is configurable to five asynchronous and synchronous serial interfaces:</li> <li>Asynchronous interfaces (UART and Asynchronous Communications Interface Adapter (ACIA))</li> <li>8-bit clock synchronous interface</li> <li>Simple IIC (master-only)</li> <li>Simple SPI</li> <li>Smart card interface.</li> <li>The smart card interface complies with the ISO/IEC 7816-3 standard for electronic signals and transmission protocol.</li> <li>Each SCI has FIFO buffers to enable continuous and full-duplex communication, and the data transfer speed can be configured independently using an on-chip baud rate generator. See section 34, Serial Communications Interface (SCI) in User's Manual.</li> </ul>                                                                                |

| IrDA Interface (IrDA)                      | The IrDA interface sends and receives IrDA data communication waveforms in cooperation with the SCI1 based on the IrDA (Infrared Data Association) standard 1.0. See section 35, IrDA Interface in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| I <sup>2</sup> C Bus Interface (IIC)       | The three-channel IIC conforms with and provides a subset of the NXP I <sup>2</sup> C bus (Inter-<br>Integrated Circuit bus) interface functions. See section 36, I <sup>2</sup> C Bus Interface (IIC) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Serial Peripheral Interface (SPI)          | Two independent SPI channels are capable of high-speed, full-duplex synchronous serial communications with multiple processors and peripheral devices. See section 38, Serial Peripheral Interface (SPI) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Serial Sound Interface (SSI)               | The SSI peripheral provides functionality to interface with digital audio devices for transmitting PCM audio data over a serial bus with the MCU. The SSI supports an audio clock frequency of up to 50 MHz, and can be operated as a slave or master receiver, transmitter, or transceiver to suit various applications. The SSI includes 8-stage FIFO buffers in the receiver and transmitter, and supports interrupts and DMA-driven data reception and transmission. See section 41, Serial Sound Interface (SSI) in User's Manual.                                                                                                                                                                                                                                                                            |

| Quad Serial Peripheral Interface<br>(QSPI) | The QSPI is a memory controller for connecting a serial ROM (nonvolatile memory such as a serial flash memory, serial EEPROM, or serial FeRAM) that has an SPI-compatible interface. See section 39, Quad Serial Peripheral Interface (QSPI) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Controller Area Network (CAN)<br>Module    | The CAN module provides functionality to receive and transmit data using a message-based protocol between multiple slaves and masters in electromagnetically-noisy applications. The CAN module complies with the ISO 11898-1 (CAN 2.0A/CAN 2.0B) standard and supports up to 32 mailboxes, which can be configured for transmission or reception in normal mailbox and FIFO modes. Both standard (11-bit) and extended (29-bit) messaging formats are supported. See section 37, Controller Area Network (CAN) Module in User's Manual.                                                                                                                                                                                                                                                                           |

| USB 2.0 Full-Speed Module (USBFS)          | Full-Speed USB controller that can operate as a host controller or device controller. The module supports full-speed and low-speed (host controller only) transfer as defined in Universal Serial Bus Specification 2.0. The module has an internal USB transceiver and supports all of the transfer types defined in Universal Serial Bus Specification 2.0. The USB has buffer memory for data transfer, providing a maximum of 10 pipes. Pipes 1 to 9 can be assigned any endpoint number based on the peripheral devices used for communication or based on your system. See section 32, USB 2.0 Full-Speed Module (USBFS) in User's Manual.                                                                                                                                                                   |

| USB 2.0 High-Speed Module<br>(USBHS)       | High-Speed USB controller that can operate as a host controller or a device controller. As a host controller, the USBHS supports high-speed transfer, full-speed transfer, and low-speed transfer as defined in Universal Serial Bus Specification 2.0. As a device controller, the USBHS supports high-speed transfer and full-speed transfer as defined in Universal Serial Bus Specification 2.0. The USBHS has an internal USB transceiver and supports all of the transfer types defined in Universal Serial Bus Specification 2.0. The USBHS has FIFO buffers for data transfer, providing a maximum of 10 pipes. Any endpoint number can be assigned to pipes 1 to 9, based on the peripheral devices or your system for communication. See section 33, USB 2.0 High-Speed Module (USBHS) in User's Manual. |

Table 1.9

Communication interfaces (1/2)

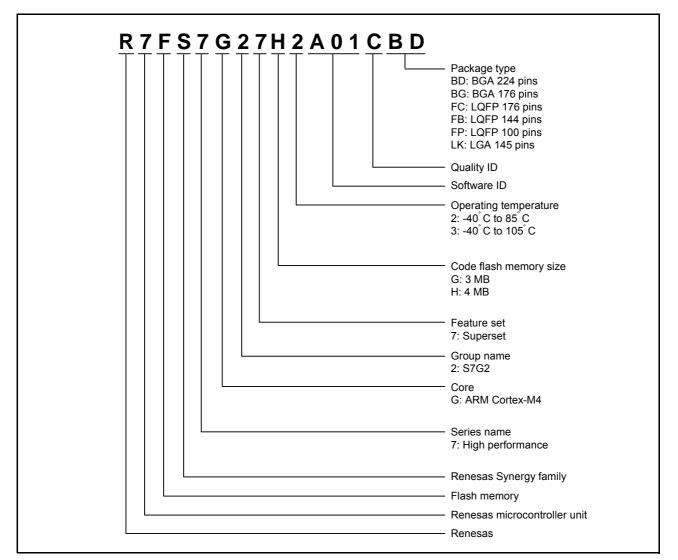

## 1.3 Part Numbering

Figure 1.2 Part numbering scheme

## 1.7 Pin Lists

## Table 1.17 Pin list (1/12)

| Pin     | numbe   | ər      |         |         |         | æ                               |          | Extb         | ous   | Time                                  | ers                       |                       |                | Con            | nmuni                                     | cation                                                | interfa        | aces      |                       |                            |                              |                                       |      | Ana                  | log              | нмі  |                 |                |

|---------|---------|---------|---------|---------|---------|---------------------------------|----------|--------------|-------|---------------------------------------|---------------------------|-----------------------|----------------|----------------|-------------------------------------------|-------------------------------------------------------|----------------|-----------|-----------------------|----------------------------|------------------------------|---------------------------------------|------|----------------------|------------------|------|-----------------|----------------|

| BGA224  | BGA176  | LQFP176 | LGA145  | LQFP144 | LQFP100 | Power, System,<br>Clock, Debug, | I/O port | External bus | SDRAM | AGT                                   | GPT                       | GPT                   | RTC            | USBFS,<br>CAN  | SCI0,2,4,6,8<br>(30 MHz)                  | SCI1,3,5,7,9<br>(30 MHz)                              | S              | SPI, QSPI | SSI                   | MII<br>(25 MHz)            | RMII<br>(50 MHz)             | USBHS                                 | SDHI | ADC12                | DAC12,<br>ACMPHS | CTSU | Interrupt       | GLCDC, PDC     |

| N13     | N13     | 1       | N13     | 1       | 1       | -                               | P40<br>0 | -            | -     | -                                     | -                         | GTI<br>OC<br>6A_<br>A | -              | -              | SC<br>K4_<br>B                            | SC<br>K7_<br>A                                        | SC<br>L0_<br>A | -         | AU<br>DIO<br>_CL<br>K | ET1<br>_TX<br>_CL<br>K     | -                            | -                                     | -    | AD<br>TR<br>G1<br>_B | -                | -    | IRQ<br>0        | -              |

| P15     | R15     | 2       | L11     | 2       | 2       | -                               | P40<br>1 | -            | -     | -                                     | GT<br>ET<br>RG<br>A_<br>B | GTI<br>OC<br>6B_<br>A | -              | CT<br>X0_<br>B | CT<br>S4_<br>RT<br>S4_<br>B/<br>SS<br>4_B | TX<br>D7_<br>A/<br>MO<br>SI7<br>_A/<br>SD<br>A7_<br>A | SD<br>A0_<br>A | -         | -                     | ET0<br>_M<br>DC            | ET0<br>_M<br>DC              | -                                     | -    | -                    | -                | -    | IRQ<br>5-<br>DS | -              |

| N14     | P14     | 3       | M1<br>3 | 3       | 3       | -                               | P40<br>2 | -            | -     | AG<br>TIO<br>0_B<br>/AG<br>TIO<br>1_B | -                         | -                     | RT<br>CIC<br>0 | CR<br>X0_<br>B | -                                         | RX<br>D7_<br>A/<br>MIS<br>O7<br>_A/<br>SC<br>L7_<br>A | -              | -         | -                     | ET0<br>_M<br>DIO           | ET0<br>_M<br>DIO             | -                                     | -    | -                    | -                | -    | IRQ<br>4-<br>DS | -              |

| N15     | M1<br>2 | 4       | K11     | 4       | 4       | -                               | P40<br>3 | -            | -     | AG<br>TIO<br>0_C<br>/AG<br>TIO<br>1_C | -                         | GTI<br>OC<br>3A_<br>B | RT<br>CIC<br>1 | -              | -                                         | CT<br>S7_<br>RT<br>S7_<br>A/<br>SS<br>7_A             | -              | -         | SSI<br>SC<br>K0_<br>A | ET1<br>_M<br>DC            | ET1<br>_M<br>DC              | -                                     | -    | -                    | -                | -    | -               | PIX<br>D7      |

| K10     | M1<br>3 | 5       | L12     | 5       | 5       | -                               | P40<br>4 | -            | -     | -                                     | -                         | GTI<br>OC<br>3B_<br>B | RT<br>CIC<br>2 | -              | -                                         | -                                                     | -              | -         | SSI<br>WS<br>0_A      | ET1<br>_M<br>DIO           | ET1<br>_M<br>DIO             | -                                     | -    | -                    | -                | -    | -               | PIX<br>D6      |

| M1<br>3 | P15     | 6       | L13     | 6       | 6       | -                               | P40<br>5 | -            | -     | -                                     | -                         | GTI<br>OC<br>1A_<br>B | -              | -              | -                                         | -                                                     | -              | -         | SSI<br>TX<br>D0_<br>A | ET1<br>_TX<br>_E<br>N      | RMI<br>I1_<br>TX<br>D_<br>EN | -                                     | -    | -                    | -                | -    | -               | PIX<br>D5      |

| 9L      | N14     | 7       | J10     | 7       | 7       | -                               | P40<br>6 | -            | -     | -                                     | -                         | GTI<br>OC<br>1B_<br>B | -              | -              | -                                         | -                                                     | -              | -         | SSI<br>RX<br>D0_<br>A | ET1<br>_R<br>X_<br>ER      | RMI<br>I1_<br>TX<br>D1       | -                                     | -    | -                    | -                | -    | -               | PIX<br>D4      |

| M1<br>4 | N15     | 8       | H10     | 8       | -       | -                               | P70<br>0 | -            | -     | -                                     | -                         | GTI<br>OC<br>5A_<br>B | -              | -              | -                                         | -                                                     | -              | -         | -                     | ET1<br>_ET<br>XD<br>1      | RMI<br>I1_<br>TX<br>D0       | -                                     | -    | -                    | -                | -    | -               | PIX<br>D3      |

| M1<br>5 | M1<br>4 | 9       | K12     | 9       | -       | -                               | P70<br>1 | -            | -     | -                                     | -                         | GTI<br>OC<br>5B_<br>B | -              | -              | -                                         | -                                                     | -              | -         | -                     | ET1<br>_ET<br>XD<br>0      | RE<br>F50<br>CK<br>1         | -                                     | -    | -                    | -                | -    | -               | PIX<br>D2      |

| K11     | L12     | 10      | K13     | 10      | -       | -                               | P70<br>2 | -            | -     | -                                     | -                         | GTI<br>OC<br>6A_<br>B | -              | -              | -                                         | -                                                     | -              | -         | -                     | ET1<br>_E<br>RX<br>D1      | RMI<br>I1_<br>RX<br>D0       | -                                     | -    | -                    | -                | -    | -               | PIX<br>D1      |

| J8      | M1<br>5 | 11      | J11     | 11      | -       | -                               | P70<br>3 | -            | -     | -                                     | -                         | GTI<br>OC<br>6B_<br>B | -              | -              | -                                         | -                                                     | -              | -         | -                     | ET1<br>_E<br>RX<br>D0      | RMI<br>I1_<br>RX<br>D1       | -                                     | -    | -                    | -                | -    | -               | PIX<br>D0      |

| J10     | L13     | 12      | H11     | 12      | -       | -                               | P70<br>4 | -            | -     | -                                     | -                         | -                     | -              | -              | -                                         | -                                                     | -              | -         | -                     | ET1<br>_R<br>X_<br>CL<br>K | RMI<br>I1_<br>RX<br>_E<br>R  | -                                     | -    | -                    | -                | -    | -               | HS<br>YN<br>C  |

| L13     | K12     | 13      | G11     | 13      | -       | -                               | P70<br>5 | -            | -     | -                                     | -                         | -                     | -              | -              | -                                         | -                                                     | -              | -         | -                     | ET1<br>_C<br>RS            | RMI<br>I1_<br>CR<br>S_<br>DV | -                                     | -    | -                    | -                | -    | -               | PIX<br>CL<br>K |

| L14     | L14     | 14      | -       | -       | -       | -                               | P70<br>6 | -            | -     | -                                     | -                         | -                     | -              | -              | -                                         | RX<br>D3_<br>B/<br>MIS<br>O3<br>_B/<br>SC<br>L3_<br>B | -              | -         | -                     | -                          | -                            | US<br>BH<br>S_V<br>RC<br>UR<br>B      | -    | -                    | -                | -    | IRQ<br>7        | -              |

| L15     | L15     | 15      | -       | -       | -       | -                               | P70<br>7 | -            | -     | -                                     | -                         | -                     | -              | -              | -                                         | TX<br>D3_<br>B/<br>MO<br>SI3<br>_B/<br>SD<br>A3_<br>B | -              | -         | -                     | -                          | -                            | US<br>BH<br>S_<br>OV<br>RC<br>UR<br>A | -    | -                    | -                | -    | IRQ<br>8        | -              |

| S7G2 |  |

|------|--|

|------|--|

## Table 1.17 Pin list (4/12)

| Pin ı  | numbe  | ər      |        |         |         | 1                               |          | Extb         | ous   | Time             | ers                  |                        |                | Con                                          | nmuni                                                 | cation                                                | interfa        | aces                 |                        |                            |                              |                                  |                 | Ana            | log              | НМІ                 |                 |            |

|--------|--------|---------|--------|---------|---------|---------------------------------|----------|--------------|-------|------------------|----------------------|------------------------|----------------|----------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|----------------|----------------------|------------------------|----------------------------|------------------------------|----------------------------------|-----------------|----------------|------------------|---------------------|-----------------|------------|

| BGA224 | BGA176 | LQFP176 | LGA145 | LQFP144 | LQFP100 | Power, System,<br>Clock, Debug, | l/O port | External bus | SDRAM | AGT              | GPT                  | GPT                    | RTC            | USBFS,<br>CAN                                | SCI0,2,4,6,8<br>(30 MHz)                              | SCI1,3,5,7,9<br>(30 MHz)                              | IIC            | SPI, QSPI            | SSI                    | MII<br>(25 MHz)            | RMII<br>(50 MHz)             | USBHS                            | SDHI            | ADC12          | DAC12,<br>ACMPHS | CTSU                | Interrupt       | GLCDC, PDC |

| D14    | C15    | 40      | D11    | 32      | 21      | -                               | P41<br>1 | -            | -     | AG<br>TO<br>A1   | GT<br>OV<br>UP<br>_B | GTI<br>OC<br>9A_<br>A  | -              | -                                            | TX<br>D0_<br>B/<br>MO<br>SI0<br>_B/<br>SD<br>A0_<br>B | CT<br>S3_<br>RT<br>S3_<br>A/<br>SS<br>3_A             | -              | MO<br>SIA<br>_B      | -                      | ET0<br>_E<br>RX<br>D1      | RMI<br>IO_<br>RX<br>D0       | -                                | SD<br>0D<br>AT0 | -              | -                | TS0<br>7            | IRQ<br>4        | -          |

| C15    | C14    | 41      | C12    | 33      | 22      | -                               | P41<br>0 | -            | -     | AG<br>TO<br>B1   | GT<br>OV<br>LO<br>_B | GTI<br>OC<br>9B_<br>A  | -              | -                                            | RX<br>D0_<br>B/<br>MIS<br>O0<br>_B/<br>SC<br>L0_<br>B | SC<br>K3_<br>A                                        | -              | MIS<br>OA<br>_B      | -                      | ET0<br>_E<br>RX<br>D0      | RMI<br>IO_<br>RX<br>D1       | -                                | SD<br>0D<br>AT1 | -              | -                | TS0<br>6            | IRQ<br>5        | -          |

| C14    | B15    | 42      | B13    | 34      | 23      | -                               | 940<br>9 | -            | -     | -                | GT<br>OW<br>UP<br>_B | GTI<br>OC<br>10A<br>_A | -              | US<br>B_<br>EXI<br>CE<br>N_<br>A             | -                                                     | TX<br>D3_<br>A/<br>MO<br>SI3<br>_A/<br>SD<br>A3_<br>A | -              | -                    | -                      | ETO<br>_R<br>X_<br>CL<br>K | RMI<br>IO_<br>RX<br>_E<br>R  | US<br>BH<br>S_<br>EXI<br>CE<br>N | -               | -              | -                | TS0<br>5            | IRQ<br>6        | -          |

| B15    | D13    | 43      | D10    | 35      | 24      | -                               | P40<br>8 | -            | -     | -                | GT<br>OW<br>LO<br>_B | GTI<br>OC<br>10B<br>_A | -              | US<br>B_I<br>D_<br>A                         | -                                                     | RX<br>D3_<br>A/<br>MIS<br>O3<br>_A/<br>SC<br>L3_<br>A | -              | -                    | -                      | ET0<br>_C<br>RS            | RMI<br>I0_<br>CR<br>S_<br>DV | US<br>BH<br>S_I<br>D             | -               | -              | -                | TS0<br>4            | IRQ<br>7        | -          |

| A15    | A15    | 44      | A13    | 36      | 25      | -                               | P40<br>7 | -            | -     | -                | -                    | -                      | RT<br>CO<br>UT | US<br>B_<br>VB<br>US                         | CT<br>S4_<br>RT<br>S4_<br>A/<br>SS<br>4_A             | -                                                     | SD<br>A0_<br>B | SS<br>LB3<br>_A      | -                      | ET0<br>_E<br>XO<br>UT      | ET0<br>_E<br>XO<br>UT        | -                                | -               | AD<br>TR<br>G0 | -                | TS0<br>3            | -               | -          |

| B13    | C13    | 45      | B11    | 37      | 26      | VS<br>S_<br>US<br>B             | -        | -            | -     | -                | -                    | -                      | -              | -                                            | -                                                     | -                                                     | -              | -                    | -                      | -                          | -                            | -                                | -               | -              | -                | -                   | -               | -          |

| B14    | B14    | 46      | A12    | 38      | 27      |                                 | -        | -            | -     | -                | -                    | -                      | -              | US<br>B_<br>DM                               | -                                                     | -                                                     | -              | -                    | -                      | -                          | -                            | -                                | -               | -              | -                | -                   | -               | -          |

| A14    | A14    | 47      | B12    | 39      | 28      |                                 | -        | -            | -     | -                | -                    | -                      | -              | US<br>B_<br>DP                               | -                                                     | -                                                     | -              | -                    | -                      | -                          | -                            | -                                | -               | -              | -                | -                   | -               | -          |

| A13    | B13    | 48      | A11    | 40      | 29      | VC<br>C_<br>US<br>B             | -        | -            | -     | -                | -                    | -                      | -              | -                                            | -                                                     | -                                                     | -              | -                    | -                      | -                          | -                            | -                                | -               | -              | -                | -                   | -               | -          |

| C13    | C12    | 49      | C11    | 41      | 30      | -                               | P20<br>7 | A17          | -     | -                | -                    | -                      | -              | -                                            | -                                                     | -                                                     | -              | SS<br>LB2<br>_A      | -                      | -                          | -                            | -                                | -               | -              | -                | TS0<br>2            | -               | -          |

| G9     | D12    | 50      | B10    | 42      | 31      | -                               | P20<br>6 | WAI<br>T     | -     | -                | GTI<br>U_<br>A       | -                      | -              | US<br>B_<br>VB<br>US<br>EN<br>_A             | RX<br>D4_<br>A/<br>MIS<br>O4<br>_A/<br>SC<br>L4_<br>A | -                                                     | SD<br>A1_<br>A | SS<br>LB1<br>_A      | SSI<br>DA<br>TA1<br>_A | ET0<br>_LI<br>NK<br>STA    | ET0<br>_LI<br>NK<br>STA      | -                                | SD<br>0D<br>AT2 | -              | -                | TS0<br>1            | IRQ<br>0-<br>DS | -          |

| C12    | E12    | 51      | A10    | 43      | 32      | CL<br>KO<br>UT<br>_A            | P20<br>5 | A16          | -     | AG<br>TO<br>1    | GTI<br>V_<br>A       | GTI<br>OC<br>4A_<br>B  | -              | US<br>B_<br>OV<br>RC<br>UR<br>A_<br>DS       | TX<br>D4_<br>A/<br>MO<br>SI4<br>_A/<br>SD<br>A4_<br>A | CT<br>S9_<br>RT<br>S9_<br>A/<br>SS<br>9_A             | SC<br>L1_<br>A | SS<br>LB0<br>_A      | SSI<br>WS<br>1_A       | ET0<br>_W<br>OL            | ET0<br>_W<br>OL              | -                                | SD<br>0D<br>AT3 | -              | -                | TS<br>CA<br>P_<br>A | IRQ<br>1-<br>DS | -          |

| D11    | A13    | 52      | C10    | 44      | -       | CA<br>CR<br>EF_<br>A            | P20<br>4 | A18          | -     | AG<br>TIO<br>1_A | GTI<br>W_<br>A       | GTI<br>OC<br>4B_<br>B  | -              | US<br>B_<br>OV<br>RC<br>UR<br>B_<br>A-<br>DS | SC<br>K4_<br>A                                        | SC<br>K9_<br>A                                        | SC<br>LO_<br>B | RS<br>PC<br>KB<br>_A | SSI<br>SC<br>K1_<br>A  | ET0<br>_R<br>X_<br>DV      | -                            | -                                | SD<br>0D<br>AT4 | -              | -                | TSO<br>0            | -               | -          |

| B12    | D11    | 53      | A9     | 45      | -       | -                               | P20<br>3 | A19          | -     | -                | -                    | GTI<br>OC<br>5A_<br>A  | -              | CT<br>X0_<br>A                               | CT<br>S2_<br>RT<br>S2_<br>A/<br>SS<br>2_A             | TX<br>D9_<br>A/<br>MO<br>SI9<br>_A/<br>SD<br>A9_<br>A | -              | MO<br>SIB<br>_A      | -                      | ET0<br>_C<br>OL            | -                            | -                                | SD<br>0D<br>AT5 | -              | -                | TS<br>CA<br>P_<br>B | IRQ<br>2-<br>DS | -          |

| Item                                          |                         | Symbol              | Min   | Тур | Max   | Unit | Test conditions   |

|-----------------------------------------------|-------------------------|---------------------|-------|-----|-------|------|-------------------|

| HOCO clock oscillator                         | Without FLL             | f <sub>HOCO16</sub> | 15.61 | 16  | 16.39 | MHz  | –20 ≤ Ta ≤ 105°C  |

| oscillation frequency                         |                         | f <sub>HOCO18</sub> | 17.56 | 18  | 18.44 |      |                   |

|                                               |                         | f <sub>HOCO20</sub> | 19.52 | 20  | 20.48 |      |                   |

|                                               |                         | f <sub>HOCO16</sub> | 15.52 | 16  | 16.48 |      | –40 ≤ Ta ≤ –20°C  |

|                                               |                         | f <sub>HOCO18</sub> | 17.46 | 18  | 18.54 |      |                   |

|                                               |                         | f <sub>HOCO20</sub> | 19.40 | 20  | 20.60 |      |                   |

|                                               | With FLL                | f <sub>HOCO16</sub> | 15.91 | 16  | 16.09 |      | SOSC frequency is |

|                                               |                         | f <sub>HOCO18</sub> | 17.90 | 18  | 18.10 |      | 32.768kHz ± 50ppm |

|                                               |                         | f <sub>HOCO20</sub> | 19.89 | 20  | 20.11 |      |                   |

| HOCO clock oscillation stat                   | bilization wait time *2 | t <sub>HOCOWT</sub> | -     | -   | 64.7  | μs   | -                 |

| FLL stabilization wait time                   |                         | t <sub>FLLWT</sub>  | -     | -   | 3     | ms   | -                 |

| PLL clock frequency                           |                         | f <sub>PLL</sub>    | 120   | -   | 240   | MHz  | -                 |

| PLL clock oscillation stabilization wait time |                         | t <sub>PLLWT</sub>  | -     | -   | 174.9 | μs   | Figure 2.7        |

Table 2.13

Clock timing except for sub-clock oscillator (2/2)

Note 1. When setting up the main clock oscillator, ask the oscillator manufacturer for an oscillation evaluation and use the results as the recommended oscillation stabilization time. Set the MOSCWTCR register to a value equal to or greater than the recommended value.

After changing the setting in the MOSCCR.MOSTP bit to start main clock operation, read the OSCSF.MOSCSF flag to confirm that it is 1, and then start using the main clock oscillator.

Note 2. This is the time from release from reset state until the HOCO oscillation frequency (fHOCO) reaches the range for guaranteed operation.

## Table 2.14 Clock timing for the sub-clock oscillator

| Item                                          | Symbol                | Min | Тур    | Мах | Unit | Test conditions |

|-----------------------------------------------|-----------------------|-----|--------|-----|------|-----------------|

| Sub-clock frequency                           | f <sub>SUB</sub>      | -   | 32.768 | -   | kHz  | -               |

| Sub-clock oscillation stabilization wait time | t <sub>SUBOSCWT</sub> | -   | -      | _*1 | S    | -               |

Note 1. When setting up the sub-clock oscillator, ask the oscillator manufacturer for an oscillation evaluation and use the results as the recommended oscillation stabilization time.

After changing the setting in the SOSCCR.SOSTP bit to start sub-clock operation, only start using the sub-clock oscillator after the sub-clock oscillation stabilization time elapses with an adequate margin. Two times the value shown is recommended.

## 2.3.4 Wakeup Timing and Duration

| Table 2.16 | Timing of recovery from low-power modes and duration |

|------------|------------------------------------------------------|

|------------|------------------------------------------------------|

| ltem                           |                                             |                                                                     | Symbol              | Min  | Тур | Мах              | Unit                 | Test<br>conditions                   |

|--------------------------------|---------------------------------------------|---------------------------------------------------------------------|---------------------|------|-----|------------------|----------------------|--------------------------------------|

| Recovery time<br>from Software | Crystal resonator                           | System clock source is main clock oscillator* <sup>2</sup>          | t <sub>SBYMC</sub>  | -    | -   | 2.8              | ms                   | Figure 2.10<br>The division          |

| Standby mode*1                 | connected<br>to main<br>clock<br>oscillator | System clock source is PLL with main clock oscillator* <sup>3</sup> | t <sub>SBYPC</sub>  | -    | -   | 3.2              | ms                   | ratio of all<br>oscillators is<br>1. |

|                                | External<br>clock input                     | System clock source is main<br>clock oscillator*4                   | t <sub>SBYEX</sub>  | -    | -   | 280              | μs                   |                                      |

|                                | to main<br>clock<br>oscillator              | System clock source is PLL with main clock oscillator*5             | t <sub>SBYPE</sub>  | -    | -   | 700              | μs                   |                                      |

|                                | System clock<br>oscillator*8                | < source is sub-clock                                               | t <sub>SBYSC</sub>  | -    | -   | 1.3              | ms                   | -                                    |

|                                | System clock                                | < source is LOCO*8                                                  | t <sub>SBYLO</sub>  | -    | -   | 1.4              | ms                   |                                      |

|                                | System clock<br>oscillator*6                | source is HOCO clock                                                | t <sub>SBYHO</sub>  | -    | -   | 300              | μs                   |                                      |

|                                | System clock<br>oscillator*7                | source is MOCO clock                                                | t <sub>SBYMO</sub>  | -    | -   | 300              | μs                   |                                      |

| Recovery time from             | n Deep Softwa                               | are Standby mode                                                    | t <sub>DSBY</sub>   | -    | -   | 1.0              | ms                   | Figure 2.11                          |

| Wait time after car            | cellation of De                             | ep Software Standby mode                                            | t <sub>DSBYWT</sub> | 31   | -   | 32               | t <sub>cyc</sub>     |                                      |

| Recovery time<br>from Software | • •                                         | mode when system clock<br>DCO (20 MHz)                              | t <sub>SNZ</sub>    | -    | -   | 68               | μs                   | -                                    |

| Standby mode to<br>Snooze      | High-speed i<br>source is MC                | mode when system clock<br>DCO (8 MHz)                               | t <sub>SNZ</sub>    | -    | -   | 14* <sup>9</sup> | μs                   |                                      |

| Normal mode                    | System clock                                | source is main clock oscillator                                     | t <sub>NML</sub>    | _*11 | -   | -                | t <sub>cycmosc</sub> | Figure 2.10                          |

| duration* <sup>10</sup>        | System clock<br>oscillator                  |                                                                     |                     |      |     | .,               |                      |                                      |

Note 1. The recovery time is determined by the system clock source. When multiple oscillators are active, the recovery time can be determined with the following equation:

Total recovery time = recovery time for an oscillator as the system clock source + the longest oscillation stabilization time of any oscillators requiring longer stabilization times than the system clock source + 2 LOCO cycles (when LOCO is operating) + 3 SOSC cycles (when Subosc is oscillating and MSTPC0 = 0 (CAC module stop)).

Note 2. When the frequency of the crystal is 24 MHz (Main Clock Oscillator Wait Control Register (MOSCWTCR) is set to 05h). For other settings (MOSCWTCR is set to Xh), the recovery time can be determined with the following equation:

$t_{SBYMC}$  (MOSCWTCR = Xh) =  $t_{SBYMC}$  (MOSCWTCR = 05h) + ( $t_{MAINOSCWT}$  (MOSCWTCR = Xh) -  $t_{MAINOSCWT}$  (MOSCWTCR = 05h))

Note 3. When the frequency of PLL is 240 MHz (Main Clock Oscillator Wait Control Register (MOSCWTCR) is set to 05h). For other settings (MOSCWTCR is set to Xh), the recovery time can be determined with the following equation:

$t_{\text{SBYMC}} \text{ (MOSCWTCR = Xh) = } t_{\text{SBYMC}} \text{ (MOSCWTCR = 05h) + } (t_{\text{MAINOSCWT}} \text{ (MOSCWTCR = Xh) - } t_{\text{MAINOSCWT}} \text{ (MOSCWTCR = 05h))}$

Note 4. When the frequency of the external clock is 24 MHz (Main Clock Oscillator Wait Control Register (MOSCWTCR) is set to 00h). For other settings (MOSCWTCR is set to Xh), the recovery time can be determined with the following equation:

$t_{SBYMC}$  (MOSCWTCR = Xh) =  $t_{SBYMC}$  (MOSCWTCR = 00h) + ( $t_{MAINOSCWT}$  (MOSCWTCR = Xh) -  $t_{MAINOSCWT}$  (MOSCWTCR = 00h))

Note 5. When the frequency of PLL is 240 MHz (Main Clock Oscillator Wait Control Register (MOSCWTCR) is set to 00h). For other settings (MOSCWTCR is set to Xh), the recovery time can be determined with the following

equation:

$t_{SBYMC}$  (MOSCWTCR = Xh) =  $t_{SBYMC}$  (MOSCWTCR = 00h) + ( $t_{MAINOSCWT}$  (MOSCWTCR = Xh) -  $t_{MAINOSCWT}$  (MOSCWTCR = 00h))

Note 6. The HOCO frequency is 20 MHz.

Note 7. The MOCO frequency is 8 MHz.

Note 8. In Subosc-speed mode, the sub-clock oscillator or LOCO continues oscillating in Software Standby mode.

Note 9. When the SNZCR.RXDREQEN bit is set to 0, 86  $\mu s$  is added as the power supply recovery time.

Note 10. This defines the duration of Normal mode after a transition from Snooze to Normal mode.

The following cases are valid uses of the main clock oscillator:

- The crystal resonator is connected to main clock oscillator

- The external clock is input to main clock oscillator.

The following cases are excluded:

- The main clock resonator is not connected to the system clock source

- Transition is made from Software Standby to Normal mode.

Note 11. The same value as set in MOSCWTCR.MSTS[3:0]. Duration of Normal mode must be longer than the main clock oscillator wait time.

MOSCWTCR: Main Clock Oscillator Wait Control Register

$t_{cycmosc}$ : Main clock oscillator frequency cycle.

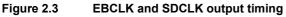

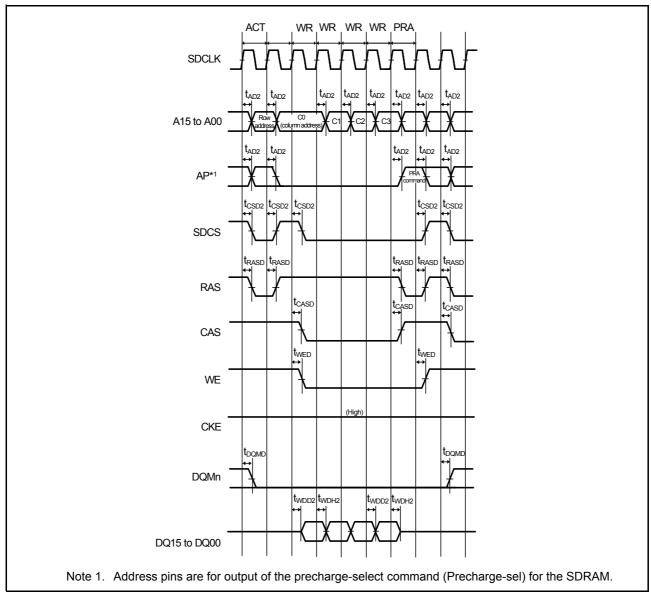

Figure 2.19 SDRAM single read timing

Figure 2.22 SDRAM multiple write timing

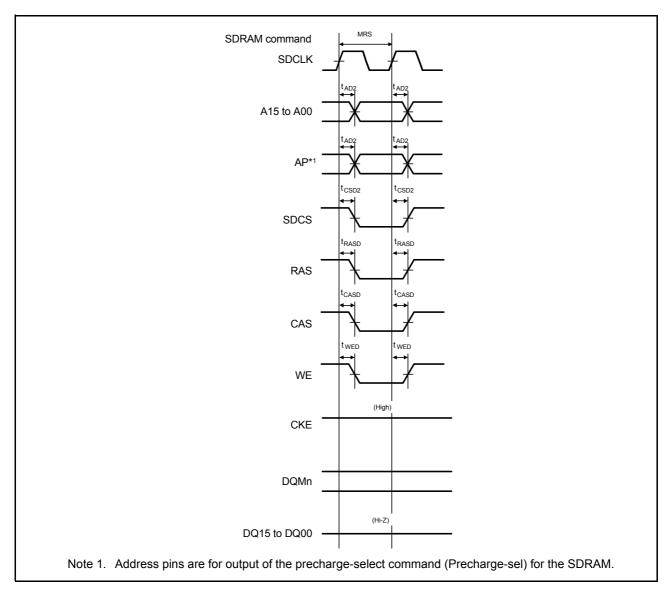

Figure 2.24 SDRAM mode register set timing

Note 1. t<sub>PBcyc</sub>: PCLKB cycle.

Note 2.  $t_{cac}$ : CAC count clock source cycle.

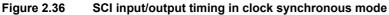

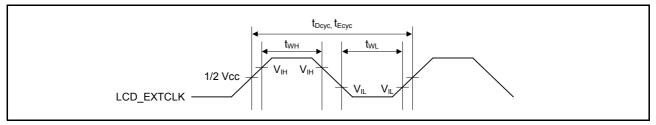

### 2.3.10 SCI Timing

Table 2.22

SCI timing (1)

Conditions: High drive output is selected in the port drive capability bit in the PmnPFS register for the following pins: SCK0 to SCK9 (except for SCK4\_B, SCK7\_A), SCK4\_B, SCK7\_A.

For other pins, middle drive output is selected in the port drive capability bit in the PmnPFS register.

| ltem |                          |                      | Symbol            | Min | Мах | Unit <sup>*1</sup> | Test conditions |

|------|--------------------------|----------------------|-------------------|-----|-----|--------------------|-----------------|

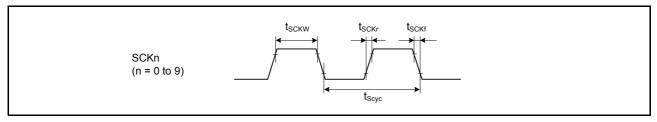

| SCI  | Input clock cycle        | Asynchronous         | t <sub>Scyc</sub> | 4   | -   | t <sub>Pcyc</sub>  | Figure 2.35     |

|      |                          | Clock<br>synchronous |                   | 6   | -   |                    |                 |

|      | Input clock pulse width  |                      | t <sub>scкw</sub> | 0.4 | 0.6 | t <sub>Scyc</sub>  |                 |

|      | Input clock rise time    |                      | t <sub>SCKr</sub> | -   | 5   | ns                 |                 |

|      | Input clock fall time    |                      | t <sub>SCKf</sub> | -   | 5   | ns                 |                 |

|      | Output clock cycle       | Asynchronous         | t <sub>Scyc</sub> | 6   | -   | t <sub>Pcyc</sub>  |                 |

|      |                          | Clock<br>synchronous |                   | 4   | -   |                    |                 |

|      | Output clock pulse width |                      | t <sub>SCKW</sub> | 0.4 | 0.6 | t <sub>Scyc</sub>  |                 |

|      | Output clock rise time   |                      | t <sub>SCKr</sub> | -   | 5   | ns                 |                 |

|      | Output clock fall time   |                      | t <sub>SCKf</sub> | -   | 5   | ns                 |                 |

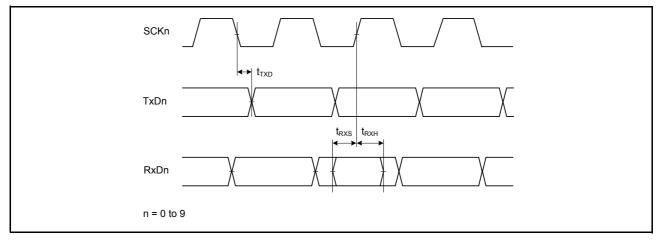

|      | Transmit data delay      | Clock<br>synchronous | t <sub>TXD</sub>  | -   | 25  | ns                 | Figure 2.36     |

|      | Receive data setup time  | Clock<br>synchronous | t <sub>RXS</sub>  | 15  | -   | ns                 |                 |

|      | Receive data hold time   | Clock<br>synchronous | t <sub>RXH</sub>  | 5   | -   | ns                 |                 |

Note 1.  $t_{Pcyc}$ : PCLKA cycle.

Figure 2.35 SCK clock input/output timing

Table 2.23

SCI timing (2)

Conditions: High drive output is selected in the port drive capability bit in the PmnPFS register for the following pins: SCK0 to SCK9

(except for SCK4\_B, SCK7\_A).

For the SCK4\_B and SCK7\_A pins, middle drive output is selected in the port drive capability bit in the PmnPFS register.

For the MISO1\_A pins, low drive output is selected in the port drive capability bit in the PmnPFS register.

For other pins, middle drive output is selected in the port drive capability bit in the PmnPFS register.

| ltem          |                                    | Symbol                                  | Min                                       | Мах                                       | Unit               | Test<br>conditions |

|---------------|------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------|--------------------|--------------------|

| Simple<br>SPI | SCK clock cycle output<br>(master) | t <sub>SPcyc</sub>                      | 4 (PCLKA ≤ 60 MHz)<br>8 (PCLKA > 60 MHz)  | 65536                                     | t <sub>Pcyc</sub>  | Figure 2.37        |

|               | SCK clock cycle input (slave)      | -                                       | 6 (PCLKA ≤ 60 MHz)<br>12 (PCLKA > 60 MHz) | 65536                                     |                    |                    |

|               | SCK clock high pulse width         | t <sub>SPCKWH</sub>                     | 0.4                                       | 0.6                                       | t <sub>SPcyc</sub> |                    |

|               | SCK clock low pulse width          | t <sub>SPCKWL</sub>                     | 0.4                                       | 0.6                                       | t <sub>SPcyc</sub> |                    |

|               | SCK clock rise and fall time       | t <sub>SPCKr</sub> , t <sub>SPCKf</sub> | -                                         | 20                                        | ns                 |                    |

|               | Data input setup time              | t <sub>SU</sub>                         | 33.3                                      | -                                         | ns                 | Figure 2.38 to     |

|               | Data input hold time               | t <sub>H</sub>                          | 33.3                                      | -                                         | ns                 | Figure 2.41        |

|               | SS input setup time                | t <sub>LEAD</sub>                       | 1                                         | -                                         | t <sub>SPcyc</sub> |                    |

|               | SS input hold time                 | t <sub>LAG</sub>                        | 1                                         | -                                         | t <sub>SPcyc</sub> |                    |

|               | Data output delay                  | t <sub>OD</sub>                         | -                                         | 33.3                                      | ns                 |                    |

|               | Data output hold time              | t <sub>OH</sub>                         | -10                                       | -                                         | ns                 |                    |

|               | Data rise and fall time            | t <sub>Dr</sub> , t <sub>Df</sub>       | -                                         | 16.6                                      | ns                 |                    |

|               | SS input rise and fall time        | t <sub>SSLr</sub> , t <sub>SSLf</sub>   | -                                         | 16.6                                      | ns                 |                    |

|               | Slave access time                  | t <sub>SA</sub>                         | -                                         | 4 (PCLKA ≤ 60 MHz)<br>8 (PCLKA > 60 MHz)  | t <sub>Pcyc</sub>  | Figure 2.41        |

|               | Slave output release time          | t <sub>REL</sub>                        | -                                         | 5 (PCLKA ≤ 60 MHz)<br>10 (PCLKA > 60 MHz) | t <sub>Pcyc</sub>  |                    |

MISO1\_A is not supported in these specifications. Note:

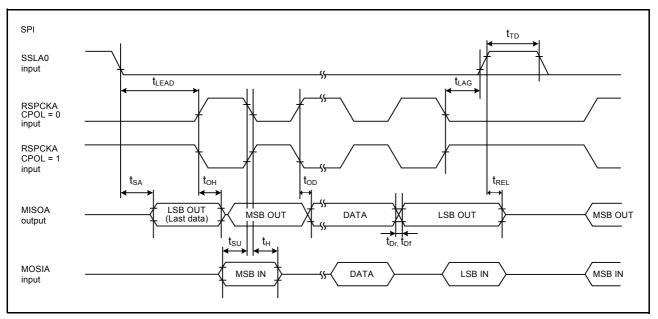

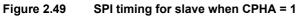

## 2.3.12 QSPI Timing

## Table 2.26 QSPI timing

Conditions: High drive output is selected in the port drive capability bit in the PmnPFS register.

| ltem |                               | Symbol             | Min                                                | Мах                                                 | Unit*1             | Test conditions |

|------|-------------------------------|--------------------|----------------------------------------------------|-----------------------------------------------------|--------------------|-----------------|

| QSPI | QSPCK clock cycle             | t <sub>QScyc</sub> | 2                                                  | 48                                                  | t <sub>Pcyc</sub>  | Figure 2.50     |

|      | QSPCK clock high pulse width  | t <sub>QSWH</sub>  | t <sub>QScyc</sub> × 0.4                           | -                                                   | ns                 |                 |

|      | QSPCK clock low pulse width   | t <sub>QSWL</sub>  | t <sub>QScyc</sub> × 0.4                           | -                                                   | ns                 |                 |

|      | Data input setup time         | t <sub>Su</sub>    | 11                                                 | -                                                   | ns                 | Figure 2.51     |

|      | Data input hold time          | t <sub>IH</sub>    | 0                                                  | -                                                   | ns                 |                 |

|      | QSSL setup time               | t <sub>LEAD</sub>  | (N+0.5) x<br>t <sub>Qscyc</sub> - 5 * <sup>2</sup> | (N+0.5) x<br>t <sub>Qscyc</sub> +100 * <sup>2</sup> | ns                 |                 |

|      | QSSL hold time                | t <sub>LAG</sub>   | (N+0.5) x<br>t <sub>Qscyc</sub> - 5 * <sup>3</sup> | (N+0.5) x<br>t <sub>Qscyc</sub> +100 *3             | ns                 |                 |

|      | Data output delay             | t <sub>OD</sub>    | -                                                  | 4                                                   | ns                 | ]               |

|      | Data output hold time         | t <sub>ОН</sub>    | -3.3                                               | -                                                   | ns                 | ]               |

|      | Successive transmission delay | t <sub>TD</sub>    | 1                                                  | 16                                                  | t <sub>QScyc</sub> | ]               |

Note 1. t<sub>Pcyc</sub>: PCLKA cycle.

Note 2. N is set to 0 or 1 in SFMSLD.

Note 3. N is set to 0 or 1 in SFMSHD.

## Figure 2.50 QSPI clock timing

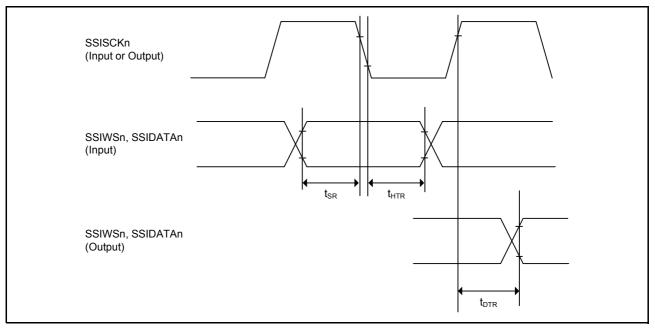

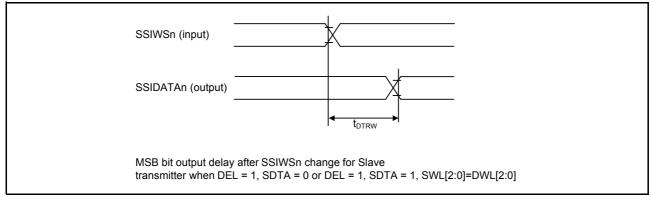

Figure 2.55 SSI data transmit and receive timing when SSICR.SCKP = 1

### Figure 2.56 SSI data output delay after SSIWSn change

### 2.3.15 SD/MMC Host Interface Timing

Table 2.30

SD/MMC Host Interface signal timing

Conditions: High drive output is selected in the port drive capability bit in the PmnPFS register.

Clock duty ratio is 50%.

| Item                          | Symbol              | Min | Max | Unit | Test conditions |

|-------------------------------|---------------------|-----|-----|------|-----------------|

| SDCLK clock cycle             | T <sub>SDCYC</sub>  | 20  | -   | ns   | Figure 2.57     |

| SDCLK clock high pulse width  | T <sub>SDWH</sub>   | 6.5 | -   | ns   |                 |

| SDCLK clock low pulse width   | T <sub>SDWL</sub>   | 6.5 | -   | ns   |                 |

| SDCLK clock rise time         | T <sub>SDLH</sub>   | -   | 3   | ns   |                 |

| SDCLK clock fall time         | T <sub>SDHL</sub>   | -   | 3   | ns   |                 |

| SDCMD/SDDAT output data delay | T <sub>SDODLY</sub> | -6  | 5   | ns   |                 |

| SDCMD/SDDAT input data setup  | T <sub>SDIS</sub>   | 4   | -   | ns   |                 |

| SDCMD/SDDAT input data hold   | T <sub>SDIH</sub>   | 2   | -   | ns   |                 |

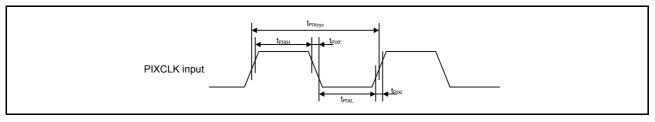

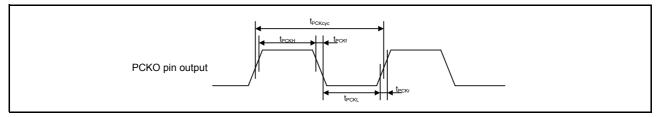

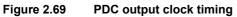

### PDC Timing 2.3.17

Table 2.32PDC timingConditions: Middle drive output is selected in the port drive capability bit in the PmnPFS register.Output load conditions:  $V_{OH}$  = VCC × 0.5,  $V_{OL}$  = VCC × 0.5, C = 30 pF

| ltem |                               | Symbol              | Min                                        | Max | Unit | Test conditions |  |

|------|-------------------------------|---------------------|--------------------------------------------|-----|------|-----------------|--|

| PDC  | PIXCLK input cycle time       | t <sub>PIXcyc</sub> | 37                                         | -   | ns   | Figure 2.68     |  |

|      | PIXCLK input high pulse width | t <sub>PIXH</sub>   | 10                                         | -   | ns   |                 |  |

|      | PIXCLK input low pulse width  | t <sub>PIXL</sub>   | 10                                         | -   | ns   |                 |  |

|      | PIXCLK rise time              | t <sub>PIXr</sub>   | -                                          | 5   | ns   |                 |  |

|      | PIXCLK fall time              | t <sub>PIXf</sub>   | -                                          | 5   | ns   |                 |  |

|      | PCKO output cycle time        | t <sub>PCKcyc</sub> | 2 × t <sub>PBcyc</sub>                     | -   | ns   | Figure 2.69     |  |

|      | PCKO output high pulse width  | t <sub>PCKH</sub>   | $(t_{PCKcyc} - t_{PCKr} - t_{PCKf})/2 - 3$ | -   | ns   |                 |  |

|      | PCKO output low pulse width   | t <sub>PCKL</sub>   | $(t_{PCKcyc} - t_{PCKr} - t_{PCKf})/2 - 3$ | -   | ns   |                 |  |

|      | PCKO rise time                | t <sub>PCKr</sub>   | -                                          | 5   | ns   |                 |  |

|      | PCKO fall time                | t <sub>PCKf</sub>   | -                                          | 5   | ns   |                 |  |

|      | VSYNV/HSYNC input setup time  | t <sub>SYNCS</sub>  | 10                                         | -   | ns   | Figure 2.70     |  |

|      | VSYNV/HSYNC input hold time   | t <sub>SYNCH</sub>  | 5                                          | -   | ns   |                 |  |

|      | PIXD input setup time         | t <sub>PIXDS</sub>  | 10                                         | -   | ns   |                 |  |

|      | PIXD input hold time          | t <sub>PIXDH</sub>  | 5                                          | -   | ns   |                 |  |

## Note 1. t<sub>PBcyc</sub>: PCLKB cycle.

Figure 2.68 PDC input clock timing

## Figure 2.70 PDC AC timing

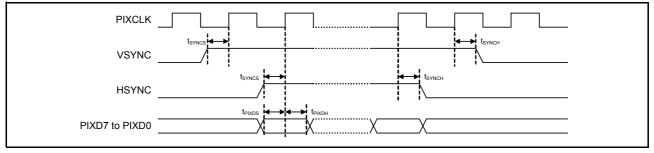

## 2.3.18 Graphics LCD Controller Timing

## Table 2.33 Graphics LCD Controller timing

Conditions:

S7G2

LCD\_CLK: High drive output is selected in the port drive capability bit in the PmnPFS register. LCD\_DATA: Middle drive output is selected in the port drive capability bit in the PmnPFS register.

| Item                                                                             | Symbol            | Min               | Тур  | Max  | Unit              | Test conditions   |             |

|----------------------------------------------------------------------------------|-------------------|-------------------|------|------|-------------------|-------------------|-------------|

| LCD_EXTCLK input clock freq                                                      | t <sub>Ecyc</sub> | -                 | -    | 60*1 | MHz               | Figure 2.71       |             |

| LCD_EXTCLK input clock low                                                       | t <sub>WL</sub>   | 0.45              | -    | 0.55 | t <sub>Ecyc</sub> |                   |             |

| LCD_EXTCLK input clock high                                                      | t <sub>WH</sub>   | 0.45              | -    | 0.55 |                   |                   |             |

| LCD_CLK output clock frequency                                                   |                   | t <sub>Lcyc</sub> | -    | -    | 60*1              | MHz               | Figure 2.72 |

| LCD_CLK output clock low put                                                     | t <sub>LOL</sub>  | 0.4               | -    | 0.6  | t <sub>Lcyc</sub> | Figure 2.72       |             |

| LCD_CLK output clock high pulse width                                            |                   | t <sub>LOH</sub>  | 0.4  | -    | 0.6               | t <sub>Lcyc</sub> | Figure 2.72 |

| LCD data output delay timing _A or _B combinations*2<br>_A and _B combinations*3 |                   | t <sub>DD</sub>   | -3.5 | -    | 4                 | ns                | Figure 2.73 |

|                                                                                  |                   |                   | -5.0 | -    | 5.5               |                   |             |

| LCD data output rise time (0.8 to 2.0 V)                                         |                   | t <sub>Dr</sub>   | -    | -    | 2                 |                   | Figure 2.74 |

| LCD data output fall time (2.0 to 0.8 V)                                         |                   | t <sub>Df</sub>   | -    | -    | 2                 |                   |             |

Note 1. Parallel RGB888, 666,565: Maximum 54 MHz Serial RGB888: Maximum 60 MHz (4x speed)

Note 2. Use pins that have a letter appended to their names, for instance, "\_A" or "\_B", to indicate

Note 3. Pins of group"\_A" and "\_B" combinations are used.

# Table 2.40 A/D conversion characteristics for unit 0 (2/2) Conditions: PCLKC = 1 to 60 MHz

| ltem                                                                        | Min                                                                    | Тур                                                            | Max                    | Unit | Test conditions |     |                                                                                                                                 |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------|------------------------|------|-----------------|-----|---------------------------------------------------------------------------------------------------------------------------------|

| Channel-dedicated<br>sample-and-hold<br>circuits in use<br>(AN000 to AN002) | Conversion time*1<br>(operation at<br>PCLKC = 60 MHz)                  | Permissible signal<br>source impedance<br>Max. = 1 kΩ          | 1.06<br>(0.4 + 0.25)*2 | -    | -               | μs  | <ul> <li>Sampling of channel-<br/>dedicated sample-and-hold<br/>circuits in 24 states</li> <li>Sampling in 15 states</li> </ul> |

|                                                                             | Offset error                                                           |                                                                | -                      | ±1.5 | ±3.5            | LSB | AN000 to AN002 = 0.25 V                                                                                                         |

|                                                                             | Full-scale error                                                       |                                                                | -                      | ±1.5 | ±3.5            | LSB | AN000 to AN002 =<br>VREFH0- 0.25 V                                                                                              |

|                                                                             | Absolute accuracy                                                      |                                                                | -                      | ±2.5 | ±5.5            | LSB | -                                                                                                                               |

|                                                                             | DNL differential nonlinearity error<br>INL integral nonlinearity error |                                                                | -                      | ±1.0 | ±2.0            | LSB | -                                                                                                                               |

|                                                                             |                                                                        |                                                                | -                      | ±1.5 | ±3.0            | LSB | -                                                                                                                               |

|                                                                             | Holding characteristics of sample-and hold circuits                    |                                                                | -                      | -    | 20              | μs  | -                                                                                                                               |

|                                                                             | Dynamic range                                                          |                                                                | 0.25                   | -    | VREFH<br>00.25  | V   | -                                                                                                                               |

| Channel-dedicated<br>sample-and-hold<br>circuits not in use                 | Conversion time*1<br>(operation at<br>PCLKC = 60 MHz)                  | Permissible signal source impedance Max. = $1  \text{k}\Omega$ | 0.88 (0.667)*2         | -    | -               | μs  | Sampling in 40 states                                                                                                           |

| (AN000 to AN002)                                                            | Offset error                                                           |                                                                | -                      | ±1.0 | ±2.5            | LSB | -                                                                                                                               |

|                                                                             | Full-scale error                                                       |                                                                | -                      | ±1.0 | ±2.5            | LSB | -                                                                                                                               |

|                                                                             | Absolute accuracy                                                      |                                                                | -                      | ±2.0 | ±4.5            | LSB | -                                                                                                                               |

|                                                                             | DNL differential nonlinearity error                                    |                                                                | -                      | ±0.5 | ±1.5            | LSB | -                                                                                                                               |