Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Active                                                         |

| Number of LABs/CLBs            | 8672                                                           |

| Number of Logic Elements/Cells | 19512                                                          |

| Total RAM Bits                 | 516096                                                         |

| Number of I/O                  | 304                                                            |

| Number of Gates                | 1200000                                                        |

| Voltage - Supply               | 1.14V ~ 1.26V                                                  |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | -40°C ~ 125°C (TJ)                                             |

| Package / Case                 | 400-BGA                                                        |

| Supplier Device Package        | 400-FBGA (21x21)                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xa3s1200e-4fgg400q |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Key Feature Differences from Commercial XC Devices

- AEC-Q100 device qualification and full production part approval process (PPAP) documentation support available in both extended temperature I- and Q-Grades

- Guaranteed to meet full electrical specification over the  $T_J = -40^{\circ}$ C to +125°C temperature range (Q-Grade)

- XA Spartan-3E devices are available in the -4 speed grade only.

- PCI-66 is not supported in the XA Spartan-3E FPGA product line.

- The readback feature is not supported in the XA

### Table 1: Summary of XA Spartan-3E FPGA Attributes

Spartan-3E FPGA product line.

- XA Spartan-3E devices are available in Step 1 only.

- JTAG configuration frequency reduced from 30 MHz to 25 MHz.

- Platform Flash is not supported within the XA family.

- XA Spartan-3E devices are available in Pb-free packaging only.

- MultiBoot is not supported in XA versions of this product.

- The XA Spartan-3E device must be power cycled prior to reconfiguration.

|           |                 | Equivalent     | (    | CLB<br>One CLB = | Array<br>Four Slic | ces)            |                                        | Block                      |                          |      |                     | Maximum                   |

|-----------|-----------------|----------------|------|------------------|--------------------|-----------------|----------------------------------------|----------------------------|--------------------------|------|---------------------|---------------------------|

| Device    | System<br>Gates | Logic<br>Cells | Rows | Columns          | Total<br>CLBs      | Total<br>Slices | Distributed<br>RAM bits <sup>(1)</sup> | RAM<br>bits <sup>(1)</sup> | Dedicated<br>Multipliers | DCMs | Maximum<br>User I/O | Differential<br>I/O Pairs |

| XA3S100E  | 100K            | 2,160          | 22   | 16               | 240                | 960             | 15K                                    | 72K                        | 4                        | 2    | 108                 | 40                        |

| XA3S250E  | 250K            | 5,508          | 34   | 26               | 612                | 2,448           | 38K                                    | 216K                       | 12                       | 4    | 172                 | 68                        |

| XA3S500E  | 500K            | 10,476         | 46   | 34               | 1,164              | 4,656           | 73K                                    | 360K                       | 20                       | 4    | 190                 | 77                        |

| XA3S1200E | 1200K           | 19,512         | 60   | 46               | 2,168              | 8,672           | 136K                                   | 504K                       | 28                       | 8    | 304                 | 124                       |

| XA3S1600E | 1600K           | 33,192         | 76   | 58               | 3,688              | 14,752          | 231K                                   | 648K                       | 36                       | 8    | 376                 | 156                       |

Notes:

1. By convention, one Kb is equivalent to 1,024 bits.

# **Architectural Overview**

The XA Spartan-3E family architecture consists of five fundamental programmable functional elements:

- Configurable Logic Blocks (CLBs) contain flexible Look-Up Tables (LUTs) that implement logic plus storage elements used as flip-flops or latches. CLBs perform a wide variety of logical functions as well as store data.

- Input/Output Blocks (IOBs) control the flow of data between the I/O pins and the internal logic of the device. Each IOB supports bidirectional data flow plus 3-state operation. Supports a variety of signal standards, including four high-performance differential standards. Double Data-Rate (DDR) registers are included.

- **Block RAM** provides data storage in the form of 18-Kbit dual-port blocks.

- **Multiplier Blocks** accept two 18-bit binary numbers as inputs and calculate the product.

Digital Clock Manager (DCM) Blocks provide self-calibrating, fully digital solutions for distributing, delaying, multiplying, dividing, and phase-shifting clock signals.

These elements are organized as shown in Figure 1. A ring of IOBs surrounds a regular array of CLBs. Each device has two columns of block RAM except for the XA3S100E, which has one column. Each RAM column consists of several 18-Kbit RAM blocks. Each block RAM is associated with a dedicated multiplier. The DCMs are positioned in the center with two at the top and two at the bottom of the device. The XA3S100E has only one DCM at the top and bottom, while the XA3S1200E and XA3S1600E add two DCMs in the middle of the left and right sides.

The XA Spartan-3E family features a rich network of traces that interconnect all five functional elements, transmitting signals among them. Each functional element has an associated switch matrix that permits multiple connections to the routing.

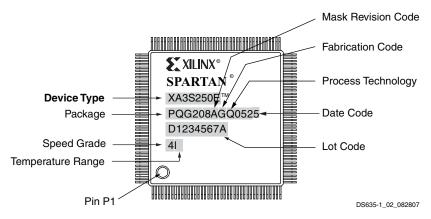

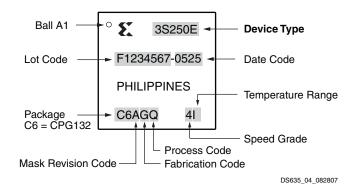

# **Package Marking**

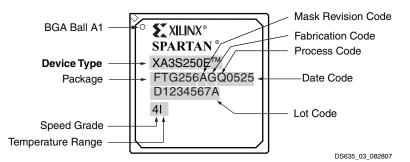

Figure 2 provides a top marking example for XA Spartan-3E FPGAs in the quad-flat packages. Figure 3 shows the top marking for XA Spartan-3E FPGAs in BGA packages except the 132-ball chip-scale package (CPG132). The markings for the BGA packages are nearly identical to those

for the quad-flat packages, except that the marking is rotated with respect to the ball A1 indicator. Figure 4 shows the top marking for XA Spartan-3E FPGAs in the CPG132 package.

Figure 2: XA Spartan-3E FPGA QFP Package Marking Example

Figure 3: XA Spartan-3E FPGA BGA Package Marking Example

Figure 4: XA Spartan-3E FPGA CPG132 Package Marking Example

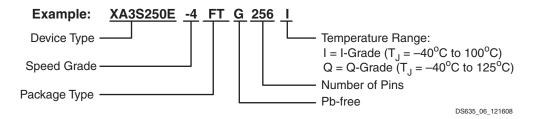

# **Ordering Information**

XA Spartan-3E FPGAs are available in Pb-free packaging options for all device/package combinations. All devices are in Pb-free packages only, with a "G" character to the ordering code. All devices are available in either I-Grade or

Q-Grade temperature ranges. Only the -4 speed grade is available for the XA Spartan-3E family. See Table 2 for valid device/package combinations.

### Pb-Free Packaging

| Device    |    | Speed Grade |        | Package Type / Number of Pins                    |   | Temperature Range (T <sub>J</sub> ) |

|-----------|----|-------------|--------|--------------------------------------------------|---|-------------------------------------|

| XA3S100E  | -4 | Only        | VQG100 | 100-pin Very Thin Quad Flat Pack (VQFP)          | I | I-Grade (-40°C to 100°C)            |

| XA3S250E  |    | l           | CPG132 | 132-ball Chip-Scale Package (CSP)                | Q | Q-Grade (-40°C to 125°C)            |

| XA3S500E  |    |             | TQG144 | 144-pin Thin Quad Flat Pack (TQFP)               | 1 |                                     |

| XA3S1200E |    |             | PQG208 | 208-pin Plastic Quad Flat Pack (PQFP)            |   |                                     |

| XA3S1600E |    |             | FTG256 | 256-ball Fine-Pitch Thin Ball Grid Array (FTBGA) |   |                                     |

|           |    |             | FGG400 | 400-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                     |

|           |    |             | FGG484 | 484-ball Fine-Pitch Ball Grid Array (FBGA)       |   |                                     |

# **DC Specifications**

### Table 6: General Recommended Operating Conditions

| Symbol                               | Descriptio                                                       | n                             | Min   | Nominal | Max                    | Units |

|--------------------------------------|------------------------------------------------------------------|-------------------------------|-------|---------|------------------------|-------|

| TJ                                   | Junction temperature                                             | I-Grade                       | -40   | 25      | 100                    | °C    |

|                                      |                                                                  | Q-Grade                       | -40   | 25      | 125                    | °C    |

| V <sub>CCINT</sub>                   | Internal supply voltage                                          | 1.140                         | 1.200 | 1.260   | V                      |       |

| V <sub>CCO</sub> <sup>(1)</sup>      | Output driver supply voltage                                     | 1.100                         | -     | 3.465   | V                      |       |

| V <sub>CCAUX</sub>                   | Auxiliary supply voltage                                         |                               | 2.375 | 2.500   | 2.625                  | V     |

| $\Delta V_{CCAUX}^{(2)}$             | Voltage variance on $V_{CCAUX}$ whe                              | en using a DCM                | -     | -       | 10                     | mV/ms |

| V <sub>IN</sub> <sup>(3,4,5,6)</sup> | Input voltage extremes to avoid turning on I/O protection diodes |                               |       | -       | V <sub>CCO</sub> + 0.5 | V     |

|                                      |                                                                  | Dedicated pins <sup>(4)</sup> | -0.5  | -       | $V_{CCAUX} + 0.5$      | V     |

| T <sub>IN</sub>                      | Input signal transition time <sup>(7)</sup>                      | 1                             | _     | -       | 500                    | ns    |

#### Notes:

- 1. This  $V_{CCO}$  range spans the lowest and highest operating voltages for all supported I/O standards. Table 9 lists the recommended  $V_{CCO}$  range specific to each of the single-ended I/O standards, and Table 11 lists that specific to the differential standards.

- 2. Only during DCM operation is it recommended that the rate of change of  $V_{CCAUX}$  not exceed 10 mV/ms.

- Each of the User I/O and Dual-Purpose pins is associated with one of the four banks' V<sub>CCO</sub> rails. Meeting the V<sub>IN</sub> limit ensures that the internal diode junctions that exist between these pins and their associated V<sub>CCO</sub> and GND rails do not turn on. See Absolute Maximum Ratings in <u>DS312</u>).

- 4. All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) draw power from the V<sub>CCAUX</sub> rail (2.5V). Meeting the V<sub>IN</sub> max limit ensures that the internal diode junctions that exist between each of these pins and the V<sub>CCAUX</sub> and GND rails do not turn on.

- 5. Input voltages outside the recommended range is permissible provided that the I<sub>IK</sub> input clamp diode rating is met and no more than 100 pins exceed the range simultaneously. See Absolute Maximum Ratings in <u>DS312</u>).

- 6. See XAPP459, "Eliminating I/O Coupling Effects when Interfacing Large-Swing Single-Ended Signals to User I/O Pins."

- 7. Measured between 10% and 90%  $V_{CCO}$ . Follow Signal Integrity recommendations.

# General DC Characteristics for I/O Pins

### Table 7: General DC Characteristics of User I/O, Dual-Purpose, and Dedicated Pins

| Symbol                          | Description                                                                          | Test Conditions                                                                    | Min   | Тур  | Max   | Units |

|---------------------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------|------|-------|-------|

| ΙL                              | Leakage current at User I/O,<br>Input-only, Dual-Purpose, and<br>Dedicated pins      | Driver is in a high-impedance state, $V_{IN} = 0V$ or $V_{CCO}$ max, sample-tested | -10   | _    | +10   | μA    |

| I <sub>RPU</sub> <sup>(2)</sup> | Current through pull-up resistor at                                                  | $V_{IN} = 0V, V_{CCO} = 3.3V$                                                      | -0.36 | _    | -1.24 | mA    |

|                                 | User I/O, Dual-Purpose, Input-only, and Dedicated pins                               | $V_{IN} = 0V, V_{CCO} = 2.5V$                                                      | -0.22 | -    | -0.80 | mA    |

|                                 |                                                                                      | $V_{IN} = 0V, V_{CCO} = 1.8V$                                                      | -0.10 |      | -0.42 | mA    |

|                                 |                                                                                      | $V_{IN} = 0V, V_{CCO} = 1.5V$                                                      | -0.06 | 0.27 |       | mA    |

|                                 |                                                                                      | $V_{IN} = 0V, V_{CCO} = 1.2V$                                                      | -0.04 | _    | -0.22 | mA    |

| R <sub>PU</sub> <sup>(2)</sup>  | Equivalent pull-up resistor value at                                                 | $V_{IN} = 0V, V_{CCO} = 3.0V \text{ to } 3.465V$                                   | 2.4   | -    | 10.8  | kΩ    |

|                                 | User I/O, Dual-Purpose, Input-only,<br>and Dedicated pins (based on I <sub>BPU</sub> | $V_{IN} = 0V, V_{CCO} = 2.3V \text{ to } 2.7V$                                     | 2.7   | -    | 11.8  | kΩ    |

|                                 | per Note 2)                                                                          | $V_{IN} = 0V, V_{CCO} = 1.7V \text{ to } 1.9V$                                     | 4.3   | _    | 20.2  | kΩ    |

|                                 |                                                                                      | $V_{IN} = 0V, V_{CCO} = 1.4V \text{ to } 1.6V$                                     | 5.0   | -    | 25.9  | kΩ    |

|                                 |                                                                                      | $V_{IN} = 0V, V_{CCO} = 1.14V$ to 1.26V                                            | 5.5   | -    | 32.0  | kΩ    |

| Symbol                                                                               | Description                                                                                                                         | Test Conditions                                                                                         | Min  | Тур  | Max          | Units |

|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------|------|--------------|-------|

| I <sub>RPD</sub> <sup>(2)</sup>                                                      | Current through pull-down resistor at<br>User I/O, Dual-Purpose, Input-only,<br>and Dedicated pins                                  | $V_{IN} = V_{CCO}$                                                                                      | 0.10 | _    | 0.75         | mA    |

| $R_{PD}^{(2)}$                                                                       | Equivalent pull-down resistor value at                                                                                              | $V_{IN} = V_{CCO} = 3.0V$ to 3.45V                                                                      | 4.0  | -    | 34.5         | kΩ    |

| User I/O, Dual-Purpose, Input-only,<br>and Dedicated pins (based on I <sub>BPD</sub> | $V_{IN} = V_{CCO} = 2.3V$ to 2.7V                                                                                                   | 3.0                                                                                                     | _    | 27.0 | kΩ           |       |

|                                                                                      | per Note 2)                                                                                                                         | $V_{IN} = V_{CCO} = 1.7V$ to 1.9V                                                                       | 2.3  | _    | 19.0<br>16.0 | kΩ    |

|                                                                                      |                                                                                                                                     | $V_{IN} = V_{CCO} = 1.4V$ to 1.6V                                                                       | 1.8  | _    |              | kΩ    |

|                                                                                      |                                                                                                                                     | $V_{IN} = V_{CCO} = 1.14V$ to 1.26V                                                                     | 1.5  | -    | 12.6         | kΩ    |

| I <sub>REF</sub>                                                                     | V <sub>REF</sub> current per pin                                                                                                    | All V <sub>CCO</sub> levels                                                                             | -10  | _    | +10          | μA    |

| C <sub>IN</sub>                                                                      | Input capacitance                                                                                                                   | -                                                                                                       | -    | _    | 10           | pF    |

| R <sub>DT</sub>                                                                      | Resistance of optional differential<br>termination circuit within a differential<br>I/O pair. Not available on Input-only<br>pairs. | $V_{OCM} Min \le V_{ICM} \le V_{OCM} Max$<br>$V_{OD} Min \le V_{ID} \le V_{OD} Max$<br>$V_{CCO} = 2.5V$ | _    | 120  | _            | Ω     |

## Table 7: General DC Characteristics of User I/O, Dual-Purpose, and Dedicated Pins (Continued)

#### Notes:

1. The numbers in this table are based on the conditions set forth in Table 6.

2. This parameter is based on characterization. The pull-up resistance  $R_{PU} = V_{CCO} / I_{RPU}$ . The pull-down resistance  $R_{PD} = V_{IN} / I_{RPD}$ .

| Symbol              | Description                  | Device    | I-Grade Maximum | Q-Grade<br>Maximum | Units |

|---------------------|------------------------------|-----------|-----------------|--------------------|-------|

| I <sub>CCINTQ</sub> | Quiescent V <sub>CCINT</sub> | XA3S100E  | 36              | 58                 | mA    |

|                     | supply current               | XA3S250E  | 104             | 158                | mA    |

|                     |                              | XA3S500E  | 145             | 300                | mA    |

|                     |                              | XA3S1200E | 324             | 500                | mA    |

|                     |                              | XA3S1600E | 457             | 750                | mA    |

| I <sub>CCOQ</sub>   | Quiescent V <sub>CCO</sub>   | XA3S100E  | 1.5             | 2.0                | mA    |

|                     | supply current               | XA3S250E  | 1.5             | 3.0                | mA    |

|                     |                              | XA3S500E  | 1.5             | 3.0                | mA    |

|                     |                              | XA3S1200E | 2.5             | 4.0                | mA    |

|                     |                              | XA3S1600E | 2.5             | 4.0                | mA    |

| Symbol              | Description                  | Device    | I-Grade Maximum | Q-Grade<br>Maximum | Units |

|---------------------|------------------------------|-----------|-----------------|--------------------|-------|

| I <sub>CCAUXQ</sub> | Quiescent V <sub>CCAUX</sub> | XA3S100E  | 13              | 22                 | mA    |

|                     | supply current               | XA3S250E  | 26              | 43                 | mA    |

|                     |                              | XA3S500E  | 34              | 63                 | mA    |

|                     |                              | XA3S1200E | 59              | 100                | mA    |

|                     |                              | XA3S1600E | 86              | 150                | mA    |

### Table 8: Quiescent Supply Current Characteristics (Continued)

#### Notes:

- 1. The numbers in this table are based on the conditions set forth in Table 6.

- The numbers in this table are based on the conditions set for the half of the conditions of the conditions of the conditions and the conditions of the condit

- There are two recommended ways to estimate the total power consumption (quiescent plus dynamic) for a specific design: a) The <u>Spartan-3E XPower Estimator</u> provides quick, approximate, typical estimates, and does not require a netlist of the design. b) XPower <u>Analyzer uses a netlist as input to provide maximum estimates as well as more accurate typical estimates.</u>

- 4. The maximum numbers in this table indicate the minimum current each power rail requires in order for the FPGA to power-on successfully.

### Single-Ended I/O Standards

| Table O: Decommonded Operation | a Conditions for Lloor 1/0a | Lloing Single Ended Standarde  |

|--------------------------------|-----------------------------|--------------------------------|

| Table 9: Recommended Operatin  | y contaitions for user i/us | S USING SINGLE-Ended Standards |

| IOSTANDARD                | TANDARD V <sub>CCO</sub> for Drivers <sup>(2)</sup> V <sub>REF</sub> |         |         |         |                                          |         |                          | V <sub>IH</sub>          |

|---------------------------|----------------------------------------------------------------------|---------|---------|---------|------------------------------------------|---------|--------------------------|--------------------------|

| Attribute                 | Min (V)                                                              | Nom (V) | Max (V) | Min (V) | Nom (V)                                  | Max (V) | Max (V)                  | Min (V)                  |

| LVTTL                     | 3.0                                                                  | 3.3     | 3.465   |         |                                          |         | 0.8                      | 2.0                      |

| LVCMOS33 <sup>(4)</sup>   | 3.0                                                                  | 3.3     | 3.465   |         |                                          |         | 0.8                      | 2.0                      |

| LVCMOS25 <sup>(4,5)</sup> | 2.3                                                                  | 2.5     | 2.7     |         |                                          |         | 0.7                      | 1.7                      |

| LVCMOS18                  | 1.65                                                                 | 1.8     | 1.95    |         | <sub>EF</sub> is not use<br>se I/O stand |         | 0.4                      | 0.8                      |

| LVCMOS15                  | 1.4                                                                  | 1.5     | 1.6     |         |                                          |         | 0.4                      | 0.8                      |

| LVCMOS12                  | 1.1                                                                  | 1.2     | 1.3     |         |                                          |         | 0.4                      | 0.7                      |

| PCI33_3                   | 3.0                                                                  | 3.3     | 3.465   |         |                                          |         | 0.3 * V <sub>CCO</sub>   | 0.5 * V <sub>CCO</sub>   |

| HSTL_I_18                 | 1.7                                                                  | 1.8     | 1.9     | 0.8     | 0.9                                      | 1.1     | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |

| HSTL_III_18               | 1.7                                                                  | 1.8     | 1.9     | -       | 1.1                                      | -       | V <sub>REF</sub> - 0.1   | V <sub>REF</sub> + 0.1   |

| SSTL18_I                  | 1.7                                                                  | 1.8     | 1.9     | 0.833   | 0.833 0.900 0.969                        |         |                          | V <sub>REF</sub> + 0.125 |

| SSTL2_I                   | 2.3                                                                  | 2.5     | 2.7     | 1.15    | 1.25                                     | 1.35    | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 |

#### Notes:

- 1. Descriptions of the symbols used in this table are as follows:

- $\label{eq:V_CCO} V_{CCO} \text{the supply voltage for output drivers} \\ V_{REF} \text{the reference voltage for setting the input switching threshold} \\ V_{IL} \text{the input voltage that indicates a Low logic level} \\ V_{IH} \text{the input voltage that indicates a High logic level} \\ \end{array}$

- 2. The V<sub>CCO</sub> rails supply only output drivers, not input circuits.

- For device operation, the maximum signal voltage ( $V_{IH}$  max) may be as high as  $V_{IN}$  max. See Table 72 in DS312. З.

- There is approximately 100 mV of hysteresis on inputs using LVCMOS33 and LVCMOS25 I/O standards. 4.

- All Dedicated pins (PROG\_B, DONE, TCK, TDI, TDO, and TMS) use the LVCMOS25 standard and draw power from the V<sub>CCAUX</sub> rail (2.5V). 5. The Dual-Purpose configuration pins use the LVCMOS standard before the User mode. When using these pins as part of a standard 2.5V configuration interface, apply 2.5V to the  $V_{CCO}$  lines of Banks 0, 1, and 2 at power-on as well as throughout configuration.

- For information on PCI IP solutions, see www.xilinx.com/pci. 6.

### **Differential I/O Standards**

|                          | V <sub>CCO</sub> for Drivers <sup>(1)</sup> |             |         |             | V <sub>ID</sub> |             | V <sub>ICM</sub> |         |         |  |

|--------------------------|---------------------------------------------|-------------|---------|-------------|-----------------|-------------|------------------|---------|---------|--|

| IOSTANDARD<br>Attribute  | Min (V)                                     | Nom (V)     | Max (V) | Min<br>(mV) | Nom<br>(mV)     | Max<br>(mV) | Min (V)          | Nom (V) | Max (V) |  |

| LVDS_25                  | 2.375                                       | 2.50        | 2.625   | 100         | 350             | 600         | 0.30             | 1.25    | 2.20    |  |

| BLVDS_25                 | 2.375                                       | 2.50        | 2.625   | 100         | 350             | 600         | 0.30             | 1.25    | 2.20    |  |

| MINI_LVDS_25             | 2.375                                       | 2.50        | 2.625   | 200         | -               | 600         | 0.30             | -       | 2.2     |  |

| LVPECL_25 <sup>(2)</sup> |                                             | Inputs Only |         | 100         | 800             | 1000        | 0.5              | 1.2     | 2.0     |  |

| RSDS_25                  | 2.375                                       | 2.50        | 2.625   | 100         | 200             | -           | 0.3              | 1.20    | 1.4     |  |

| DIFF_HSTL_I_18           | 1.7                                         | 1.8         | 1.9     | 100         | -               | -           | 0.8              | -       | 1.1     |  |

| DIFF_HSTL_III_18         | 1.7                                         | 1.8         | 1.9     | 100         | -               | -           | 0.8              | -       | 1.1     |  |

| DIFF_SSTL18_I            | 1.7                                         | 1.8         | 1.9     | 100         | -               | -           | 0.7              | -       | 1.1     |  |

| DIFF_SSTL2_I             | 2.3                                         | 2.5         | 2.7     | 100         | -               | -           | 1.0              | -       | 1.5     |  |

### Table 11: Recommended Operating Conditions for User I/Os Using Differential Signal Standards

#### Notes:

1. The  $V_{CCO}$  rails supply only differential output drivers, not input circuits.

2. V<sub>REF</sub> inputs are not used for any of the differential I/O standards.

### Table 12: DC Characteristics of User I/Os Using Differential Signal Standards

|                         |             | V <sub>OD</sub> |             | ΔV          | ОD          |            | V <sub>OCM</sub> |            | ΔV <sub>C</sub> | ОСМ         | V <sub>OH</sub>         | V <sub>OL</sub>         |

|-------------------------|-------------|-----------------|-------------|-------------|-------------|------------|------------------|------------|-----------------|-------------|-------------------------|-------------------------|

| IOSTANDARD<br>Attribute | Min<br>(mV) | Typ<br>(mV)     | Max<br>(mV) | Min<br>(mV) | Max<br>(mV) | Min<br>(V) | Тур<br>(V)       | Max<br>(V) | Min<br>(mV)     | Max<br>(mV) | Min<br>(V)              | Max<br>(V)              |

| LVDS_25                 | 250         | 350             | 450         | -           | -           | 1.125      | -                | 1.375      | -               | -           | -                       | -                       |

| BLVDS_25                | 250         | 350             | 450         | -           | -           | -          | 1.20             | -          | -               | -           | -                       | -                       |

| MINI_LVDS_25            | 300         | -               | 600         | -           | 50          | 1.0        | -                | 1.4        | -               | 50          | -                       | -                       |

| RSDS_25                 | 100         | -               | 400         | -           | -           | 1.1        | -                | 1.4        | -               | -           | -                       | -                       |

| DIFF_HSTL_I_18          | -           | -               | -           | -           | -           | -          | -                | -          | -               | -           | $V_{CCO} - 0.4$         | 0.4                     |

| DIFF_HSTL_III_18        | -           | -               | -           | -           | -           | -          | -                | -          | -               | -           | $V_{CCO} - 0.4$         | 0.4                     |

| DIFF_SSTL18_I           | -           | -               | _           | -           | -           | -          | -                | -          | -               | -           | V <sub>TT</sub> + 0.475 | V <sub>TT</sub> – 0.475 |

| DIFF_SSTL2_I            | -           | -               | -           | -           | _           | _          | -                | -          | _               | _           | V <sub>TT</sub> + 0.61  | V <sub>TT</sub> – 0.61  |

#### Notes:

1. The numbers in this table are based on the conditions set forth in Table 6, and Table 11.

2. Output voltage measurements for all differential standards are made with a termination resistor (R<sub>T</sub>) of 100Ω across the N and P pins of the differential signal pair. The exception is for BLVDS, shown in Figure 5 below.

3. At any given time, no more than two of the following differential output standards may be assigned to an I/O bank: LVDS\_25, RSDS\_25, MINI\_LVDS\_25

# XILINX<sup>®</sup>

|                                                                 |                                                                                                                        |                                                                              | IFD_<br>DELAY_                             |           | -4 Speed<br>Grade |       |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------|-----------|-------------------|-------|

| Symbol                                                          | Description                                                                                                            | Conditions                                                                   | VALUE=                                     | Device    | Min               | Units |

| Setup Time                                                      | s                                                                                                                      |                                                                              | <u>.</u>                                   |           |                   |       |

| T <sub>PSDCM</sub>                                              | When writing to the Input Flip-Flop                                                                                    | LVCMOS25 <sup>(2)</sup> ,                                                    | 0                                          | XA3S100E  | 2.98              | ns    |

| data at<br>transiti<br>The D0                                   | (IFF), the time from the setup of data at the Input pin to the active                                                  | IFD_DELAY_VALUE = 0, with $DCM^{(4)}$                                        |                                            | XA3S250E  | 2.59              | ns    |

|                                                                 | transition at a Global Clock pin.                                                                                      |                                                                              |                                            | XA3S500E  | 2.59              | ns    |

|                                                                 | The DCM is used. No Input Delay                                                                                        |                                                                              |                                            | XA3S1200E | 2.58              | ns    |

|                                                                 | is programmed.                                                                                                         |                                                                              |                                            | XA3S1600E | 2.59              | ns    |

| T <sub>PSFD</sub>                                               | PSFD When writing to IFF, the time from<br>the setup of data at the Input pin to<br>an active transition at the Global |                                                                              |                                            | XA3S100E  | 3.58              | ns    |

|                                                                 |                                                                                                                        |                                                                              | IFD_DELAY_VALUE = default software setting | 3         | XA3S250E          | 3.91  |

| Clock pin. The DCM is not used.                                 | denaur contrare county                                                                                                 | 2                                                                            | XA3S500E                                   | 4.02      | ns                |       |

|                                                                 | The Input Delay is programmed.                                                                                         |                                                                              | 5                                          | XA3S1200E | 5.52              | ns    |

|                                                                 |                                                                                                                        |                                                                              | 4                                          | XA3S1600E | 4.46              | ns    |

| Hold Times                                                      |                                                                                                                        |                                                                              |                                            |           |                   |       |

| T <sub>PHDCM</sub>                                              | When writing to IFF, the time from                                                                                     | LVCMOS25 <sup>(3)</sup> ,<br>IFD_DELAY_VALUE = 0,<br>with DCM <sup>(4)</sup> | 0                                          | XA3S100E  | -0.52             | ns    |

|                                                                 | the active transition at the Global<br>Clock pin to the point when data                                                |                                                                              |                                            | XA3S250E  | 0.14              | ns    |

|                                                                 | must be held at the Input pin. The                                                                                     |                                                                              |                                            | XA3S500E  | 0.14              | ns    |

|                                                                 | DCM is used. No Input Delay is                                                                                         |                                                                              |                                            | XA3S1200E | 0.15              | ns    |

|                                                                 | programmed.                                                                                                            |                                                                              |                                            | XA3S1600E | 0.14              | ns    |

| T <sub>PHFD</sub>                                               | When writing to IFF, the time from                                                                                     | LVCMOS25 <sup>(3)</sup> ,                                                    | 2                                          | XA3S100E  | -0.24             | ns    |

|                                                                 | the active transition at the Global<br>Clock pin to the point when data                                                | IFD_DELAY_VALUE =<br>default software setting                                | 3                                          | XA3S250E  | -0.32             | ns    |

| must be held at the Input pin.<br>DCM is not used. The Input De | must be held at the Input pin. The                                                                                     | ueiauli suliwale selling                                                     | 2                                          | XA3S500E  | -0.49             | ns    |

|                                                                 | DCM is not used. The Input Delay                                                                                       |                                                                              | 5                                          | XA3S1200E | -0.63             | ns    |

|                                                                 | is programmed.                                                                                                         |                                                                              | 4                                          | XA3S1600E | -0.39             | ns    |

### Table 14: Pin-to-Pin Setup and Hold Times for the IOB Input Path (System Synchronous)

Notes:

1. The numbers in this table are tested using the methodology presented in Table 19 and are based on the operating conditions set forth in Table 6 and Table 9.

2. This setup time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, subtract the appropriate adjustment from Table 17. If this is true of the data Input, add the appropriate Input adjustment from the same table.

3. This hold time requires adjustment whenever a signal standard other than LVCMOS25 is assigned to the Global Clock Input or the data Input. If this is true of the Global Clock Input, add the appropriate Input adjustment from Table 17. If this is true of the data Input, subtract the appropriate Input adjustment from the same table. When the hold time is negative, it is possible to change the data before the clock's active edge.

4. DCM output jitter is included in all measurements.

| Convert C<br>LVCMOS25 w<br>Fast Slew Ra<br>Signal Stand | ate to the F | Drive and<br>ollowing | Add the<br>Adjustment<br>Below<br>-4 Speed<br>Grade | Units |

|---------------------------------------------------------|--------------|-----------------------|-----------------------------------------------------|-------|

| Single-Ended                                            | =            | ,                     |                                                     |       |

|                                                         | Slow         | 2 mA                  | 5.41                                                | ns    |

|                                                         |              | 4 mA                  | 2.41                                                | ns    |

|                                                         |              | 6 mA                  | 1.90                                                | ns    |

|                                                         |              | 8 mA                  | 0.67                                                | ns    |

|                                                         |              | 12 mA                 | 0.70                                                | ns    |

|                                                         |              | 16 mA                 | 0.43                                                | ns    |

|                                                         | Fast         | 2 mA                  | 5.00                                                | ns    |

|                                                         |              | 4 mA                  | 1.96                                                | ns    |

|                                                         |              | 6 mA                  | 1.45                                                | ns    |

|                                                         |              | 8 mA                  | 0.34                                                | ns    |

|                                                         |              | 12 mA                 | 0.30                                                | ns    |

|                                                         |              | 16 mA                 | 0.30                                                | ns    |

| LVCMOS33                                                | Slow         | 2 mA                  | 5.29                                                | ns    |

|                                                         |              | 4 mA                  | 1.89                                                | ns    |

|                                                         |              | 6 mA                  | 1.04                                                | ns    |

|                                                         |              | 8 mA                  | 0.69                                                | ns    |

|                                                         |              | 12 mA                 | 0.42                                                | ns    |

|                                                         |              | 16 mA                 | 0.43                                                | ns    |

|                                                         | Fast         | 2 mA                  | 4.87                                                | ns    |

|                                                         |              | 4 mA                  | 1.52                                                | ns    |

|                                                         |              | 6 mA                  | 0.39                                                | ns    |

|                                                         |              | 8 mA                  | 0.34                                                | ns    |

|                                                         |              | 12 mA                 | 0.30                                                | ns    |

|                                                         |              | 16 mA                 | 0.30                                                | ns    |

| LVCMOS25                                                | Slow         | 2 mA                  | 4.21                                                | ns    |

|                                                         |              | 4 mA                  | 2.26                                                | ns    |

|                                                         |              | 6 mA                  | 1.52                                                | ns    |

|                                                         |              | 8 mA                  | 1.08                                                | ns    |

|                                                         |              | 12 mA                 | 0.68                                                | ns    |

|                                                         | Fast         | 2 mA                  | 3.67                                                | ns    |

|                                                         |              | 4 mA                  | 1.72                                                | ns    |

|                                                         |              | 6 mA                  | 0.46                                                | ns    |

|                                                         |              | 8 mA                  | 0.21                                                | ns    |

|                                                         |              | 12 mA                 | 0                                                   | ns    |

#### Table 18: Output Timing Adjustments for IOB

### Table 18: Output Timing Adjustments for IOB (Continued)

| Convert Output Time from<br>LVCMOS25 with 12mA Drive and<br>Fast Slew Rate to the Following |                              | Add the<br>Adjustment<br>Below<br>-4 Speed<br>Grade | -          |       |

|---------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------|------------|-------|

|                                                                                             | Signal Standard (IOSTANDARD) |                                                     |            | Units |

| LVCMOS18                                                                                    | Slow                         | 2 mA                                                | 5.24       | ns    |

|                                                                                             |                              | 4 mA                                                | 3.21       | ns    |

|                                                                                             |                              | 6 mA                                                | 2.49       | ns    |

|                                                                                             | 8 mA                         |                                                     | 1.90       | ns    |

|                                                                                             | Fast 2 mA                    |                                                     | 4.15       | ns    |

|                                                                                             |                              | 4 mA                                                | 2.13       | ns    |

|                                                                                             |                              | 6 mA                                                | 1.14       | ns    |

|                                                                                             |                              | 8 mA                                                | 0.75       | ns    |

| LVCMOS15                                                                                    | Slow                         | 2 mA                                                | 4.68       | ns    |

|                                                                                             |                              | 4 mA                                                | 3.97       | ns    |

|                                                                                             |                              | 6 mA                                                | 3.11       | ns    |

|                                                                                             | Fast                         | 2 mA                                                | 3.38       | ns    |

|                                                                                             |                              | 4 mA                                                | 2.70       | ns    |

|                                                                                             |                              | 6 mA                                                | 1.53       | ns    |

| LVCMOS12                                                                                    | Slow                         | 2 mA                                                | 6.63       | ns    |

|                                                                                             | Fast                         | 2 mA                                                | 4.44       | ns    |

| HSTL_I_18                                                                                   |                              |                                                     | 0.34       | ns    |

| HSTL_III_18                                                                                 |                              |                                                     | 0.55       | ns    |

| PCI33_3                                                                                     |                              |                                                     | 0.46       | ns    |

| SSTL18_I                                                                                    |                              |                                                     | 0.25       | ns    |

| SSTL2_I                                                                                     |                              |                                                     | -0.20      | ns    |

| Differential Sta                                                                            | ndards                       |                                                     | !          |       |

| LVDS_25                                                                                     |                              |                                                     | -0.55      | ns    |

| BLVDS_25                                                                                    |                              |                                                     | 0.04       | ns    |

| MINI_LVDS_25                                                                                |                              |                                                     | -0.56      | ns    |

| LVPECL_25                                                                                   |                              |                                                     | Input Only | ns    |

| RSDS_25                                                                                     |                              |                                                     | -0.48      | ns    |

| DIFF_HSTL_I_18                                                                              |                              |                                                     | 0.42       | ns    |

| DIFF_HSTL_III_18                                                                            |                              |                                                     | 0.55       | ns    |

| DIFF_SSTL18_I                                                                               |                              |                                                     | 0.40       | ns    |

| DIFF_SSTL2_I                                                                                |                              |                                                     | 0.44       | ns    |

#### Notes:

1. The numbers in this table are tested using the methodology presented in Table 19 and are based on the operating conditions set forth in Table 6, Table 9, and Table 11.

These adjustments are used to convert output- and three-state-path times originally specified for the LVCMOS25 standard with 12 mA drive and Fast slew rate to times that correspond to other signal standards. Do not adjust times that measure when outputs go into a high-impedance state.

# **Configurable Logic Block Timing**

Table 20: CLB (SLICEM) Timing

|                      |                                                                                                                                         | -4 Spee | ed Grade |       |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---------|----------|-------|

| Symbol               | Description                                                                                                                             | Min     | Max      | Units |

| Clock-to-Output      | Times                                                                                                                                   |         |          |       |

| Т <sub>СКО</sub>     | When reading from the FFX (FFY) Flip-Flop, the time from the active transition at the CLK input to data appearing at the XQ (YQ) output | -       | 0.60     | ns    |

| Setup Times          | -                                                                                                                                       |         | ļ.       | Į     |

| T <sub>AS</sub>      | Time from the setup of data at the F or G input to the active transition at the CLK input of the CLB                                    | 0.52    | -        | ns    |

| T <sub>DICK</sub>    | Time from the setup of data at the BX or BY input to the active transition at the CLK input of the CLB                                  | 1.81    | -        | ns    |

| Hold Times           | 1                                                                                                                                       |         |          |       |

| T <sub>AH</sub>      | Time from the active transition at the CLK input to the point where data is last held at the F or G input                               | 0       | -        | ns    |

| T <sub>CKDI</sub>    | Time from the active transition at the CLK input to the point where data is last held at the BX or BY input                             | 0       | -        | ns    |

| Clock Timing         |                                                                                                                                         |         |          | I     |

| Т <sub>СН</sub>      | The High pulse width of the CLB's CLK signal                                                                                            | 0.80    | -        | ns    |

| T <sub>CL</sub>      | The Low pulse width of the CLK signal                                                                                                   | 0.80    | -        | ns    |

| F <sub>TOG</sub>     | Toggle frequency (for export control)                                                                                                   | 0       | 572      | MHz   |

| Propagation Tim      | es                                                                                                                                      |         | 1        | l     |

| T <sub>ILO</sub>     | The time it takes for data to travel from the CLB's F (G) input to the X (Y) output                                                     | -       | 0.76     | ns    |

| Set/Reset Pulse      | Width                                                                                                                                   |         | L        | 1     |

| T <sub>RPW_CLB</sub> | The minimum allowable pulse width, High or Low, to the CLB's SR input                                                                   | 1.80    | -        | ns    |

Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 6.

## **Clock Buffer/Multiplexer Switching Characteristics**

### Table 23: Clock Distribution Switching Characteristics

|                                                                                                             |                   | Maximum        |       |

|-------------------------------------------------------------------------------------------------------------|-------------------|----------------|-------|

| Description                                                                                                 | Symbol            | -4 Speed Grade | Units |

| Global clock buffer (BUFG, BUFGMUX, BUFGCE) I input to O-output delay                                       | T <sub>GIO</sub>  | 1.46           | ns    |

| Global clock multiplexer (BUFGMUX) select S-input setup to I0 and I1 inputs. Same as BUFGCE enable CE-input | T <sub>GSI</sub>  | 0.63           | ns    |

| Frequency of signals distributed on global buffers (all sides)                                              | F <sub>BUFG</sub> | 311            | MHz   |

## 18 x 18 Embedded Multiplier Timing

### Table 24: 18 x 18 Embedded Multiplier Timing

|                                              |                                                                                                                                                                          | -4 Spee | ed Grade            |       |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------|-------|

| Symbol                                       | Description                                                                                                                                                              | Min     | Max                 | Units |

| Combinatoria                                 | l Delay                                                                                                                                                                  |         |                     |       |

| T <sub>MULT</sub>                            | Combinatorial multiplier propagation delay from the A and B inputs to the P outputs, assuming 18-bit inputs and a 36-bit product (AREG, BREG, and PREG registers unused) | -       | 4.88 <sup>(1)</sup> | ns    |

| Clock-to-Outp                                | out Times                                                                                                                                                                | L       | 1                   |       |

| T <sub>MSCKP_P</sub>                         | Clock-to-output delay from the active transition of the CLK input to valid data appearing on the P outputs when using the PREG register <sup>(2)</sup>                   | -       | 1.10                | ns    |

| T <sub>MSCKP_A</sub><br>T <sub>MSCKP_B</sub> | Clock-to-output delay from the active transition of the CLK input to valid data appearing on the P outputs when using either the AREG or BREG register <sup>(3)</sup>    | -       | 4.97                | ns    |

| Setup Times                                  |                                                                                                                                                                          | L       | 1                   |       |

| T <sub>MSDCK_P</sub>                         | Data setup time at the A or B input before the active transition at the CLK when using only the PREG output register (AREG, BREG registers unused) <sup>(2)</sup>        | 3.98    | -                   | ns    |

| T <sub>MSDCK_A</sub>                         | Data setup time at the A input before the active transition at the CLK when using the AREG input register $^{\rm (3)}$                                                   | 0.23    | -                   | ns    |

| T <sub>MSDCK_B</sub>                         | Data setup time at the B input before the active transition at the CLK when using the BREG input register $^{\rm (3)}$                                                   | 0.39    | -                   | ns    |

| Hold Times                                   |                                                                                                                                                                          | L       |                     |       |

| T <sub>MSCKD_P</sub>                         | Data hold time at the A or B input before the active transition at the CLK when using only the PREG output register (AREG, BREG registers unused) <sup>(2)</sup>         | -0.97   |                     |       |

| T <sub>MSCKD_A</sub>                         | Data hold time at the A input before the active transition at the CLK when using the AREG input register $^{\rm (3)}$                                                    | 0.04    |                     |       |

| T <sub>MSCKD_B</sub>                         | Data hold time at the B input before the active transition at the CLK when using the BREG input register <sup><math>(3)</math></sup>                                     | 0.05    |                     |       |

### Table 24: 18 x 18 Embedded Multiplier Timing (Continued)

|                   |                                                                                                                                                   | -4 Speed Grade |     |       |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|-------|--|--|--|--|

| Symbol            | Description                                                                                                                                       | Min            | Max | Units |  |  |  |  |

| Clock Frequen     | Clock Frequency                                                                                                                                   |                |     |       |  |  |  |  |

| F <sub>MULT</sub> | Internal operating frequency for a two-stage 18x18 multiplier using the AREG and BREG input registers and the PREG output register <sup>(1)</sup> | 0              | 240 | MHz   |  |  |  |  |

Notes:

1. Combinatorial delay is less and pipelined performance is higher when multiplying input data with less than 18 bits.

2. The PREG register is typically used in both single-stage and two-stage pipelined multiplier implementations.

3. Input registers AREG or BREG are typically used when inferring a two-stage multiplier.

### **Block RAM Timing**

### Table 25: Block RAM Timing

|                   |                                                                                                                         | -4 Spee |      |       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------|---------|------|-------|

| Symbol            | Description                                                                                                             | Min     | Max  | Units |

| Clock-to-Ou       | tput Times                                                                                                              |         |      | -     |

| Т <sub>ВСКО</sub> | When reading from block RAM, the delay from the active transition at the CLK input to data appearing at the DOUT output | -       | 2.82 | ns    |

| Setup Times       | ,                                                                                                                       |         | J    | _ IL  |

| T <sub>BACK</sub> | Setup time for the ADDR inputs before the active transition at the CLK input of the block RAM                           | 0.38    | -    | ns    |

| T <sub>BDCK</sub> | Setup time for data at the DIN inputs before the active transition at the CLK input of the block RAM                    | 0.23    | -    | ns    |

| T <sub>BECK</sub> | Setup time for the EN input before the active transition at the CLK input of the block RAM                              | 0.77    | -    | ns    |

| T <sub>BWCK</sub> | Setup time for the WE input before the active transition at the CLK input of the block RAM                              | 1.26    | -    | ns    |

| Hold Times        |                                                                                                                         |         |      |       |

| T <sub>BCKA</sub> | Hold time on the ADDR inputs after the active transition at the CLK input                                               | 0.14    | -    | ns    |

| T <sub>BCKD</sub> | Hold time on the DIN inputs after the active transition at the CLK input                                                | 0.13    | -    | ns    |

| T <sub>BCKE</sub> | Hold time on the EN input after the active transition at the CLK input                                                  | 0       | -    | ns    |

| Т <sub>ВСКW</sub> | Hold time on the WE input after the active transition at the CLK input                                                  | 0       | -    | ns    |

### Table 25: Block RAM Timing (Continued)

|                     |                                                                                                                                                                        | -4 Speed Grade |     |       |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|-------|

| Symbol              | Description                                                                                                                                                            | Min            | Max | Units |

| Clock Timing        | •                                                                                                                                                                      |                |     |       |

| T <sub>BPWH</sub>   | High pulse width of the CLK signal                                                                                                                                     | 1.59           | -   | ns    |

| T <sub>BPWL</sub>   | Low pulse width of the CLK signal                                                                                                                                      | 1.59           | -   | ns    |

| <b>Clock Freque</b> | ncy                                                                                                                                                                    |                |     |       |

| F <sub>BRAM</sub>   | Block RAM clock frequency. RAM read output value written back<br>into RAM, for shift registers and circular buffers. Write-only or<br>read-only performance is faster. | 0              | 230 | MHz   |

#### Notes:

1. The numbers in this table are based on the operating conditions set forth in Table 6.

### **Digital Clock Manager Timing**

For specification purposes, the DCM consists of three key components: the Delay-Locked Loop (DLL), the Digital Frequency Synthesizer (DFS), and the Phase Shifter (PS).

Aspects of DLL operation play a role in all DCM applications. All such applications inevitably use the CLKIN and the CLKFB inputs connected to either the CLK0 or the CLK2X feedback, respectively. Thus, specifications in the DLL tables (Table 26 and Table 27) apply to any application that only employs the DLL component. When the DFS and/or the PS components are used together with the DLL, then the specifications listed in the DFS and PS tables (Table 28 through Table 31) supersede any corresponding ones in the DLL tables. DLL specifications that do not change with the addition of DFS or PS functions are presented in Table 26 and Table 27.

Period jitter and cycle-cycle jitter are two of many different ways of specifying clock jitter. Both specifications describe statistical variation from a mean value.

Period jitter is the worst-case deviation from the ideal clock period over a collection of millions of samples. In a histogram of period jitter, the mean value is the clock period.

Cycle-cycle jitter is the worst-case difference in clock period between adjacent clock cycles in the collection of clock periods sampled. In a histogram of cycle-cycle jitter, the mean value is zero.

### Spread Spectrum

DCMs accept typical spread spectrum clocks as long as they meet the input requirements. The DLL will track the frequency changes created by the spread spectrum clock to drive the global clocks to the FPGA logic. See <u>XAPP469</u>, *Spread-Spectrum Clocking Reception for Displays* for details.

### Table 29: Switching Characteristics for the DFS

|                                      |                                                                                                                                                               |                                                                                                            |        | -4 Spee                              | ed Grade                             |       |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------|--------------------------------------|--------------------------------------|-------|

| Symbol                               | Description                                                                                                                                                   |                                                                                                            | Device | Device Min                           |                                      | Units |

| Output Frequency Ranges              |                                                                                                                                                               |                                                                                                            |        |                                      |                                      | I     |

| CLKOUT_FREQ_FX                       | Frequency for the CLKFX and CLKFX180 or                                                                                                                       | utputs                                                                                                     | All    | 5                                    | 311                                  | MHz   |

| Output Clock Jitter <sup>(2,3)</sup> |                                                                                                                                                               |                                                                                                            |        |                                      | 1                                    | 1     |

| CLKOUT_PER_JITT_FX                   | Period jitter at the CLKFX and CLKFX180                                                                                                                       |                                                                                                            | All    | Тур                                  | Max                                  |       |