Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 1584                                                                       |

| Total RAM Bits                 | 18432                                                                      |

| Number of I/O                  | 157                                                                        |

| Number of Gates                | 60000                                                                      |

| Voltage - Supply               | 1.14V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 201-VFBGA, CSBGA                                                           |

| Supplier Device Package        | 201-CSP (8x8)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/aglp060v2-cs201i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# I/Os Per Package <sup>1</sup>

| IGLOO PLUS Devices | AGLP030           | AGLP060 | AGLP125 |  |  |  |  |  |

|--------------------|-------------------|---------|---------|--|--|--|--|--|

| Package            | Single-Ended I/Os |         |         |  |  |  |  |  |

| CS201              | 120               | 157     | -       |  |  |  |  |  |

| CS281              | -                 | -       | 212     |  |  |  |  |  |

| CS289              | 120               | 157     | 212     |  |  |  |  |  |

| VQ128              | 101               | -       | -       |  |  |  |  |  |

| VQ176              | _                 | 137     | -       |  |  |  |  |  |

Note: When the Flash\*Freeze pin is used to directly enable Flash\*Freeze mode and not used as a regular I/O, the number of single-ended user I/Os available is reduced by one.

Table 2 • IGLOO PLUS FPGAs Package Size Dimensions

| Package                | CS201 | CS281   | CS289   | VQ128   | VQ176   |

|------------------------|-------|---------|---------|---------|---------|

| Length × Width (mm/mm) | 8 × 8 | 10 × 10 | 14 × 14 | 14 × 14 | 20 × 20 |

| Nominal Area (mm2)     | 64    | 100     | 196     | 196     | 400     |

| Pitch (mm)             | 0.5   | 0.5     | 0.8     | 0.4     | 0.4     |

| Height (mm)            | 0.89  | 1.05    | 1.20    | 1.0     | 1.0     |

# **IGLOO PLUS Device Status**

| IGLOO PLUS Device | Status     |

|-------------------|------------|

| AGLP030           | Production |

| AGLP060           | Production |

| AGLP125           | Production |

II Revision 17

#### VersaTiles

The IGLOO PLUS core consists of VersaTiles, which have been enhanced beyond the ProASIC PLUS® core tiles. The IGLOO PLUS VersaTile supports the following:

- · All 3-input logic functions—LUT-3 equivalent

- · Latch with clear or set

- · D-flip-flop with clear or set

- · Enable D-flip-flop with clear or set

Refer to Figure 1-3 for VersaTile configurations.

# LUT-3 Equivalent D-Flip-Flop with Clear or Set Data CLK CLR D-FF CLR CLR CLR CLR CLR CLR CLR

Figure 1-3 • VersaTile Configurations

#### User Nonvolatile FlashROM

IGLOO PLUS devices have 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications:

- · Internet protocol addressing (wireless or fixed)

- · System calibration settings

- Device serialization and/or inventory control

- Subscription-based business models (for example, set-top boxes)

- Secure key storage for secure communications algorithms

- Asset management/tracking

- · Date stamping

- · Version management

The FlashROM is written using the standard IGLOO PLUS IEEE 1532 JTAG programming interface. The core can be individually programmed (erased and written), and on-chip AES decryption can be used selectively to securely load data over public networks (except in AGLP030 devices), as in security keys stored in the FlashROM for a user design.

The FlashROM can be programmed via the JTAG programming interface, and its contents can be read back either through the JTAG programming interface or via direct FPGA core addressing. Note that the FlashROM can only be programmed from the JTAG interface and cannot be programmed from the internal logic array.

The FlashROM is programmed as 8 banks of 128 bits; however, reading is performed on a byte-by-byte basis using a synchronous interface. A 7-bit address from the FPGA core defines which of the 8 banks and which of the 16 bytes within that bank are being read. The three most significant bits (MSBs) of the FlashROM address determine the bank, and the four least significant bits (LSBs) of the FlashROM address define the byte.

The IGLOO PLUS development software solutions, Libero<sup>®</sup> System-on-Chip (SoC) and Designer, have extensive support for the FlashROM. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. Another feature allows the inclusion of static data for system version control. Data for the FlashROM can be generated quickly and easily using Libero SoC and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FlashROM contents.

Revision 17 1-5

IGLOO PLUS Device Family Overview

#### SRAM and FIFO

IGLOO PLUS devices (except AGLP030 devices) have embedded SRAM blocks along their north side. Each variable-aspect-ratio SRAM block is 4,608 bits in size. Available memory configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1 bits. The individual blocks have independent read and write ports that can be configured with different bit widths on each port. For example, data can be sent through a 4-bit port and read as a single bitstream. The embedded SRAM blocks can be initialized via the device JTAG port (ROM emulation mode) using the UJTAG macro (except in AGLP030 devices).

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using additional core VersaTiles. The FIFO width and depth are programmable. The FIFO also features programmable Almost Empty (AEMPTY) and Almost Full (AFULL) flags in addition to the normal Empty and Full flags. The embedded FIFO control unit contains the counters necessary for generation of the read and write address pointers. The embedded SRAM/FIFO blocks can be cascaded to create larger configurations.

#### PLL and CCC

IGLOO PLUS devices provide designers with very flexible clock conditioning circuit (CCC) capabilities. Each member of the IGLOO PLUS family contains six CCCs. One CCC (center west side) has a PLL. The AGLP030 device does not have a PLL or CCCs; it contains only inputs to six globals.

The six CCC blocks are located at the four corners and the centers of the east and west sides. One CCC (center west side) has a PLL.

The four corner CCCs and the east CCC allow simple clock delay operations as well as clock spine access.

The inputs of the six CCC blocks are accessible from the FPGA core or from one of several inputs located near the CCC that have dedicated connections to the CCC block.

The CCC block has these key features:

- Wide input frequency range (f<sub>IN CCC</sub>) = 1.5 MHz up to 250 MHz

- Output frequency range (f<sub>OUT CCC</sub>) = 0.75 MHz up to 250 MHz

- · 2 programmable delay types for clock skew minimization

- · Clock frequency synthesis (for PLL only)

#### Additional CCC specifications:

- Internal phase shift = 0°, 90°, 180°, and 270°. Output phase shift depends on the output divider configuration (for PLL only).

- Output duty cycle = 50% ± 1.5% or better (for PLL only)

- Low output jitter: worst case < 2.5% × clock period peak-to-peak period jitter when single global network used (for PLL only)

- Maximum acquisition time is 300 µs (for PLL only)

- Exceptional tolerance to input period jitter—allowable input jitter is up to 1.5 ns (for PLL only)

- Four precise phases; maximum misalignment between adjacent phases (for PLL only) is 40 ps × 250 MHz / f<sub>OUT CCC</sub>

## Global Clocking

IGLOO PLUS devices have extensive support for multiple clocking domains. In addition to the CCC and PLL support described above, there is a comprehensive global clock distribution network.

Each VersaTile input and output port has access to nine VersaNets: six chip (main) and three quadrant global networks. The VersaNets can be driven by the CCC or directly accessed from the core via multiplexers (MUXes). The VersaNets can be used to distribute low-skew clock signals or for rapid distribution of high-fanout nets.

#### I/Os with Advanced I/O Standards

The IGLOO PLUS family of FPGAs features a flexible I/O structure, supporting a range of voltages (1.2 V, 1.5 V, 1.8 V, 2.5 V, 3.0 V wide range, and 3.3 V). IGLOO PLUS FPGAs support many different I/O standards.

The I/Os are organized into four banks. All devices in IGLOO PLUS have four banks. The configuration of these banks determines the I/O standards supported.

1-6 Revision 17

# 2 – IGLOO PLUS DC and Switching Characteristics

# **General Specifications**

# **Operating Conditions**

Stresses beyond those listed in Table 2-1 may cause permanent damage to the device.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Absolute Maximum Ratings are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions specified in Table 2-2 on page 2-2 is not implied.

Table 2-1 • Absolute Maximum Ratings

| Symbol                        | Parameter                    | Limits          | Units |

|-------------------------------|------------------------------|-----------------|-------|

| VCC                           | DC core supply voltage       | -0.3 to 1.65    | V     |

| VJTAG                         | JTAG DC voltage              | -0.3 to 3.75    | V     |

| VPUMP                         | Programming voltage          | -0.3 to 3.75    | V     |

| VCCPLL                        | Analog power supply (PLL)    | -0.3 to 1.65    | V     |

| VCCI                          | DC I/O buffer supply voltage | -0.3 to 3.75    | V     |

| VI <sup>1</sup>               | I/O input voltage            | −0.3 V to 3.6 V | V     |

| T <sub>STG</sub> <sup>2</sup> | Storage temperature          | -65 to +150     | °C    |

| T <sub>J</sub> <sup>2</sup>   | Junction temperature         | +125            | °C    |

#### Notes:

Revision 17 2-1

<sup>1.</sup> The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 2-4 on page 2-3.

<sup>2.</sup> For flash programming and retention maximum limits, refer to Table 2-3 on page 2-3, and for recommended operating limits, refer to Table 2-2 on page 2-2.

IGLOO PLUS DC and Switching Characteristics

Ramping up (V2 devices):  $0.65 \text{ V} < \text{trip\_point\_up} < 1.05 \text{ V}$ Ramping down (V2 devices):  $0.55 \text{ V} < \text{trip\_point\_down} < 0.95 \text{ V}$

VCC and VCCI ramp-up trip points are about 100 mV higher than ramp-down trip points. This specifically built-in hysteresis prevents undesirable power-up oscillations and current surges. Note the following:

- During programming, I/Os become tristated and weakly pulled up to VCCI.

- JTAG supply, PLL power supplies, and charge pump VPUMP supply have no influence on I/O behavior.

#### PLL Behavior at Brownout Condition

Microsemi recommends using monotonic power supplies or voltage regulators to ensure proper powerup behavior. Power ramp-up should be monotonic at least until VCC and VCCPLX exceed brownout activation levels (see Figure 2-1 and Figure 2-2 on page 2-5 for more details).

When PLL power supply voltage and/or VCC levels drop below the VCC brownout levels (0.75 V  $\pm$  0.25 V for V5 devices, and 0.75 V  $\pm$  0.2 V for V2 devices), the PLL output lock signal goes Low and/or the output clock is lost. Refer to the "Brownout Voltage" section in the "Power-Up/-Down Behavior of Low Power Flash Devices" chapter of the *IGLOO PLUS Device Family User's Guide* for information on clock and lock recovery.

# Internal Power-Up Activation Sequence

- 1. Core

- 2. Input buffers

- 3. Output buffers, after 200 ns delay from input buffer activation

To make sure the transition from input buffers to output buffers is clean, ensure that there is no path longer than 100 ns from input buffer to output buffer in your design.

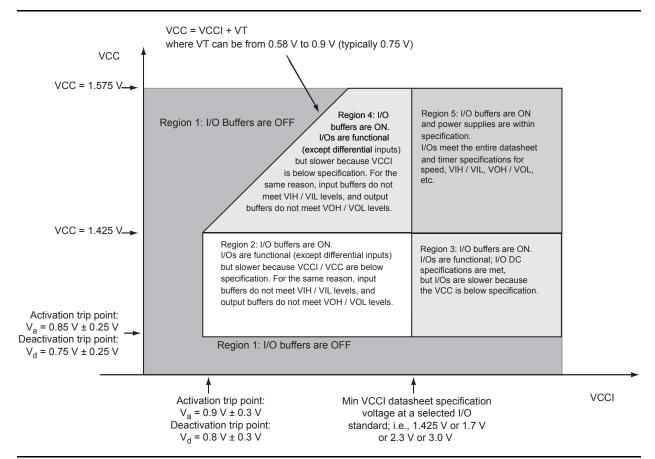

Figure 2-1 • V5 Devices – I/O State as a Function of VCCI and VCC Voltage Levels

2-4 Revision 17

IGLOO PLUS DC and Switching Characteristics

Table 2-12 • Quiescent Supply Current (IDD), No IGLOO PLUS Flash\*Freeze Mode <sup>1</sup>

|                                                   | Core Voltage  | AGLP030 | AGLP060 | AGLP125 | Units |

|---------------------------------------------------|---------------|---------|---------|---------|-------|

| ICCA Current <sup>2</sup>                         | 1             | 1       |         | 1       | ı     |

| Typical (25°C)                                    | 1.2 V         | 6       | 10      | 13      | μΑ    |

|                                                   | 1.5 V         | 16      | 20      | 28      | μΑ    |

| ICCI or IJTAG Current                             | •             | •       | •       | •       | •     |

| VCCI / VJTAG = 1.2 V (per bank)<br>Typical (25°C) | 1.2 V         | 1.7     | 1.7     | 1.7     | μA    |

| VCCI / VJTAG = 1.5 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 1.8     | 1.8     | 1.8     | μA    |

| VCCI / VJTAG = 1.8 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 1.9     | 1.9     | 1.9     | μΑ    |

| VCCI / VJTAG = 2.5 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 2.2     | 2.2     | 2.2     | μA    |

| VCCI / VJTAG = 3.3 V (per bank)<br>Typical (25°C) | 1.2 V / 1.5 V | 2.5     | 2.5     | 2.5     | μA    |

#### Notes:

2-8 Revision 17

IDD = N<sub>BANKS</sub> \* ICCI + ICCA. JTAG counts as one bank when powered.

Includes VCC, VCCPLL, and VPUMP currents.

# **Power Consumption of Various Internal Resources**

Table 2-15 • Different Components Contributing to Dynamic Power Consumption in IGLOO PLUS Devices For IGLOO PLUS V2 or V5 Devices, 1.5 V Core Supply Voltage

|           |                                                                | Device Sp                   | mic Power     |                    |

|-----------|----------------------------------------------------------------|-----------------------------|---------------|--------------------|

| Parameter | Definition                                                     | AGLP125                     | AGLP060       | AGLP030            |

| PAC1      | Clock contribution of a Global Rib                             | 4.489                       | 2.696         | 0.000 <sup>1</sup> |

| PAC2      | Clock contribution of a Global Spine                           | 1.991                       | 1.962         | 3.499              |

| PAC3      | Clock contribution of a VersaTile row                          | 1.510 1.523 1.53            |               |                    |

| PAC4      | Clock contribution of a VersaTile used as a sequential module  | 0.153                       | 0.151         | 0.151              |

| PAC5      | First contribution of a VersaTile used as a sequential module  | 0.029                       | 0.029         | 0.029              |

| PAC6      | Second contribution of a VersaTile used as a sequential module | 0.323                       | 0.323         | 0.323              |

| PAC7      | Contribution of a VersaTile used as a combinatorial module     | 0.280                       | 0.300         | 0.278              |

| PAC8      | Average contribution of a routing net                          | 1.097                       | 1.081         | 1.130              |

| PAC9      | Contribution of an I/O input pin (standard-dependent)          | See Ta                      | ble 2-13 on p | page 2-9.          |

| PAC10     | Contribution of an I/O output pin (standard-dependent)         | See Table 2-14 on page 2-9. |               |                    |

| PAC11     | Average contribution of a RAM block during a read operation    | 25.00                       |               |                    |

| PAC12     | Average contribution of a RAM block during a write operation   | 30.00                       |               |                    |

| PAC13     | Dynamic contribution for PLL                                   |                             | 2.70          |                    |

Note: 1. There is no Center Global Rib present in AGLP030, and thus it starts directly at the spine resulting in  $0\mu W/MHz$ .

Table 2-16 • Different Components Contributing to the Static Power Consumption in IGLOO PLUS Devices For IGLOO PLUS V2 or V5 Devices, 1.5 V Core Supply Voltage

|           |                                          | Device-Specific Static Power (mW) |                            |         |  |  |  |

|-----------|------------------------------------------|-----------------------------------|----------------------------|---------|--|--|--|

| Parameter | Definition                               | AGLP125                           | AGLP060                    | AGLP030 |  |  |  |

| PDC1      | Array static power in Active mode        | See Table 2-12 on page 2-8        |                            |         |  |  |  |

| PDC2      | Array static power in Static (Idle) mode | See Ta                            | See Table 2-11 on page 2-7 |         |  |  |  |

| PDC3      | Array static power in Flash*Freeze mode  | See Table 2-9 on page 2-7         |                            |         |  |  |  |

| PDC4      | Static PLL contribution                  | 1.84 <sup>1</sup>                 |                            |         |  |  |  |

| PDC5      | Bank quiescent power (VCCI-dependent)    | See Table 2-12 on page 2-8        |                            |         |  |  |  |

#### Notes:

- 1. This is the minimum contribution of the PLL when operating at lowest frequency.

- 2. For a different output load, drive strength, or slew rate, Microsemi recommends using the Microsemi power spreadsheet calculator or the SmartPower tool in Libero SoC software.

2-10 Revision 17

# **Power Calculation Methodology**

This section describes a simplified method to estimate power consumption of an application. For more accurate and detailed power estimations, use the SmartPower tool in Libero SoC software.

The power calculation methodology described below uses the following variables:

- · The number of PLLs as well as the number and the frequency of each output clock generated

- · The number of combinatorial and sequential cells used in the design

- · The internal clock frequencies

- · The number and the standard of I/O pins used in the design

- · The number of RAM blocks used in the design

- Toggle rates of I/O pins as well as VersaTiles—guidelines are provided in Table 2-19 on page 2-14.

- Enable rates of output buffers—guidelines are provided for typical applications in Table 2-20 on page 2-14.

- Read rate and write rate to the memory—guidelines are provided for typical applications in Table 2-20 on page 2-14. The calculation should be repeated for each clock domain defined in the design.

## Methodology

# Total Power Consumption—P<sub>TOTAL</sub>

$P_{TOTAL} = P_{STAT} + P_{DYN}$

P<sub>STAT</sub> is the total static power consumption.

P<sub>DYN</sub> is the total dynamic power consumption.

#### Total Static Power Consumption—PSTAT

P<sub>STAT</sub> = (PDC1 or PDC2 or PDC3) + N<sub>BANKS</sub> \* PDC5

N<sub>BANKS</sub> is the number of I/O banks powered in the design.

# Total Dynamic Power Consumption—PDYN

PDYN = PCLOCK + PS-CELL + PC-CELL + PNET + PINPUTS + POUTPUTS + PMEMORY + PPLL

# Global Clock Contribution—P<sub>CLOCK</sub>

```

P<sub>CLOCK</sub> = (PAC1 + N<sub>SPINE</sub>*PAC2 + N<sub>ROW</sub>*PAC3 + N<sub>S-CELL</sub>* PAC4) * F<sub>CLK</sub>

```

N<sub>SPINE</sub> is the number of global spines used in the user design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *IGLOO PLUS FPGA Fabric User's Guide*.

N<sub>ROW</sub> is the number of VersaTile rows used in the design—guidelines are provided in the "Spine Architecture" section of the Global Resources chapter in the *IGLOO PLUS FPGA Fabric User's Guide*.

F<sub>CLK</sub> is the global clock signal frequency.

N<sub>S-CFLL</sub> is the number of VersaTiles used as sequential modules in the design.

PAC1, PAC2, PAC3, and PAC4 are device-dependent.

#### Sequential Cells Contribution—P<sub>S-CFL</sub>

```

P_{S-CELL} = N_{S-CELL} * (PAC5 + \alpha_1 / 2 * PAC6) * F_{CLK}

```

$N_{S\text{-}CELL}$  is the number of VersaTiles used as sequential modules in the design. When a multi-tile sequential cell is used, it should be accounted for as 1.

$\alpha_{\text{1}}$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-19 on page 2-14.

F<sub>CLK</sub> is the global clock signal frequency.

2-12 Revision 17

IGLOO PLUS DC and Switching Characteristics

# 1.5 V LVCMOS (JESD8-11)

Low-Voltage CMOS for 1.5 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 1.5 V applications. It uses a 1.5 V input buffer and a push-pull output buffer.

Table 2-58 • Minimum and Maximum DC Input and Output Levels

| 1.5 V<br>LVCMOS   | VIL       |             | VIL VIH    |           | VOL         | VOH         | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup>        | IIH <sup>2</sup>        |

|-------------------|-----------|-------------|------------|-----------|-------------|-------------|-----|----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V   | Min.<br>V  | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μ <b>Α</b> <sup>4</sup> | μ <b>Α</b> <sup>4</sup> |

| 2 mA              | -0.3      | 0.35 * VCCI | 0.7 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 13                      | 16                      | 10                      | 10                      |

| 4 mA              | -0.3      | 0.35 * VCCI | 0.7 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 4   | 4  | 25                      | 33                      | 10                      | 10                      |

#### Notes:

- 1. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 4. Currents are measured at 85°C junction temperature.

- 5. Software default selection highlighted in gray.

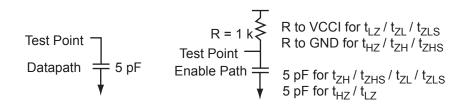

Figure 2-10 • AC Loading

Table 2-59 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.5            | 0.75                 | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

2-36 Revision 17

# 1.2 V LVCMOS Wide Range

Table 2-68 • Minimum and Maximum DC Input and Output Levels

| 1.2 V<br>LVCMOS<br>Range <sup>1</sup> | Wide                                                                          |           | VIL         | VIH         |           | VOL         | VOH         | IOL | ЮН | IOSL                    | юзн                    |                         | IIH <sup>4</sup>        |

|---------------------------------------|-------------------------------------------------------------------------------|-----------|-------------|-------------|-----------|-------------|-------------|-----|----|-------------------------|------------------------|-------------------------|-------------------------|

| Drive<br>Strength                     | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>2</sup> | Min.<br>V | Max.<br>V   | Min.<br>V   | Max.<br>V | Max.<br>V   | Min.<br>V   | mA  | mA | Max.<br>mA <sup>5</sup> | Max<br>mA <sup>5</sup> | μ <b>Α</b> <sup>6</sup> | μ <b>Α</b> <sup>6</sup> |

| 100 μΑ                                | 2 mA                                                                          | -0.3      | 0.35 * VCCI | 0.65 * VCCI | 3.6       | 0.25 * VCCI | 0.75 * VCCI | 2   | 2  | 20                      | 26                     | 10                      | 10                      |

#### Notes:

- 1. Applicable to V2 devices only.

- 2. The minimum drive strength for any LVCMOS 1.2 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 3. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 4. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 5. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 6. Currents are measured at 85°C junction temperature.

- 7. Software default selection highlighted in gray.

Table 2-69 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 1.2            | 0.6                  | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

Revision 17 2-39

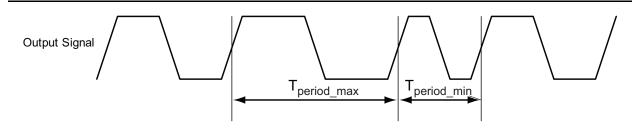

Note: Peak-to-peak jitter measurements are defined by  $T_{peak-to-peak} = T_{period\_max} - T_{period\_min}$

Figure 2-22 • Peak-to-Peak Jitter Definition

Revision 17 2-63

| C          | S201                |

|------------|---------------------|

| Pin Number | AGLP030<br>Function |

| H14        | IO45RSB1            |

| H15        | IO43RSB1            |

| J1         | GEA0/IO107RSB3      |

| J2         | IO105RSB3           |

| J3         | IO104RSB3           |

| J4         | IO102RSB3           |

| J6         | VCCIB3              |

| J7         | GND                 |

| J8         | VCC                 |

| J9         | GND                 |

| J10        | VCCIB1              |

| J12        | NC                  |

| J13        | NC                  |

| J14        | IO52RSB1            |

| J15        | IO50RSB1            |

| K1         | IO103RSB3           |

| K2         | IO101RSB3           |

| K3         | IO99RSB3            |

| K4         | IO100RSB3           |

| K6         | GND                 |

| K7         | VCCIB2              |

| K8         | VCCIB2              |

| K9         | VCCIB2              |

| K10        | VCCIB1              |

| K12        | NC                  |

| K13        | IO57RSB1            |

| K14        | IO49RSB1            |

| K15        | IO53RSB1            |

| L1         | IO96RSB3            |

| L2         | IO98RSB3            |

| L3         | IO95RSB3            |

| L4         | IO94RSB3            |

| L12        | NC                  |

| L13        | NC                  |

| L14        | IO51RSB1            |

| CS201      |          |

|------------|----------|

| AGLP030    |          |

| Pin Number | Function |

| L15        | IO58RSB1 |

| M1         | IO93RSB3 |

| M2         | IO92RSB3 |

| М3         | IO97RSB3 |

| M4         | GND      |

| M5         | NC       |

| M6         | IO79RSB2 |

| M7         | IO77RSB2 |

| M8         | IO72RSB2 |

| M9         | IO70RSB2 |

| M10        | IO61RSB2 |

| M11        | IO59RSB2 |

| M12        | GND      |

| M13        | NC       |

| M14        | IO55RSB1 |

| M15        | IO56RSB1 |

| N1         | NC       |

| N2         | NC       |

| N3         | GND      |

| N4         | NC       |

| N5         | IO88RSB2 |

| N6         | IO81RSB2 |

| N7         | IO75RSB2 |

| N8         | IO68RSB2 |

| N9         | IO66RSB2 |

| N10        | IO65RSB2 |

| N11        | IO71RSB2 |

| N12        | IO63RSB2 |

| N13        | GND      |

| N14        | TDO      |

| N15        | VJTAG    |

| P1         | NC       |

| P2         | NC       |

| P3         | NC       |

| P4         | NC       |

| CS201      |                     |

|------------|---------------------|

|            |                     |

| Pin Number | AGLP030<br>Function |

| P5         | IO87RSB2            |

| P6         | IO86RSB2            |

| P7         | IO84RSB2            |

| P8         | IO80RSB2            |

| P9         | IO74RSB2            |

| P10        | IO73RSB2            |

| P11        | IO76RSB2            |

| P12        | IO67RSB2            |

| P13        | IO64RSB2            |

| P14        | VPUMP               |

| P15        | TRST                |

| R1         | NC                  |

| R2         | NC                  |

| R3         | IO91RSB2            |

| R4         | FF/IO90RSB2         |

| R5         | IO89RSB2            |

| R6         | IO83RSB2            |

| R7         | IO82RSB2            |

| R8         | IO85RSB2            |

| R9         | IO78RSB2            |

| R10        | IO69RSB2            |

| R11        | IO62RSB2            |

| R12        | IO60RSB2            |

| R13        | TMS                 |

| R14        | TDI                 |

| R15        | TCK                 |

|            |                     |

|            | CS281            |

|------------|------------------|

| Pin Number | AGLP125 Function |

| A1         | GND              |

| A2         | GAB0/IO02RSB0    |

| A3         | GAC1/IO05RSB0    |

| A4         | IO09RSB0         |

| A5         | IO13RSB0         |

| A6         | IO15RSB0         |

| A7         | IO18RSB0         |

| A8         | IO23RSB0         |

| A9         | IO25RSB0         |

| A10        | VCCIB0           |

| A11        | IO33RSB0         |

| A12        | IO41RSB0         |

| A13        | IO43RSB0         |

| A14        | IO46RSB0         |

| A15        | IO55RSB0         |

| A16        | IO56RSB0         |

| A17        | GBC1/IO58RSB0    |

| A18        | GBA0/IO61RSB0    |

| A19        | GND              |

| B1         | GAA2/IO211RSB3   |

| B2         | VCCIB0           |

| В3         | GAB1/IO03RSB0    |

| B4         | GAC0/IO04RSB0    |

| B5         | IO11RSB0         |

| В6         | GND              |

| В7         | IO21RSB0         |

| B8         | IO22RSB0         |

| В9         | IO28RSB0         |

| B10        | IO32RSB0         |

| B11        | IO36RSB0         |

| B12        | IO39RSB0         |

| B13        | IO42RSB0         |

| B14        | GND              |

| B15        | IO52RSB0         |

| B16        | GBC0/IO57RSB0    |

| B17        | GBA1/IO62RSB0    |

| CS281            |  |  |

|------------------|--|--|

| AGLP125 Function |  |  |

| VCCIB1           |  |  |

| IO64RSB1         |  |  |

| GAB2/IO209RSB3   |  |  |

| IO210RSB3        |  |  |

| IO12RSB0         |  |  |

| IO47RSB0         |  |  |

| IO54RSB0         |  |  |

| GBB2/IO65RSB1    |  |  |

| IO206RSB3        |  |  |

| IO208RSB3        |  |  |

| GAA0/IO00RSB0    |  |  |

| GAA1/IO01RSB0    |  |  |

| IO10RSB0         |  |  |

| IO17RSB0         |  |  |

| IO24RSB0         |  |  |

| IO27RSB0         |  |  |

| GND              |  |  |

| IO31RSB0         |  |  |

| IO40RSB0         |  |  |

| IO49RSB0         |  |  |

| IO45RSB0         |  |  |

| GBB0/IO59RSB0    |  |  |

| GBA2/IO63RSB1    |  |  |

| GBC2/IO67RSB1    |  |  |

| IO66RSB1         |  |  |

| IO203RSB3        |  |  |

| IO205RSB3        |  |  |

| IO07RSB0         |  |  |

| IO06RSB0         |  |  |

| IO14RSB0         |  |  |

| IO20RSB0         |  |  |

| IO29RSB0         |  |  |

| IO34RSB0         |  |  |

| IO30RSB0         |  |  |

| IO37RSB0         |  |  |

| IO38RSB0         |  |  |

|                  |  |  |

| CS281      |                  |

|------------|------------------|

| Pin Number | AGLP125 Function |

| E13        | IO48RSB0         |

| E14        | GBB1/IO60RSB0    |

| E15        | IO53RSB0         |

| E16        | IO69RSB1         |

| E18        | IO68RSB1         |

| E19        | IO71RSB1         |

| F1         | IO198RSB3        |

| F2         | GND              |

| F3         | IO201RSB3        |

| F4         | IO204RSB3        |

| F5         | IO16RSB0         |

| F15        | IO50RSB0         |

| F16        | IO74RSB1         |

| F17        | IO72RSB1         |

| F18        | GND              |

| F19        | IO73RSB1         |

| G1         | IO195RSB3        |

| G2         | IO200RSB3        |

| G4         | IO202RSB3        |

| G5         | IO08RSB0         |

| G7         | GAC2/IO207RSB3   |

| G8         | VCCIB0           |

| G9         | IO26RSB0         |

| G10        | IO35RSB0         |

| G11        | IO44RSB0         |

| G12        | VCCIB0           |

| G13        | IO51RSB0         |

| G15        | IO70RSB1         |

| G16        | IO75RSB1         |

| G18        | GCC0/IO80RSB1    |

| G19        | GCB1/IO81RSB1    |

| H1         | GFB0/IO191RSB3   |

| H2         | IO196RSB3        |

| H4         | GFC1/IO194RSB3   |

| H5         | GFB1/IO192RSB3   |

| H7         | VCCIB3           |

# **CS289**

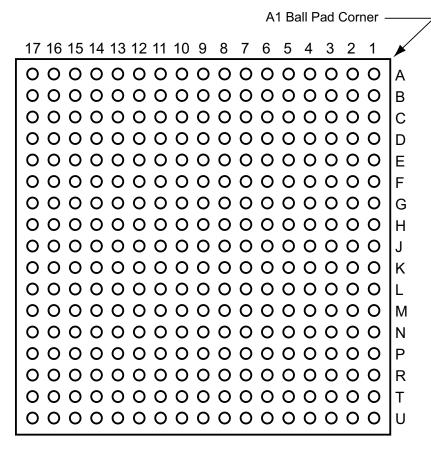

Note: This is the bottom view of the package.

#### Note

For Package Manufacturing and Environmental information, visit the Resource Center at  $\label{eq:http://www.microsemi.com/soc/products/solutions/package/docs.aspx \ .$

4-16 Revision 17

# Package Pin Assignments

| (          | CS289          |

|------------|----------------|

|            | AGLP030        |

| Pin Number | Function       |

| G10        | GND            |

| G11        | GND            |

| G12        | IO40RSB1       |

| G13        | NC             |

| G14        | IO39RSB1       |

| G15        | IO44RSB1       |

| G16        | NC             |

| G17        | GND            |

| H1         | NC             |

| H2         | GEC0/IO108RSB3 |

| H3         | NC             |

| H4         | IO112RSB3      |

| H5         | NC             |

| H6         | IO109RSB3      |

| H7         | GND            |

| H8         | GND            |

| H9         | GND            |

| H10        | GND            |

| H11        | GND            |

| H12        | NC             |

| H13        | NC             |

| H14        | IO45RSB1       |

| H15        | VCCIB1         |

| H16        | GDB0/IO48RSB1  |

| H17        | IO42RSB1       |

| J1         | NC             |

| J2         | GEA0/IO107RSB3 |

| J3         | VCCIB3         |

| J4         | IO105RSB3      |

| J5         | NC             |

| J6         | NC             |

| J7         | VCC            |

| J8         | GND            |

| J9         | GND            |

| J10        | GND            |

| J11        | VCC            |

| J12        | IO50RSB1       |

| (          | CS289               |  |

|------------|---------------------|--|

| Pin Number | AGLP030<br>Function |  |

| J13        | IO43RSB1            |  |

| J14        | IO51RSB1            |  |

| J15        | IO52RSB1            |  |

| J16        | GDC0/IO46RSB1       |  |

| J17        | GDA0/IO47RSB1       |  |

| K1         | GND                 |  |

| K2         | GEB0/IO106RSB3      |  |

| K3         | IO102RSB3           |  |

| K4         | IO104RSB3           |  |

| K5         | IO99RSB3            |  |

| K6         | NC                  |  |

| K7         | GND                 |  |

| K8         | GND                 |  |

| K9         | GND                 |  |

| K10        | GND                 |  |

| K11        | GND                 |  |

| K12        | NC                  |  |

| K13        | NC                  |  |

| K14        | NC                  |  |

| K15        | IO53RSB1            |  |

| K16        | GND                 |  |

| K17        | IO49RSB1            |  |

| L1         | IO103RSB3           |  |

| L2         | IO101RSB3           |  |

| L3         | NC                  |  |

| L4         | GND                 |  |

| L5         | NC                  |  |

| L6         | NC                  |  |

| L7         | GND                 |  |

| L8         | GND                 |  |

| L9         | VCC                 |  |

| L10        | GND                 |  |

| L11        | GND                 |  |

| L12        | IO58RSB1            |  |

| L13        | IO54RSB1            |  |

| L14        | VCCIB1              |  |

| L15        | NC                  |  |

| (           | CS289          |  |

|-------------|----------------|--|

| Dia Namakan | AGLP030        |  |

| Pin Number  | Function<br>NC |  |

| L16         |                |  |

| L17         | NC             |  |

| M1          | NC             |  |

| M2          | VCCIB3         |  |

| M3          | IO100RSB3      |  |

| M4          | IO98RSB3       |  |

| M5          | IO93RSB3       |  |

| M6          | IO97RSB3       |  |

| M7          | NC             |  |

| M8          | NC             |  |

| M9          | IO71RSB2       |  |

| M10         | NC             |  |

| M11         | IO63RSB2       |  |

| M12         | NC             |  |

| M13         | IO57RSB1       |  |

| M14         | NC             |  |

| M15         | NC             |  |

| M16         | NC             |  |

| M17         | VCCIB1         |  |

| N1          | NC             |  |

| N2          | NC             |  |

| N3          | IO95RSB3       |  |

| N4          | IO96RSB3       |  |

| N5          | GND            |  |

| N6          | NC             |  |

| N7          | IO85RSB2       |  |

| N8          | IO79RSB2       |  |

| N9          | IO77RSB2       |  |

| N10         | VCCIB2         |  |

| N11         | NC             |  |

| N12         | NC             |  |

| N13         | IO59RSB2       |  |

| N14         | NC             |  |

| N15         | GND            |  |

| N16         | IO56RSB1       |  |

| N17         | IO55RSB1       |  |

| P1          | IO94RSB3       |  |

4-18 Revision 17

| CS289      |                  |

|------------|------------------|

| Pin Number | AGLP125 Function |

| P8         | GND              |

| P9         | IO132RSB2        |

| P10        | IO125RSB2        |

| P11        | IO126RSB2        |

| P12        | IO112RSB2        |

| P13        | VCCIB2           |

| P14        | IO108RSB2        |

| P15        | GDA2/IO105RSB2   |

| P16        | GDC2/IO107RSB2   |

| P17        | VJTAG            |

| R1         | GND              |

| R2         | GEA2/IO164RSB2   |

| R3         | IO158RSB2        |

| R4         | IO155RSB2        |

| R5         | IO150RSB2        |

| R6         | VCCIB2           |

| R7         | IO145RSB2        |

| R8         | IO141RSB2        |

| R9         | IO134RSB2        |

| R10        | IO130RSB2        |

| R11        | GND              |

| R12        | IO118RSB2        |

| R13        | IO116RSB2        |

| R14        | IO114RSB2        |

| R15        | IO110RSB2        |

| R16        | TMS              |

| R17        | TRST             |

| T1         | GEA1/IO166RSB3   |

| T2         | GEC2/IO162RSB2   |

| Т3         | IO153RSB2        |

| T4         | GND              |

| T5         | IO147RSB2        |

| Т6         | IO143RSB2        |

| T7         | IO140RSB2        |

| Т8         | IO139RSB2        |

| Т9         | VCCIB2           |

| T10        | IO131RSB2        |

| T11        | IO127RSB2        |

|            | CS289                 |  |

|------------|-----------------------|--|

| Pin Number | AGLP125 Function      |  |

| T12        | IO124RSB2             |  |

| T13        | IO122RSB2             |  |

| T14        | GND                   |  |

| T15        | IO115RSB2             |  |

| T16        | TDI                   |  |

| T17        | TDO                   |  |

| U1         | FF/GEB2/IO163RS<br>B2 |  |

| U2         | GND                   |  |

| U3         | IO151RSB2             |  |

| U4         | IO149RSB2             |  |

| U5         | IO146RSB2             |  |

| U6         | IO142RSB2             |  |

| U7         | GND                   |  |

| U8         | IO138RSB2             |  |

| U9         | IO136RSB2             |  |

| U10        | IO133RSB2             |  |

| U11        | IO129RSB2             |  |

| U12        | GND                   |  |

| U13        | IO123RSB2             |  |

| U14        | IO120RSB2             |  |

| U15        | IO117RSB2             |  |

| U16        | TCK                   |  |

| U17        | VPUMP                 |  |

Revision 17 4-25

# Datasheet Information

| Revision                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Revision 13<br>(June 2012)  | Figure 2-30 • FIFO Read and Figure 2-31 • FIFO Write have been added (SAR 34843).                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

|                             | Updated the terminology used in Timing Characteristics in the following tables: Table 2-96 • FIFO and Table 2-97 • FIFO (SAR 38236).                                                                                                                                                                                                                                                                                                                                                                                | 2-76 |

|                             | The following sentence was removed from the "VMVx I/O Supply Voltage (quiet)" section in the "Pin Descriptions and Packaging" section: "Within the package, the VMV plane is decoupled from the simultaneous switching noise originating from the output buffer VCCI domain" and replaced with "Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks" (SAR 38320). The datasheet mentions that "VMV pins must be connected to the corresponding VCCI pins" for an ESD enhancement. | 3-1  |

| Revision 12<br>(March 2012) | The "In-System Programming (ISP) and Security" section and "Security" section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 34664).                                                                                                                                                                                                                                                |      |

|                             | The Y security option and Licensed DPA Logo were added to the "IGLOO PLUS Ordering Information" section. The trademarked Licensed DPA Logo identifies that a product is covered by a DPA counter-measures license from Cryptography Research (SAR 34724).                                                                                                                                                                                                                                                           | III  |

|                             | The "Specifying I/O States During Programming" section is new (SAR 34695).                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-7  |

|                             | The following sentence was removed from the "Advanced Architecture" section: "In addition, extensive on-chip programming circuitry allows for rapid, single-voltage (3.3 V) programming of IGLOO PLUS devices via an IEEE 1532 JTAG interface"                                                                                                                                                                                                                                                                      | 1-3  |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

5-2 Revision 17

# Datasheet Information

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                        | Page         |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Revision 11<br>(continued) | Table 2-2 • Recommended Operating Conditions <sup>1,2</sup> was revised. 1.2 V DC wide range supply voltage and 3.3 V wide range supply voltage (SAR 26270) were added for VCCI. VJTAG DC Voltage was revised (SAR 24052). The value range for VPUMP programming voltage for operation was changed from "0 to 3.45" to "0 to 3.6" (SAR 25220). | 2-2          |

|                            | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = 70°C, VCC = 1.425 V) and Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = 70°C, VCC = 1.14 V) were revised.                                                                                               | 2-6, 2-6     |

|                            | Table 2-8 • Power Supply State per Mode is new.                                                                                                                                                                                                                                                                                                | 2-7          |

|                            | The tables in the "Quiescent Supply Current" section were updated (SARs 24882 and 24112). Some of the table notes were changed or deleted.                                                                                                                                                                                                     | 2-7          |

|                            | VIH maximum values in tables were updated as needed to 3.6 V (SARs 20990, 79370).                                                                                                                                                                                                                                                              | N/A          |

|                            | The values in the following tables were updated. 3.3 V LVCMOS and 1.2 V LVCMOS wide range were added to the tables where applicable.                                                                                                                                                                                                           |              |

|                            | Table 2-13 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings                                                                                                                                                                                                                                                       | 2-9          |

|                            | Table 2-14 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings <sup>1</sup>                                                                                                                                                                                                                                         | 2-9          |

|                            | Table 2-21 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings                                                                                                                                                                                            | 2-19<br>2-20 |

|                            | Table 2-22 • Summary of Maximum and Minimum DC Input Levels                                                                                                                                                                                                                                                                                    | 2-20         |

|                            | Table 2-23 • Summary of AC Measuring Points                                                                                                                                                                                                                                                                                                    | 2 20         |

|                            | Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings, STD Speed Grade, Commercial-Case Conditions: $T_J$ = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V                                                                                                                                                     | 2-22         |

|                            | Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings, STD Speed Grade Commercial-Case Conditions: $T_J$ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V                                                                                                                                                       | 2-23         |

|                            | Table 2-28 • I/O Output Buffer Maximum Resistances <sup>1</sup>                                                                                                                                                                                                                                                                                | 2-24         |

|                            | A table note was added to Table 2-16 • Different Components Contributing to the                                                                                                                                                                                                                                                                | 2-10,        |

|                            | Static Power Consumption in IGLOO PLUS Devices and Table 2-18 • Different Components Contributing to the Static Power Consumption in IGLOO PLUS Devices stating the value for PDC4 is the minimum contribution of the PLL when operating at lowest frequency.                                                                                  | 2-11         |

|                            | Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances was revised, including addition of 3.3 V and 1.2 V LVCMOS wide range.                                                                                                                                                                                                                      | 2-25         |

|                            | The notes defining $R_{WEAK\ PULL-UP-MAX}$ and $R_{WEAK\ PULLDOWN-MAX}$ were revised (SAR 21348).                                                                                                                                                                                                                                              |              |

|                            | Table 2-30 • I/O Short Currents IOSH/IOSL was revised to include data for 3.3 V and 1.2 V LVCMOS wide range (SAR 79353 and SAR 79366).                                                                                                                                                                                                         | 2-25         |

|                            | Table 2-31 • Duration of Short Circuit Event before Failure was revised to change the maximum temperature from 110°C to 100°C, with an example of six months instead of three months (SAR 26259).                                                                                                                                              | 2-26         |

5-4 Revision 17

| Revision                | Changes                                                                                                                                                                                                                                                                                                                     | Page                    |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Revision 11 (continued) | The tables in the "Single-Ended I/O Characteristics" section were updated. Notes clarifying IIL and IIH were added.                                                                                                                                                                                                         | 2-27                    |

|                         | Tables for 3.3 V LVCMOS and 1.2 V LVCMOS wide range were added (SAR 79370, SAR 79353, and SAR 79366).                                                                                                                                                                                                                       |                         |

|                         | Notes in the wide range tables state that the minimum drive strength for any LVCMOS 3.3 V (or LVCMOS 1.2 V) software configuration when run in wide range is $\pm 100~\mu A$ . Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models (SAR 25700). |                         |

|                         | The following sentence was deleted from the "2.5 V LVCMOS" section: It uses a 5 V-tolerant input buffer and push-pull output buffer (SAR 24916).                                                                                                                                                                            | 2-32                    |

|                         | The tables in the "Input Register" section, "Output Register" section, and "Output Enable Register" section were updated. The tables in the "VersaTile Characteristics" section were updated.                                                                                                                               | 2-45<br>through<br>2-56 |

|                         | The following tables were updated in the "Global Tree Timing Characteristics" section:                                                                                                                                                                                                                                      | 2-58                    |

|                         | Table 2-85 • AGLP060 Global Resource (1.5 V)                                                                                                                                                                                                                                                                                |                         |

|                         | Table 2-86 • AGLP125 Global Resource (1.5 V)                                                                                                                                                                                                                                                                                |                         |

|                         | Table 2-88 • AGLP060 Global Resource (1.2 V)                                                                                                                                                                                                                                                                                |                         |

|                         | Table 2-90 • IGLOO PLUS CCC/PLL Specification and Table 2-91 • IGLOO PLUS CCC/PLL Specification were revised (SAR 79388). VCO output jitter and maximum peak-to-peak jitter data were changed. Three notes were added to the table in connection with these changes.                                                        | 2-61                    |

|                         | Figure 2-28 • Write Access after Write onto Same Address and Figure 2-29 • Write Access after Read onto Same Address were deleted.                                                                                                                                                                                          | N/A                     |

|                         | The tables in the "SRAM", "FIFO" and "Embedded FlashROM Characteristics" sections were updated.                                                                                                                                                                                                                             | 2-68,<br>2-78           |

Revision 17 5-5

# Datasheet Information

| Revision                                                                                | Changes                                                                                                                                                                                                                                                                                                                             | Page          |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Revision 10 (Apr 2009) Product Brief v1.5 DC and Switching Characteristics Advance v0.5 | The –F speed grade is no longer offered for IGLOO PLUS devices. References to it have been removed from the document. The speed grade column and note regarding –F speed grade were removed from "IGLOO PLUS Ordering Information". The "Speed Grade and Temperature Grade Matrix" section was removed.                             | III, IV       |

| Revision 9 (Feb 2009) Product Brief v1.4                                                | The "Advanced I/O" section was revised to add two bullets regarding support of wide range power supply voltage.                                                                                                                                                                                                                     | I             |

|                                                                                         | The "I/Os with Advanced I/O Standards" section was revised to add 3.0 V wide range to the list of supported voltages. The "Wide Range I/O Support" section is new.                                                                                                                                                                  | 1-7           |

| Revision 8 (Jan 2009)<br>Packaging v1.5                                                 | The "CS201" pin table was revised to add a note regarding pins G1 and H1.                                                                                                                                                                                                                                                           | 4-8           |

| Revision 7 (Dec 2008) Product Brief v1.3                                                | A note was added to IGLOO PLUS Devices: "AGLP060 in CS201 does not support the PLL."                                                                                                                                                                                                                                                | _             |

|                                                                                         | Table 2 • IGLOO PLUS FPGAs Package Size Dimensions was updated to change the nominal size of VQ176 from 100 to 400 mm <sup>2</sup> .                                                                                                                                                                                                | II            |

| Revision 6 (Oct 2008)  DC and Switching Characteristics Advance v0.4                    | Data was revised significantly in the following tables: Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings, STD Speed Grade, Commercial-Case Conditions: T <sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V                                                                         | 2-22,<br>2-33 |

|                                                                                         | Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings, STD Speed Grade Commercial-Case Conditions: $T_J$ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V Table 2-50 • 2.5 LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage Table 2-51 • 2.5 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage |               |

| Revision 5 (Aug 2008)<br>Product Brief v1.2                                             | The VQ128 and VQ176 packages were added to Table 1 • IGLOO PLUS Product Family, the "I/Os Per Package <sup>1</sup> " table, Table 2 • IGLOO PLUS FPGAs Package Size Dimensions, "IGLOO PLUS Ordering Information", and the "Temperature Grade Offerings" table.                                                                     | I to IV       |

| Packaging v1.4                                                                          | The "VQ128" package drawing and pin table are new.                                                                                                                                                                                                                                                                                  | 4-2           |

|                                                                                         | The "VQ176" package drawing and pin table are new.                                                                                                                                                                                                                                                                                  | 4-5           |

| Revision 4 (Jul 2008) Product Brief v1.1 DC and Switching Characteristics Advance v0.3  | As a result of the Libero IDE v8.4 release, Actel now offers a wide range of core voltage support. The document was updated to change 1.2 V / 1.5 V to 1.2 V to 1.5 V.                                                                                                                                                              | N/A           |

| Revision 3 (Jun 2008) DC and Switching Characteristics Advance v0.2                     | Tables have been updated to reflect default values in the software. The default I/O capacitance is 5 pF. Tables have been updated to include the LVCMOS 1.2 V I/O set.                                                                                                                                                              | N/A           |

|                                                                                         | Table note 3 was updated in Table 2-2 • Recommended Operating Conditions <sup>1,2</sup> to add the sentence, "VCCI should be at the same voltage within a given I/O bank." References to table notes 5, 6, 7, and 8 were added. Reference to table note 3 was removed from VPUMP Operation and placed next to VCC.                  | 2-2           |

|                                                                                         | Table 2-4 • Overshoot and Undershoot Limits <sup>1</sup> was revised to remove "as measured on quiet I/Os" from the title. Table note 2 was revised to remove "estimated SSO density over cycles." Table note 3 was deleted.                                                                                                        | 2-3           |

5-6 Revision 17