Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                            |

|--------------------------------|----------------------------------------------------------------------------|

| Product Status                 | Active                                                                     |

| Number of LABs/CLBs            | -                                                                          |

| Number of Logic Elements/Cells | 1584                                                                       |

| Total RAM Bits                 | 18432                                                                      |

| Number of I/O                  | 157                                                                        |

| Number of Gates                | 60000                                                                      |

| Voltage - Supply               | 1.425V ~ 1.575V                                                            |

| Mounting Type                  | Surface Mount                                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                         |

| Package / Case                 | 201-VFBGA, CSBGA                                                           |

| Supplier Device Package        | 201-CSP (8x8)                                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/aglp060v5-cs201i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Each I/O module contains several input, output, and output enable registers.

Hot-swap (also called hot-plug, or hot-insertion) is the operation of hot-insertion or hot-removal of a card in a powered-up system.

Cold-sparing (also called cold-swap) refers to the ability of a device to leave system data undisturbed when the system is powered up, while the component itself is powered down, or when power supplies are floating.

### Wide Range I/O Support

IGLOO PLUS devices support JEDEC-defined wide range I/O operation. IGLOO PLUS devices support both the JESD8-B specification, covering 3 V and 3.3 V supplies, for an effective operating range of 2.7 V to 3.6 V, and JESD8-12 with its 1.2 V nominal, supporting an effective operating range of 1.14 V to 1.575 V.

Wider I/O range means designers can eliminate power supplies or power conditioning components from the board or move to less costly components with greater tolerances. Wide range eases I/O bank management and provides enhanced protection from system voltage spikes, while providing the flexibility to easily run custom voltage applications.

### **Specifying I/O States During Programming**

You can modify the I/O states during programming in FlashPro. In FlashPro, this feature is supported for PDB files generated from Designer v8.5 or greater. See the *FlashPro User's Guide* for more information.

Note: PDB files generated from Designer v8.1 to Designer v8.4 (including all service packs) have limited display of Pin Numbers only.

- 1. Load a PDB from the FlashPro GUI. You must have a PDB loaded to modify the I/O states during programming.

- From the FlashPro GUI, click PDB Configuration. A FlashPoint Programming File Generator window appears.

- 3. Click the Specify I/O States During Programming button to display the Specify I/O States During Programming dialog box.

- 4. Sort the pins as desired by clicking any of the column headers to sort the entries by that header. Select the I/Os you wish to modify (Figure 1-4 on page 1-8).

- 5. Set the I/O Output State. You can set Basic I/O settings if you want to use the default I/O settings for your pins, or use Custom I/O settings to customize the settings for each pin. Basic I/O state settings:

- 1 I/O is set to drive out logic High

- 0 I/O is set to drive out logic Low

Last Known State – I/O is set to the last value that was driven out prior to entering the programming mode, and then held at that value during programming Z -Tri-State: I/O is tristated

# 2 – IGLOO PLUS DC and Switching Characteristics

## **General Specifications**

## **Operating Conditions**

Stresses beyond those listed in Table 2-1 may cause permanent damage to the device.

Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Absolute Maximum Ratings are stress ratings only; functional operation of the device at these or any other conditions beyond those listed under the Recommended Operating Conditions specified in Table 2-2 on page 2-2 is not implied.

Table 2-1 • Absolute Maximum Ratings

| Symbol                        | Parameter                    | Limits          | Units |

|-------------------------------|------------------------------|-----------------|-------|

| VCC                           | DC core supply voltage       | -0.3 to 1.65    | V     |

| VJTAG                         | JTAG DC voltage              | -0.3 to 3.75    | V     |

| VPUMP                         | Programming voltage          | -0.3 to 3.75    | V     |

| VCCPLL                        | Analog power supply (PLL)    | -0.3 to 1.65    | V     |

| VCCI                          | DC I/O buffer supply voltage | -0.3 to 3.75    | V     |

| VI <sup>1</sup>               | I/O input voltage            | −0.3 V to 3.6 V | V     |

| T <sub>STG</sub> <sup>2</sup> | Storage temperature          | -65 to +150     | °C    |

| $T_J^2$                       | Junction temperature         | +125            | °C    |

#### Notes:

<sup>1.</sup> The device should be operated within the limits specified by the datasheet. During transitions, the input signal may undershoot or overshoot according to the limits shown in Table 2-4 on page 2-3.

<sup>2.</sup> For flash programming and retention maximum limits, refer to Table 2-3 on page 2-3, and for recommended operating limits, refer to Table 2-2 on page 2-2.

## **Calculating Power Dissipation**

## **Quiescent Supply Current**

Quiescent supply current ( $I_{DD}$ ) calculation depends on multiple factors, including operating voltages (VCC, VCCI, and VJTAG), operating temperature, system clock frequency, and power mode usage. Microsemi recommends using the Power Calculator and SmartPower software estimation tools to evaluate the projected static and active power based on the user design, power mode usage, operating voltage, and temperature.

Table 2-8 • Power Supply State per Mode

|                      |     | Power Supply Configurations |      |       |                 |  |  |  |  |  |  |  |

|----------------------|-----|-----------------------------|------|-------|-----------------|--|--|--|--|--|--|--|

| Modes/Power Supplies | VCC | VCCPLL                      | VCCI | VJTAG | VPUMP           |  |  |  |  |  |  |  |

| Flash*Freeze         | On  | On                          | On   | On    | On/off/floating |  |  |  |  |  |  |  |

| Sleep                | Off | Off                         | On   | Off   | Off             |  |  |  |  |  |  |  |

| Shutdown             | Off | Off                         | Off  | Off   | Off             |  |  |  |  |  |  |  |

| No Flash*Freeze      | On  | On                          | On   | On    | On/off/floating |  |  |  |  |  |  |  |

Note: Off: Power Supply level = 0 V

Table 2-9 • Quiescent Supply Current (IDD) Characteristics, IGLOO PLUS Flash\*Freeze Mode\*

|                | Core Voltage | AGLP030 | AGLP060 | AGLP125 | Units |

|----------------|--------------|---------|---------|---------|-------|

| Typical (25°C) | 1.2 V        | 4       | 8       | 13      | μΑ    |

|                | 1.5 V        | 6       | 10      | 18      | μΑ    |

Note: \*IDD includes VCC, VPUMP, VCCI, VJTAG, and VCCPLL currents.

Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO PLUS Sleep Mode\*

| ICCI Current                           | Core Voltage  | AGLP030 | AGLP060 | AGLP125 | Units |

|----------------------------------------|---------------|---------|---------|---------|-------|

| VCCI = 1.2 V (per bank) Typical (25°C) | 1.2 V         | 1.7     | 1.7     | 1.7     | μΑ    |

| VCCI = 1.5 V (per bank) Typical (25°C) | 1.2 V / 1.5 V | 1.8     | 1.8     | 1.8     | μΑ    |

| VCCI = 1.8 V (per bank) Typical (25°C) | 1.2 V / 1.5 V | 1.9     | 1.9     | 1.9     | μΑ    |

| VCCI = 2.5 V (per bank) Typical (25°C) | 1.2 V / 1.5 V | 2.2     | 2.2     | 2.2     | μΑ    |

| VCCI = 3.3 V (per bank) Typical (25°C) | 1.2 V / 1.5 V | 2.5     | 2.5     | 2.5     | μΑ    |

Note: \*IDD = N<sub>BANKS</sub> \* ICCI

Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOO PLUS Shutdown Mode

|                | Core Voltage  | AGLP030 | AGLP060 | AGLP125 | Units |

|----------------|---------------|---------|---------|---------|-------|

| Typical (25°C) | 1.2 V / 1.5 V | 0       | 0       | 0       | μΑ    |

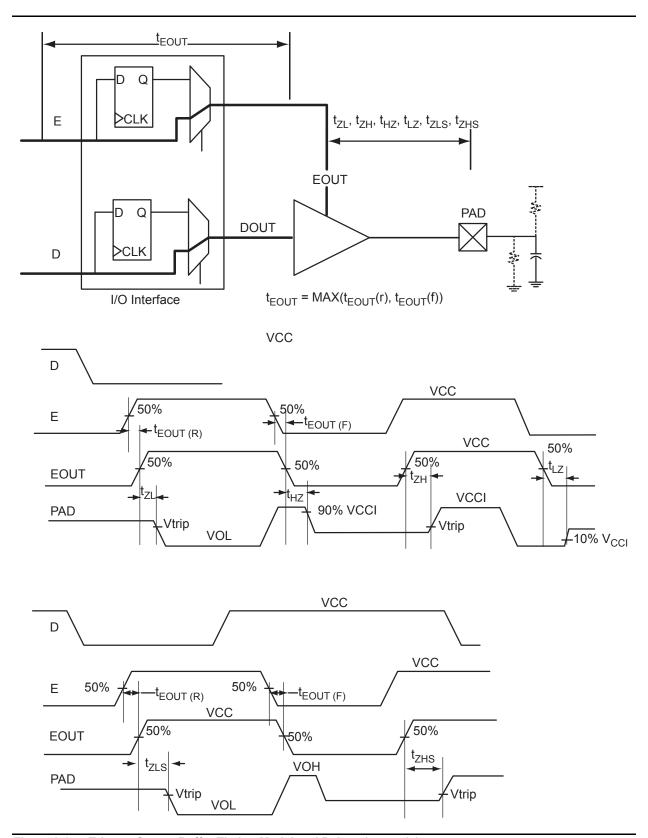

Figure 2-6 • Tristate Output Buffer Timing Model and Delays (example)

2-18 Revision 17

IGLOO PLUS DC and Switching Characteristics

Table 2-22 • Summary of Maximum and Minimum DC Input Levels

Applicable to Commercial and Industrial Conditions

|                                      | Comm             | nercial <sup>1</sup> | Indus            | strial <sup>2</sup> |

|--------------------------------------|------------------|----------------------|------------------|---------------------|

|                                      | IIL <sup>3</sup> | IIH <sup>4</sup>     | IIL <sup>3</sup> | IIH <sup>4</sup>    |

| DC I/O Standards                     | μΑ               | μΑ                   | μΑ               | μΑ                  |

| 3.3 V LVTTL / 3.3 V LVCMOS           | 10               | 10                   | 15               | 15                  |

| 3.3 V LVCMOS Wide Range              | 10               | 10                   | 15               | 15                  |

| 2.5 V LVCMOS                         | 10               | 10                   | 15               | 15                  |

| 1.8 V LVCMOS                         | 10               | 10                   | 15               | 15                  |

| 1.5 V LVCMOS                         | 10               | 10                   | 15               | 15                  |

| 1.2 V LVCMOS <sup>5</sup>            | 10               | 10                   | 15               | 15                  |

| 1.2 V LVCMOS Wide Range <sup>5</sup> | 10               | 10                   | 15               | 15                  |

#### Notes:

- 1. Commercial range (0°C <  $T_A$  < 70°C)

- 2. Industrial range  $(-40^{\circ}\text{C} < T_A < 85^{\circ}\text{C})$

- 3. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 4. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

- 5. Applicable to IGLOO PLUS V2 devices operating at VCCI 3 VCC.

## Summary of I/O Timing Characteristics – Default I/O Software Settings

Table 2-23 • Summary of AC Measuring Points

| Standard                   | Measuring Trip Point (Vtrip) |

|----------------------------|------------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 1.4 V                        |

| 3.3 V LVCMOS Wide Range    | 1.4 V                        |

| 2.5 V LVCMOS               | 1.2 V                        |

| 1.8 V LVCMOS               | 0.90 V                       |

| 1.5 V LVCMOS               | 0.75 V                       |

| 1.2 V LVCMOS               | 0.60 V                       |

| 1.2 V LVCMOS Wide Range    | 0.60 V                       |

2-20 Revision 17

Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings, STD Speed Grade Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

| I/O Standard                            | Drive Strength | Equivalent Software Default<br>Drive Strength Option <sup>1</sup> | Slew Rate | Capacitive Load (pF) | External Resistor (\O) | tвоит | t <sub>DP</sub> | <sup>‡</sup> DIN | t <sub>PY</sub> ) | tpys | teour | t <sub>ZL</sub> | tzн  | t <sub>LZ</sub> | tнz  | Units |

|-----------------------------------------|----------------|-------------------------------------------------------------------|-----------|----------------------|------------------------|-------|-----------------|------------------|-------------------|------|-------|-----------------|------|-----------------|------|-------|

| 3.3 V LVTTL /<br>3.3 V LVCMOS           | 12 mA          | 12 mA                                                             | High      | 5 pF                 | -                      | 0.98  | 2.31            | 0.19             | 0.99              | 1.37 | 0.67  | 2.34            | 1.86 | 2.65            | 3.38 | ns    |

| 3.3 V LVCMOS<br>Wide Range <sup>2</sup> | 100 µA         | 12 mA                                                             | High      | 5 pF                 | -                      | 0.98  | 3.21            | 0.19             | 1.32              | 1.92 | 0.67  | 3.21            | 2.52 | 3.73            | 4.73 | ns    |

| 2.5 V LVCMOS                            | 12 mA          | 12 mA                                                             | High      | 5 pF                 | _                      | 0.98  | 2.29            | 0.19             | 1.19              | 1.40 | 0.67  | 2.32            | 1.94 | 2.65            | 3.27 | ns    |

| 1.8 V LVCMOS                            | 8 mA           | 8 mA                                                              | High      | 5 pF                 | _                      | 0.98  | 2.45            | 0.19             | 1.12              | 1.61 | 0.67  | 2.48            | 2.16 | 2.71            | 3.16 | ns    |

| 1.5 V LVCMOS                            | 4 mA           | 4 mA                                                              | High      | 5 pF                 | -                      | 0.98  | 2.71            | 0.19             | 1.26              | 1.80 | 0.67  | 2.75            | 2.39 | 2.78            | 3.15 | ns    |

| 1.2 V LVCMOS                            | 2 mA           | 2 mA                                                              | High      | 5 pF                 | -                      | 0.98  | 3.38            | 0.19             | 1.57              | 2.34 | 0.67  | 3.26            | 2.78 | 2.99            | 3.24 | ns    |

| 1.2 V LVCMOS<br>Wide Range <sup>3</sup> | 100 µA         | 2 mA                                                              | High      | 5 pF                 | -                      | 0.98  | 3.38            | 0.19             | 1.57              | 2.34 | 0.67  | 3.26            | 2.78 | 2.99            | 3.24 | ns    |

#### Notes:

- 1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is  $\pm 100~\mu A$ . Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

- 3. All LVCMOS 1.2 V software macros support LVCMOS 1.2 V wide range as specified in the JESD8-12 specification.

- 4. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

IGLOO PLUS DC and Switching Characteristics

#### **Timing Characteristics**

#### Applies to 1.5 V DC Core Voltage

Table 2-36 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>.I</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 3.94            | 0.18             | 0.85            | 1.15             | 0.66              | 4.02            | 3.46            | 1.82            | 1.87            | ns    |

| 4 mA           | STD         | 0.97              | 3.94            | 0.18             | 0.85            | 1.15             | 0.66              | 4.02            | 3.46            | 1.82            | 1.87            | ns    |

| 6 mA           | STD         | 0.97              | 3.20            | 0.18             | 0.85            | 1.15             | 0.66              | 3.27            | 2.94            | 2.04            | 2.27            | ns    |

| 8 mA           | STD         | 0.97              | 3.20            | 0.18             | 0.85            | 1.15             | 0.66              | 3.27            | 2.94            | 2.04            | 2.27            | ns    |

| 12 mA          | STD         | 0.97              | 2.72            | 0.18             | 0.85            | 1.15             | 0.66              | 2.78            | 2.57            | 2.20            | 2.53            | ns    |

| 16 mA          | STD         | 0.97              | 2.72            | 0.18             | 0.85            | 1.15             | 0.66              | 2.78            | 2.57            | 2.20            | 2.53            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-37 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 2.36            | 0.18             | 0.85            | 1.15             | 0.66              | 2.41            | 1.90            | 1.82            | 1.98            | ns    |

| 4 mA           | STD         | 0.97              | 2.36            | 0.18             | 0.85            | 1.15             | 0.66              | 2.41            | 1.90            | 1.82            | 1.98            | ns    |

| 6 mA           | STD         | 0.97              | 1.96            | 0.18             | 0.85            | 1.15             | 0.66              | 2.01            | 1.56            | 2.04            | 2.38            | ns    |

| 8 mA           | STD         | 0.97              | 1.96            | 0.18             | 0.85            | 1.15             | 0.66              | 2.01            | 1.56            | 2.04            | 2.38            | ns    |

| 12 mA          | STD         | 0.97              | 1.76            | 0.18             | 0.85            | 1.15             | 0.66              | 1.80            | 1.39            | 2.20            | 2.64            | ns    |

| 16 mA          | STD         | 0.97              | 1.76            | 0.18             | 0.85            | 1.15             | 0.66              | 1.80            | 1.39            | 2.20            | 2.64            | ns    |

#### Notes:

- 1. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

- 2. Software default selection highlighted in gray.

#### Applies to 1.2 V DC Core Voltage

Table 2-38 • 3.3 V LVTTL / 3.3 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.98              | 4.56            | 0.19             | 0.99            | 1.37             | 0.67              | 4.63            | 3.98            | 2.26            | 2.57            | ns    |

| 4 mA           | STD         | 0.98              | 4.56            | 0.19             | 0.99            | 1.37             | 0.67              | 4.63            | 3.98            | 2.26            | 2.57            | ns    |

| 6 mA           | STD         | 0.98              | 3.80            | 0.19             | 0.99            | 1.37             | 0.67              | 3.96            | 3.45            | 2.49            | 2.98            | ns    |

| 8 mA           | STD         | 0.98              | 3.80            | 0.19             | 0.99            | 137              | 0.67              | 3.86            | 3.45            | 2.49            | 2.98            | ns    |

| 12 mA          | STD         | 0.98              | 3.31            | 0.19             | 0.99            | 1.37             | 0.67              | 3.36            | 3.07            | 2.65            | 3.25            | ns    |

| 16 mA          | STD         | 0.98              | 3.31            | 0.19             | 0.99            | 1.37             | 0.67              | 3.36            | 3.07            | 2.65            | 3.25            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

2-28 Revision 17

Table 2-39 • 3.3 V LVTTL / 3.3 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.98              | 2.92            | 0.19             | 0.99            | 1.37             | 0.67              | 2.97            | 2.38            | 2.25            | 2.70            | ns    |

| 4 mA           | STD         | 0.98              | 2.92            | 0.19             | 0.99            | 1.37             | 0.67              | 2.97            | 2.38            | 2.25            | 2.70            | ns    |

| 6 mA           | STD         | 0.98              | 2.52            | 0.19             | 0.99            | 1.37             | 0.67              | 2.56            | 2.03            | 2.49            | 3.11            | ns    |

| 8 mA           | STD         | 0.98              | 2.52            | 0.19             | 0.99            | 1.37             | 0.67              | 2.56            | 2.03            | 2.49            | 3.11            | ns    |

| 12 mA          | STD         | 0.98              | 2.31            | 0.19             | 0.99            | 1.37             | 0.67              | 2.34            | 1.86            | 2.65            | 3.38            | ns    |

| 16 mA          | STD         | 0.98              | 2.31            | 0.19             | 0.99            | 1.37             | 0.67              | 2.34            | 1.86            | 2.65            | 3.38            | ns    |

#### Notes:

- 1. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

- 2. Software default selection highlighted in gray

#### 3.3 V LVCMOS Wide Range

Table 2-40 • Minimum and Maximum DC Input and Output Levels

| 3.3 V LVCMOS<br>Wide Range | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> |           | 'IL       | v         | ΊΗ        | VOL       | VOH       | IOL | ЮН  | IOSL                    | IOSH                    | IIL <sup>2</sup>        | IIH <sup>3</sup>        |

|----------------------------|-------------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|-----|-------------------------|-------------------------|-------------------------|-------------------------|

| Drive<br>Strength          |                                                                               | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | μΑ  | μΑ  | Max.<br>μA <sup>4</sup> | Max.<br>μA <sup>4</sup> | μ <b>Α</b> <sup>5</sup> | μ <b>Α</b> <sup>5</sup> |

| 100 μΑ                     | 2 mA                                                                          | -0.3      | 0.8       | 2         | 3.6       | 0.2       | VDD – 0.2 | 100 | 100 | 25                      | 27                      | 10                      | 10                      |

| 100 μΑ                     | 4 mA                                                                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | VDD – 0.2 | 100 | 100 | 25                      | 27                      | 10                      | 10                      |

| 100 μΑ                     | 6 mA                                                                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | VDD – 0.2 | 100 | 100 | 51                      | 54                      | 10                      | 10                      |

| 100 μΑ                     | 8 mA                                                                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | VDD – 0.2 | 100 | 100 | 51                      | 54                      | 10                      | 10                      |

| 100 μΑ                     | 12 mA                                                                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | VDD – 0.2 | 100 | 100 | 103                     | 109                     | 10                      | 10                      |

| 100 μΑ                     | 16 mA                                                                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | VDD – 0.2 | 100 | 100 | 103                     | 109                     | 10                      | 10                      |

#### Notes:

- 1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

- 2. IIL is the input leakage current per I/O pin over recommended operation conditions where -0.3 V < VIN < VIL.

- 3. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < V CCI. Input current is larger when operating outside recommended ranges.

- 4. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

- 5. Currents are measured at 85°C junction temperature.

- 6. Software default selection highlighted in gray.

Table 2-41 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 3.3            | 1.4                  | 5                      |

Note: \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

#### **Timing Characteristics**

#### Applies to 1.5 V DC Core Voltage

Table 2-54 • 1.8 V LVCMOS Low Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>.I</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | $t_{ZL}$ | $t_{ZH}$ | $t_{LZ}$ | $t_{HZ}$ | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|----------|----------|----------|----------|-------|

| 2 mA           | STD         | 0.97              | 5.89            | 0.18             | 1.00            | 1.43             | 0.66              | 6.01     | 5.43     | 1.78     | 1.30     | ns    |

| 4 mA           | STD         | 0.97              | 4.82            | 0.18             | 1.00            | 1.43             | 0.66              | 4.92     | 4.56     | 2.08     | 2.08     | ns    |

| 6 mA           | STD         | 0.97              | 4.13            | 0.18             | 1.00            | 1.43             | 0.66              | 4.21     | 3.96     | 2.30     | 2.46     | ns    |

| 8 mA           | STD         | 0.97              | 4.13            | 0.18             | 1.00            | 1.43             | 0.66              | 4.21     | 3.96     | 2.30     | 2.46     | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-55 • 1.8 V LVCMOS High Slew – Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: T<sub>.I</sub> = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.97              | 2.82            | 0.18             | 1.00            | 1.43             | 0.66              | 2.88            | 2.78            | 1.78            | 1.35            | ns    |

| 4 mA           | STD         | 0.97              | 2.30            | 0.18             | 1.00            | 1.43             | 0.66              | 2.35            | 2.11            | 2.08            | 2.15            | ns    |

| 6 mA           | STD         | 0.97              | 2.00            | 0.18             | 1.00            | 1.43             | 0.66              | 2.04            | 1.76            | 2.29            | 2.55            | ns    |

| 8 mA           | STD         | 0.97              | 2.00            | 0.18             | 1.00            | 1.43             | 0.66              | 2.04            | 1.76            | 2.29            | 2.55            | ns    |

#### Notes:

- 1. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

- 2. Software default selection highlighted in gray.

#### Applies to 1.2 V DC Core Voltage

Table 2-56 • 1.8 V LVCMOS Low Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V

| Drive Strength | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|----------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 2 mA           | STD         | 0.98              | 6.43            | 0.19             | 1.12            | 1.61             | 0.67              | 6.54            | 5.93            | 2.19            | 1.88            | ns    |

| 4 mA           | STD         | 0.98              | 5.33            | 0.19             | 1.12            | 1.61             | 0.67              | 5.41            | 5.03            | 2.50            | 2.68            | ns    |

| 6 mA           | STD         | 0.98              | 4.61            | 0.19             | 1.12            | 1.61             | 0.67              | 4.69            | 4.41            | 2.72            | 3.07            | ns    |

| 8 mA           | STD         | 0.98              | 4.61            | 0.19             | 1.12            | 1.61             | 0.67              | 4.69            | 4.41            | 2.72            | 3.07            | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

Table 2-57 • 1.8 V LVCMOS High Slew – Applies to 1.2 V DC Core Voltage

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.7 V

| <b>Drive Strength</b> | Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | $t_{LZ}$ | t <sub>HZ</sub> | Units |

|-----------------------|-------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|----------|-----------------|-------|

| 2 mA                  | STD         | 0.98              | 3.30            | 0.19             | 1.12            | 1.61             | 0.67              | 3.34            | 3.21            | 2.19     | 1.93            | ns    |

| 4 mA                  | STD         | 0.98              | 2.76            | 0.19             | 1.12            | 1.61             | 0.67              | 2.79            | 2.51            | 2.50     | 2.76            | ns    |

| 6 mA                  | STD         | 0.98              | 2.45            | 0.19             | 1.12            | 1.61             | 0.67              | 2.48            | 2.16            | 2.71     | 3.16            | ns    |

| 8 mA                  | STD         | 0.98              | 2.45            | 0.19             | 1.12            | 1.61             | 0.67              | 2.48            | 2.16            | 2.71     | 3.16            | ns    |

#### Notes:

- 1. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

- 2. Software default selection highlighted in gray.

IGLOO PLUS DC and Switching Characteristics

#### 1.2 V DC Core Voltage

Table 2-77 • Output Data Register Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter            | Description                                                          | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|-------|

| t <sub>OCLKQ</sub>   | Clock-to-Q of the Output Data Register                               | 1.03 | ns    |

| tosud                | Data Setup Time for the Output Data Register                         | 0.52 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 1.22 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 1.31 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | ns    |

| torecclr             | Asynchronous Clear Recovery Time for the Output Data Register        | 0.24 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | ns    |

| torecpre             | Asynchronous Preset Recovery Time for the Output Data Register       | 0.24 | ns    |

| towclr               | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.19 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.19 | ns    |

| tockmpwh             | Clock Minimum Pulse Width High for the Output Data Register          | 0.31 | ns    |

| tockmpwl             | Clock Minimum Pulse Width Low for the Output Data Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

2-48 Revision 17

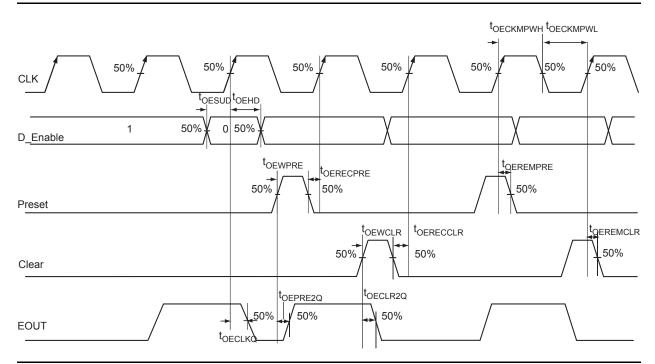

## **Output Enable Register**

Figure 2-16 • Output Enable Register Timing Diagram

**Timing Characteristics**

1.5 V DC Core Voltage

Table 2-78 • Output Enable Register Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

|                                                               |                                                                                                                                                                                                                                                                                               | Units                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| of the Output Enable Register                                 | 0.68                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| Time for the Output Enable Register                           | 0.33                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| Time for the Output Enable Register                           | 0.00                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| ous Clear-to-Q of the Output Enable Register                  | 0.84                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| ous Preset-to-Q of the Output Enable Register                 | 0.91                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| ous Clear Removal Time for the Output Enable Register         | 0.00                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| ous Clear Recovery Time for the Output Enable Register        | 0.24                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| ous Preset Removal Time for the Output Enable Register        | 0.00                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| ous Preset Recovery Time for the Output Enable Register       | 0.24                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| ous Clear Minimum Pulse Width for the Output Enable Register  | 0.19                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| ous Preset Minimum Pulse Width for the Output Enable Register | 0.19                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| num Pulse Width High for the Output Enable Register           | 0.31                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| num Pulse Width Low for the Output Enable Register            | 0.28                                                                                                                                                                                                                                                                                          | ns                                                                                                                                                                                                                                                                                                                                 |

| 1                                                             | ous Preset Removal Time for the Output Enable Register ous Preset Recovery Time for the Output Enable Register ous Clear Minimum Pulse Width for the Output Enable Register ous Preset Minimum Pulse Width for the Output Enable Register oum Pulse Width High for the Output Enable Register | ous Preset Removal Time for the Output Enable Register  0.00  ous Preset Recovery Time for the Output Enable Register  0.24  ous Clear Minimum Pulse Width for the Output Enable Register  0.19  ous Preset Minimum Pulse Width for the Output Enable Register  0.19  output Pulse Width High for the Output Enable Register  0.31 |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## **Timing Characteristics**

1.5 V DC Core Voltage

Table 2-80 • Combinatorial Cell Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.425 V

| Combinatorial Cell | Equation                | Parameter       | Std. | Units |

|--------------------|-------------------------|-----------------|------|-------|

| INV                | Y = !A                  | t <sub>PD</sub> | 0.72 | ns    |

| AND2               | Y = A · B               | t <sub>PD</sub> | 0.86 | ns    |

| NAND2              | Y = !(A · B)            | t <sub>PD</sub> | 1.00 | ns    |

| OR2                | Y = A + B               | t <sub>PD</sub> | 1.26 | ns    |

| NOR2               | Y = !(A + B)            | t <sub>PD</sub> | 1.16 | ns    |

| XOR2               | Y = A ⊕ B               | t <sub>PD</sub> | 1.46 | ns    |

| MAJ3               | Y = MAJ(A, B, C)        | t <sub>PD</sub> | 1.47 | ns    |

| XOR3               | Y = A ⊕ B ⊕ C           | t <sub>PD</sub> | 2.12 | ns    |

| MUX2               | Y = A !S + B S          | t <sub>PD</sub> | 1.24 | ns    |

| AND3               | $Y = A \cdot B \cdot C$ | t <sub>PD</sub> | 1.40 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### 1.2 V DC Core Voltage

Table 2-81 • Combinatorial Cell Propagation Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Combinatorial Cell | Equation                | Parameter       | Std. | Units |

|--------------------|-------------------------|-----------------|------|-------|

| INV                | Y = !A                  | t <sub>PD</sub> | 1.26 | ns    |

| AND2               | Y = A · B               | t <sub>PD</sub> | 1.46 | ns    |

| NAND2              | Y = !(A · B)            | t <sub>PD</sub> | 1.78 | ns    |

| OR2                | Y = A + B               | t <sub>PD</sub> | 2.47 | ns    |

| NOR2               | Y = !(A + B)            | t <sub>PD</sub> | 2.17 | ns    |

| XOR2               | Y = A ⊕ B               | t <sub>PD</sub> | 2.62 | ns    |

| MAJ3               | Y = MAJ(A, B, C)        | t <sub>PD</sub> | 2.66 | ns    |

| XOR3               | Y = A ⊕ B ⊕ C           | t <sub>PD</sub> | 3.77 | ns    |

| MUX2               | Y = A !S + B S          | t <sub>PD</sub> | 2.20 | ns    |

| AND3               | $Y = A \cdot B \cdot C$ | t <sub>PD</sub> | 2.49 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

IGLOO PLUS DC and Switching Characteristics

#### 1.2 V DC Core Voltage

Table 2-83 • Register Delays

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter           | Description                                                   | Std. | Units |

|---------------------|---------------------------------------------------------------|------|-------|

| t <sub>CLKQ</sub>   | Clock-to-Q of the Core Register                               | 1.61 | ns    |

| t <sub>SUD</sub>    | Data Setup Time for the Core Register                         | 1.17 | ns    |

| $t_{HD}$            | Data Hold Time for the Core Register                          | 0.00 | ns    |

| t <sub>SUE</sub>    | Enable Setup Time for the Core Register                       | 1.29 | ns    |

| t <sub>HE</sub>     | Enable Hold Time for the Core Register                        | 0.00 | ns    |

| t <sub>CLR2Q</sub>  | Asynchronous Clear-to-Q of the Core Register                  | 0.87 | ns    |

| t <sub>PRE2Q</sub>  | Asynchronous Preset-to-Q of the Core Register                 | 0.89 | ns    |

| t <sub>REMCLR</sub> | Asynchronous Clear Removal Time for the Core Register         | 0.00 | ns    |

| t <sub>RECCLR</sub> | Asynchronous Clear Recovery Time for the Core Register        | 0.24 | ns    |

| t <sub>REMPRE</sub> | Asynchronous Preset Removal Time for the Core Register        | 0.00 | ns    |

| t <sub>RECPRE</sub> | Asynchronous Preset Recovery Time for the Core Register       | 0.24 | ns    |

| t <sub>WCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Core Register  | 0.46 | ns    |

| t <sub>WPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Core Register | 0.46 | ns    |

| t <sub>CKMPWH</sub> | Clock Minimum Pulse Width High for the Core Register          | 0.95 | ns    |

| t <sub>CKMPWL</sub> | Clock Minimum Pulse Width Low for the Core Register           | 0.95 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

2-56 Revision 17

Table 2-95 • RAM512X18

Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V

| Parameter             | Description                                                                                                          | Std.  | Units |

|-----------------------|----------------------------------------------------------------------------------------------------------------------|-------|-------|

| t <sub>AS</sub>       | Address setup time                                                                                                   | 1.28  | ns    |

| t <sub>AH</sub>       | Address hold time                                                                                                    |       | ns    |

| t <sub>ENS</sub>      | REN, WEN setup time                                                                                                  | 1.13  | ns    |

| t <sub>ENH</sub>      | REN, WEN hold time                                                                                                   | 0.13  | ns    |

| t <sub>DS</sub>       | Input data (WD) setup time                                                                                           | 1.10  | ns    |

| t <sub>DH</sub>       | Input data (WD) hold time                                                                                            | 0.55  | ns    |

| t <sub>CKQ1</sub>     | Clock High to new data valid on RD (output retained)                                                                 |       | ns    |

| t <sub>CKQ2</sub>     | Clock High to new data valid on RD (pipelined)                                                                       | 2.67  | ns    |

| t <sub>C2CRWH</sub> 1 | Address collision clk-to-clk delay for reliable read access after write on same address – applicable to opening edge |       | ns    |

| t <sub>C2CWRH</sub> 1 | Address collision clk-to-clk delay for reliable write access after read on same address – applicable to opening edge |       | ns    |

| t <sub>RSTBQ</sub>    | RESET Low to data out Low on RD (flow through)                                                                       | 3.21  | ns    |

|                       | RESET Low to data out Low on RD (pipelined)                                                                          | 3.21  | ns    |

| t <sub>REMRSTB</sub>  | RESET removal                                                                                                        | 0.93  | ns    |

| t <sub>RECRSTB</sub>  | RESET recovery                                                                                                       |       | ns    |

| t <sub>MPWRSTB</sub>  | RESET minimum pulse width                                                                                            |       | ns    |

| t <sub>CYC</sub>      | Clock cycle time                                                                                                     | 10.90 | ns    |

| F <sub>MAX</sub>      | Maximum frequency                                                                                                    | 92    | MHz   |

#### Notes:

<sup>1.</sup> For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs.

<sup>2.</sup> For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

## **Special Function Pins**

NC No Connect

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

DC Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

## **Packaging**

Semiconductor technology is constantly shrinking in size while growing in capability and functional integration. To enable next-generation silicon technologies, semiconductor packages have also evolved to provide improved performance and flexibility.

Microsemi consistently delivers packages that provide the necessary mechanical and environmental protection to ensure consistent reliability and performance. Microsemi IC packaging technology efficiently supports high-density FPGAs with large-pin-count Ball Grid Arrays (BGAs), but is also flexible enough to accommodate stringent form factor requirements for Chip Scale Packaging (CSP). In addition, Microsemi offers a variety of packages designed to meet your most demanding application and economic requirements for today's embedded and mobile systems.

### **Related Documents**

IGLOO PLUS Device Family User's Guide

http://www.microsemi.com/soc/documents/IGLOOPLUS UG.pdf

The following documents provide packaging information and device selection for low power flash devices.

## **Product Catalog**

http://www.microsemi.com/soc/documents/ProdCat PIB.pdf

Lists devices currently recommended for new designs and the packages available for each member of the family. Use this document or the datasheet tables to determine the best package for your design, and which package drawing to use.

## Package Mechanical Drawings

http://www.microsemi.com/soc/documents/PckgMechDrwngs.pdf

This document contains the package mechanical drawings for all packages currently or previously supplied by Microsemi. Use the bookmarks to navigate to the package mechanical drawings.

Additional packaging materials are available at

http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

### IGLOO PLUS Low Power Flash FPGAs

| (          | CS289    |

|------------|----------|

|            | AGLP030  |

| Pin Number | Function |

| A1         | IO03RSB0 |

| A2         | NC       |

| A3         | NC       |

| A4         | GND      |

| A5         | IO10RSB0 |

| A6         | IO14RSB0 |

| A7         | IO16RSB0 |

| A8         | IO18RSB0 |

| A9         | GND      |

| A10        | IO23RSB0 |

| A11        | IO27RSB0 |

| A12        | NC       |

| A13        | NC       |

| A14        | GND      |

| A15        | NC       |

| A16        | NC       |

| A17        | IO30RSB0 |

| B1         | IO01RSB0 |

| B2         | GND      |

| В3         | NC       |

| B4         | NC       |

| B5         | IO07RSB0 |

| В6         | NC       |

| В7         | VCCIB0   |

| В8         | IO17RSB0 |

| В9         | IO19RSB0 |

| B10        | IO24RSB0 |

| B11        | IO28RSB0 |

| B12        | VCCIB0   |

| B13        | NC       |

| B14        | NC       |

| B15        | NC       |

| B16        | IO31RSB0 |

| B17        | GND      |

| C1         | NC       |

| C2         | IO00RSB0 |

| C3         | IO04RSB0 |

|            |          |

|            | CS289               |  |  |

|------------|---------------------|--|--|

| •          |                     |  |  |

| Pin Number | AGLP030<br>Function |  |  |

| C4         | NC                  |  |  |

| C5         | VCCIB0              |  |  |

| C6         | IO09RSB0            |  |  |

| C7         | IO13RSB0            |  |  |

| C8         | IO15RSB0            |  |  |

| C9         | IO21RSB0            |  |  |

| C10        | GND                 |  |  |

| C11        | IO29RSB0            |  |  |

| C12        | NC                  |  |  |

| C13        | NC                  |  |  |

| C14        | NC                  |  |  |

| C15        | GND                 |  |  |

| C16        | IO34RSB0            |  |  |

| C17        | NC                  |  |  |

| D1         | NC                  |  |  |

| D2         | IO119RSB3           |  |  |

| D3         | GND                 |  |  |

| D4         | IO02RSB0            |  |  |

| D5         | NC                  |  |  |

| D6         | NC                  |  |  |

| D7         | NC                  |  |  |

| D8         | GND                 |  |  |

| D9         | IO20RSB0            |  |  |

| D10        | IO25RSB0            |  |  |

| D11        | NC                  |  |  |

| D12        | NC                  |  |  |

| D13        | GND                 |  |  |

| D14        | IO32RSB0            |  |  |

| D15        | IO35RSB0            |  |  |

| D16        | NC                  |  |  |

| D17        | NC                  |  |  |

| E1         | VCCIB3              |  |  |

| E2         | IO114RSB3           |  |  |

| E3         | IO115RSB3           |  |  |

| E4         | IO118RSB3           |  |  |

| E5         | IO05RSB0            |  |  |

| E6         | NC                  |  |  |

|            |                     |  |  |

| CS289      |                     |  |

|------------|---------------------|--|

| <u> </u>   |                     |  |

| Pin Number | AGLP030<br>Function |  |

| E7         | IO06RSB0            |  |

| E8         | IO11RSB0            |  |

| E9         | IO22RSB0            |  |

| E10        | IO26RSB0            |  |

| E11        | VCCIB0              |  |

| E12        | NC                  |  |

| E13        | IO33RSB0            |  |

| E14        | IO36RSB1            |  |

| E15        | IO38RSB1            |  |

| E16        | VCCIB1              |  |

| E17        | NC                  |  |

| F1         | IO111RSB3           |  |

| F2         | NC                  |  |

| F3         | IO116RSB3           |  |

| F4         | VCCIB3              |  |

| F5         | IO117RSB3           |  |

| F6         | NC                  |  |

| F7         | NC                  |  |

| F8         | IO08RSB0            |  |

| F9         | IO12RSB0            |  |

| F10        | NC                  |  |

| F11        | NC                  |  |

| F12        | NC                  |  |

| F13        | NC                  |  |

| F14        | GND                 |  |

| F15        | NC                  |  |

| F16        | IO37RSB1            |  |

| F17        | IO41RSB1            |  |

| G1         | IO110RSB3           |  |

| G2         | GND                 |  |

| G3         | IO113RSB3           |  |

| G4         | NC                  |  |

| G5         | NC                  |  |

| G6         | NC                  |  |

| G7         | GND                 |  |

| G8         | GND                 |  |

| G9         | VCC                 |  |

#### Datasheet Information

| Revision                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Page   |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Revision 13<br>(June 2012)  | Figure 2-30 • FIFO Read and Figure 2-31 • FIFO Write have been added (SAR 34843).                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-73   |

|                             | Updated the terminology used in Timing Characteristics in the following tables: Table 2-96 • FIFO and Table 2-97 • FIFO (SAR 38236).                                                                                                                                                                                                                                                                                                                                                                                | 2-76   |

|                             | The following sentence was removed from the "VMVx I/O Supply Voltage (quiet)" section in the "Pin Descriptions and Packaging" section: "Within the package, the VMV plane is decoupled from the simultaneous switching noise originating from the output buffer VCCI domain" and replaced with "Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks" (SAR 38320). The datasheet mentions that "VMV pins must be connected to the corresponding VCCI pins" for an ESD enhancement. | 3-1    |

| Revision 12<br>(March 2012) | The "In-System Programming (ISP) and Security" section and "Security" section were revised to clarify that although no existing security measures can give an absolute guarantee, Microsemi FPGAs implement the best security available in the industry (SAR 34664).                                                                                                                                                                                                                                                | l, 1-2 |

|                             | The Y security option and Licensed DPA Logo were added to the "IGLOO PLUS Ordering Information" section. The trademarked Licensed DPA Logo identifies that a product is covered by a DPA counter-measures license from Cryptography Research (SAR 34724).                                                                                                                                                                                                                                                           | III    |

|                             | The "Specifying I/O States During Programming" section is new (SAR 34695).                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-7    |

|                             | The following sentence was removed from the "Advanced Architecture" section:                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1-3    |

|                             | "In addition, extensive on-chip programming circuitry allows for rapid, single-voltage (3.3 V) programming of IGLOO PLUS devices via an IEEE 1532 JTAG interface" (SAR 34684).                                                                                                                                                                                                                                                                                                                                      |        |

5-2 Revision 17

#### Datasheet Information

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                        | Page         |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Revision 11<br>(continued) | Table 2-2 • Recommended Operating Conditions <sup>1,2</sup> was revised. 1.2 V DC wide range supply voltage and 3.3 V wide range supply voltage (SAR 26270) were added for VCCI. VJTAG DC Voltage was revised (SAR 24052). The value range for VPUMP programming voltage for operation was changed from "0 to 3.45" to "0 to 3.6" (SAR 25220). | 2-2          |

|                            | Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = 70°C, VCC = 1.425 V) and Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to TJ = 70°C, VCC = 1.14 V) were revised.                                                                                               | 2-6, 2-6     |

|                            | Table 2-8 • Power Supply State per Mode is new.                                                                                                                                                                                                                                                                                                | 2-7          |

|                            | The tables in the "Quiescent Supply Current" section were updated (SARs 24882 and 24112). Some of the table notes were changed or deleted.                                                                                                                                                                                                     | 2-7          |

|                            | VIH maximum values in tables were updated as needed to 3.6 V (SARs 20990, 79370).                                                                                                                                                                                                                                                              | N/A          |

|                            | The values in the following tables were updated. 3.3 V LVCMOS and 1.2 V LVCMOS wide range were added to the tables where applicable.                                                                                                                                                                                                           |              |

|                            | Table 2-13 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings                                                                                                                                                                                                                                                       | 2-9          |

|                            | Table 2-14 • Summary of I/O Output Buffer Power (per pin) – Default I/O Software Settings <sup>1</sup>                                                                                                                                                                                                                                         | 2-9          |

|                            | Table 2-21 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Commercial and Industrial Conditions—Software Default Settings                                                                                                                                                                                            | 2-19<br>2-20 |

|                            | Table 2-22 • Summary of Maximum and Minimum DC Input Levels                                                                                                                                                                                                                                                                                    | 2-20         |

|                            | Table 2-23 • Summary of AC Measuring Points                                                                                                                                                                                                                                                                                                    | 2 20         |

|                            | Table 2-25 • Summary of I/O Timing Characteristics—Software Default Settings, STD Speed Grade, Commercial-Case Conditions: $T_J$ = 70°C, Worst-Case VCC = 1.425 V, Worst-Case VCCI = 3.0 V                                                                                                                                                     | 2-22         |

|                            | Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings, STD Speed Grade Commercial-Case Conditions: $T_J$ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V                                                                                                                                                       | 2-23         |

|                            | Table 2-28 • I/O Output Buffer Maximum Resistances <sup>1</sup>                                                                                                                                                                                                                                                                                | 2-24         |

|                            | A table note was added to Table 2-16 • Different Components Contributing to the                                                                                                                                                                                                                                                                | 2-10,        |

|                            | Static Power Consumption in IGLOO PLUS Devices and Table 2-18 • Different Components Contributing to the Static Power Consumption in IGLOO PLUS Devices stating the value for PDC4 is the minimum contribution of the PLL when operating at lowest frequency.                                                                                  | 2-11         |

|                            | Table 2-29 • I/O Weak Pull-Up/Pull-Down Resistances was revised, including addition of 3.3 V and 1.2 V LVCMOS wide range.                                                                                                                                                                                                                      | 2-25         |

|                            | The notes defining $R_{WEAK\ PULL-UP-MAX}$ and $R_{WEAK\ PULLDOWN-MAX}$ were revised (SAR 21348).                                                                                                                                                                                                                                              |              |