Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                      |

|--------------------------------|-----------------------------------------------------------------------------|

| Number of LABs/CLBs            | ·                                                                           |

| Number of Logic Elements/Cells | 1584                                                                        |

| Total RAM Bits                 | 18432                                                                       |

| Number of I/O                  | 157                                                                         |

| Number of Gates                | 60000                                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 201-VFBGA, CSBGA                                                            |

| Supplier Device Package        | 201-CSP (8x8)                                                               |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/aglp060v5-csg201i |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 🌜 Microsemi.

IGLOO PLUS Low Power Flash FPGAs

# I/Os Per Package<sup>1</sup>

| IGLOO PLUS Devices | AGLP030 | LP030 AGLP060     |     |  |  |  |  |

|--------------------|---------|-------------------|-----|--|--|--|--|

| Package            |         | Single-Ended I/Os |     |  |  |  |  |

| CS201              | 120     | 157               | _   |  |  |  |  |

| CS281              | -       | -                 | 212 |  |  |  |  |

| CS289              | 120     | 157               | 212 |  |  |  |  |

| VQ128              | 101     | -                 | _   |  |  |  |  |

| VQ176              | -       | 137               | _   |  |  |  |  |

Note: When the Flash\*Freeze pin is used to directly enable Flash\*Freeze mode and not used as a regular I/O, the number of singleended user I/Os available is reduced by one.

### Table 2 • IGLOO PLUS FPGAs Package Size Dimensions

| Package                | CS201 | CS281   | CS289   | VQ128   | VQ176   |

|------------------------|-------|---------|---------|---------|---------|

| Length × Width (mm/mm) | 8 × 8 | 10 × 10 | 14 × 14 | 14 × 14 | 20 × 20 |

| Nominal Area (mm2)     | 64    | 100     | 196     | 196     | 400     |

| Pitch (mm)             | 0.5   | 0.5     | 0.8     | 0.4     | 0.4     |

| Height (mm)            | 0.89  | 1.05    | 1.20    | 1.0     | 1.0     |

# **IGLOO PLUS Device Status**

| IGLOO PLUS Device | Status     |

|-------------------|------------|

| AGLP030           | Production |

| AGLP060           | Production |

| AGLP125           | Production |

The IGLOO PLUS family device architecture mitigates the need for ASIC migration at higher user volumes. This makes the IGLOO PLUS family a cost-effective ASIC replacement solution, especially for applications in the consumer, networking/communications, computing, and avionics markets.

# Firm-Error Immunity

Firm errors occur most commonly when high-energy neutrons, generated in the upper atmosphere, strike a configuration cell of an SRAM FPGA. The energy of the collision can change the state of the configuration cell and thus change the logic, routing, or I/O behavior in an unpredictable way. These errors are impossible to prevent in SRAM FPGAs. The consequence of this type of error can be a complete system failure. Firm errors do not exist in the configuration memory of IGLOO PLUS flash-based FPGAs. Once it is programmed, the flash cell configuration element of IGLOO PLUS FPGAs cannot be altered by high-energy neutrons and is therefore immune to them. Recoverable (or soft) errors occur in the user data SRAM of all FPGA devices. These can easily be mitigated by using error detection and correction (EDAC) circuitry built into the FPGA fabric.

# **Advanced Flash Technology**

The IGLOO PLUS family offers many benefits, including nonvolatility and reprogrammability, through an advanced flash-based, 130 nm LVCMOS process with seven layers of metal. Standard CMOS design techniques are used to implement logic and control functions. The combination of fine granularity, enhanced flexible routing resources, and abundant flash switches allows for very high logic utilization without compromising device routability or performance. Logic functions within the device are interconnected through a four-level routing hierarchy.

IGLOO PLUS family FPGAs utilize design and process techniques to minimize power consumption in all modes of operation.

# **Advanced Architecture**

The proprietary IGLOO PLUS architecture provides granularity comparable to standard-cell ASICs. The IGLOO PLUS device consists of five distinct and programmable architectural features (Figure 1-1 on page 1-4):

- Flash\*Freeze technology

- FPGA VersaTiles

- Dedicated FlashROM

- Dedicated SRAM/FIFO memory<sup>†</sup>

- Extensive CCCs and PLLs<sup>†</sup>

- Advanced I/O structure

The FPGA core consists of a sea of VersaTiles. Each VersaTile can be configured as a three-input logic function, a D-flip-flop (with or without enable), or a latch by programming the appropriate flash switch interconnections. The versatility of the IGLOO PLUS core tile as either a three-input lookup table (LUT) equivalent or a D-flip-flop/latch with enable allows for efficient use of the FPGA fabric. The VersaTile capability is unique to the ProASIC® family of third-generation-architecture flash FPGAs. VersaTiles are connected with any of the four levels of routing hierarchy. Flash switches are distributed throughout the device to provide nonvolatile, reconfigurable interconnect programming. Maximum core utilization is possible for virtually any design.

*<sup>†</sup>* The AGLP030 device does not support PLL or SRAM.

IGLOO PLUS Device Family Overview

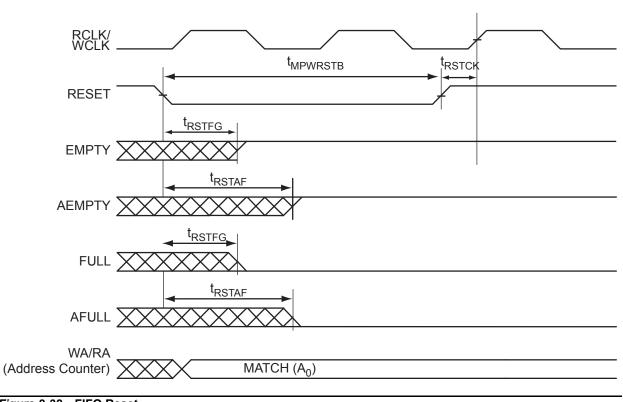

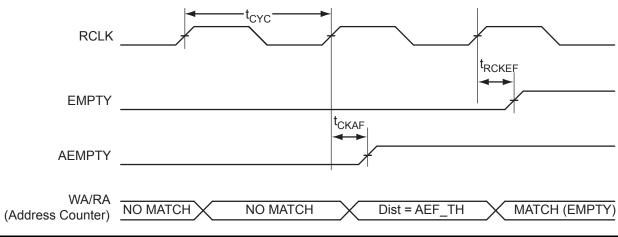

# SRAM and FIFO

IGLOO PLUS devices (except AGLP030 devices) have embedded SRAM blocks along their north side. Each variable-aspect-ratio SRAM block is 4,608 bits in size. Available memory configurations are 256×18, 512×9, 1k×4, 2k×2, and 4k×1 bits. The individual blocks have independent read and write ports that can be configured with different bit widths on each port. For example, data can be sent through a 4-bit port and read as a single bitstream. The embedded SRAM blocks can be initialized via the device JTAG port (ROM emulation mode) using the UJTAG macro (except in AGLP030 devices).

In addition, every SRAM block has an embedded FIFO control unit. The control unit allows the SRAM block to be configured as a synchronous FIFO without using additional core VersaTiles. The FIFO width and depth are programmable. The FIFO also features programmable Almost Empty (AEMPTY) and Almost Full (AFULL) flags in addition to the normal Empty and Full flags. The embedded FIFO control unit contains the counters necessary for generation of the read and write address pointers. The embedded SRAM/FIFO blocks can be cascaded to create larger configurations.

# PLL and CCC

IGLOO PLUS devices provide designers with very flexible clock conditioning circuit (CCC) capabilities. Each member of the IGLOO PLUS family contains six CCCs. One CCC (center west side) has a PLL. The AGLP030 device does not have a PLL or CCCs; it contains only inputs to six globals.

The six CCC blocks are located at the four corners and the centers of the east and west sides. One CCC (center west side) has a PLL.

The four corner CCCs and the east CCC allow simple clock delay operations as well as clock spine access.

The inputs of the six CCC blocks are accessible from the FPGA core or from one of several inputs located near the CCC that have dedicated connections to the CCC block.

The CCC block has these key features:

- Wide input frequency range (f<sub>IN CCC</sub>) = 1.5 MHz up to 250 MHz

- Output frequency range (f<sub>OUT CCC</sub>) = 0.75 MHz up to 250 MHz

- 2 programmable delay types for clock skew minimization

- Clock frequency synthesis (for PLL only)

Additional CCC specifications:

- Internal phase shift = 0°, 90°, 180°, and 270°. Output phase shift depends on the output divider configuration (for PLL only).

- Output duty cycle = 50% ± 1.5% or better (for PLL only)

- Low output jitter: worst case < 2.5% × clock period peak-to-peak period jitter when single global network used (for PLL only)

- Maximum acquisition time is 300 µs (for PLL only)

- Exceptional tolerance to input period jitter—allowable input jitter is up to 1.5 ns (for PLL only)

- + Four precise phases; maximum misalignment between adjacent phases (for PLL only) is 40 ps × 250 MHz /  $f_{OUT\ CCC}$

## **Global Clocking**

IGLOO PLUS devices have extensive support for multiple clocking domains. In addition to the CCC and PLL support described above, there is a comprehensive global clock distribution network.

Each VersaTile input and output port has access to nine VersaNets: six chip (main) and three quadrant global networks. The VersaNets can be driven by the CCC or directly accessed from the core via multiplexers (MUXes). The VersaNets can be used to distribute low-skew clock signals or for rapid distribution of high-fanout nets.

# I/Os with Advanced I/O Standards

The IGLOO PLUS family of FPGAs features a flexible I/O structure, supporting a range of voltages (1.2 V, 1.5 V, 1.8 V, 2.5 V, 3.0 V wide range, and 3.3 V). IGLOO PLUS FPGAs support many different I/O standards.

The I/Os are organized into four banks. All devices in IGLOO PLUS have four banks. The configuration of these banks determines the I/O standards supported.

IGLOO PLUS DC and Switching Characteristics

# Package Thermal Characteristics

The device junction-to-case thermal resistivity is  $\theta_{jc}$  and the junction-to-ambient air thermal resistivity is  $\theta_{ja}$ . The thermal characteristics for  $\theta_{ja}$  are shown for two air flow rates. The maximum operating junction temperature is 100°C. EQ 2 shows a sample calculation of the maximum operating power dissipation allowed for a 484-pin FBGA package at commercial temperature and in still air.

EQ 2

Maximum Power Allowed =

$$\frac{\text{Max. junction temp. (°C)} - \text{Max. ambient temp. (°C)}}{\theta_{ja}(°C/W)} = \frac{100°C - 70°C}{20.5°C/W} = 1.46 \text{ W}$$

|                             |         | Pin   |               |               | $	heta_{ja}$ |       |         |      |

|-----------------------------|---------|-------|---------------|---------------|--------------|-------|---------|------|

| Package Type                | Device  | Count | $\theta_{jc}$ | $\theta_{jb}$ | Still Air    | 1 m/s | 2.5 m/s | Unit |

| Chip Scale Package (CSP)    | AGLP030 | CS201 | -             | -             | 46.3         | -     | -       | C/W  |

|                             | AGLP060 | CS201 | 7.1           | 19.7          | 40.5         | 35.1  | 32.9    | C/W  |

|                             | AGLP060 | CS289 | 13.9          | 34.1          | 48.7         | 43.5  | 41.9    | C/W  |

|                             | AGLP125 | CS289 | 10.8          | 27.9          | 42.2         | 37.1  | 35.5    | C/W  |

|                             | AGLP125 | CS281 | 11.3          | 17.6          | -            | -     | -       | C/W  |

| Thin Quad Flat Package (VQ) | AGLP030 | VQ128 | 18.0          | 50.0          | 56.0         | 49.0  | 47.0    | C/W  |

|                             | AGLP060 | VQ176 | 21.0          | 55.0          | 58.0         | 52.0  | 50.0    | C/W  |

### Table 2-5 • Package Thermal Resistivities

## **Temperature and Voltage Derating Factors**

Table 2-6 • Temperature and Voltage Derating Factors for Timing Delays (normalized to T<sub>J</sub> = 70°C, VCC = 1.425 V)

For IGLOO PLUS V2 or V5 devices, 1.5 V DC Core Supply Voltage

| Array Voltage |       | Junction Temperature (°C) |       |       |       |       |  |  |  |  |  |  |  |

|---------------|-------|---------------------------|-------|-------|-------|-------|--|--|--|--|--|--|--|

| VCC (V)       | –40°C | O°C                       | 25°C  | 70°C  | 85°C  | 100°C |  |  |  |  |  |  |  |

| 1.425         | 0.934 | 0.953                     | 0.971 | 1.000 | 1.007 | 1.013 |  |  |  |  |  |  |  |

| 1.5           | 0.855 | 0.874                     | 0.891 | 0.917 | 0.924 | 0.929 |  |  |  |  |  |  |  |

| 1.575         | 0.799 | 0.816                     | 0.832 | 0.857 | 0.864 | 0.868 |  |  |  |  |  |  |  |

# Table 2-7 • Temperature and Voltage Derating Factors for Timing Delays (normalized to T<sub>J</sub> = 70°C, VCC = 1.14 V)

For IGLOO PLUS V2, 1.2 V DC Core Supply Voltage

| Array Voltage |       | Junction Temperature (°C) |       |       |       |       |  |  |  |  |  |  |  |

|---------------|-------|---------------------------|-------|-------|-------|-------|--|--|--|--|--|--|--|

| VCC (V)       | –40°C | 0°C                       | 25°C  | 70°C  | 85°C  | 100°C |  |  |  |  |  |  |  |

| 1.14          | 0.963 | 0.975                     | 0.989 | 1.000 | 1.007 | 1.011 |  |  |  |  |  |  |  |

| 1.2           | 0.853 | 0.865                     | .0877 | 0.893 | 0.893 | 0.897 |  |  |  |  |  |  |  |

| 1.26          | 0.781 | 0.792                     | 0.803 | 0.813 | 0.819 | 0.822 |  |  |  |  |  |  |  |

# **Calculating Power Dissipation**

# **Quiescent Supply Current**

Quiescent supply current ( $I_{DD}$ ) calculation depends on multiple factors, including operating voltages (VCC, VCCI, and VJTAG), operating temperature, system clock frequency, and power mode usage. Microsemi recommends using the Power Calculator and SmartPower software estimation tools to evaluate the projected static and active power based on the user design, power mode usage, operating voltage, and temperature.

## Table 2-8 • Power Supply State per Mode

|                      |     | Power Supply Configurations |      |       |                 |  |  |  |  |  |  |

|----------------------|-----|-----------------------------|------|-------|-----------------|--|--|--|--|--|--|

| Modes/Power Supplies | VCC | VCCPLL                      | VCCI | VJTAG | VPUMP           |  |  |  |  |  |  |

| Flash*Freeze         | On  | On                          | On   | On    | On/off/floating |  |  |  |  |  |  |

| Sleep                | Off | Off                         | On   | Off   | Off             |  |  |  |  |  |  |

| Shutdown             | Off | Off                         | Off  | Off   | Off             |  |  |  |  |  |  |

| No Flash*Freeze      | On  | On                          | On   | On    | On/off/floating |  |  |  |  |  |  |

*Note:* Off: Power Supply level = 0 V

## Table 2-9 • Quiescent Supply Current (IDD) Characteristics, IGLOO PLUS Flash\*Freeze Mode\*

|                | Core Voltage | AGLP030 | AGLP060 | AGLP125 | Units |

|----------------|--------------|---------|---------|---------|-------|

| Typical (25°C) | 1.2 V        | 4       | 8       | 13      | μA    |

|                | 1.5 V        | 6       | 10      | 18      | μA    |

|                |              | 6       | 10      | 18      |       |

Note: \*IDD includes VCC, VPUMP, VCCI, VJTAG, and VCCPLL currents.

### Table 2-10 • Quiescent Supply Current (IDD) Characteristics, IGLOO PLUS Sleep Mode\*

| ICCI Current                           | Core Voltage  | AGLP030 | AGLP060 | AGLP125 | Units |

|----------------------------------------|---------------|---------|---------|---------|-------|

| VCCI = 1.2 V (per bank) Typical (25°C) | 1.2 V         | 1.7     | 1.7     | 1.7     | μA    |

| VCCI = 1.5 V (per bank) Typical (25°C) | 1.2 V / 1.5 V | 1.8     | 1.8     | 1.8     | μA    |

| VCCI = 1.8 V (per bank) Typical (25°C) | 1.2 V / 1.5 V | 1.9     | 1.9     | 1.9     | μA    |

| VCCI = 2.5 V (per bank) Typical (25°C) | 1.2 V / 1.5 V | 2.2     | 2.2     | 2.2     | μA    |

| VCCI = 3.3 V (per bank) Typical (25°C) | 1.2 V / 1.5 V | 2.5     | 2.5     | 2.5     | μA    |

Note: \*IDD = N<sub>BANKS</sub> \* ICCI

### Table 2-11 • Quiescent Supply Current (IDD) Characteristics, IGLOO PLUS Shutdown Mode

|                | Core Voltage  | AGLP030 | AGLP060 | AGLP125 | Units |

|----------------|---------------|---------|---------|---------|-------|

| Typical (25°C) | 1.2 V / 1.5 V | 0       | 0       | 0       | μA    |

| I/O Standard                            | Drive Strength | Equivalent Software Default<br>Drive Strength Option <sup>1</sup> | Slew Rate | Capacitive Load (pF) | External Resistor ( $\Omega$ ) | teouт | top  | t <sub>DIN</sub> | tev) | tpys | teour | tzı  | tzH  | tız  | t <sub>HZ</sub> | Units |

|-----------------------------------------|----------------|-------------------------------------------------------------------|-----------|----------------------|--------------------------------|-------|------|------------------|------|------|-------|------|------|------|-----------------|-------|

| 3.3 V LVTTL /<br>3.3 V LVCMOS           | 12 mA          | 12 mA                                                             | High      | 5 pF                 | -                              | 0.98  | 2.31 | 0.19             | 0.99 | 1.37 | 0.67  | 2.34 | 1.86 | 2.65 | 3.38            | ns    |

| 3.3 V LVCMOS<br>Wide Range <sup>2</sup> | 100 µA         | 12 mA                                                             | High      | 5 pF                 | Ι                              | 0.98  | 3.21 | 0.19             | 1.32 | 1.92 | 0.67  | 3.21 | 2.52 | 3.73 | 4.73            | ns    |

| 2.5 V LVCMOS                            | 12 mA          | 12 mA                                                             | High      | 5 pF                 | -                              | 0.98  | 2.29 | 0.19             | 1.19 | 1.40 | 0.67  | 2.32 | 1.94 | 2.65 | 3.27            | ns    |

| 1.8 V LVCMOS                            | 8 mA           | 8 mA                                                              | High      | 5 pF                 | -                              | 0.98  | 2.45 | 0.19             | 1.12 | 1.61 | 0.67  | 2.48 | 2.16 | 2.71 | 3.16            | ns    |

| 1.5 V LVCMOS                            | 4 mA           | 4 mA                                                              | High      | 5 pF                 | -                              | 0.98  | 2.71 | 0.19             | 1.26 | 1.80 | 0.67  | 2.75 | 2.39 | 2.78 | 3.15            | ns    |

| 1.2 V LVCMOS                            | 2 mA           | 2 mA                                                              | High      | 5 pF                 | -                              | 0.98  | 3.38 | 0.19             | 1.57 | 2.34 | 0.67  | 3.26 | 2.78 | 2.99 | 3.24            | ns    |

| 1.2 V LVCMOS<br>Wide Range <sup>3</sup> | 100 µA         | 2 mA                                                              | High      | 5 pF                 | -                              | 0.98  | 3.38 | 0.19             | 1.57 | 2.34 | 0.67  | 3.26 | 2.78 | 2.99 | 3.24            | ns    |

# Table 2-26 • Summary of I/O Timing Characteristics—Software Default Settings, STD Speed GradeCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 3.0 V

Notes:

1. The minimum drive strength for any LVCMOS 3.3 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. All LVCMOS 3.3 V software macros support LVCMOS 3.3 V wide range as specified in the JESD-8B specification.

All LVCMOS 1.2 V software macros support LVCMOS 1.2 V wide range as specified in the JESD8-12 specification.

For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# Single-Ended I/O Characteristics

# 3.3 V LVTTL / 3.3 V LVCMOS

Low-Voltage Transistor–Transistor Logic (LVTTL) is a general-purpose standard (EIA/JESD) for 3.3 V applications. It uses an LVTTL input buffer and push-pull output buffer.

| 3.3 V LVTTL /<br>3.3 V LVCMOS | v         | IL        | v         | н         | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|-------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength             | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 2   | 2  | 25                      | 27                      | 10              | 10               |

| 4 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 4   | 4  | 25                      | 27                      | 10              | 10               |

| 6 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 6   | 6  | 51                      | 54                      | 10              | 10               |

| 8 mA                          | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 8   | 8  | 51                      | 54                      | 10              | 10               |

| 12 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 12  | 12 | 103                     | 109                     | 10              | 10               |

| 16 mA                         | -0.3      | 0.8       | 2         | 3.6       | 0.4       | 2.4       | 16  | 16 | 103                     | 109                     | 10              | 10               |

## Table 2-34 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

Test Point

$$rac{1}{1}$$

$rac{1}{1}$   $rac{1$

## Figure 2-7 • AC Loading

### Table 2-35 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 3.3            | 1.4                  | 5                      |

*Note:* \**Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.*

# 🌜 Microsemi.

IGLOO PLUS DC and Switching Characteristics

# 2.5 V LVCMOS

Low-Voltage CMOS for 2.5 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 2.5 V applications.

| 2.5 V<br>LVCMOS   | v         | 1L        | v         | н         | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL¹            | IIH <sup>2</sup> |

|-------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|-----------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup> | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 2   | 2  | 16                      | 18                      | 10              | 10               |

| 4 mA              | -0.3      | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 4   | 4  | 16                      | 18                      | 10              | 10               |

| 6 mA              | -0.3      | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 6   | 6  | 32                      | 37                      | 10              | 10               |

| 8 mA              | -0.3      | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 8   | 8  | 32                      | 37                      | 10              | 10               |

| 12 mA             | -0.3      | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 12  | 12 | 65                      | 74                      | 10              | 10               |

### Table 2-46 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

Test Point

$$rac{1}{4}$$

$rac{1}{4}$   $rac{1$

## Figure 2-8 • AC Loading

## Table 2-47 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 2.5            | 1.2                  | 5                      |

*Note:* \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

# static Microsemi.

IGLOO PLUS DC and Switching Characteristics

## Timing Characteristics

### Applies to 1.2 V DC Core Voltage

### Table 2-70 • 1.2 V LVCMOS Wide Range Low Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>J</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.14 V

| Drive<br>Strength | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>dout</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|-------------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 µA            | 2 mA                                                                          | STD            | 0.98              | 8.27            | 0.19             | 1.57            | 2.34             | 0.67              | 7.94            | 6.77            | 3.00            | 3.11            | ns    |

Notes:

The minimum drive strength for any LVCMOS 1.2 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### Table 2-71 • 1.2 V LVCMOS Wide Range High Slew – Applies to 1.2 V DC Core Voltage Commercial-Case Conditions: T<sub>1</sub> = 70°C, Worst-Case VCC = 1.14 V, Worst-Case VCCI = 1.14 V

| Drive<br>Strength | Equivalent<br>Software<br>Default<br>Drive<br>Strength<br>Option <sup>1</sup> | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>ZH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|-------------------------------------------------------------------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 100 µA            | 2 mA                                                                          | STD            | 0.98              | 3.38            | 0.19             | 1.57            | 2.34             | 0.67              | 3.26            | 2.78            | 2.99            | 3.24            | ns    |

Notes:

1. The minimum drive strength for any LVCMOS 1.2 V software configuration when run in wide range is ±100 μA. Drive strength displayed in the software is supported for normal range only. For a detailed I/V curve, refer to the IBIS models.

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

3. Software default selection highlighted in gray.

# **Output Register**

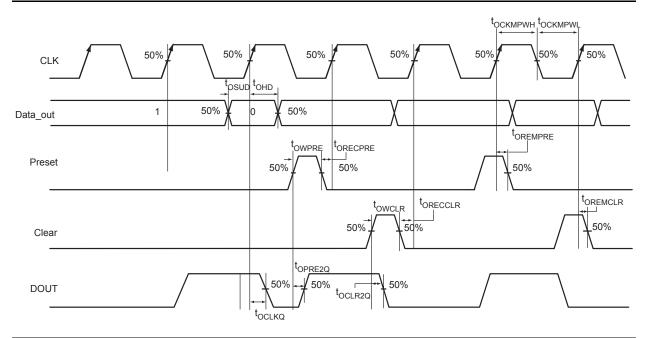

## Figure 2-15 • Output Register Timing Diagram

## **Timing Characteristics**

1.5 V DC Core Voltage

# Table 2-76 • Output Data Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                                                          | Std. | Units |

|----------------------|----------------------------------------------------------------------|------|-------|

| t <sub>oclkq</sub>   | Clock-to-Q of the Output Data Register                               | 0.66 | ns    |

| tosud                | Data Setup Time for the Output Data Register                         | 0.33 | ns    |

| t <sub>OHD</sub>     | Data Hold Time for the Output Data Register                          | 0.00 | ns    |

| t <sub>OCLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Data Register                  | 0.82 | ns    |

| t <sub>OPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Data Register                 | 0.88 | ns    |

| t <sub>OREMCLR</sub> | Asynchronous Clear Removal Time for the Output Data Register         | 0.00 | ns    |

| t <sub>ORECCLR</sub> | Asynchronous Clear Recovery Time for the Output Data Register        | 0.24 | ns    |

| t <sub>OREMPRE</sub> | Asynchronous Preset Removal Time for the Output Data Register        | 0.00 | ns    |

| t <sub>ORECPRE</sub> | Asynchronous Preset Recovery Time for the Output Data Register       | 0.24 | ns    |

| t <sub>OWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Data Register  | 0.19 | ns    |

| t <sub>OWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Data Register | 0.19 | ns    |

| t <sub>оскмрwн</sub> | Clock Minimum Pulse Width High for the Output Data Register          | 0.31 | ns    |

| t <sub>OCKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Data Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

# 🌜 Microsemi.

IGLOO PLUS DC and Switching Characteristics

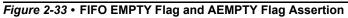

# Embedded SRAM and FIFO Characteristics

#### RAM4K9 **RAM512X18** RADDR8 **RD17** ADDRA11 DOUTA8 RADDR7 RD16 DOUTA7 ADDRA10 -٠ . . ٠ DOUTAO ADDRA0 RADDR0 RD0 DINA8 DINA7 . RW1 RW0 DINA0 WIDTHA1 WIDTHA0 PIPE PIPEA WMODEA BLKA d REN WENA O RCLK CLKA ADDRB11 DOUTB8 WADDR8 ADDRB10 DOUTB7 WADDR7 ٠ ٠ ADDRB0 DOUTBO WADDR0 WD17 WD16 DINB8 DINB7 • WD0 . DINB0 WW1 ŴŴŎ WIDTHB1 WIDTHB0 PIPEB WMODEB BLKB -d WEN WENB d **DWCLK CLKB** RESET RESET

# SRAM

Figure 2-23 • RAM Models

IGLOO PLUS DC and Switching Characteristics

Figure 2-32 • FIFO Reset

Pin Descriptions and Packaging

## VCOMPLA/B/C/D/E/F PLL Ground

Ground to analog PLL power supplies. When the PLLs are not used, the Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground.

There is one VCOMPLF pin on IGLOO PLUS devices.

### VJTAG JTAG Supply Voltage

Low power flash devices have a separate bank for the dedicated JTAG pins. The JTAG pins can be run at any voltage from 1.5 V to 3.3 V (nominal). Isolating the JTAG power supply in a separate I/O bank gives greater flexibility in supply selection and simplifies power supply and PCB design. If the JTAG interface is neither used nor planned for use, the VJTAG pin together with the TRST pin could be tied to GND. It should be noted that VCC is required to be powered for JTAG operation; VJTAG alone is insufficient. If a device is in a JTAG chain of interconnected boards, the board containing the device can be powered down, provided both VJTAG and VCC to the part remain powered; otherwise, JTAG signals will not be able to transition the device, even in bypass mode.

Microsemi recommends that VPUMP and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail.

### VPUMP Programming Supply Voltage

IGLOO PLUS devices support single-voltage ISP of the configuration flash and FlashROM. For programming, VPUMP should be 3.3 V nominal. During normal device operation, VPUMP can be left floating or can be tied (pulled up) to any voltage between 0 V and the VPUMP maximum. Programming power supply voltage (VPUMP) range is listed in the datasheet.

When the VPUMP pin is tied to ground, it will shut off the charge pump circuitry, resulting in no sources of oscillation from the charge pump circuitry.

For proper programming, 0.01  $\mu$ F and 0.33  $\mu$ F capacitors (both rated at 16 V) are to be connected in parallel across VPUMP and GND, and positioned as close to the FPGA pins as possible.

Microsemi recommends that VPUMP and VJTAG power supplies be kept separate with independent filtering capacitors rather than supplying them from a common rail.

# **User Pins**

## I/O

GL

### User Input/Output

The I/O pin functions as an input, output, tristate, or bidirectional buffer. Input and output signal levels are compatible with the I/O standard selected.

During programming, I/Os become tristated and weakly pulled up to VCCI. With VCCI, VMV, and VCC supplies continuously powered up, when the device transitions from programming to operating mode, the I/Os are instantly configured to the desired user configuration.

Unused I/Os are configured as follows:

- Output buffer is disabled (with tristate value of high impedance)

- Input buffer is disabled (with tristate value of high impedance)

- Weak pull-up is programmed

#### Globals

GL I/Os have access to certain clock conditioning circuitry (and the PLL) and/or have direct access to the global network (spines). Additionally, the global I/Os can be used as regular I/Os, since they have identical capabilities. Unused GL pins are configured as inputs with pull-up resistors.

See more detailed descriptions of global I/O connectivity in the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed Signal FPGAs" chapter of the *IGLOO PLUS FPGA Fabric User's Guide*. All inputs labeled GC/GF are direct inputs into the quadrant clocks. For example, if GAA0 is used for an input, GAA1 and GAA2 are no longer available for input to the quadrant globals. All inputs labeled GC/GF are direct inputs into the chip-level globals, and the rest are connected to the quadrant globals. The inputs to the global network are multiplexed, and only one input can be used as a global input.

Refer to the I/O Structure chapter of the IGLOO PLUS FPGA Fabric User's Guide for an explanation of the naming of global pins.

# **Special Function Pins**

## NC

## **No Connect**

This pin is not connected to circuitry within the device. These pins can be driven to any voltage or can be left floating with no effect on the operation of the device.

#### DC

### Do Not Connect

This pin should not be connected to any signals on the PCB. These pins should be left unconnected.

# Packaging

Semiconductor technology is constantly shrinking in size while growing in capability and functional integration. To enable next-generation silicon technologies, semiconductor packages have also evolved to provide improved performance and flexibility.

Microsemi consistently delivers packages that provide the necessary mechanical and environmental protection to ensure consistent reliability and performance. Microsemi IC packaging technology efficiently supports high-density FPGAs with large-pin-count Ball Grid Arrays (BGAs), but is also flexible enough to accommodate stringent form factor requirements for Chip Scale Packaging (CSP). In addition, Microsemi offers a variety of packages designed to meet your most demanding application and economic requirements for today's embedded and mobile systems.

# **Related Documents**

IGLOO PLUS Device Family User's Guide

http://www.microsemi.com/soc/documents/IGLOOPLUS\_UG.pdf

The following documents provide packaging information and device selection for low power flash devices.

# **Product Catalog**

### http://www.microsemi.com/soc/documents/ProdCat\_PIB.pdf

Lists devices currently recommended for new designs and the packages available for each member of the family. Use this document or the datasheet tables to determine the best package for your design, and which package drawing to use.

# Package Mechanical Drawings

#### http://www.microsemi.com/soc/documents/PckgMechDrwngs.pdf

This document contains the package mechanical drawings for all packages currently or previously supplied by Microsemi. Use the bookmarks to navigate to the package mechanical drawings.

Additional packaging materials are available at http://www.microsemi.com/soc/products/solutions/package/docs.aspx.

IGLOO PLUS Low Power Flash FPGAs

| V          | /Q176               | \<br>\     | /Q176               | V          | /Q176               |

|------------|---------------------|------------|---------------------|------------|---------------------|

| Pin Number | AGLP060<br>Function | Pin Number | AGLP060<br>Function | Pin Number | AGLP060<br>Function |

| 1          | GAA2/IO156RSB3      | 36         | IO119RSB3           | 70         | IO89RSB2            |

| 2          | IO155RSB3           | 37         | GND                 | 71         | IO88RSB2            |

| 3          | GAB2/IO154RSB3      | 38         | VCCIB3              | 72         | IO87RSB2            |

| 4          | IO153RSB3           | 39         | GEC1/IO116RSB3      | 73         | IO86RSB2            |

| 5          | GAC2/IO152RSB3      | 40         | GEB1/IO114RSB3      | 74         | IO85RSB2            |

| 6          | GND                 | 41         | GEC0/IO115RSB3      | 75         | IO84RSB2            |

| 7          | VCCIB3              | 42         | GEB0/IO113RSB3      | 76         | GND                 |

| 8          | IO149RSB3           | 43         | GEA1/IO112RSB3      | 77         | VCCIB2              |

| 9          | IO147RSB3           | 44         | GEA0/IO111RSB3      | 78         | IO83RSB2            |

| 10         | IO145RSB3           | 45         | GEA2/IO110RSB2      | 79         | IO82RSB2            |

| 11         | IO144RSB3           | 46         | NC                  | 80         | GDC2/IO80RSB2       |

| 12         | IO143RSB3           | 47         | FF/GEB2/IO109R      | 81         | IO81RSB2            |

| 13         | VCC                 |            | SB2                 | 82         | GDA2/IO78RSB2       |

| 14         | IO141RSB3           | 48         | GEC2/IO108RSB2      | 83         | GDB2/IO79RSB2       |

| 15         | GFC1/IO140RSB3      | 49         | IO106RSB2           | 84         | NC                  |

| 16         | GFB1/IO138RSB3      | 50         | IO107RSB2           | 85         | NC                  |

| 17         | GFB0/IO137RSB3      | 51         | IO104RSB2           | 86         | тск                 |

| 18         | VCOMPLF             | 52         | IO105RSB2           | 87         | TDI                 |

| 19         | GFA1/IO136RSB3      | 53         | IO102RSB2           | 88         | TMS                 |

| 20         | VCCPLF              | 54         | IO103RSB2           | 89         | VPUMP               |

| 21         | GFA0/IO135RSB3      | 55         | GND                 | 90         | TDO                 |

| 22         | GND                 | 56         | VCCIB2              | 91         | TRST                |

| 23         | VCCIB3              | 57         | IO101RSB2           | 92         | VJTAG               |

| 24         | GFA2/IO134RSB3      | 58         | IO100RSB2           | 93         | GDA1/IO76RSB1       |

| 25         | GFB2/IO133RSB3      | 59         | IO99RSB2            | 94         | GDC0/IO73RSB1       |

| 26         | GFC2/IO132RSB3      | 60         | IO98RSB2            | 95         | GDB1/IO74RSB1       |

| 27         | IO131RSB3           | 61         | IO97RSB2            | 96         | GDC1/IO72RSB1       |

| 28         | IO130RSB3           | 62         | IO96RSB2            | 97         | VCCIB1              |

| 29         | IO129RSB3           | 63         | IO95RSB2            | 98         | GND                 |

| 30         | IO127RSB3           | 64         | IO94RSB2            | 99         | IO70RSB1            |

| 31         | IO126RSB3           | 65         | IO93RSB2            | 100        | IO69RSB1            |

| 32         | IO125RSB3           | 66         | VCC                 | 101        | IO67RSB1            |

| 33         | IO123RSB3           | 67         | IO92RSB2            | 102        | IO66RSB1            |

| 34         | IO122RSB3           | 68         | IO91RSB2            | 103        | IO65RSB1            |

| 35         | IO121RSB3           | 69         | IO90RSB2            | 104        | IO63RSB1            |

IGLOO PLUS Low Power Flash FPGAs

|            | CS281            |            | CS281            |            | CS281            |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | AGLP125 Function | Pin Number | AGLP125 Function | Pin Number | AGLP125 Function |

| A1         | GND              | B18        | VCCIB1           | E13        | IO48RSB0         |

| A2         | GAB0/IO02RSB0    | B19        | IO64RSB1         | E14        | GBB1/IO60RSB0    |

| A3         | GAC1/IO05RSB0    | C1         | GAB2/IO209RSB3   | E15        | IO53RSB0         |

| A4         | IO09RSB0         | C2         | IO210RSB3        | E16        | IO69RSB1         |

| A5         | IO13RSB0         | C6         | IO12RSB0         | E18        | IO68RSB1         |

| A6         | IO15RSB0         | C14        | IO47RSB0         | E19        | IO71RSB1         |

| A7         | IO18RSB0         | C18        | IO54RSB0         | F1         | IO198RSB3        |

| A8         | IO23RSB0         | C19        | GBB2/IO65RSB1    | F2         | GND              |

| A9         | IO25RSB0         | D1         | IO206RSB3        | F3         | IO201RSB3        |

| A10        | VCCIB0           | D2         | IO208RSB3        | F4         | IO204RSB3        |

| A11        | IO33RSB0         | D4         | GAA0/IO00RSB0    | F5         | IO16RSB0         |

| A12        | IO41RSB0         | D5         | GAA1/IO01RSB0    | F15        | IO50RSB0         |

| A13        | IO43RSB0         | D6         | IO10RSB0         | F16        | IO74RSB1         |

| A14        | IO46RSB0         | D7         | IO17RSB0         | F17        | IO72RSB1         |

| A15        | IO55RSB0         | D8         | IO24RSB0         | F18        | GND              |

| A16        | IO56RSB0         | D9         | IO27RSB0         | F19        | IO73RSB1         |

| A17        | GBC1/IO58RSB0    | D10        | GND              | G1         | IO195RSB3        |

| A18        | GBA0/IO61RSB0    | D11        | IO31RSB0         | G2         | IO200RSB3        |

| A19        | GND              | D12        | IO40RSB0         | G4         | IO202RSB3        |

| B1         | GAA2/IO211RSB3   | D13        | IO49RSB0         | G5         | IO08RSB0         |

| B2         | VCCIB0           | D14        | IO45RSB0         | G7         | GAC2/IO207RSB3   |

| B3         | GAB1/IO03RSB0    | D15        | GBB0/IO59RSB0    | G8         | VCCIB0           |

| B4         | GAC0/IO04RSB0    | D16        | GBA2/IO63RSB1    | G9         | IO26RSB0         |

| B5         | IO11RSB0         | D18        | GBC2/IO67RSB1    | G10        | IO35RSB0         |

| B6         | GND              | D19        | IO66RSB1         | G11        | IO44RSB0         |

| B7         | IO21RSB0         | E1         | IO203RSB3        | G12        | VCCIB0           |

| B8         | IO22RSB0         | E2         | IO205RSB3        | G13        | IO51RSB0         |

| B9         | IO28RSB0         | E4         | IO07RSB0         | G15        | IO70RSB1         |

| B10        | IO32RSB0         | E5         | IO06RSB0         | G16        | IO75RSB1         |

| B11        | IO36RSB0         | E6         | IO14RSB0         | G18        | GCC0/IO80RSB1    |

| B12        | IO39RSB0         | E7         | IO20RSB0         | G19        | GCB1/IO81RSB1    |

| B13        | IO42RSB0         | E8         | IO29RSB0         | H1         | GFB0/IO191RSB3   |

| B14        | GND              | E9         | IO34RSB0         | H2         | IO196RSB3        |

| B15        | IO52RSB0         | E10        | IO30RSB0         | H4         | GFC1/IO194RSB3   |

| B16        | GBC0/IO57RSB0    | E11        | IO37RSB0         | H5         | GFB1/IO192RSB3   |

| B17        | GBA1/IO62RSB0    | E12        | IO38RSB0         | H7         | VCCIB3           |

| stati Microsemi.                 |

|----------------------------------|

| IGLOO PLUS Low Power Flash FPGAs |

|            | CS281            |            | CS281                 |

|------------|------------------|------------|-----------------------|

| Pin Number | AGLP125 Function | Pin Number | AGLP125 Function      |

| R15        | IO109RSB2        | V10        | IO133RSB2             |

| R16        | GDA1/IO103RSB1   | V11        | IO127RSB2             |

| R18        | GDB0/IO102RSB1   | V12        | IO123RSB2             |

| R19        | GDC0/IO100RSB1   | V13        | IO120RSB2             |

| T1         | IO171RSB3        | V14        | GND                   |

| T2         | GEC0/IO169RSB3   | V15        | IO113RSB2             |

| T4         | GEB0/IO167RSB3   | V16        | GDA2/IO105RSB2        |

| T5         | IO157RSB2        | V17        | TDI                   |

| Т6         | IO158RSB2        | V18        | VCCIB2                |

| Τ7         | IO148RSB2        | V19        | TDO                   |

| Т8         | IO145RSB2        | W1         | GND                   |

| Т9         | IO143RSB2        | W2         | FF/GEB2/IO163RSE<br>2 |

| T10        | GND              | W3         | IO155RSB2             |

| T11        | IO129RSB2        | W4         | IO152RSB2             |

| T12        | IO126RSB2        | W5         | IO150RSB2             |

| T13        | IO125RSB2        | W6         | IO147RSB2             |

| T14        | IO116RSB2        | W7         | IO142RSB2             |

| T15        | GDC2/IO107RSB2   | W8         | IO139RSB2             |

| T16        | TMS              | W9         | IO136RSB2             |

| T18        | VJTAG            | W10        | VCCIB2                |

| T19        | GDB1/IO101RSB1   | W11        | IO128RSB2             |

| U1         | IO160RSB2        | W12        | IO124RSB2             |

| U2         | GEA1/IO166RSB3   | W13        | IO119RSB2             |

| U6         | IO151RSB2        | W14        | IO115RSB2             |

| U14        | IO121RSB2        | W15        | IO114RSB2             |

| U18        | TRST             | W16        | IO110RSB2             |

| U19        | GDA0/IO104RSB1   | W17        | GDB2/IO106RSB2        |

| V1         | IO159RSB2        | W18        | ТСК                   |

| V2         | VCCIB3           | W19        | GND                   |

| V3         | GEC2/IO162RSB2   |            |                       |

| V4         | IO156RSB2        |            |                       |

| V5         | IO153RSB2        |            |                       |

| V6         | GND              |            |                       |

| V7         | IO144RSB2        |            |                       |

| V8         | IO141RSB2        |            |                       |

V9

IO140RSB2

Package Pin Assignments

|            | CS289               |            | CS289               | C          | S289                |

|------------|---------------------|------------|---------------------|------------|---------------------|

| Pin Number | AGLP030<br>Function | Pin Number | AGLP030<br>Function | Pin Number | AGLP030<br>Function |

| G10        | GND                 | J13        | IO43RSB1            | L16        | NC                  |

| G11        | GND                 | J14        | IO51RSB1            | L17        | NC                  |

| G12        | IO40RSB1            | J15        | IO52RSB1            | M1         | NC                  |

| G13        | NC                  | J16        | GDC0/IO46RSB1       | M2         | VCCIB3              |

| G14        | IO39RSB1            | J17        | GDA0/IO47RSB1       | M3         | IO100RSB3           |

| G15        | IO44RSB1            | K1         | GND                 | M4         | IO98RSB3            |

| G16        | NC                  | K2         | GEB0/IO106RSB3      | M5         | IO93RSB3            |

| G17        | GND                 | K3         | IO102RSB3           | M6         | IO97RSB3            |

| H1         | NC                  | K4         | IO104RSB3           | M7         | NC                  |

| H2         | GEC0/IO108RSB3      | K5         | IO99RSB3            | M8         | NC                  |

| H3         | NC                  | K6         | NC                  | M9         | IO71RSB2            |

| H4         | IO112RSB3           | K7         | GND                 | M10        | NC                  |

| H5         | NC                  | K8         | GND                 | M11        | IO63RSB2            |

| H6         | IO109RSB3           | К9         | GND                 | M12        | NC                  |

| H7         | GND                 | K10        | GND                 | M13        | IO57RSB1            |

| H8         | GND                 | K11        | GND                 | M14        | NC                  |

| H9         | GND                 | K12        | NC                  | M15        | NC                  |

| H10        | GND                 | K13        | NC                  | M16        | NC                  |

| H11        | GND                 | K14        | NC                  | M17        | VCCIB1              |

| H12        | NC                  | K15        | IO53RSB1            | N1         | NC                  |

| H13        | NC                  | K16        | GND                 | N2         | NC                  |

| H14        | IO45RSB1            | K17        | IO49RSB1            | N3         | IO95RSB3            |

| H15        | VCCIB1              | L1         | IO103RSB3           | N4         | IO96RSB3            |

| H16        | GDB0/IO48RSB1       | L2         | IO101RSB3           | N5         | GND                 |

| H17        | IO42RSB1            | L3         | NC                  | N6         | NC                  |

| J1         | NC                  | L4         | GND                 | N7         | IO85RSB2            |

| J2         | GEA0/IO107RSB3      | L5         | NC                  | N8         | IO79RSB2            |

| J3         | VCCIB3              | L6         | NC                  | N9         | IO77RSB2            |

| J4         | IO105RSB3           | L7         | GND                 | N10        | VCCIB2              |

| J5         | NC                  | L8         | GND                 | N11        | NC                  |

| J6         | NC                  | L9         | VCC                 | N12        | NC                  |

| J7         | VCC                 | L10        | GND                 | N13        | IO59RSB2            |

| J8         | GND                 | L11        | GND                 | N14        | NC                  |

| J9         | GND                 | L12        | IO58RSB1            | N15        | GND                 |

| J10        | GND                 | L13        | IO54RSB1            | N16        | IO56RSB1            |

| J11        | VCC                 | L14        | VCCIB1              | N17        | IO55RSB1            |

| J12        | IO50RSB1            | L15        | NC                  | P1         | IO94RSB3            |

| stati Microsemi.                 |

|----------------------------------|

| IGLOO PLUS Low Power Flash FPGAs |

| (          | CS289               | ) C        | CS289               |  |  |

|------------|---------------------|------------|---------------------|--|--|

| Pin Number | AGLP030<br>Function | Pin Number | AGLP030<br>Function |  |  |

| P2         | NC                  | T5         | NC                  |  |  |

| P3         | GND                 | Т6         | IO84RSB2            |  |  |

| P4         | NC                  | T7         | IO81RSB2            |  |  |

| P5         | NC                  | Т8         | IO76RSB2            |  |  |

| P6         | IO87RSB2            | Т9         | VCCIB2              |  |  |

| P7         | IO80RSB2            | T10        | IO69RSB2            |  |  |

| P8         | GND                 | T11        | IO65RSB2            |  |  |

| P9         | IO72RSB2            | T12        | IO64RSB2            |  |  |

| P10        | IO67RSB2            | T13        | NC                  |  |  |

| P11        | IO61RSB2            | T14        | GND                 |  |  |

| P12        | NC                  | T15        | NC                  |  |  |

| P13        | VCCIB2              | T16        | TDI                 |  |  |

| P14        | NC                  | T17        | TDO                 |  |  |

| P15        | IO60RSB2            | U1         | FF/IO90RSB2         |  |  |

| P16        | IO62RSB2            | U2         | GND                 |  |  |

| P17        | VJTAG               | U3         | NC                  |  |  |

| R1         | GND                 | U4         | IO88RSB2            |  |  |

| R2         | IO91RSB2            | U5         | IO86RSB2            |  |  |

| R3         | NC                  | U6         | IO82RSB2            |  |  |

| R4         | NC                  | U7         | GND                 |  |  |

| R5         | NC                  | U8         | IO75RSB2            |  |  |

| R6         | VCCIB2              | U9         | IO73RSB2            |  |  |

| R7         | IO83RSB2            | U10        | IO68RSB2            |  |  |

| R8         | IO78RSB2            | U11        | IO66RSB2            |  |  |

| R9         | IO74RSB2            | U12        | GND                 |  |  |

| R10        | IO70RSB2            | U13        | NC                  |  |  |

| R11        | GND                 | U14        | NC                  |  |  |

| R12        | NC                  | U15        | NC                  |  |  |

| R13        | NC                  | U16        | ТСК                 |  |  |

| R14        | NC                  | U17        | VPUMP               |  |  |

| R15        | NC                  | <u> </u>   |                     |  |  |

| R16        | TMS                 | 1          |                     |  |  |

| R17        | TRST                | 1          |                     |  |  |

| T1         | IO92RSB3            | 1          |                     |  |  |

| T2         | IO89RSB2            | 1          |                     |  |  |

| T3         | NC                  | 1          |                     |  |  |

|            |                     | 4          |                     |  |  |

T4

GND

Package Pin Assignments

| CS289      |                  | CS289      |                  | CS289      |                  |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | AGLP060 Function | Pin Number | AGLP060 Function | Pin Number | AGLP060 Function |

| A1         | GAB1/IO03RSB0    | C5         | VCCIB0           | E9         | IO22RSB0         |

| A2         | NC               | C6         | IO09RSB0         | E10        | IO26RSB0         |

| A3         | NC               | C7         | IO13RSB0         | E11        | VCCIB0           |

| A4         | GND              | C8         | IO15RSB0         | E12        | NC               |

| A5         | IO10RSB0         | C9         | IO21RSB0         | E13        | GBB1/IO33RSB0    |

| A6         | IO14RSB0         | C10        | GND              | E14        | GBA2/IO36RSB1    |

| A7         | IO16RSB0         | C11        | IO29RSB0         | E15        | GBB2/IO38RSB1    |

| A8         | IO18RSB0         | C12        | NC               | E16        | VCCIB1           |

| A9         | GND              | C13        | NC               | E17        | IO44RSB1         |

| A10        | IO23RSB0         | C14        | NC               | F1         | GFC1/IO140RSB3   |

| A11        | IO27RSB0         | C15        | GND              | F2         | IO142RSB3        |

| A12        | NC               | C16        | GBA0/IO34RSB0    | F3         | IO149RSB3        |

| A13        | NC               | C17        | IO39RSB1         | F4         | VCCIB3           |

| A14        | GND              | D1         | IO150RSB3        | F5         | GAB2/IO154RSB3   |

| A15        | NC               | D2         | IO151RSB3        | F6         | IO153RSB3        |

| A16        | NC               | D3         | GND              | F7         | NC               |

| A17        | GBC0/IO30RSB0    | D4         | GAB0/IO02RSB0    | F8         | IO08RSB0         |

| B1         | GAA1/IO01RSB0    | D5         | NC               | F9         | IO12RSB0         |

| B2         | GND              | D6         | NC               | F10        | NC               |

| B3         | NC               | D7         | NC               | F11        | NC               |

| B4         | NC               | D8         | GND              | F12        | NC               |

| B5         | IO07RSB0         | D9         | IO20RSB0         | F13        | GBC2/IO40RSB1    |

| B6         | NC               | D10        | IO25RSB0         | F14        | GND              |

| B7         | VCCIB0           | D11        | NC               | F15        | IO43RSB1         |

| B8         | IO17RSB0         | D12        | NC               | F16        | IO46RSB1         |

| B9         | IO19RSB0         | D13        | GND              | F17        | IO45RSB1         |

| B10        | IO24RSB0         | D14        | GBB0/IO32RSB0    | G1         | GFC0/IO139RSB3   |

| B11        | IO28RSB0         | D15        | GBA1/IO35RSB0    | G2         | GND              |

| B12        | VCCIB0           | D16        | IO37RSB1         | G3         | IO144RSB3        |

| B13        | NC               | D17        | IO42RSB1         | G4         | IO145RSB3        |

| B14        | NC               | E1         | VCCIB3           | G5         | IO146RSB3        |

| B15        | NC               | E2         | IO147RSB3        | G6         | IO148RSB3        |

| B16        | GBC1/IO31RSB0    | E3         | GAC2/IO152RSB3   | G7         | GND              |

| B17        | GND              | E4         | GAA2/IO156RSB3   | G8         | GND              |

| C1         | IO155RSB3        | E5         | GAC1/IO05RSB0    | G9         | VCC              |

| C2         | GAA0/IO00RSB0    | E6         | NC               | G10        | GND              |

| C3         | GAC0/IO04RSB0    | E7         | IO06RSB0         | G11        | GND              |

| C4         | NC               | E8         | IO11RSB0         | G12        | IO48RSB1         |