Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                                      |

|--------------------------------|-----------------------------------------------------------------------------|

| Number of LABs/CLBs            | -                                                                           |

| Number of Logic Elements/Cells | 1584                                                                        |

| Total RAM Bits                 | 18432                                                                       |

| Number of I/O                  | 137                                                                         |

| Number of Gates                | 60000                                                                       |

| Voltage - Supply               | 1.425V ~ 1.575V                                                             |

| Mounting Type                  | Surface Mount                                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                                          |

| Package / Case                 | 176-TQFP                                                                    |

| Supplier Device Package        | 176-VQFP (20x20)                                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/aglp060v5-vqg176i |

|                                |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1 – IGLOO PLUS Device Family Overview

### **General Description**

The IGLOO PLUS family of flash FPGAs, based on a 130 nm flash process, offers the lowest power FPGA, a single-chip solution, small-footprint packages, reprogrammability, and an abundance of advanced features.

The Flash\*Freeze technology used in IGLOO PLUS devices enables entering and exiting an ultra-low power mode that consumes as little as 5  $\mu$ W while retaining the design information, SRAM content, registers, and I/O states. Flash\*Freeze technology simplifies power management through I/O and clock management with rapid recovery to operation mode.

The Low Power Active capability (static idle) allows for ultra-low power consumption while the IGLOO PLUS device is completely functional in the system. This allows the IGLOO PLUS device to control system power management based on external inputs (e.g., scanning for keyboard stimulus) while consuming minimal power.

Nonvolatile flash technology gives IGLOO PLUS devices the advantage of being a secure, low power, single-chip solution that is Instant On. IGLOO PLUS is reprogrammable and offers time-to-market benefits at an ASIC-level unit cost.

These features enable designers to create high-density systems using existing ASIC or FPGA design flows and tools.

IGLOO PLUS devices offer 1 kbit of on-chip, reprogrammable, nonvolatile FlashROM storage as well as clock conditioning circuitry based on an integrated phase-locked loop (PLL). IGLOO PLUS devices have up to 125 k system gates, supported with up to 36 kbits of true dual-port SRAM and up to 212 user I/Os. The AGLP030 devices have no PLL or RAM support.

### Flash\*Freeze Technology

The IGLOO PLUS device offers unique Flash\*Freeze technology, allowing the device to enter and exit ultra-low power Flash\*Freeze mode. IGLOO PLUS devices do not need additional components to turn off I/Os or clocks while retaining the design information, SRAM content, registers, and I/O states. Flash\*Freeze technology is combined with in-system programmability, which enables users to quickly and easily upgrade and update their designs in the final stages of manufacturing or in the field. The ability of IGLOO PLUS V2 devices to support a wide range of core and I/O voltages (1.2 V to 1.5 V) allows further reduction in power consumption, thus achieving the lowest total system power.

During Flash\*Freeze mode, each I/O can be set to the following configurations: hold previous state, tristate, or set as HIGH or LOW.

The availability of low power modes, combined with reprogrammability, a single-chip and single-voltage solution, and availability of small-footprint, high-pin-count packages, make IGLOO PLUS devices the best fit for portable electronics.

### Flash Advantages

### Low Power

IGLOO PLUS devices exhibit power characteristics similar to those of an ASIC, making them an ideal choice for power-sensitive applications. IGLOO PLUS devices have only a very limited power-on current surge and no high-current transition period, both of which occur on many FPGAs.

IGLOO PLUS devices also have low dynamic power consumption to further maximize power savings; power is even further reduced by the use of a 1.2 V core voltage.

Low dynamic power consumption, combined with low static power consumption and Flash\*Freeze technology, gives the IGLOO PLUS device the lowest total system power offered by any FPGA.

### VersaTiles

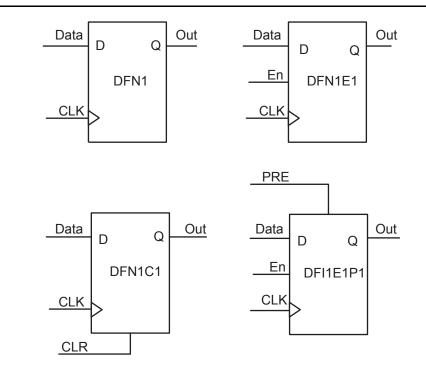

The IGLOO PLUS core consists of VersaTiles, which have been enhanced beyond the ProASIC<sup>PLUS®</sup> core tiles. The IGLOO PLUS VersaTile supports the following:

- All 3-input logic functions—LUT-3 equivalent

- Latch with clear or set

- D-flip-flop with clear or set

- Enable D-flip-flop with clear or set

Refer to Figure 1-3 for VersaTile configurations.

### Figure 1-3 • VersaTile Configurations

### User Nonvolatile FlashROM

IGLOO PLUS devices have 1 kbit of on-chip, user-accessible, nonvolatile FlashROM. The FlashROM can be used in diverse system applications:

- Internet protocol addressing (wireless or fixed)

- System calibration settings

- · Device serialization and/or inventory control

- Subscription-based business models (for example, set-top boxes)

- · Secure key storage for secure communications algorithms

- Asset management/tracking

- Date stamping

- Version management

The FlashROM is written using the standard IGLOO PLUS IEEE 1532 JTAG programming interface. The core can be individually programmed (erased and written), and on-chip AES decryption can be used selectively to securely load data over public networks (except in AGLP030 devices), as in security keys stored in the FlashROM for a user design.

The FlashROM can be programmed via the JTAG programming interface, and its contents can be read back either through the JTAG programming interface or via direct FPGA core addressing. Note that the FlashROM can only be programmed from the JTAG interface and cannot be programmed from the internal logic array.

The FlashROM is programmed as 8 banks of 128 bits; however, reading is performed on a byte-by-byte basis using a synchronous interface. A 7-bit address from the FPGA core defines which of the 8 banks and which of the 16 bytes within that bank are being read. The three most significant bits (MSBs) of the FlashROM address determine the bank, and the four least significant bits (LSBs) of the FlashROM address define the byte.

The IGLOO PLUS development software solutions, Libero<sup>®</sup> System-on-Chip (SoC) and Designer, have extensive support for the FlashROM. One such feature is auto-generation of sequential programming files for applications requiring a unique serial number in each part. Another feature allows the inclusion of static data for system version control. Data for the FlashROM can be generated quickly and easily using Libero SoC and Designer software tools. Comprehensive programming file support is also included to allow for easy programming of large numbers of parts with differing FlashROM contents.

### Combinatorial Cells Contribution—P<sub>C-CELL</sub>

$P_{C-CELL} = N_{C-CELL} * \alpha_1 / 2 * PAC7 * F_{CLK}$

N<sub>C-CELL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_{1}$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-19 on page 2-14.

$\mathsf{F}_{\mathsf{CLK}}$  is the global clock signal frequency.

### Routing Net Contribution—P<sub>NET</sub>

$P_{NET} = (N_{S-CELL} + N_{C-CELL}) * \alpha_1 / 2 * PAC8 * F_{CLK}$

$N_{S\text{-}CELL}$  is the number of VersaTiles used as sequential modules in the design.

N<sub>C-CELL</sub> is the number of VersaTiles used as combinatorial modules in the design.

$\alpha_{1}$  is the toggle rate of VersaTile outputs—guidelines are provided in Table 2-19 on page 2-14.

$\mathsf{F}_{\mathsf{CLK}}$  is the global clock signal frequency.

### I/O Input Buffer Contribution—PINPUTS

$P_{INPUTS} = N_{INPUTS} * \alpha_2 / 2 * P_{AC9} * F_{CLK}$

N<sub>INPUTS</sub> is the number of I/O input buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-19 on page 2-14.

$F_{CLK}$  is the global clock signal frequency.

### I/O Output Buffer Contribution—POUTPUTS

$P_{OUTPUTS} = N_{OUTPUTS} * \alpha_2 / 2 * \beta_1 * PAC10 * F_{CLK}$

N<sub>OUTPUTS</sub> is the number of I/O output buffers used in the design.

$\alpha_2$  is the I/O buffer toggle rate—guidelines are provided in Table 2-19 on page 2-14.

$\beta_1$  is the I/O buffer enable rate—guidelines are provided in Table 2-20 on page 2-14.

F<sub>CLK</sub> is the global clock signal frequency.

### RAM Contribution—P<sub>MEMORY</sub>

$\mathsf{P}_{\mathsf{MEMORY}} = \mathsf{P}_{\mathsf{AC11}} * \mathsf{N}_{\mathsf{BLOCKS}} * \mathsf{F}_{\mathsf{READ-CLOCK}} * \beta_2 + \mathsf{PAC12} * \mathsf{N}_{\mathsf{BLOCK}} * \mathsf{F}_{\mathsf{WRITE-CLOCK}} * \beta_3$

N<sub>BLOCKS</sub> is the number of RAM blocks used in the design.

$\mathsf{F}_{\mathsf{READ-CLOCK}}$  is the memory read clock frequency.

$\beta_2$  is the RAM enable rate for read operations.

F<sub>WRITE-CLOCK</sub> is the memory write clock frequency.

$\beta_3$  is the RAM enable rate for write operations—guidelines are provided in Table 2-20 on page 2-14.

### PLL Contribution—PPLL

$P_{PLL} = PDC4 + PAC1_3 * F_{CLKOUT}$

F<sub>CLKOUT</sub> is the output clock frequency.<sup>1</sup>

### Guidelines

#### **Toggle Rate Definition**

A toggle rate defines the frequency of a net or logic element relative to a clock. It is a percentage. If the toggle rate of a net is 100%, this means that this net switches at half the clock frequency. Below are some examples:

- The average toggle rate of a shift register is 100% because all flip-flop outputs toggle at half of the clock frequency.

- The average toggle rate of an 8-bit counter is 25%:

If a PLL is used to generate more than one output clock, include each output clock in the formula by adding its corresponding contribution (P<sub>AC13</sub>\* F<sub>CLKOUT</sub> product) to the total PLL contribution.

- Bit 0 (LSB) = 100%

- Bit 1 = 50%

- Bit 2 = 25%

- ...

- Bit 7 (MSB) = 0.78125%

- Average toggle rate = (100% + 50% + 25% + 12.5% + . . . + 0.78125%) / 8

### Enable Rate Definition

Output enable rate is the average percentage of time during which tristate outputs are enabled. When nontristate output buffers are used, the enable rate should be 100%.

| Component      | Definition                       | Guideline |

|----------------|----------------------------------|-----------|

| $\alpha_1$     | Toggle rate of VersaTile outputs | 10%       |

| α <sub>2</sub> | I/O buffer toggle rate           | 10%       |

### Table 2-20 • Enable Rate Guidelines Recommended for Power Calculation

| Component      | Definition                           | Guideline |

|----------------|--------------------------------------|-----------|

| β <sub>1</sub> | I/O output buffer enable rate        | 100%      |

| β <sub>2</sub> | RAM enable rate for read operations  | 12.5%     |

| β <sub>3</sub> | RAM enable rate for write operations | 12.5%     |

| Parameter         | Parameter Definition                                                        |

|-------------------|-----------------------------------------------------------------------------|

| t <sub>DP</sub>   | Data to Pad delay through the Output Buffer                                 |

| t <sub>PY</sub>   | Pad to Data delay through the Input Buffer                                  |

| t <sub>DOUT</sub> | Data to Output Buffer delay through the I/O interface                       |

| t <sub>EOUT</sub> | Enable to Output Buffer Tristate Control delay through the I/O interface    |

| t <sub>DIN</sub>  | Input Buffer to Data delay through the I/O interface                        |

| t <sub>HZ</sub>   | Enable to Pad delay through the Output Buffer—High to Z                     |

| t <sub>ZH</sub>   | Enable to Pad delay through the Output Buffer—Z to High                     |

| t <sub>LZ</sub>   | Enable to Pad delay through the Output Buffer—Low to Z                      |

| t <sub>ZL</sub>   | Enable to Pad delay through the Output Buffer—Z to Low                      |

| t <sub>ZHS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to High |

| t <sub>ZLS</sub>  | Enable to Pad delay through the Output Buffer with delayed enable—Z to Low  |

### Table 2-24 • I/O AC Parameter Definitions

### 🌜 Microsemi.

IGLOO PLUS DC and Switching Characteristics

### 2.5 V LVCMOS

Low-Voltage CMOS for 2.5 V is an extension of the LVCMOS standard (JESD8-5) used for general-purpose 2.5 V applications.

| 2.5 V<br>LVCMOS   | v         | 1L        | v         | н         | VOL       | VOH       | IOL | ЮН | IOSL                    | IOSH                    | IIL <sup>1</sup> | IIH <sup>2</sup> |

|-------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----|----|-------------------------|-------------------------|------------------|------------------|

| Drive<br>Strength | Min.<br>V | Max.<br>V | Min.<br>V | Max.<br>V | Max.<br>V | Min.<br>V | mA  | mA | Max.<br>mA <sup>3</sup> | Max.<br>mA <sup>3</sup> | μA <sup>4</sup>  | μA <sup>4</sup>  |

| 2 mA              | -0.3      | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 2   | 2  | 16                      | 18                      | 10               | 10               |

| 4 mA              | -0.3      | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 4   | 4  | 16                      | 18                      | 10               | 10               |

| 6 mA              | -0.3      | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 6   | 6  | 32                      | 37                      | 10               | 10               |

| 8 mA              | -0.3      | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 8   | 8  | 32                      | 37                      | 10               | 10               |

| 12 mA             | -0.3      | 0.7       | 1.7       | 3.6       | 0.7       | 1.7       | 12  | 12 | 65                      | 74                      | 10               | 10               |

### Table 2-46 • Minimum and Maximum DC Input and Output Levels

Notes:

1. IIL is the input leakage current per I/O pin over recommended operation conditions where –0.3 V < VIN < VIL.

2. IIH is the input leakage current per I/O pin over recommended operating conditions VIH < VIN < VCCI. Input current is larger when operating outside recommended ranges.

3. Currents are measured at high temperature (100°C junction temperature) and maximum voltage.

4. Currents are measured at 85°C junction temperature.

5. Software default selection highlighted in gray.

Test Point

$$rac{1}{4}$$

$rac{1}{4}$   $rac{1$

### Figure 2-8 • AC Loading

### Table 2-47 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | C <sub>LOAD</sub> (pF) |

|---------------|----------------|----------------------|------------------------|

| 0             | 2.5            | 1.2                  | 5                      |

*Note:* \*Measuring point = Vtrip. See Table 2-23 on page 2-20 for a complete table of trip points.

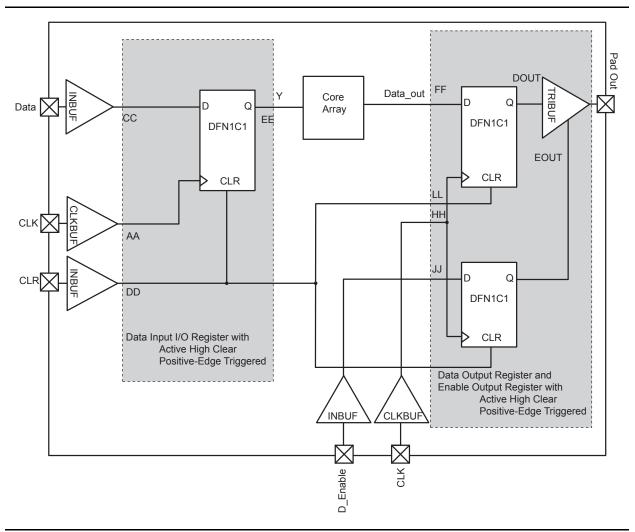

Figure 2-13 • Timing Model of the Registered I/O Buffers with Asynchronous Clear

## 🔨 Microsemi

IGLOO PLUS DC and Switching Characteristics

### 1.2 V DC Core Voltage

## Table 2-75 • Input Data Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.14 V

| Parameter            | Description                                                         | Std. | Units |

|----------------------|---------------------------------------------------------------------|------|-------|

| t <sub>ICLKQ</sub>   | Clock-to-Q of the Input Data Register                               | 0.66 | ns    |

| t <sub>ISUD</sub>    | Data Setup Time for the Input Data Register                         | 0.43 | ns    |

| t <sub>IHD</sub>     | Data Hold Time for the Input Data Register                          | 0.00 | ns    |

| t <sub>ICLR2Q</sub>  | Asynchronous Clear-to-Q of the Input Data Register                  | 0.86 | ns    |

| t <sub>IPRE2Q</sub>  | Asynchronous Preset-to-Q of the Input Data Register                 | 0.86 | ns    |

| t <sub>IREMCLR</sub> | Asynchronous Clear Removal Time for the Input Data Register         | 0.00 | ns    |

| t <sub>IRECCLR</sub> | Asynchronous Clear Recovery Time for the Input Data Register        | 0.24 | ns    |

| t <sub>IREMPRE</sub> | Asynchronous Preset Removal Time for the Input Data Register        | 0.00 | ns    |

| t <sub>IRECPRE</sub> | Asynchronous Preset Recovery Time for the Input Data Register       | 0.24 | ns    |

| t <sub>IWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Input Data Register  | 0.19 | ns    |

| t <sub>IWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Input Data Register | 0.19 | ns    |

| t <sub>ICKMPWH</sub> | Clock Minimum Pulse Width High for the Input Data Register          | 0.31 | ns    |

| t <sub>ICKMPWL</sub> | Clock Minimum Pulse Width Low for the Input Data Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

### Output Enable Register

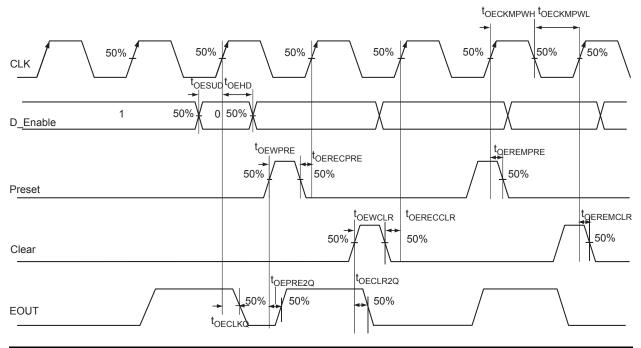

### Figure 2-16 • Output Enable Register Timing Diagram

### **Timing Characteristics**

### 1.5 V DC Core Voltage

## Table 2-78 • Output Enable Register Propagation DelaysCommercial-Case Conditions: TJ = 70°C, Worst-Case VCC = 1.425 V

| Parameter             | Description                                                            | Std. | Units |

|-----------------------|------------------------------------------------------------------------|------|-------|

| t <sub>OECLKQ</sub>   | Clock-to-Q of the Output Enable Register                               | 0.68 | ns    |

| tOESUD                | Data Setup Time for the Output Enable Register                         | 0.33 | ns    |

| t <sub>OEHD</sub>     | Data Hold Time for the Output Enable Register                          | 0.00 | ns    |

| t <sub>OECLR2Q</sub>  | Asynchronous Clear-to-Q of the Output Enable Register                  | 0.84 | ns    |

| t <sub>OEPRE2Q</sub>  | Asynchronous Preset-to-Q of the Output Enable Register                 | 0.91 | ns    |

| t <sub>OEREMCLR</sub> | Asynchronous Clear Removal Time for the Output Enable Register         | 0.00 | ns    |

| t <sub>OERECCLR</sub> | Asynchronous Clear Recovery Time for the Output Enable Register        | 0.24 | ns    |

| t <sub>OEREMPRE</sub> | Asynchronous Preset Removal Time for the Output Enable Register        | 0.00 | ns    |

| t <sub>OERECPRE</sub> | Asynchronous Preset Recovery Time for the Output Enable Register       | 0.24 | ns    |

| t <sub>OEWCLR</sub>   | Asynchronous Clear Minimum Pulse Width for the Output Enable Register  | 0.19 | ns    |

| t <sub>OEWPRE</sub>   | Asynchronous Preset Minimum Pulse Width for the Output Enable Register | 0.19 | ns    |

| t <sub>ОЕСКМРWH</sub> | Clock Minimum Pulse Width High for the Output Enable Register          | 0.31 | ns    |

| t <sub>OECKMPWL</sub> | Clock Minimum Pulse Width Low for the Output Enable Register           | 0.28 | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### VersaTile Specifications as a Sequential Module

The IGLOO PLUS library offers a wide variety of sequential cells, including flip-flops and latches. Each has a data input and optional enable, clear, or preset. In this section, timing characteristics are presented for a representative sample from the library. For more details, refer to the *Fusion, IGLOO/e, and ProASIC3/E Macro Library Guide*.

Figure 2-19 • Sample of Sequential Cells

### **Global Tree Timing Characteristics**

Global clock delays include the central rib delay, the spine delay, and the row delay. Delays do not include I/O input buffer clock delays, as these are I/O standard–dependent, and the clock may be driven and conditioned internally by the CCC module. For more details on clock conditioning capabilities, refer to the "Clock Conditioning Circuits" section on page 2-61. Table 2-84 to Table 2-89 on page 2-60 present minimum and maximum global clock delays within each device. Minimum and maximum delays are measured with minimum and maximum loading.

### **Timing Characteristics**

1.5 V DC Core Voltage

### Table 2-84 • AGLP030 Global Resource

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.425 V

|                      |                                           |   | St                | td.               |       |

|----------------------|-------------------------------------------|---|-------------------|-------------------|-------|

| Parameter            | Description                               | Γ | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          |   | 1.21              | 1.42              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         |   | 1.23              | 1.49              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |   | 1.18              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |   | 1.15              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |   |                   | 0.27              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

#### Table 2-85 • AGLP060 Global Resource Commercial-Case Conditions: T<sub>1</sub> = 70°C, VCC = 1.425 V

|                      |                                           |  | St                |                   |       |

|----------------------|-------------------------------------------|--|-------------------|-------------------|-------|

| Parameter            | Description                               |  | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          |  | 1.32              | 1.62              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         |  | 1.34              | 1.72              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock |  | 1.18              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  |  | 1.15              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |  |                   | 0.38              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 for derating values.

### Table 2-88 • AGLP060 Global Resource Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | St                | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.02              | 2.43              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.09              | 2.65              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.56              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

### Table 2-89 • AGLP125 Global Resource

### Commercial-Case Conditions: T<sub>J</sub> = 70°C, VCC = 1.14 V

|                      |                                           | Si                | Std.              |       |

|----------------------|-------------------------------------------|-------------------|-------------------|-------|

| Parameter            | Description                               | Min. <sup>1</sup> | Max. <sup>2</sup> | Units |

| t <sub>RCKL</sub>    | Input Low Delay for Global Clock          | 2.08              | 2.54              | ns    |

| t <sub>RCKH</sub>    | Input High Delay for Global Clock         | 2.15              | 2.77              | ns    |

| t <sub>RCKMPWH</sub> | Minimum Pulse Width High for Global Clock | 1.40              |                   | ns    |

| t <sub>RCKMPWL</sub> | Minimum Pulse Width Low for Global Clock  | 1.65              |                   | ns    |

| t <sub>RCKSW</sub>   | Maximum Skew for Global Clock             |                   | 0.62              | ns    |

Notes:

1. Value reflects minimum load. The delay is measured from the CCC output to the clock pin of a sequential element, located in a lightly loaded row (single element is connected to the global net).

2. Value reflects maximum load. The delay is measured on the clock pin of the farthest sequential element, located in a fully loaded row (all available flip-flops are connected to the global net in the row).

3. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-6 for derating values.

## static Microsemi.

IGLOO PLUS DC and Switching Characteristics

## Table 2-91 • IGLOO PLUS CCC/PLL Specification For IGLOO PLUS V2 Devices, 1.2 V DC Core Supply Voltage

| Parameter                                                               | Min.                                             | Тур.                | Max.                | Units                |

|-------------------------------------------------------------------------|--------------------------------------------------|---------------------|---------------------|----------------------|

| Clock Conditioning Circuitry Input Frequency fIN_CCC                    | 1.5                                              |                     | 160                 | MHz                  |

| Clock Conditioning Circuitry Output Frequency f <sub>OUT_CCC</sub>      | 0.75                                             |                     | 160                 | MHz                  |

| Delay Increments in Programmable Delay Blocks <sup>1, 2</sup>           |                                                  | 580 <sup>3</sup>    |                     | ps                   |

| Number of Programmable Values in Each Programmable Delay Block          |                                                  |                     | 32                  |                      |

| Serial Clock (SCLK) for Dynamic PLL <sup>4,5</sup>                      |                                                  |                     | 60                  | MHz                  |

| Input Cycle-to-Cycle Jitter (peak magnitude)                            |                                                  |                     | .25                 | ns                   |

| Acquisition Time                                                        |                                                  |                     |                     |                      |

| LockControl = 0                                                         |                                                  |                     | 300                 | μs                   |

| LockControl = 1                                                         |                                                  |                     | 6.0                 | ms                   |

| Tracking Jitter <sup>6</sup>                                            |                                                  |                     |                     |                      |

| LockControl = 0                                                         |                                                  |                     | 4                   | ns                   |

| LockControl = 1                                                         |                                                  |                     | 3                   | ns                   |

| Output Duty Cycle                                                       | 48.5                                             |                     | 51.5                | %                    |

| Delay Range in Block: Programmable Delay 1 <sup>1, 2</sup>              | 2.3                                              |                     | 20.86               | ns                   |

| Delay Range in Block: Programmable Delay 2 <sup>1, 2</sup>              | 0.863                                            |                     | 20.86               | ns                   |

| Delay Range in Block: Fixed Delay <sup>1, 2</sup>                       |                                                  | 5.7                 |                     | ns                   |

| VCO Output Peak-to-Peak Period Jitter F <sub>CCC_OUT</sub> <sup>7</sup> | Maximum Peak-to-Peak Period Jitter <sup>7,</sup> |                     |                     |                      |

|                                                                         | $SSO \le 2$                                      | $\text{SSO} \leq 4$ | $\text{SSO} \leq 8$ | $\text{SSO} \leq 16$ |

| 0.75 MHz to 50 MHz                                                      | 0.50%                                            | 1.20%               | 2.00%               | 3.00%                |

| 50 MHz to 160 MHz                                                       | 2.50%                                            | 5.00%               | 7.00%               | 15.00%               |

Notes:

1. This delay is a function of voltage and temperature. See Table 2-6 on page 2-6 and Table 2-7 on page 2-6 for deratings.

2.  $T_J = 25^{\circ}C$ , VCC = 1.2 V

- 3. When the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available. Refer to the online help associated with the core for more information.

- 4. Maximum value obtained for a STD speed grade device in Worst Case Commercial Conditions.For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-6 and Table 2-7 on page 2-6 for derating values.

5. The AGLP030 device does not support PLL.

- 6. Tracking jitter is defined as the variation in clock edge position of PLL outputs with reference to PLL input clock edge. Tracking jitter does not measure the variation in PLL output period, which is covered by period jitter parameter.

- 7. VCO output jitter is calculated as a percentage of the VCO frequency. The jitter (in ps) can be calculated by multiplying the VCO period by the per cent jitter. The VCO jitter (in ps) applies to CCC\_OUT regardless of the output divider settings. For example, if the jitter on VCO is 300 ps, the jitter on CCC\_OUT is also 300 ps, regardless of the output divider settings.

- 8. Measurements are done with LVTTL 3.3 V, 8 mA, I/O drive strength and high slew rate. VCC/VCCPLL = 1.14 V, VCCI = 3.3 V, VQ/PQ/TQ type of packages, 20 pF load.

- 9. SSO are outputs that are synchronous to a single clock domain, and have their clock-to-out times within ±200 ps of each other. Switching I/Os are placed outside of the PLL bank. Refer to the "Simultaneously Switching Outputs (SSOs) and Printed Circuit Board Layout" section in the IGLOO PLUS FPGA Fabric User's Guide

## 🌜 Microsemi.

IGLOO PLUS DC and Switching Characteristics

## Embedded SRAM and FIFO Characteristics

#### RAM4K9 **RAM512X18** RADDR8 **RD17** ADDRA11 DOUTA8 RADDR7 RD16 DOUTA7 ADDRA10 -٠ . . ٠ DOUTAO ADDRA0 RADDR0 RD0 DINA8 DINA7 . RW1 RW0 DINA0 WIDTHA1 WIDTHA0 PIPE PIPEA WMODEA BLKA d REN WENA O RCLK CLKA ADDRB11 DOUTB8 WADDR8 ADDRB10 DOUTB7 WADDR7 ٠ ٠ ADDRB0 DOUTBO WADDR0 WD17 WD16 DINB8 DINB7 • WD0 . DINB0 WW1 ŴŴŎ WIDTHB1 WIDTHB0 PIPEB WMODEB BLKB -d WEN WENB d **DWCLK CLKB** RESET RESET

### SRAM

Figure 2-23 • RAM Models

## 3 – Pin Descriptions and Packaging

## **Supply Pins**

### GND

### Ground

Ground supply voltage to the core, I/O outputs, and I/O logic.

### GNDQ Ground (quiet)

Quiet ground supply voltage to input buffers of I/O banks. Within the package, the GNDQ plane is decoupled from the simultaneous switching noise originated from the output buffer ground domain. This minimizes the noise transfer within the package and improves input signal integrity. GNDQ must always be connected to GND on the board.

#### VCC

#### **Core Supply Voltage**

Supply voltage to the FPGA core, nominally 1.5 V for IGLOO PLUS V5 devices, and 1.2 V or 1.5 V for IGLOO PLUS V2 devices. VCC is required for powering the JTAG state machine in addition to VJTAG. Even when a device is in bypass mode in a JTAG chain of interconnected devices, both VCC and VJTAG must remain powered to allow JTAG signals to pass through the device.

For IGLOO PLUS V2 devices, VCC can be switched dynamically from 1.2 V to 1.5 V or vice versa. This allows in-system programming (ISP) when VCC is at 1.5 V and the benefit of low power operation when VCC is at 1.2 V.

#### VCCIBx

### I/O Supply Voltage

Supply voltage to the bank's I/O output buffers and I/O logic. Bx is the I/O bank number. There are four I/O banks on low power flash devices plus a dedicated VJTAG bank. Each bank can have a separate VCCI connection. All I/Os in a bank will run off the same VCCIBx supply. VCCI can be 1.2 V, 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VCCI pins tied to GND.

### VMVx I/O Supply Voltage (quiet)

Quiet supply voltage to the input buffers of each I/O bank. *x* is the bank number. Within the package, the VMV plane biases the input stage of the I/Os in the I/O banks. This minimizes the noise transfer within the package and improves input signal integrity. Each bank must have at least one VMV connection, and no VMV should be left unconnected. All I/Os in a bank run off the same VMVx supply. VMV is used to provide a quiet supply voltage to the input buffers of each I/O bank. VMVx can be 1.2 V, 1.5 V, 1.8 V, 2.5 V, or 3.3 V, nominal voltage. Unused I/O banks should have their corresponding VMV pins tied to GND. VMV and VCCI should be at the same voltage within a given I/O bank. Used VMV pins must be connected to the corresponding VCCI pins of the same bank (i.e., VMV0 to VCCIB0, VMV1 to VCCIB1, etc.).

### VCCPLA/B/C/D/E/F PLL Supply Voltage

Supply voltage to analog PLL, nominally 1.5 V or 1.2 V, depending on the device.

- 1.5 V for IGLOO PLUS V5 devices

- 1.2 V or 1.5 V for IGLOO PLUS V2 devices

When the PLLs are not used, the Microsemi Designer place-and-route tool automatically disables the unused PLLs to lower power consumption. The user should tie unused VCCPLx and VCOMPLx pins to ground. Microsemi recommends tying VCCPLx to VCC and using proper filtering circuits to decouple VCC noise from the PLLs. Refer to the PLL Power Supply Decoupling section of the "Clock Conditioning Circuits in Low Power Flash Devices and Mixed signal FPGAs " chapter of the *IGLOO PLUS FPGA Fabric User's Guide* for a complete board solution for the PLL analog power supply and ground.

There is one VCCPLF pin on IGLOO PLUS devices.

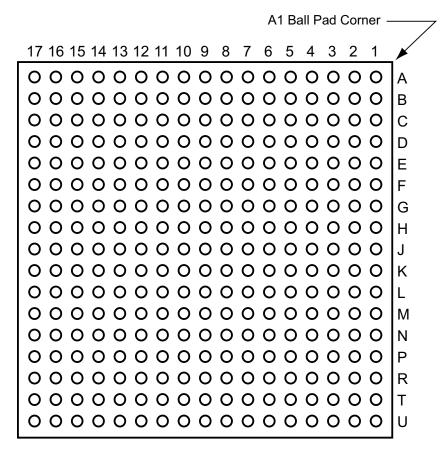

### **CS289**

*Note:* This is the bottom view of the package.

### Note

For Package Manufacturing and Environmental information, visit the Resource Center at http://www.microsemi.com/soc/products/solutions/package/docs.aspx .

Package Pin Assignments

| CS289      |                     | CS289      |                     | CS289      |                     |  |

|------------|---------------------|------------|---------------------|------------|---------------------|--|

| Pin Number | AGLP030<br>Function | Pin Number | AGLP030<br>Function | Pin Number | AGLP030<br>Function |  |

| G10        | GND                 | J13        | IO43RSB1            | L16        | NC                  |  |

| G11        | GND                 | J14        | IO51RSB1            | L17        | NC                  |  |

| G12        | IO40RSB1            | J15        | IO52RSB1            | M1         | NC                  |  |

| G13        | NC                  | J16        | GDC0/IO46RSB1       | M2         | VCCIB3              |  |

| G14        | IO39RSB1            | J17        | GDA0/IO47RSB1       | M3         | IO100RSB3           |  |

| G15        | IO44RSB1            | K1         | GND                 | M4         | IO98RSB3            |  |

| G16        | NC                  | K2         | GEB0/IO106RSB3      | M5         | IO93RSB3            |  |

| G17        | GND                 | K3         | IO102RSB3           | M6         | IO97RSB3            |  |

| H1         | NC                  | K4         | IO104RSB3           | M7         | NC                  |  |

| H2         | GEC0/IO108RSB3      | K5         | IO99RSB3            | M8         | NC                  |  |

| H3         | NC                  | K6         | NC                  | M9         | IO71RSB2            |  |

| H4         | IO112RSB3           | K7         | GND                 | M10        | NC                  |  |

| H5         | NC                  | K8         | GND                 | M11        | IO63RSB2            |  |

| H6         | IO109RSB3           | К9         | GND                 | M12        | NC                  |  |

| H7         | GND                 | K10        | GND                 | M13        | IO57RSB1            |  |

| H8         | GND                 | K11        | GND                 | M14        | NC                  |  |

| H9         | GND                 | K12        | NC                  | M15        | NC                  |  |

| H10        | GND                 | K13        | NC                  | M16        | NC                  |  |

| H11        | GND                 | K14        | NC                  | M17        | VCCIB1              |  |

| H12        | NC                  | K15        | IO53RSB1            | N1         | NC                  |  |

| H13        | NC                  | K16        | GND                 | N2         | NC                  |  |

| H14        | IO45RSB1            | K17        | IO49RSB1            | N3         | IO95RSB3            |  |

| H15        | VCCIB1              | L1         | IO103RSB3           | N4         | IO96RSB3            |  |

| H16        | GDB0/IO48RSB1       | L2         | IO101RSB3           | N5         | GND                 |  |

| H17        | IO42RSB1            | L3         | NC                  | N6         | NC                  |  |

| J1         | NC                  | L4         | GND                 | N7         | IO85RSB2            |  |

| J2         | GEA0/IO107RSB3      | L5         | NC                  | N8         | IO79RSB2            |  |

| J3         | VCCIB3              | L6         | NC                  | N9         | IO77RSB2            |  |

| J4         | IO105RSB3           | L7         | GND                 | N10        | VCCIB2              |  |

| J5         | NC                  | L8         | GND                 | N11        | NC                  |  |

| J6         | NC                  | L9         | VCC                 | N12        | NC                  |  |

| J7         | VCC                 | L10        | GND                 | N13        | IO59RSB2            |  |

| J8         | GND                 | L11        | GND                 | N14        | NC                  |  |

| J9         | GND                 | L12        | IO58RSB1            | N15        | GND                 |  |

| J10        | GND                 | L13        | IO54RSB1            | N16        | IO56RSB1            |  |

| J11        | VCC                 | L14        | VCCIB1              | N17        | IO55RSB1            |  |

| J12        | IO50RSB1            | L15        | NC                  | P1         | IO94RSB3            |  |

IGLOO PLUS Low Power Flash FPGAs

|            | CS289            | CS289      |                  | CS289      |                  |

|------------|------------------|------------|------------------|------------|------------------|

| Pin Number | AGLP060 Function | Pin Number | AGLP060 Function | Pin Number | AGLP060 Function |

| G13        | IO41RSB1         | J17        | GCA1/IO56RSB1    | M4         | IO122RSB3        |

| G14        | IO47RSB1         | K1         | GND              | M5         | GEB0/IO113RSB3   |

| G15        | IO49RSB1         | K2         | GFA0/IO135RSB3   | M6         | GEB1/IO114RSB3   |

| G16        | IO50RSB1         | K3         | GFB2/IO133RSB3   | M7         | NC               |

| G17        | GND              | K4         | IO128RSB3        | M8         | NC               |

| H1         | VCOMPLF          | K5         | IO123RSB3        | M9         | IO90RSB2         |

| H2         | GFB0/IO137RSB3   | K6         | IO125RSB3        | M10        | NC               |

| H3         | NC               | K7         | GND              | M11        | IO83RSB2         |

| H4         | IO141RSB3        | K8         | GND              | M12        | NC               |

| H5         | IO143RSB3        | K9         | GND              | M13        | GDA1/IO76RSB1    |

| H6         | GFB1/IO138RSB3   | K10        | GND              | M14        | GDA0/IO77RSB1    |

| H7         | GND              | K11        | GND              | M15        | IO71RSB1         |

| H8         | GND              | K12        | IO64RSB1         | M16        | IO69RSB1         |

| H9         | GND              | K13        | IO61RSB1         | M17        | VCCIB1           |

| H10        | GND              | K14        | IO66RSB1         | N1         | IO119RSB3        |

| H11        | GND              | K15        | IO65RSB1         | N2         | IO120RSB3        |

| H12        | GCC1/IO52RSB1    | K16        | GND              | N3         | GEC0/IO115RSB3   |

| H13        | IO51RSB1         | K17        | GCC2/IO60RSB1    | N4         | GEA0/IO111RSB3   |

| H14        | GCA0/IO57RSB1    | L1         | GFA2/IO134RSB3   | N5         | GND              |

| H15        | VCCIB1           | L2         | GFC2/IO132RSB3   | N6         | NC               |

| H16        | GCA2/IO58RSB1    | L3         | IO127RSB3        | N7         | IO104RSB2        |

| H17        | GCC0/IO53RSB1    | L4         | GND              | N8         | IO98RSB2         |

| J1         | VCCPLF           | L5         | IO121RSB3        | N9         | IO96RSB2         |

| J2         | GFA1/IO136RSB3   | L6         | GEC1/IO116RSB3   | N10        | VCCIB2           |

| J3         | VCCIB3           | L7         | GND              | N11        | NC               |

| J4         | IO131RSB3        | L8         | GND              | N12        | NC               |

| J5         | IO130RSB3        | L9         | VCC              | N13        | GDB2/IO79RSB2    |

| J6         | IO129RSB3        | L10        | GND              | N14        | NC               |

| J7         | VCC              | L11        | GND              | N15        | GND              |

| J8         | GND              | L12        | GDC1/IO72RSB1    | N16        | GDB0/IO75RSB1    |

| J9         | GND              | L13        | GDB1/IO74RSB1    | N17        | GDC0/IO73RSB1    |

| J10        | GND              | L14        | VCCIB1           | P1         | IO118RSB3        |

| J11        | VCC              | L15        | IO70RSB1         | P2         | IO117RSB3        |

| J12        | GCB2/IO59RSB1    | L16        | IO68RSB1         | P3         | GND              |

| J13        | GCB1/IO54RSB1    | L17        | IO67RSB1         | P4         | NC               |

| J14        | IO62RSB1         | M1         | IO126RSB3        | P5         | NC               |

| J15        | IO63RSB1         | M2         | VCCIB3           | P6         | IO106RSB2        |

| J16        | GCB0/IO55RSB1    | M3         | IO124RSB3        | P7         | IO99RSB2         |

# IGLOO PLUS Low Power Flash FPGAs

| Revision                   | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Page                   |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Revision 12<br>(continued) | The reference to guidelines for global spines and VersaTile rows, given in the "Global Clock Contribution—P <sub>CLOCK</sub> " section, was corrected to the "Spine Architecture" section of the Global Resources chapter in the <i>IGLOO PLUS FPGA Fabric User's Guide</i> (SAR 34733).                                                                                                                                                                                                                    | 2-12                   |

|                            | $t_{\text{DOUT}}$ was corrected to $t_{\text{DIN}}$ in Figure 2-4 $\bullet$ Input Buffer Timing Model and Delays (example) (SAR 37107).                                                                                                                                                                                                                                                                                                                                                                     | 2-16                   |

|                            | The AC Loading figures in the "Single-Ended I/O Characteristics" section were updated to match tables in the "Summary of I/O Timing Characteristics – Default I/O Software Settings" section (SAR 34887).                                                                                                                                                                                                                                                                                                   | 2-27                   |

|                            | Minimum pulse width High and Low values were added to the tables in the "Global Tree Timing Characteristics" section. The maximum frequency for global clock parameter was removed from these tables because a frequency on the global is only an indication of what the global network can do. There are other limiters such as the SRAM, I/Os, and PLL. SmartTime software should be used to determine the design frequency (SAR 36963).                                                                  | 2-58                   |

|                            | Table 2-90 • IGLOO PLUS CCC/PLL Specification and Table 2-91 • IGLOO PLUS CCC/PLL Specification were updated. A note was added to both tables indicating that when the CCC/PLL core is generated by Microsemi core generator software, not all delay values of the specified delay increments are available (SAR 34820).                                                                                                                                                                                    | 2-61,<br>2-62          |

|                            | The value for serial clock was missing from these tables and has been restored. The value and units for input cycle-to-cycle jitter were incorrect and have been restored. The note to Table 2-90 • IGLOO PLUS CCC/PLL Specification giving specifications for which measurements done was corrected from VCC/VCCPLL = 1.14 V to VCC/VCCPLL = 1.425 V. The Delay Range in Block: Programmable Delay 2 value in Table 2-91 • IGLOO PLUS CCC/PLL Specification was corrected from 0.025 to 0.863 (SAR 37058). |                        |

|                            | Figure 2-28 • Write Access after Read onto Same Address was deleted. Reference was made to a new application note, <i>Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs</i> , which covers these cases in detail (SAR 34868).                                                                                                                                                                                                                                            | 2-65,                  |

|                            | The port names in the SRAM "Timing Waveforms", SRAM "Timing Characteristics" tables, Figure 2-32 • FIFO Reset, and the FIFO "Timing Characteristics" tables were revised to ensure consistency with the software names (SAR 35748).                                                                                                                                                                                                                                                                         | 2-68,<br>2-74,<br>2-76 |

|                            | The "Pin Descriptions and Packaging" chapter has been added (SAR 34769).                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3-1                    |

|                            | Package names used in the "Package Pin Assignments" section were revised to match standards given in <i>Package Mechanical Drawings</i> (SAR 34769).                                                                                                                                                                                                                                                                                                                                                        | 4-1                    |

| Revision 11<br>(July 2010) | The versioning system for datasheets has been changed. Datasheets are assigned a revision number that increments each time the datasheet is revised. The "IGLOO PLUS Device Status" table indicates the status for each device in the family.                                                                                                                                                                                                                                                               | N/A                    |

|                            | The "Reprogrammable Flash Technology" section was revised to add "250 MHz (1.5 V systems) and 160 MHz (1.2 V systems) System Performance."                                                                                                                                                                                                                                                                                                                                                                  | I                      |

|                            | The "I/Os with Advanced I/O Standards" section was revised to add definitions for hot-swap and cold-sparing.                                                                                                                                                                                                                                                                                                                                                                                                | 1-6                    |

|                            | Conditional statements regarding hot insertion were removed from the description of VI in Table 2-1 • Absolute Maximum Ratings, since all IGLOO PLUS devices are hot insertion enabled.                                                                                                                                                                                                                                                                                                                     | 2-1                    |

#### Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996

#### E-mail: sales.support@microsemi.com

© 2015 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,600 employees globally. Learn more at **www.microsemi.com**.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.