Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                       |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 48MHz                                                                                 |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, MMC/SD, QSPI, SCI, SPI, UART/USART, USB      |

| Peripherals                | DMA, LCD, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 102                                                                                   |

| Program Memory Size        | 1MB (1M x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | 16K × 8                                                                               |

| RAM Size                   | 192К х 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                           |

| Data Converters            | A/D 26x14b; D/A 2x12b                                                                 |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 121-LFBGA                                                                             |

| Supplier Device Package    | 121-LFBGA (8x8)                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r7fs3a77c2a01cbj-ac1 |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1. Overview

The S3A7 MCU comprises multiple series of software- and pin-compatible ARM-based 32-bit MCUs that share a common set of Renesas peripherals to facilitate design scalability and efficient platform-based product development.

This MCU provides an optimal combination of low-power, high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core running up to 48 MHz with the following features:

- Up to 1-MB code flash memory

- 192-KB SRAM

- Segment LCD Controller (SLCDC)

- Capacitive Touch Sensing Unit (CTSU)

- USB 2.0 Full-Speed Module (USBFS)

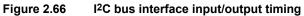

- 14-bit ADC

- 12-bit DAC

- Security features.

## 1.1 Function Outline

#### Table 1.1 ARM core

| Feature       | Functional description                                                           |

|---------------|----------------------------------------------------------------------------------|

| ARM Cortex-M4 | Maximum operating frequency: up to 48 MHz                                        |

|               | ARM Cortex-M4:                                                                   |

|               | - Revision: r0p1-01rel0                                                          |

|               | - ARMv7E-M architecture profile                                                  |

|               | - Single Precision Floating Point Unit compliant with the ANSI/IEEE Std 754-2008 |

|               | ARM Memory Protection Unit (MPU):                                                |

|               | - ARMv7 Protected Memory System Architecture                                     |

|               | - 8 protect regions                                                              |

|               | SysTick timer:                                                                   |

|               | - Driven by LOCO clock                                                           |

#### Table 1.2 Memory

| Feature                      | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Code flash memory            | Maximum 1 MB code flash memory. See section 48, Flash Memory in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Data flash memory            | 16 KB data flash memory. See section 48, Flash Memory in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Option-Setting Memory        | The Option-Setting Memory determines the state of the MCU after a reset.<br>See section 7, Option-Setting Memory in User's Manual.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Memory Mirror Function (MMF) | The MMF can be configured to mirror the desired application image load address in code flash memory to the application image link address in the unused memory 23-bit space (memory mirror space addresses). The user application code is developed and linked to run from this MMF destination address. The user application code does not need to know the load location where it is stored in code flash memory. See section 5, Memory Mirror Function (MMF) in User's Manual. |  |  |  |  |  |  |

| SRAM                         | This MCU has an on-chip high-speed SRAM with either parity-bit or Error Correction Code (ECC). There is an area in SRAM0 that provides error correction capability using ECC. See section 47, SRAM in User's Manual.                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Feature                           | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Watchdog Timer (WDT)              | The Watchdog Timer (WDT) is a 14-bit down-counter. It can be used to reset this MCU when the counter underflows because the system has run out of control and is unable to refresh the WDT. In addition, a non-maskable interrupt or interrupt can be generated by an underflow. The refresh-permitted period can be set to refresh the counter and used as the condition to detect when the system runs out of control. See section 26, Watchdog Timer (WDT) in User's Manual.                                                                                                                                                                                                               |  |  |  |  |  |

| Independent Watchdog Timer (IWDT) | The independent watchdog timer (IWDT) consists of a 14-bit down-counter that must be serviced periodically to prevent counter underflow. The IWDT provides functionality to reset this MCU or to generate a non-maskable interrupt/interrupt for a timer underflow. Because the timer operates using an independent, dedicated clock source, it is particularly useful in returning this MCU to a known state as a fail safe mechanism when the system runs out of control. The watchdog timer can be triggered automatically on reset, underflow, or refresh error, or by a refresh of the count value in the registers. See section 27, Independent Watchdog Timer (IWDT) in User's Manual. |  |  |  |  |  |

#### Table 1.3 System (2/2)

### Table 1.4 Interrupt control

| Feature                         | Functional description                                                                                                                                                                                                      |  |  |  |  |  |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Interrupt Controller Unit (ICU) | The Interrupt Controller Unit (ICU) controls which event signals are linked to the NVIC/DTC module and DMAC module. The ICU also controls NMI interrupts. See section 14, Interrupt Controller Unit (ICU) in User's Manual. |  |  |  |  |  |  |

#### Table 1.5 Event link

| Feature                     | Functional description                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Event Link Controller (ELC) | The Event Link Controller (ELC) uses the interrupt requests generated by various peripheral modules as event signals to connect them to different modules, enabling direct interaction between the modules without CPU intervention. See section 19, Event Link Controller (ELC) in User's Manual. |  |  |  |  |  |

### Table 1.6 Direct memory access

| Feature                        | Functional description                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Data Transfer Controller (DTC) | This MCU incorporates a Data Transfer Controller (DTC) that performs data transfers when activated by an interrupt request. See section 18, Data Transfer Controller (DTC) in User's Manual.                                                                                                                 |  |  |  |  |  |

| DMA Controller (DMAC)          | This MCU incorporates an 4-channel DMA Controller (DMAC) module that can transfer data without the CPU. When a DMA transfer request is generated, the DMAC transfers data stored at the transfer source address to the transfer destination address. See section 17, DMA Controller (DMAC) in User's Manual. |  |  |  |  |  |

#### Table 1.7 External bus interface

| Feature      | Functional description                                                                                                                                           |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External bus | <ul> <li>CS area: Connected to the external devices (external memory interface)</li> <li>QSPI area: Connected to the QSPI (external device interface)</li> </ul> |

#### Table 1.8 Timers

| Feature                                     | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| General PWM Timer (GPT)                     | The General PWM Timer (GPT) is a 32-bit timer with 10 channels. PWM waveforms can be generated by controlling the up-counter, down-counter, or the up- and down-counter. In addition, PWM waveforms for controlling brushless DC motors can be generated. The GPT can also be used as a general-purpose timer. See section 23, General PWM Timer (GPT) in User's Manual.                                                                                                                                                            |  |  |  |  |  |  |

| Port Output Enable for GPT (POEG)           | Use the Port Output Enable for GPT (POEG) function to place the General PWM Timer (GPT) output pins in the output disable state. See section 22, Port Output Enable for GPT (POEG) in User's Manual.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| Asynchronous General Purpose<br>Timer (AGT) | The Asynchronous General Purpose Timer (AGT) is a 16-bit timer that can be used for pulse output, external pulse width or period measurement, and counting external events. This 16-bit timer consists of a reload register and a down-counter. The reload register and the down-counter are allocated to the same address, and they can be accessed with the AGT register. See section 24, Asynchronous General Purpose Timer (AGT) in User's Manual.                                                                              |  |  |  |  |  |  |

| Realtime Clock (RTC)                        | The Realtime Clock (RTC) has two counting modes, calendar count mode and binary count<br>mode, that are used by switching register settings.<br>For calendar count mode, the RTC has a 100-year calendar from 2000 to 2099 and<br>automatically adjusts dates for leap years.<br>For binary count mode, the RTC counts seconds and retains the information as a serial value.<br>Binary count mode can be used for calendars other than the Gregorian (Western) calendar.<br>See section 25, Realtime Clock (RTC) in User's Manual. |  |  |  |  |  |  |

### Table 1.9 Communication interfaces (1/2)

| Feature                                  | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Serial Communications Interface<br>(SCI) | <ul> <li>The Serial Communication Interface (SCI) is configurable to five asynchronous and synchronous serial interfaces:</li> <li>Asynchronous interfaces (UART and asynchronous communications interface adapter (ACIA))</li> <li>8-bit clock synchronous interface</li> <li>Simple IIC (master-only)</li> <li>Simple SPI</li> <li>Smart card interface.</li> <li>The smart card interface complies with the ISO/IEC 7816-3 standard for electronic signals and transmission protocol.</li> <li>Each SCI has FIFO buffers to enable continuous and full-duplex communication, and the data transfer speed can be configured independently using an on-chip baud rate generator. See section 29, Serial Communications Interface (SCI) in User's Manual.</li> </ul> |  |  |  |  |  |  |

| IrDA Interface (IrDA)                    | The IrDA interface sends and receives IrDA data communication waveforms in cooperation with the SCI1 based on the IrDA (Infrared Data Association) standard 1.0. See section 30, IrDA Interface in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| I <sup>2</sup> C Bus Interface (IIC)     | This MCU has a three-channel I <sup>2</sup> C bus interface (IIC).<br>The IIC module conforms with and provides a subset of the NXP I <sup>2</sup> C bus (Inter-Integrated Circuit bus) interface functions. See section 31, I <sup>2</sup> C Bus Interface (IIC) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Serial Peripheral Interface (SPI)        | This MCU includes two independent channels of the Serial Peripheral Interface (SPI). The SPI channels are capable of high-speed, full-duplex synchronous serial communications with multiple processors and peripheral devices. See section 33, Serial Peripheral Interface (SPI) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Serial Sound Interface (SSI)             | The Serial Sound Interface (SSI) peripheral provides functionality to interface digital audio devices for transmitting PCM audio data over a serial bus with this MCU. The SSI supports an audio clock frequency of up to 50 MHz, and can be operated as a slave or master receiver/ transmitter/transceiver to suit various applications. The SSI includes 8-stage FIFO buffers in the receiver and transmitter, and supports interrupts and DMA-driven data reception and transmission. See section 36, Serial Sound Interface (SSI) in User's Manual.                                                                                                                                                                                                             |  |  |  |  |  |  |

| Quad Serial Peripheral Interface (QSPI)  | The QSPI is a memory controller for connecting a serial ROM (nonvolatile memory such as a serial flash memory, serial EEPROM, or serial FeRAM) that has an SPI-compatible interface. See section 34, Quad Serial Peripheral Interface (QSPI) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

RENESAS

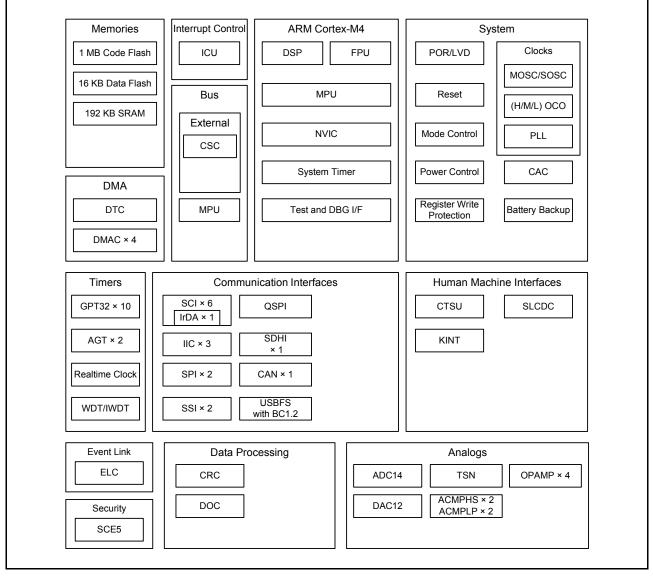

## 1.2 Block Diagram

Figure 1.1 shows the block diagram of this MCU superset. Individual devices within the group may have a subset of the features.

Figure 1.1 Block diagram

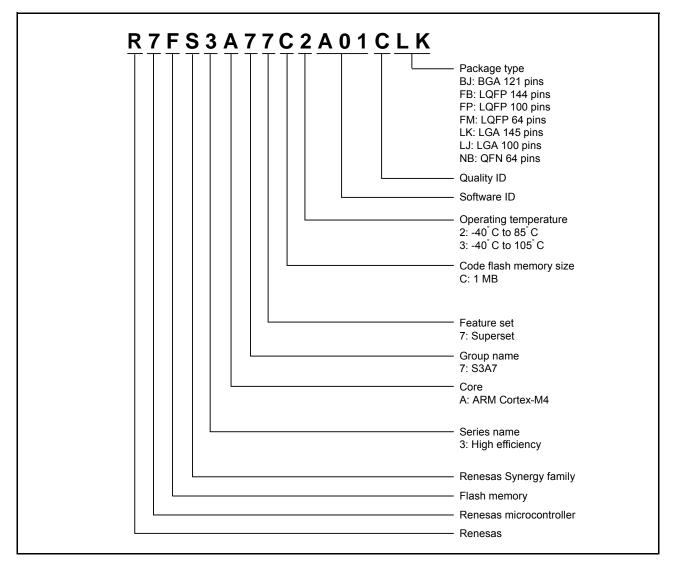

# 1.3 Part Numbering

Figure 1.2 Part numbering scheme

| Function                                              | Signal                        | I/O    | Description                                                                                                                                                                                                       |  |  |  |  |  |  |

|-------------------------------------------------------|-------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| SPI                                                   | RSPCKA, RSPCKB                | I/O    | Clock input/output pin.                                                                                                                                                                                           |  |  |  |  |  |  |

|                                                       | MOSIA, MOSIB                  | I/O    | Inputs or outputs data output from the master.                                                                                                                                                                    |  |  |  |  |  |  |

|                                                       | MISOA, MISOB                  | I/O    | Inputs or outputs data output from the slave.                                                                                                                                                                     |  |  |  |  |  |  |

|                                                       | SSLA0, SSLB0                  | I/O    | Input or output pin for slave selection.                                                                                                                                                                          |  |  |  |  |  |  |

|                                                       | SSLA1, SSLA2,                 | Output | Output pin for slave selection.                                                                                                                                                                                   |  |  |  |  |  |  |

|                                                       | SSLA3, SSLB1,<br>SSLB2, SSLB3 |        |                                                                                                                                                                                                                   |  |  |  |  |  |  |

| QSPI                                                  | QSPCLK                        | Output | QSPI clock output pin.                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                       | QSSL                          | Output | QSPI slave output pin.                                                                                                                                                                                            |  |  |  |  |  |  |

|                                                       | QIO0                          | I/O    | Master transmit data/data 0.                                                                                                                                                                                      |  |  |  |  |  |  |

|                                                       | QIO1                          | 1/0    | Master input data/data 1.                                                                                                                                                                                         |  |  |  |  |  |  |

|                                                       | QIO2, QIO3                    | 1/0    | Data 2, Data 3.                                                                                                                                                                                                   |  |  |  |  |  |  |

| CAN                                                   | CRX0                          | Input  | Receive data.                                                                                                                                                                                                     |  |  |  |  |  |  |

| 0AN                                                   | CTX0                          | Output | Transmit data.                                                                                                                                                                                                    |  |  |  |  |  |  |

| USBFS                                                 | VSS_USB                       | Input  | Ground pins.                                                                                                                                                                                                      |  |  |  |  |  |  |

|                                                       | VCC_USB_LDO                   | Input  | Power supply pin for USB LDO regulator.                                                                                                                                                                           |  |  |  |  |  |  |

|                                                       | VCC_USB                       | I/O    | Input: Power supply pin for USB transceiver.                                                                                                                                                                      |  |  |  |  |  |  |

|                                                       | 100_000                       | 1/0    | Output: USB LDO regulator output pin. This pin should be connected to an external capacitor.                                                                                                                      |  |  |  |  |  |  |

|                                                       | USB_DP                        | I/O    | D+ I/O pin of the USB on-chip transceiver. This pin should be connected to the D+ pin of the USB bus.                                                                                                             |  |  |  |  |  |  |

|                                                       | USB_DM                        | I/O    | D– I/O pin of the USB on-chip transceiver. This pin should be connected to the D– pin of the USB bus.                                                                                                             |  |  |  |  |  |  |

|                                                       | USB_VBUS                      | Input  | USB cable connection monitor pin. This pin should be connected to VBUS of the USB bus. The VBUS pin status (connected or disconnected) can be detected when the USB module is operating as a function controller. |  |  |  |  |  |  |

|                                                       | USB_EXICEN                    | Output | Low-power control signal for external power supply (OTG) chip                                                                                                                                                     |  |  |  |  |  |  |

|                                                       | USB_VBUSEN                    | Output | VBUS (5 V) supply enable signal for external power supply (616) clip                                                                                                                                              |  |  |  |  |  |  |

|                                                       | USB_OVRCURA,                  | Input  | External overcurrent detection signals should be connected to these pins                                                                                                                                          |  |  |  |  |  |  |

|                                                       | USB_OVRCURB                   | mput   | VBUS comparator signals should be connected to these pins.<br>OTG power supply chip is connected.                                                                                                                 |  |  |  |  |  |  |

|                                                       | USB_ID                        | Input  | MicroAB connector ID input signal should be connected to this pin during operation in OTG mode.                                                                                                                   |  |  |  |  |  |  |

| SDHI                                                  | SD0CLK                        | Output | SD clock output pin.                                                                                                                                                                                              |  |  |  |  |  |  |

|                                                       | SD0CMD                        | I/O    | SD command output, response input signal pin.                                                                                                                                                                     |  |  |  |  |  |  |

|                                                       | SD0DAT0 to<br>SD0DAT7         | I/O    | SD data bus pins.                                                                                                                                                                                                 |  |  |  |  |  |  |

|                                                       | SD0WP                         | Input  | SD write-protect signal.                                                                                                                                                                                          |  |  |  |  |  |  |

| Analog power                                          | AVCC0                         | Input  | Analog voltage supply pin for the analog. Connect this pin to VCC.                                                                                                                                                |  |  |  |  |  |  |

| supply                                                | AVSS0                         | Input  | Analog ground pin. Connect this pin to VSS.                                                                                                                                                                       |  |  |  |  |  |  |

|                                                       | VREFH0                        | Input  | Analog reference voltage supply pin for the A/D converter. Connect this pin to VCC when not using the A/D converter.                                                                                              |  |  |  |  |  |  |

|                                                       | VREFL0                        | Input  | Analog reference ground pin for the A/D converter. Connect this pin to VSS when not using the A/D converter.                                                                                                      |  |  |  |  |  |  |

|                                                       | VREFH                         | Input  | Analog reference voltage supply pin for D/A converter.                                                                                                                                                            |  |  |  |  |  |  |

|                                                       | VREFL                         | Input  | Analog reference ground pin for D/A converter.                                                                                                                                                                    |  |  |  |  |  |  |

| ADC14                                                 | AN000 to AN027                | Input  | Input pins for the analog signals to be processed by the A/D converter.                                                                                                                                           |  |  |  |  |  |  |

|                                                       | ADTRG0                        | Input  | Input pins for the external trigger signals that start the A/D conversion, active LOW.                                                                                                                            |  |  |  |  |  |  |

| DAC12                                                 | DA0, DA1                      | Output | Output pins for the analog signals to be processed by the D/A converter.                                                                                                                                          |  |  |  |  |  |  |

| Comparator output VCOUT Output Comparator output pin. |                               |        |                                                                                                                                                                                                                   |  |  |  |  |  |  |

| ACMPHS                                                | IVREF0 to IVREF5              | Input  | Reference voltage input pin.                                                                                                                                                                                      |  |  |  |  |  |  |

|                                                       | IVCMP0 to IVCMP5              | Input  | Analog voltage input pin.                                                                                                                                                                                         |  |  |  |  |  |  |

| ACMPLP                                                | CMPREF0,<br>CMPREF1           | Input  | Reference voltage input pin.                                                                                                                                                                                      |  |  |  |  |  |  |

|                                                       | CMPIN0, CMPIN1                | Input  | Analog voltage input pins.                                                                                                                                                                                        |  |  |  |  |  |  |

|                                                       |                               |        |                                                                                                                                                                                                                   |  |  |  |  |  |  |

| R7FS3A77C2A01CBJ |                        |                        |          |         |                |                |       |      |       |                 |                 |    |

|------------------|------------------------|------------------------|----------|---------|----------------|----------------|-------|------|-------|-----------------|-----------------|----|

|                  | A                      | В                      | С        | D       | E              | F              | G     | н    | J     | к               | L               |    |

| 11               | P407                   | P408                   | P411     | P414    | P212/<br>EXTAL | P215/<br>XCIN  | VCL   | P406 | P403  | P401            | P400            | 11 |

| 10               | USB_DM                 | USB_DP                 | P410     | P415    | P213/<br>XTAL  | P214/<br>XCOUT | VBATT | P405 | P402  | P511            | P512            | 10 |

| 9                | VCC_<br>USB            | VSS_<br>USB            | P409     | P412    | P708           | VCC            | VSS   | P404 | P002  | P001            | P000            | 9  |

| 8                | P205                   | VCC_<br>USB_<br>LDO    | P206     | P204    | P413           | P710           | P702  | P006 | P004  | P003            | P005            | 8  |

| 7                | P203                   | P202                   | P313     | P314    | P315           | P709           | P701  | P007 | AVSS0 | P011/<br>VREFL0 | P010/<br>VREFH0 | 7  |

| 6                | VSS                    | VCC                    | RES      | P201/MD | P200           | NC             | P700  | P008 | AVCC0 | P013/<br>VREFL  | P012/<br>VREFH  | 6  |

| 5                | P308                   | P309                   | P307     | P302    | P304           | P612           | P601  | P506 | P505  | P015            | P014            | 5  |

| 4                | P305                   | P306                   | P808     | P114    | P611           | P603           | P600  | P504 | P503  | VSS             | vcc             | 4  |

| 3                | P809                   | P303                   | P110/TDI | P111    | P609           | P604           | P106  | P104 | P502  | P500            | P501            | 3  |

| 2                | P301                   | P108/<br>TMS/<br>SWDIO | P113     | P608    | P613           | P605           | P602  | P105 | P102  | P801            | P800            | 2  |

| 1                | P300/<br>TCK/<br>SWCLK | P109/<br>TDO/<br>SWO   | P112     | P115    | P610           | VCC            | VSS   | P107 | P103  | P101            | P100            | 1  |

|                  | A                      | В                      | С        | D       | E              | F              | G     | Н    | J     | К               | L               | I  |

Figure 1.5 Pin assignment for BGA 121-pin (Upper perspective view)

# 1.7 Pin Lists

S3A7

| Pin nu     | umber    |            |          |            |        |          | Ϋ́,                                        |              |              | Timer                              | s                 |               |            | Comn       | nunica                                    | tion in    | terface                 | s             |                 | Analo | gs           |                   | нмі   |      |           |

|------------|----------|------------|----------|------------|--------|----------|--------------------------------------------|--------------|--------------|------------------------------------|-------------------|---------------|------------|------------|-------------------------------------------|------------|-------------------------|---------------|-----------------|-------|--------------|-------------------|-------|------|-----------|

| LGA145     | LQFP144  | BGA121     | LQFP100  | LGA100     | LQFP64 | QFN64    | Power, System, Clock,<br>Debug, CAC, VBATT | I/O ports    | External bus | AGT                                | GPT_OPS, POEG     | GPT           | RTC        | USBFS,CAN  | sci                                       | 2          | SPI/QSPI                | ISS           | IHOS            | ADC14 | DAC12, OPAMP | ACMPHS,<br>ACMPLP | SLCDC | CTSU | Interrupt |

| N13        | 1        | L11        | 1        | J10        | 1      | 1        |                                            | P400         |              |                                    |                   | GTIOC<br>6A_A |            |            | SCK4_<br>B                                | SCL0_<br>A |                         | AUDIO<br>CLK  |                 |       |              |                   |       | TS20 | IRQ0      |

| L11        | 2        | K11        | 2        | <b>1</b> 8 | 2      | 2        |                                            | P401         |              |                                    | GTET<br>RGA_<br>B | GTIOC<br>6B_A |            | CTX0_<br>B | CTS4_                                     | SDA0_<br>A |                         |               |                 |       |              |                   |       | TS19 | IRQ5      |

| M13        | 3        | J10        | 3        | F6         | 3      | 3        | VBAT<br>WIO0                               | P402         |              | AGTIO<br>0_B/<br>AGTIO<br>1_B      |                   |               | RTCIC<br>0 | CRX0_<br>B | 001_0                                     |            |                         |               |                 |       |              |                   |       | TS18 | IRQ4      |

| K11        | 4        | J11        | 4        | H10        |        |          | VBAT<br>WIO1                               | P403         |              | -<br>AGTIO<br>0_C/<br>AGTIO<br>1_C |                   | GTIOC<br>3A_B | RTCIC<br>1 |            |                                           |            |                         | SSISC<br>K0_A |                 |       |              |                   |       | TS17 |           |

| L12        | 5        | H9         | 5        | G8         |        |          | VBAT<br>WIO2                               | P404         |              |                                    |                   | GTIOC<br>3B_B | RTCIC<br>2 |            |                                           |            |                         | SSIWS<br>0_A  |                 |       |              |                   |       | TS16 | <u> </u>  |

| L13        | 6        | H10        | 6        | H9         |        |          | WIGE                                       | P405         |              |                                    |                   | GTIOC         | -          |            |                                           |            |                         | SSITX         |                 |       |              |                   |       | TS15 | <u> </u>  |

| J10        | 7        | H11        | 7        | F7         |        |          |                                            | P406         |              |                                    |                   | 1A_B<br>GTIOC |            |            |                                           |            |                         | D0_A<br>SSIRX |                 |       |              |                   |       | TS14 | <u> </u>  |

| H10        | 8        | G6         |          |            |        |          |                                            | P700         |              |                                    |                   | 1B_B<br>GTIOC |            |            |                                           |            |                         | D0_A          |                 |       |              |                   |       | TS32 | <u> </u>  |

| K12        | 9        | G7         |          |            |        |          |                                            | P701         |              |                                    |                   | 5A_B<br>GTIOC |            |            |                                           |            |                         |               |                 |       |              |                   |       | TS33 | <u> </u>  |

| K13        | 10       | G8         |          |            |        |          |                                            | P702         |              |                                    |                   | 5B_B<br>GTIOC |            |            |                                           |            |                         |               |                 |       |              |                   |       | TS34 | <u> </u>  |

| J11        | 11       |            |          |            |        |          | -                                          | P703         |              |                                    |                   | 6A_B<br>GTIOC |            |            |                                           |            |                         |               |                 |       |              |                   |       |      | <b> </b>  |

|            |          |            |          |            |        |          |                                            |              |              |                                    |                   | 6B_B          |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| H11<br>G11 | 12<br>13 |            |          |            |        |          |                                            | P704<br>P705 |              |                                    |                   |               |            |            |                                           |            |                         |               |                 |       |              |                   |       |      | <u> </u>  |

| J12<br>J13 | 14<br>15 | G10<br>G11 | 8<br>9   | G9<br>G10  | 4<br>5 | 4<br>5   | VBATT<br>VCL                               |              |              |                                    |                   |               |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| H13        | 16       | F11        | 9<br>10  | F10        | 6      | 6        | XCIN                                       | P215         |              |                                    |                   |               |            |            |                                           |            |                         |               |                 |       |              |                   |       |      | <u> </u>  |

| H12        | 17       | F10        | 11       | F9         | 7      | 7        | XCOU<br>T                                  | P214         |              |                                    |                   |               |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| F12<br>G12 | 18<br>19 | G9<br>E10  | 12<br>13 | D9<br>E9   | 8<br>9 | 8<br>9   | VSS<br>XTAL                                | P213         |              |                                    | GTET              |               |            |            | TXD1_                                     |            |                         |               |                 |       |              |                   |       |      | IRQ2      |

| 0.2        | 10       |            | 10       | 20         | 0      | Ū        |                                            |              |              |                                    | RGC_<br>A         |               |            |            | A/<br>MOSI1<br>_A/<br>SDA1_<br>A          |            |                         |               |                 |       |              |                   |       |      |           |

| G13        | 20       | E11        | 14       | E10        | 10     | 10       | EXTAL                                      | P212         |              | AGTE<br>E1                         | GTET<br>RGD_<br>A |               |            |            | RXD1_<br>A/<br>MISO1<br>_A/<br>SCL1_<br>A |            |                         |               |                 |       |              |                   |       |      | IRQ3      |

| F13        | 21       | F9         | 15       | D10        | 11     | 11       | VCC                                        | D740         |              |                                    |                   | OTIOO         |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| G10        | 22       |            |          |            |        |          |                                            | P713         |              |                                    |                   | GTIOC<br>2A_B |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| F11        | 23       |            |          |            |        |          |                                            | P712         |              |                                    |                   | GTIOC<br>2B_B |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| E13        | 24       |            |          |            |        |          |                                            | P711         |              |                                    |                   |               |            |            | CTS1_<br>RTS1_<br>B/<br>SS1_B             |            |                         |               |                 |       |              |                   |       |      |           |

| E12        | 25       | F8         | 1        | 1          |        | 1        | 1                                          | P710         |              |                                    |                   | 1             | 1          |            | SCK1_<br>B                                |            | 1                       |               |                 |       |              | 1                 |       | TS35 |           |

| F10        | 26       | F7         |          |            |        |          |                                            | P709         |              |                                    |                   |               |            |            | TXD1_<br>B/<br>MOSI1<br>_B/<br>SDA1_<br>B |            |                         |               |                 |       |              |                   |       | TS13 | IRQ10     |

| D13        | 27       | E9         | 16       | F8         |        |          | CACR<br>EF_B                               | P708         |              |                                    |                   |               |            |            | RXD1_<br>B/<br>MISO1<br>_B/<br>SCL1_<br>B |            | SSLA3<br>_ <sup>B</sup> |               |                 |       |              |                   |       | TS12 | IRQ11     |

| E11        | 28       | D10        | 17       | E8         |        | 1        |                                            | P415         |              |                                    |                   |               |            |            |                                           |            | SSLA2<br>B              |               |                 |       |              |                   |       | TS11 | <u> </u>  |

| D12        | 29       | D11        | 18       | E7         |        | <u> </u> |                                            | P414         |              |                                    |                   |               |            |            |                                           |            | -<br>SSLA1              |               | SD0W            |       |              |                   |       | TS10 | <u> </u>  |

| E10        | 30       | E8         | 19       | C9         |        |          |                                            | P413         |              |                                    | GTOU<br>UP_B      |               |            |            | CTS0_<br>RTS0_<br>B/                      |            | _B<br>SSLA0<br>_B       |               | P<br>SD0CL<br>K |       |              |                   |       | TS09 |           |

| C13        | 31       | D9         | 20       | C10        |        |          |                                            | P412         |              |                                    | GTOU              |               |            |            | SS0_B<br>SCK0_                            |            | RSPC                    |               | SD0C            |       |              |                   |       | TS08 | <u> </u>  |

|            |          |            |          |            |        |          |                                            |              |              |                                    | LO_B              |               |            |            | В                                         |            | KA_B                    |               | MD              |       |              |                   |       |      |           |

## 2.1 Absolute Maximum Ratings

#### Table 2.1 Absolute maximum ratings

| Item                      |                              | Symbol           | Value               | Unit |

|---------------------------|------------------------------|------------------|---------------------|------|

| Power supply voltage      |                              | VCC              | -0.5 to +6.5        | V    |

| Input voltage             | 5V-tolerant ports*1          | V <sub>in</sub>  | -0.3 to +6.5        | V    |

|                           | P000 to P015                 | V <sub>in</sub>  | -0.3 to AVCC0 + 0.3 | V    |

|                           | Others                       | V <sub>in</sub>  | -0.3 to VCC + 0.3   | V    |

| Reference power supply v  | voltage                      | VREFH0           | -0.3 to +6.5        | V    |

|                           |                              | VREFH            |                     | V    |

| VBATT power supply volta  | age                          | VBATT            | -0.5 to +6.5        | V    |

| Analog power supply volta | age                          | AVCC0            | -0.5 to +6.5        | V    |

| USB power supply voltage  | e                            | VCC_USB          | -0.5 to +6.5        | V    |

|                           |                              | VCC_USB_LDO      | -0.5 to +6.5        | V    |

| Analog input voltage      | When AN000 to AN015 are used | V <sub>AN</sub>  | -0.3 to AVCC0 + 0.3 | V    |

|                           | When AN016 to AN027 are used |                  | -0.3 to VCC + 0.3   | V    |

| LCD voltage               | VL1 voltage                  | V <sub>L1</sub>  | -0.3 to +2.8        | V    |

|                           | VL2 voltage                  | V <sub>L2</sub>  | -0.3 to +6.5        | V    |

|                           | VL3 voltage                  | V <sub>L3</sub>  | -0.3 to +6.5        | V    |

|                           | VL4 voltage                  | V <sub>L4</sub>  | -0.3 to +6.5        | V    |

| Operating temperature*2   | *3                           | T <sub>opr</sub> | -40 to +105         | °C   |

| Storage temperature       |                              | T <sub>stg</sub> | -55 to +125         | °C   |

Caution: Permanent damage to the MCU may result if absolute maximum ratings are exceeded. To preclude any malfunctions due to noise interference, insert capacitors of high frequency characteristics between the VCC and VSS pins, between the AVCC0 and AVSS0 pins, between the VCC\_USB and VSS\_USB pins, between the VREFH0 and VREFL0 pins, and between the VREFH and VREFL pins. Place capacitors of about 0.1 µF as close as possible to every power supply pin and use the shortest and heaviest possible traces. Also, connect capacitors as stabilization capacitance.

Connect the VCL pin to a VSS pin by a 4.7 µF capacitor. The capacitor must be placed close to the pin.

Note 1. Ports P205, P206, P400 to P404, P407, P511, P512 are 5V-tolerant. Do not input signals or an I/O pull-up power supply while the device is not powered. The current injection that results from input of such a signal or I/O pull-up might cause malfunction and the abnormal current that passes in the device at this time might cause degradation of internal elements.

Note 2. See section 2.2.1, Tj/Ta Definition.

Note 3. Contact Renesas Electronics sales office for information on derating operation under Ta = +85°C to +105°C. Derating is the systematic reduction of load for improved reliability.

| ltem                         | Symbol      | Value                                                     | Min             | Тур | Max   | Unit |

|------------------------------|-------------|-----------------------------------------------------------|-----------------|-----|-------|------|

| Power supply voltages        | VCC*1, *2   | When USBFS is not used                                    | 1.6             | -   | 5.5   | V    |

|                              |             | When USBFS is used<br>USB Regulator<br>Disable            | VCC_USB         | -   | 3.6   | V    |

|                              |             | When USBFS is used<br>USB Regulator<br>Enable             | VCC_USB<br>_LDO | -   | 5.5   | V    |

|                              | VSS         | -                                                         | -               | 0   | -     | V    |

| USB power supply voltages    | VCC_USB     | When USBFS is not used                                    | -               | VCC | -     | V    |

|                              |             | When USBFS is used<br>USB Regulator<br>Disable<br>(Input) | 3.0             | 3.3 | 3.6   | V    |

|                              | VCC_USB_LDO | When USBFS is not used                                    | -               | VCC | -     | V    |

|                              |             | When USBFS is used<br>USB Regulator<br>Enable             | 3.8             | -   | 5.5   | V    |

|                              | VSS_USB     | S_USB                                                     |                 | 0   | -     | V    |

| VBATT power supply voltage   | VBATT       | When the battery<br>backup function is not<br>used        | -               | VCC | -     | V    |

|                              |             | When the battery<br>backup function is<br>used            | 1.6             | -   | 3.6   | V    |

| Analog power supply voltages | AVCC0*1, *2 |                                                           | 1.6             | -   | 5.5   | V    |

|                              | AVSS0       |                                                           | -               | 0   | -     | V    |

|                              | VREFH0      | When used as                                              | 1.6             | -   | AVCC0 | V    |

|                              | VREFL0      | ADC14 Reference                                           | -               | 0   | -     | V    |

|                              | VREFH       | When used as                                              | 1.6             | -   | AVCC0 | V    |

|                              | VREFL       | DAC12 Reference                                           | -               | 0   | -     | V    |

### Table 2.2 Recommended operating conditions

Note 1. Use AVCC0 and VCC under the following conditions:

AVCC0 and VCC can be set individually within the operating range when VCC  $\ge$  2.0 V AVCC0 = VCC when VCC < 2.0 V

Note 2. When powering on the VCC and AVCC0 pins, power them on at the same time or the VCC pin first and then the AVCC0 pin.

#### Operating and Standby Current 2.2.9

# Table 2.11Operating and standby current (1) (1/2)Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| ltem      |                    |                 |                                                                            |               | Symbol          | Typ*10 | Мах  | Unit | Test<br>condition |

|-----------|--------------------|-----------------|----------------------------------------------------------------------------|---------------|-----------------|--------|------|------|-------------------|

| Supply    | High-speed         | Normal mode     | All peripheral clock                                                       | ICLK = 48 MHz | I <sub>CC</sub> | 11.8   | -    | mA   | *7                |

| current*1 | mode* <sup>2</sup> |                 | disabled, code executing<br>from flash* <sup>5</sup>                       | ICLK = 32 MHz |                 | 8.6    | -    |      |                   |

|           |                    |                 |                                                                            | ICLK = 16 MHz |                 | 5.1    | -    |      |                   |

|           |                    |                 |                                                                            | ICLK = 8 MHz  |                 | 3.4    | -    |      |                   |

|           |                    |                 | All peripheral clock                                                       | ICLK = 48 MHz |                 | 18.6   | -    |      |                   |

|           |                    |                 | disabled, CoreMark code executing from flash*5                             | ICLK = 32 MHz |                 | 12.7   | -    |      |                   |

|           |                    |                 |                                                                            | ICLK = 16 MHz |                 | 7.2    | -    |      |                   |

|           |                    |                 |                                                                            | ICLK = 8 MHz  |                 | 4.5    | -    |      |                   |

|           |                    |                 | All peripheral clock                                                       | ICLK = 48 MHz |                 | 30.1   | -    |      | *9                |

|           |                    |                 | enabled, code executing<br>from flash* <sup>5</sup>                        | ICLK = 32 MHz |                 | 23.2   | -    | -    | *8                |

|           |                    |                 |                                                                            | ICLK = 16 MHz |                 | 12.6   | -    |      |                   |

|           |                    |                 |                                                                            | ICLK = 8 MHz  |                 | 7.3    | -    |      |                   |

|           |                    |                 | All peripheral clock<br>enabled, code executing<br>from SRAM* <sup>5</sup> | ICLK = 48 MHz |                 | -      | 75.0 |      | *9                |

|           |                    | Sleep mode      | All peripheral clock                                                       | ICLK = 48 MHz |                 | 6.4    | -    | -    | *7                |

|           |                    |                 | disabled*5                                                                 | ICLK = 32 MHz |                 | 4.7    | -    |      |                   |

|           |                    |                 |                                                                            | ICLK = 16 MHz |                 | 3.2    | -    |      |                   |

|           |                    |                 |                                                                            | ICLK = 8 MHz  |                 | 2.4    | -    |      |                   |

|           |                    |                 | All peripheral clock                                                       | ICLK = 48 MHz |                 | 24.7   | -    |      | *9                |

|           |                    |                 | enabled*5                                                                  | ICLK = 32 MHz |                 | 19.2   | -    |      | *8                |

|           |                    |                 |                                                                            | ICLK = 16 MHz |                 | 10.7   | -    | 1    |                   |

|           |                    |                 |                                                                            | ICLK = 8 MHz  |                 | 6.4    | -    |      |                   |

|           |                    | Increase during | BGO operation*6                                                            |               |                 | 2.5    | -    |      | -                 |

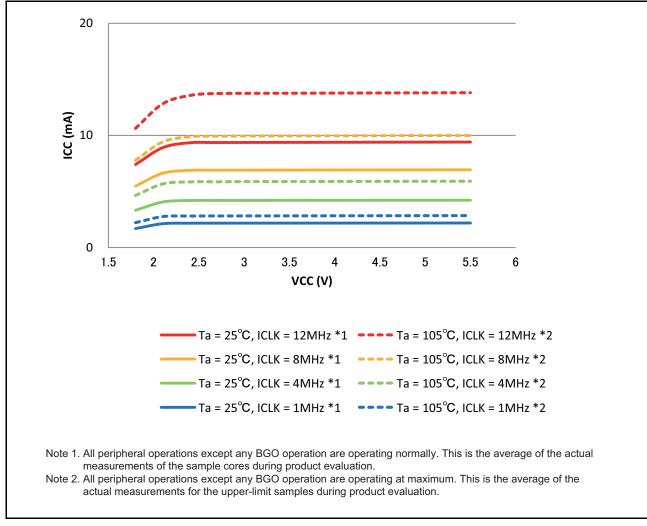

|           | Middle-speed       | Normal mode     | All peripheral clock                                                       | ICLK = 12 MHz | I <sub>CC</sub> | 3.6    | -    | mA   | *7                |

|           | mode*2             |                 | disabled, code executing<br>from flash* <sup>5</sup>                       | ICLK = 8 MHz  |                 | 3.0    | -    | -    |                   |

|           |                    |                 | from liash 9                                                               | ICLK = 1 MHz  |                 | 1.4    | -    |      |                   |

|           |                    |                 | All peripheral clock                                                       | ICLK = 12 MHz |                 | 5.2    | -    |      |                   |

|           |                    |                 | disabled, CoreMark code executing from flash*5                             | ICLK = 8 MHz  |                 | 4.0    | -    |      |                   |

|           |                    |                 | exceduling from hash                                                       | ICLK = 1 MHz  |                 | 1.6    | -    |      |                   |

|           |                    |                 | All peripheral clock                                                       | ICLK = 12 MHz |                 | 9.4    | -    |      | *8                |

|           |                    |                 | enabled, code executing from flash*5                                       | ICLK = 8 MHz  |                 | 6.9    | -    |      |                   |

|           |                    |                 |                                                                            | ICLK = 1 MHz  |                 | 2.2    | -    |      |                   |

|           |                    |                 | All peripheral clock<br>enabled, code executing<br>from SRAM* <sup>5</sup> | ICLK = 12 MHz |                 | -      | 30.0 | -    |                   |

|           |                    | Sleep mode      | All peripheral clock                                                       | ICLK = 12 MHz |                 | 2.2    | -    |      | *7                |

|           |                    |                 | disabled*5                                                                 | ICLK = 8 MHz  |                 | 2.0    | -    |      |                   |

|           |                    |                 |                                                                            | ICLK = 1 MHz  |                 | 1.3    | -    |      |                   |

|           |                    |                 | All peripheral clock                                                       | ICLK = 12 MHz |                 | 7.9    | -    |      | *8                |

|           |                    |                 | enabled*5                                                                  | ICLK = 8 MHz  |                 | 5.9    | -    |      |                   |

|           |                    |                 |                                                                            | ICLK = 1 MHz  |                 | 1.3    | -    | 1    |                   |

|           |                    | Increase during | BGO operation*6                                                            | I             | -               | 2.5    | -    |      | -                 |

Figure 2.18 Voltage dependency in middle-speed mode (reference data)

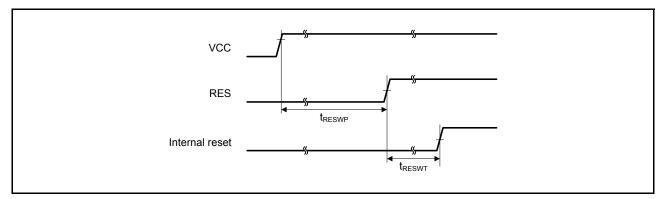

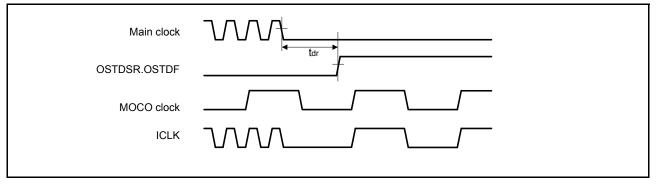

Figure 2.32 Reset input timing at power-on

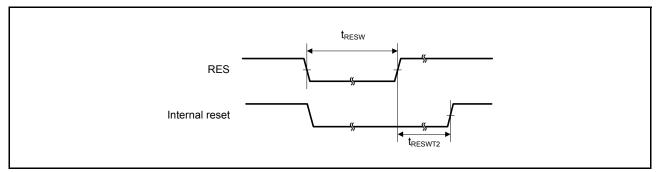

## Figure 2.33 Reset input timing (1)

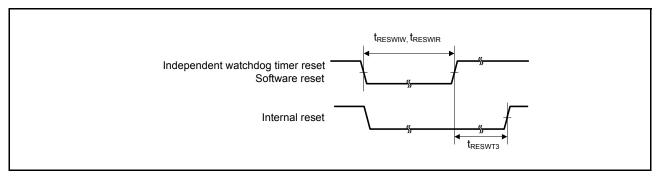

Figure 2.34 Reset input timing (2)

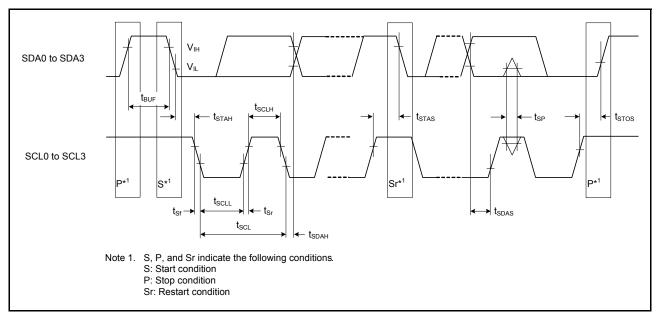

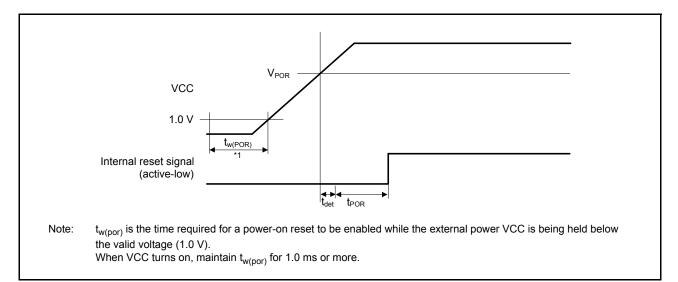

## 2.3.12 IIC Timing

### Table 2.42 IIC timing

| Conditions: VCC = AVCC0 = 2.7 to 5.5 V |

|----------------------------------------|

|----------------------------------------|

| Item                      |                                                                       | Symbol            | Min* <sup>1</sup> , * <sup>2</sup>                           | Max                         | Unit | Test<br>conditions |

|---------------------------|-----------------------------------------------------------------------|-------------------|--------------------------------------------------------------|-----------------------------|------|--------------------|

| IIC                       | SCL input cycle time                                                  | t <sub>SCL</sub>  | 6 (12) × t <sub>IICcyc</sub> + 1300                          | -                           | ns   | Figure 2.66        |

| (standard mode,<br>SMBus) | SCL input high pulse width                                            | t <sub>SCLH</sub> | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   |                    |

| Cividad)                  | SCL input low pulse width                                             | t <sub>SCLL</sub> | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   |                    |

|                           | SCL, SDA input rise time                                              | t <sub>Sr</sub>   | -                                                            | 1000                        | ns   |                    |

|                           | SCL, SDA input fall time                                              | t <sub>Sf</sub>   | -                                                            | 300                         | ns   |                    |

|                           | SCL, SDA input spike pulse removal time                               | t <sub>SP</sub>   | 0                                                            | 1 (4) × t <sub>IICcyc</sub> | ns   |                    |

|                           | SDA input bus free time<br>(When wakeup function is disabled)         | t <sub>BUF</sub>  | 3 (6) × t <sub>IICcyc</sub> + 300                            | -                           | ns   |                    |

|                           | SDA input bus free time<br>(When wakeup function is enabled)          | t <sub>BUF</sub>  | 3 (6) × t <sub>IICcyc</sub> + 4 × t <sub>Pcyc</sub><br>+ 300 | -                           | ns   |                    |

|                           | START condition input hold time<br>(When wakeup function is disabled) | t <sub>STAH</sub> | t <sub>IICcyc</sub> + 300                                    | -                           | ns   |                    |

|                           | START condition input hold time<br>(When wakeup function is enabled)  | t <sub>STAH</sub> | 1 (5) × t <sub>IICcyc</sub> + t <sub>Pcyc</sub> +<br>300     | -                           | ns   |                    |

|                           | Repeated START condition input setup time                             | t <sub>STAS</sub> | 1000                                                         | -                           | ns   |                    |

|                           | STOP condition input setup time                                       | t <sub>STOS</sub> | 1000                                                         | -                           | ns   |                    |