# E. Fenesas Electronics America Inc - <u>R7FS3A77C3A01CNB#AC1 Datasheet</u>

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                       |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 48MHz                                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, MMC/SD, SCI, SPI, UART/USART, USB                     |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                               |

| Number of I/O              | 50                                                                                    |

| Program Memory Size        | 1MB (1M x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | 16K x 8                                                                               |

| RAM Size                   | 192K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                           |

| Data Converters            | A/D 18x14b; D/A 2x12b                                                                 |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                    |

| Mounting Type              | Surface Mount                                                                         |

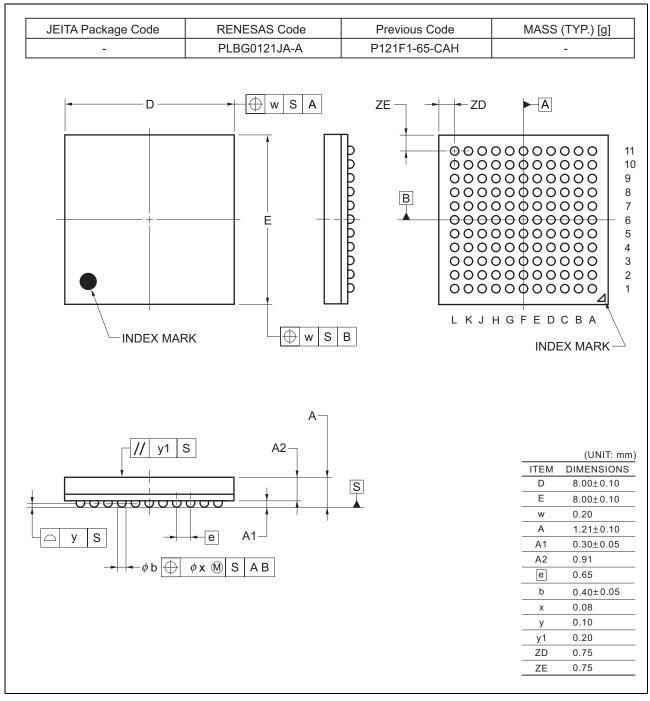

| Package / Case             | 64-WFQFN Exposed Pad                                                                  |

| Supplier Device Package    | 64-HWQFN (8x8)                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r7fs3a77c3a01cnb-ac1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 1.3System (1/2)

| Feature                                               | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating mode                                        | Two operating modes:<br>- Single-chip mode<br>- SCI/USB boot mode.<br>See section 3, Operating Modes in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Reset                                                 | This MCU has 14 types of resets:<br>• RES pin reset<br>• Power-on reset<br>• VBATT selected voltage power on reset<br>• Independent watchdog timer reset<br>• Watchdog timer reset<br>• Voltage monitor 0 reset<br>• Voltage monitor 1 reset<br>• Voltage monitor 1 reset<br>• Voltage monitor 2 reset<br>• SRAM parity error reset<br>• SRAM ECC error reset<br>• Bus master MPU error reset<br>• Bus slave MPU error reset<br>• Stack pointer error reset<br>• Software reset.<br>See section 6, Resets in User's Manual.                                                                                                       |

| Low Voltage Detection (LVD)                           | The Low Voltage Detection (LVD) monitors the voltage level input to the VCC pin, and the detection level can be selected using a software program. See section 8, Low Voltage Detection (LVD) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Clock                                                 | <ul> <li>Main clock oscillator (MOSC)</li> <li>Sub-clock oscillator (SOSC)</li> <li>High-speed on-chip oscillator (HOCO)</li> <li>Middle-speed on-chip oscillator (MOCO)</li> <li>Low-speed on-chip oscillator (LOCO)</li> <li>PLL frequency synthesizer</li> <li>Independent Watchdog Timer on-chip oscillator</li> <li>Clock out support.</li> <li>See section 9, Clock Generation Circuit in User's Manual.</li> </ul>                                                                                                                                                                                                         |

| Clock Frequency Accuracy<br>Measurement Circuit (CAC) | The Clock Frequency Accuracy Measurement Circuit (CAC) is used to check the system clock frequency with a reference clock signal by counting the number of pulses of the system clock to be measured. The reference clock can be provided externally through a CACREF pin or internally from various on-chip oscillators.<br>Event signals can be generated when the clock does not match or measurement ends. This feature is particularly useful in implementing a fail-safe mechanism for home and industrial automation applications.<br>See section 10, Clock Frequency Accuracy Measurement Circuit (CAC) in User's Manual. |

| Low Power Mode                                        | This MCU has several functions for reducing power consumption, such as setting clock dividers, controlling EBCLK output, stopping modules, selecting power control mode in normal operation, and transitioning to low power modes. See section 11, Low Power Mode in User's Manual.                                                                                                                                                                                                                                                                                                                                               |

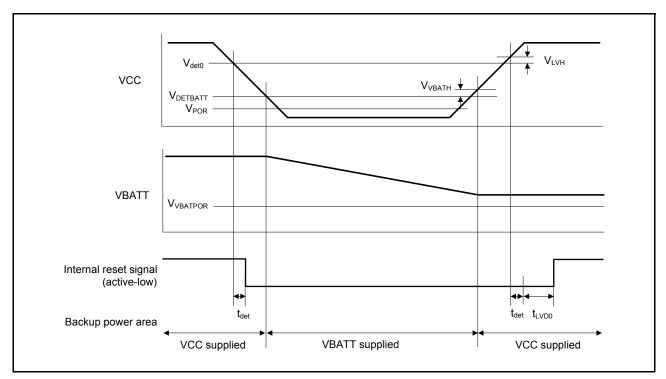

| Battery Backup Function                               | This MCU has a battery backup function that can be partly powered by a battery. The battery powered area includes RTC/AGT/SOSC/LOCO/Wakeup Control/Backup Memory/VBATT_R Low Voltage Detection/Switch between VCC/VBATT. During normal operation, the battery powered area is powered by the main power supply which is the VCC pin. When a VCC voltage drop is detected, the power source is switched to the dedicated battery backup power pin, the VBATT pin. When the voltage rises again, the power source is switched from the VBATT pin to the VCC pin. See section 12, Battery Backup Function in User's Manual.          |

| Register Write Protection                             | The Register Write Protection function protects important registers from being overwritten due to software errors. See section 13, Register Write Protection in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Memory Protection Unit (MPU)                          | This MCU incorporates two memory protection units and provide a CPU stack pointer monitor function. See section 16, Memory Protection Unit (MPU) in User's Manual.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Function | Signal                                          | I/O    | Description                                                                                                                       |  |  |  |  |  |  |

|----------|-------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| GPT      | GTETRGA,<br>GTETRGB,<br>GTETRGC,<br>GTETRGD     | Input  | External trigger input pin.                                                                                                       |  |  |  |  |  |  |

|          | GTIOC0A to<br>GTIOC9A,<br>GTIOC0B to<br>GTIOC9B | I/O    | Input capture, Output capture, or PWM output pin.                                                                                 |  |  |  |  |  |  |

|          | GTIU                                            | Input  | Hall sensor input pin U.                                                                                                          |  |  |  |  |  |  |

|          | GTIV                                            | Input  | Hall sensor input pin V.                                                                                                          |  |  |  |  |  |  |

|          | GTIW                                            | Input  | Hall sensor input pin W.                                                                                                          |  |  |  |  |  |  |

|          | GTOUUP                                          | Output | Three-phase PWM output for BLDC motor control (positive U phase).                                                                 |  |  |  |  |  |  |

|          | GTOULO                                          | Output | Three-phase PWM output for BLDC motor control (negative U phase).                                                                 |  |  |  |  |  |  |

|          | GTOVUP                                          | Output | Three-phase PWM output for BLDC motor control (positive V phase).                                                                 |  |  |  |  |  |  |

|          | GTOVLO                                          | Output | Three-phase PWM output for BLDC motor control (negative V phase).                                                                 |  |  |  |  |  |  |

|          | GTOWUP                                          | Output | Three-phase PWM output for BLDC motor control (positive W phase).                                                                 |  |  |  |  |  |  |

|          | GTOWLO                                          | Output | Three-phase PWM output for BLDC motor control (negative W phase).                                                                 |  |  |  |  |  |  |

| AGT      | AGTEE0, AGTEE1                                  | Input  | External event input enable.                                                                                                      |  |  |  |  |  |  |

|          | AGTIO0, AGTIO1                                  | I/O    | External event input and pulse output.                                                                                            |  |  |  |  |  |  |

|          | AGTO0, AGTO1                                    | Output | Pulse output.                                                                                                                     |  |  |  |  |  |  |

|          | AGTOA0, AGTOA1                                  | Output | Output compare match A output.                                                                                                    |  |  |  |  |  |  |

|          | AGTOB0, AGTOB1                                  | Output | Output compare match B output.                                                                                                    |  |  |  |  |  |  |

| RTC      | RTCOUT                                          | Output | Output pin for 1-Hz/64-Hz clock.                                                                                                  |  |  |  |  |  |  |

|          | RTCIC0 to RTCIC2                                | Input  | Time capture event input pins.                                                                                                    |  |  |  |  |  |  |

| SCI      | SCK0 to SCK4,<br>SCK9                           | I/O    | Input/output pins for the clock (clock synchronous mode).                                                                         |  |  |  |  |  |  |

|          | RXD0 to RXD4,<br>RXD9                           | Input  | Input pins for received data (asynchronous mode/clock synchronous mode).                                                          |  |  |  |  |  |  |

|          | TXD0 to TXD4,<br>TXD9                           | Output | Output pins for transmitted data (asynchronous mode/clock synchronous mode).                                                      |  |  |  |  |  |  |

|          | CTS0_RTS0 to<br>CTS4_RTS4,<br>CTS9_RTS9         | I/O    | Input/Output pins for controlling the start of transmission and reception (asynchronous mode/clock synchronous mode), active LOW. |  |  |  |  |  |  |

|          | SCL0 to SCL4,<br>SCL9                           | I/O    | Input/output pins for the IIC clock (simple IIC).                                                                                 |  |  |  |  |  |  |

|          | SDA0 to SDA4,<br>SDA9                           | I/O    | Input/output pins for the IIC data (simple IIC).                                                                                  |  |  |  |  |  |  |

|          | SCK0 to SCK4,<br>SCK9                           | I/O    | Input/output pins for the clock (simple SPI).                                                                                     |  |  |  |  |  |  |

|          | MISO0 to MISO4,<br>MISO9                        | I/O    | Input/output pins for slave transmission of data (simple SPI).                                                                    |  |  |  |  |  |  |

|          | MOSI0 to MOSI4,<br>MOSI9                        | I/O    | Input/output pins for master transmission of data (simple SPI).                                                                   |  |  |  |  |  |  |

|          | SS0 to SS4, SS9                                 | Input  | Slave-select input pins (simple SPI), active LOW.                                                                                 |  |  |  |  |  |  |

| liC      | SCL0 to SCL2                                    | I/O    | Input/output pins for clock.                                                                                                      |  |  |  |  |  |  |

|          | SDA0 to SDA2                                    | I/O    | Input/output pins for data.                                                                                                       |  |  |  |  |  |  |

| SSI      | SSISCK0                                         | I/O    | SSI serial bit clock pin.                                                                                                         |  |  |  |  |  |  |

|          | SSISCK1                                         |        |                                                                                                                                   |  |  |  |  |  |  |

|          | SSIWS0                                          | I/O    | Word select pins.                                                                                                                 |  |  |  |  |  |  |

|          | SSIWS1                                          |        |                                                                                                                                   |  |  |  |  |  |  |

|          | SSITXD0                                         | Output | Serial data output pins.                                                                                                          |  |  |  |  |  |  |

|          | SSIRXD0                                         | Input  | Serial data input pins.                                                                                                           |  |  |  |  |  |  |

|          | SSIDATA1                                        | I/O    | Serial data input/output pins.                                                                                                    |  |  |  |  |  |  |

|          | AUDIO_CLK                                       | Input  | External clock pin for audio (input oversampling clock).                                                                          |  |  |  |  |  |  |

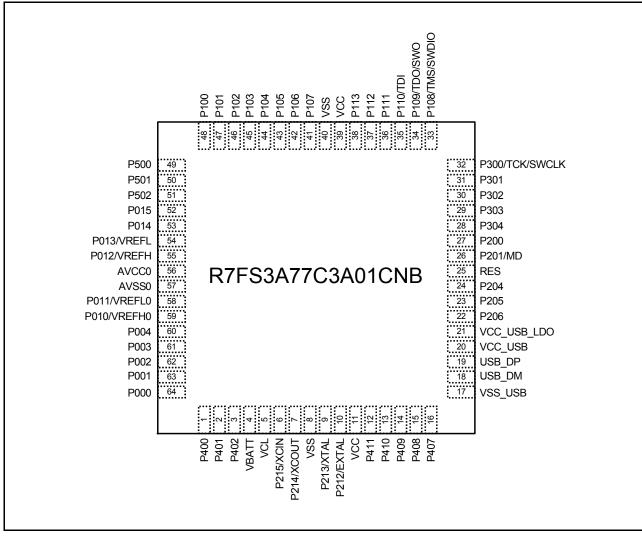

Figure 1.9 Pin assignment for QFN 64-pin (Upper perspective view)

## 1.7 Pin Lists

S3A7

| Pin nu     | umber    |            |          |            |        |          | Ϋ́,                                        |              |              | Timer                              | s                 |               |            | Comn       | nunica                                    | tion in    | terface                 | s             |                 | Analo | gs           |                   | нмі   |      |           |

|------------|----------|------------|----------|------------|--------|----------|--------------------------------------------|--------------|--------------|------------------------------------|-------------------|---------------|------------|------------|-------------------------------------------|------------|-------------------------|---------------|-----------------|-------|--------------|-------------------|-------|------|-----------|

| LGA145     | LQFP144  | BGA121     | LQFP100  | LGA100     | LQFP64 | QFN64    | Power, System, Clock,<br>Debug, CAC, VBATT | I/O ports    | External bus | AGT                                | GPT_OPS, POEG     | GPT           | RTC        | USBFS,CAN  | sci                                       | 2          | SPI/QSPI                | ISS           | IHOS            | ADC14 | DAC12, OPAMP | ACMPHS,<br>ACMPLP | SLCDC | CTSU | Interrupt |

| N13        | 1        | L11        | 1        | J10        | 1      | 1        |                                            | P400         |              |                                    |                   | GTIOC<br>6A_A |            |            | SCK4_<br>B                                | SCL0_<br>A |                         | AUDIO<br>CLK  |                 |       |              |                   |       | TS20 | IRQ0      |

| L11        | 2        | K11        | 2        | <b>1</b> 8 | 2      | 2        |                                            | P401         |              |                                    | GTET<br>RGA_<br>B | GTIOC<br>6B_A |            | CTX0_<br>B | CTS4_                                     | SDA0_<br>A |                         |               |                 |       |              |                   |       | TS19 | IRQ5      |

| M13        | 3        | J10        | 3        | F6         | 3      | 3        | VBAT<br>WIO0                               | P402         |              | AGTIO<br>0_B/<br>AGTIO<br>1_B      |                   |               | RTCIC<br>0 | CRX0_<br>B | 001_0                                     |            |                         |               |                 |       |              |                   |       | TS18 | IRQ4      |

| K11        | 4        | J11        | 4        | H10        |        |          | VBAT<br>WIO1                               | P403         |              | -<br>AGTIO<br>0_C/<br>AGTIO<br>1_C |                   | GTIOC<br>3A_B | RTCIC<br>1 |            |                                           |            |                         | SSISC<br>K0_A |                 |       |              |                   |       | TS17 |           |

| L12        | 5        | H9         | 5        | G8         |        |          | VBAT<br>WIO2                               | P404         |              |                                    |                   | GTIOC<br>3B_B | RTCIC<br>2 |            |                                           |            |                         | SSIWS<br>0_A  |                 |       |              |                   |       | TS16 | <u> </u>  |

| L13        | 6        | H10        | 6        | H9         |        |          | WIGE                                       | P405         |              |                                    |                   | GTIOC         | -          |            |                                           |            |                         | SSITX         |                 |       |              |                   |       | TS15 | <u> </u>  |

| J10        | 7        | H11        | 7        | F7         |        |          |                                            | P406         |              |                                    |                   | 1A_B<br>GTIOC |            |            |                                           |            |                         | D0_A<br>SSIRX |                 |       |              |                   |       | TS14 | <u> </u>  |

| H10        | 8        | G6         |          |            |        |          |                                            | P700         |              |                                    |                   | 1B_B<br>GTIOC |            |            |                                           |            |                         | D0_A          |                 |       |              |                   |       | TS32 | <u> </u>  |

| K12        | 9        | G7         |          |            |        |          |                                            | P701         |              |                                    |                   | 5A_B<br>GTIOC |            |            |                                           |            |                         |               |                 |       |              |                   |       | TS33 | <u> </u>  |

| K13        | 10       | G8         |          |            |        |          |                                            | P702         |              |                                    |                   | 5B_B<br>GTIOC |            |            |                                           |            |                         |               |                 |       |              |                   |       | TS34 | <u> </u>  |

| J11        | 11       |            |          |            |        |          | -                                          | P703         |              |                                    |                   | 6A_B<br>GTIOC |            |            |                                           |            |                         |               |                 |       |              |                   |       |      | <b> </b>  |

|            |          |            |          |            |        |          |                                            |              |              |                                    |                   | 6B_B          |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| H11<br>G11 | 12<br>13 |            |          |            |        |          |                                            | P704<br>P705 |              |                                    |                   |               |            |            |                                           |            |                         |               |                 |       |              |                   |       |      | <u> </u>  |

| J12<br>J13 | 14<br>15 | G10<br>G11 | 8<br>9   | G9<br>G10  | 4<br>5 | 4<br>5   | VBATT<br>VCL                               |              |              |                                    |                   |               |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| H13        | 16       | F11        | 9<br>10  | F10        | 6      | 6        | XCIN                                       | P215         |              |                                    |                   |               |            |            |                                           |            |                         |               |                 |       |              |                   |       |      | <u> </u>  |

| H12        | 17       | F10        | 11       | F9         | 7      | 7        | XCOU<br>T                                  | P214         |              |                                    |                   |               |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| F12<br>G12 | 18<br>19 | G9<br>E10  | 12<br>13 | D9<br>E9   | 8<br>9 | 8<br>9   | VSS<br>XTAL                                | P213         |              |                                    | GTET              |               |            |            | TXD1_                                     |            |                         |               |                 |       |              |                   |       |      | IRQ2      |

| 0.2        | 10       |            | 10       | 20         | 0      | Ū        |                                            | . 2.0        |              |                                    | RGC_<br>A         |               |            |            | A/<br>MOSI1<br>_A/<br>SDA1_<br>A          |            |                         |               |                 |       |              |                   |       |      |           |

| G13        | 20       | E11        | 14       | E10        | 10     | 10       | EXTAL                                      | P212         |              | AGTE<br>E1                         | GTET<br>RGD_<br>A |               |            |            | RXD1_<br>A/<br>MISO1<br>_A/<br>SCL1_<br>A |            |                         |               |                 |       |              |                   |       |      | IRQ3      |

| F13        | 21       | F9         | 15       | D10        | 11     | 11       | VCC                                        | D740         |              |                                    |                   | OTIOO         |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| G10        | 22       |            |          |            |        |          |                                            | P713         |              |                                    |                   | GTIOC<br>2A_B |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| F11        | 23       |            |          |            |        |          |                                            | P712         |              |                                    |                   | GTIOC<br>2B_B |            |            |                                           |            |                         |               |                 |       |              |                   |       |      |           |

| E13        | 24       |            |          |            |        |          |                                            | P711         |              |                                    |                   |               |            |            | CTS1_<br>RTS1_<br>B/<br>SS1_B             |            |                         |               |                 |       |              |                   |       |      |           |

| E12        | 25       | F8         | 1        | 1          |        | 1        | 1                                          | P710         |              |                                    |                   | 1             | 1          |            | SCK1_<br>B                                |            | 1                       |               |                 |       |              | 1                 |       | TS35 |           |

| F10        | 26       | F7         |          |            |        |          |                                            | P709         |              |                                    |                   |               |            |            | TXD1_<br>B/<br>MOSI1<br>_B/<br>SDA1_<br>B |            |                         |               |                 |       |              |                   |       | TS13 | IRQ10     |

| D13        | 27       | E9         | 16       | F8         |        |          | CACR<br>EF_B                               | P708         |              |                                    |                   |               |            |            | RXD1_<br>B/<br>MISO1<br>_B/<br>SCL1_<br>B |            | SSLA3<br>_ <sup>B</sup> |               |                 |       |              |                   |       | TS12 | IRQ11     |

| E11        | 28       | D10        | 17       | E8         |        | 1        |                                            | P415         |              |                                    |                   |               |            |            |                                           |            | SSLA2<br>B              |               |                 |       |              |                   |       | TS11 | <u> </u>  |

| D12        | 29       | D11        | 18       | E7         |        | <u> </u> |                                            | P414         |              |                                    |                   |               |            |            |                                           |            | -<br>SSLA1              |               | SD0W            |       |              |                   |       | TS10 | <u> </u>  |

| E10        | 30       | E8         | 19       | C9         |        |          |                                            | P413         |              |                                    | GTOU<br>UP_B      |               |            |            | CTS0_<br>RTS0_<br>B/                      |            | _B<br>SSLA0<br>_B       |               | P<br>SD0CL<br>K |       |              |                   |       | TS09 |           |

| C13        | 31       | D9         | 20       | C10        |        |          |                                            | P412         |              |                                    | GTOU              |               |            |            | SS0_B<br>SCK0_                            |            | RSPC                    |               | SD0C            |       |              |                   |       | TS08 | <u> </u>  |

|            |          |            |          |            |        |          |                                            |              |              |                                    | LO_B              |               |            |            | В                                         |            | KA_B                    |               | MD              |       |              |                   |       |      |           |

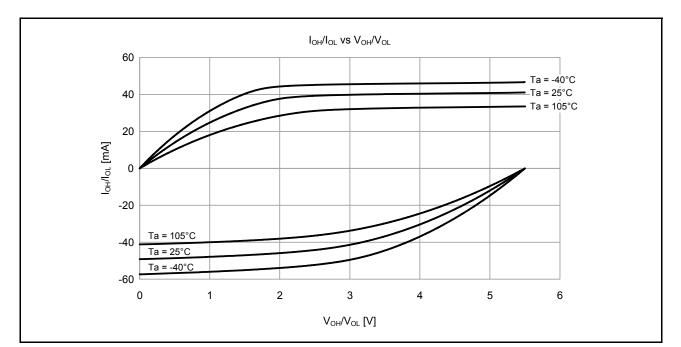

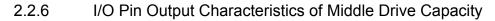

Figure 2.7 V<sub>OH</sub>/V<sub>OL</sub> and I<sub>OH</sub>/I<sub>OL</sub> Voltage Characteristics at Ta = 25°C When Middle drive output is Selected (Reference Data)

RENESAS

#### Table 2.11 Operating and standby current (1) (2/2)

Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| ltem                            |                                        |                                                            |                                                                              |                   | Symbol          | Typ* <sup>10</sup> | Мах   | Unit | Test conditions |

|---------------------------------|----------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------|-------------------|-----------------|--------------------|-------|------|-----------------|

| Supply<br>current* <sup>1</sup> | Low-speed<br>mode <sup>*3</sup>        | Normal mode                                                | All peripheral clock<br>disabled, code executing<br>from flash <sup>*5</sup> | ICLK = 1 MHz      | I <sub>CC</sub> | 0.5                | -     | mA   | *7              |

|                                 |                                        |                                                            | All peripheral clock<br>disabled, CoreMark code<br>executing from flash*5    | ICLK = 1 MHz      |                 | 0.7                | -     |      |                 |

|                                 |                                        |                                                            | All peripheral clock<br>enabled, code executing<br>from flash* <sup>5</sup>  | ICLK = 1 MHz      |                 | 1.5                | -     |      | *8              |

|                                 |                                        |                                                            | All peripheral clock<br>enabled, code executing<br>from SRAM* <sup>5</sup>   | ICLK = 1 MHz      |                 | -                  | 3.2   |      |                 |

|                                 |                                        | Sleep mode                                                 | All peripheral clock disabled*5                                              | ICLK = 1 MHz      |                 | 0.4                | -     |      | *7              |

|                                 |                                        |                                                            | All peripheral clock enabled*5                                               | ICLK = 1 MHz      |                 | 1.3                | -     |      | *8              |

| Low-voltage<br>mode*3           | ow-voltage Normal mode<br>ode*3        | All peripheral clock disabled, code executing from flash*5 | ICLK = 4 MHz                                                                 | I <sub>CC</sub>   | 2.5             | -                  | mA    | *7   |                 |

|                                 |                                        | Sleep mode                                                 | All peripheral clock<br>disabled, CoreMark code<br>executing from flash*5    | ICLK = 4 MHz      |                 | 3.0                | -     | -    |                 |

|                                 |                                        |                                                            | All peripheral clock<br>enabled, code executing<br>from flash* <sup>5</sup>  | ICLK = 4 MHz      |                 | 4.5                | -     |      | *8              |

|                                 |                                        |                                                            | All peripheral clock<br>enabled, code executing<br>from SRAM* <sup>5</sup>   | ICLK = 4 MHz      |                 | -                  | 11.2  |      |                 |

|                                 |                                        |                                                            | All peripheral clock disabled*5                                              | ICLK = 4 MHz      |                 | 2.0                | -     |      | *7              |

|                                 |                                        |                                                            | All peripheral clock enabled*5                                               | ICLK = 4 MHz      |                 | 4.0                | -     |      | *8              |

|                                 | Subosc-<br>speed<br>mode <sup>*4</sup> | Normal mode                                                | All peripheral clock disabled, code executing from flash*5                   | ICLK = 32.768 kHz | I <sub>CC</sub> | 13.5               | - μA  | μA   | *8              |

|                                 |                                        |                                                            | All peripheral clock<br>enabled, code executing<br>from flash* <sup>5</sup>  | ICLK = 32.768 kHz |                 | 25.0               | -     | -    |                 |

|                                 |                                        |                                                            | All peripheral clock<br>enabled, code executing<br>from SRAM* <sup>5</sup>   | ICLK = 32.768 kHz |                 | -                  | 214.1 |      |                 |

|                                 |                                        | Sleep mode                                                 | All peripheral clock disabled*5                                              | ICLK = 32.768 kHz | ]               | 9.5                | -     |      |                 |

|                                 |                                        |                                                            | All peripheral clock enabled*5                                               | ICLK = 32.768 kHz |                 | 21.0               | -     | 1    |                 |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. The clock source is HOCO.

Note 3.The clock source is MOCO.Note 4.The clock source is the sub-clock oscillator.

Note 5. This does not include BGO operation.

Note 6. This is the increase for programming or erasure of the ROM or flash memory for data storage during program execution.

Note 7. FCLK, BCLK, PCLKA, PCLKB, PCLKC and PCLKD are set to divided by 64.

Note 8. FCLK, BCLK, PCLKA, PCLKB, PCLKC and PCLKD are the same frequency as that of ICLK.

Note 9. FCLK, BCLK, and PCLKB are set to divided by 2 and PCLKA, PCLKC and PCLKD are the same frequency as that of ICLK. Note 10. VCC = 3.3 V.

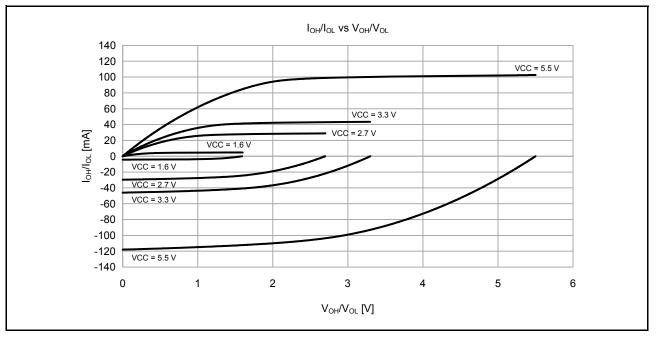

#### Figure 2.21 Voltage dependency in Subosc-speed mode (reference data)

| Table 2.12 | Operating and standby current (2) |

|------------|-----------------------------------|

|------------|-----------------------------------|

Conditions: VCC = AVCC0 = 1.6 to 5.5 V

| ltem      |                                        |                        | Symbol          | Typ*4 | Max   | Unit | Test conditions                                |

|-----------|----------------------------------------|------------------------|-----------------|-------|-------|------|------------------------------------------------|

| Supply    | Software Standby                       | T <sub>a</sub> = 25°C  | I <sub>CC</sub> | 0.9   | 6.0   | μA   | PSMCR.PSMC[1:0] = 01b (48-KB                   |

| current*1 | mode*2                                 | T <sub>a</sub> = 55°C  |                 | 1.6   | 12.2  |      | SRAM on)                                       |

|           |                                        | T <sub>a</sub> = 85°C  |                 | 4.8   | 27.1  |      |                                                |

|           |                                        | T <sub>a</sub> = 105°C |                 | 12.2  | 66.7  |      |                                                |

|           |                                        | T <sub>a</sub> = 25°C  |                 | 1.1   | 7.5   |      | PSMCR.PSMC[1:0] = 00b (All SRAM                |

|           |                                        | T <sub>a</sub> = 55°C  |                 | 2.2   | 17.0  |      | on)                                            |

|           |                                        | T <sub>a</sub> = 85°C  |                 | 7.5   | 43.3  |      |                                                |

|           |                                        | T <sub>a</sub> = 105°C | ]               | 19.6  | 105.9 |      |                                                |

|           | Increment for RTC<br>low-speed on-chip | •                      |                 | 0.5   | -     |      | -                                              |

|           | Increment for RTC sub-clock oscillator | •                      |                 | 0.5   | -     |      | SOMCR.SODRV[1:0] are 11b<br>(Low power mode 3) |

|           |                                        |                        |                 | 1.6   | -     |      | SOMCR.SODRV[1:0] are 00b<br>(Normal mode)      |

Note 1. Supply current values do not include output charge/discharge current from all pins. The values apply when internal pull-up MOSs are in the off state.

Note 2. The IWDT and LVD are not operating.

Note 3. Includes the current of sub-oscillation circuit or low-speed on-chip oscillator.

Note 4. VCC = 3.3 V.

| ltem      |                                       |              | Symbol | Min      | Тур | Max | Unit |

|-----------|---------------------------------------|--------------|--------|----------|-----|-----|------|

| Operation | System clock (ICLK)*4                 | 2.7 to 5.5 V | f      | 0.032768 | -   | 12  | MHz  |

| frequency |                                       | 2.4 to 2.7 V |        | 0.032768 | -   | 12  |      |

|           |                                       | 1.8 to 2.4 V |        | 0.032768 | -   | 8   |      |

|           | FlashIF clock (FCLK)*1, *2, *4        | 2.7 to 5.5 V |        | 0.032768 | -   | 12  |      |

|           |                                       | 2.4 to 2.7 V |        | 0.032768 | -   | 12  |      |

|           |                                       | 1.8 to 2.4 V |        | 0.032768 | -   | 8   |      |

|           | Peripheral module clock (PCLKA)*4     | 2.7 to 5.5 V |        | -        | -   | 12  |      |

|           |                                       | 2.4 to 2.7 V |        | -        | -   | 12  |      |

|           |                                       | 1.8 to 2.4 V |        | -        | -   | 8   |      |

|           | Peripheral module clock (PCLKB)*4     | 2.7 to 5.5 V |        | -        | -   | 12  |      |

|           |                                       | 2.4 to 2.7 V |        | -        | -   | 12  |      |

|           |                                       | 1.8 to 2.4 V |        | -        | -   | 8   |      |

|           | Peripheral module clock (PCLKC)*3, *4 | 2.7 to 5.5 V |        | -        | -   | 12  |      |

|           |                                       | 2.4 to 2.7 V |        | -        | -   | 12  |      |

|           |                                       | 1.8 to 2.4 V |        | -        | -   | 8   |      |

|           | Peripheral module clock (PCLKD)*4     | 2.7 to 5.5 V |        | -        | -   | 12  |      |

|           |                                       | 2.4 to 2.7 V |        | -        | -   | 12  |      |

|           |                                       | 1.8 to 2.4 V |        | -        | -   | 8   |      |

|           | External bus clock (BCLK)*4           | 2.7 to 5.5 V |        | -        | -   | 12  |      |

|           |                                       | 2.4 to 2.7 V |        | -        | -   | 12  |      |

|           |                                       | 1.8 to 2.4 V |        | -        | -   | 8   |      |

|           | EBCLK pin output                      | 2.7 to 3.6 V | 1      | -        | -   | 12  |      |

|           |                                       | 2.4 to 2.7 V | 1      | -        | -   | 8   |      |

|           |                                       | 1.8 to 2.4 V | 1      | -        | -   | 8   |      |

#### Table 2.18 Operation frequency value in middle-speed mode

Conditions: VCC = AVCC0 = 1.8 to 5.5 V

Note 1. The lower-limit frequency of FCLK is 1 MHz while programming or erasing the flash memory. When using FCLK for programming or erasing the flash memory at below 4 MHz, the frequency can be set to 1 MHz, 2 MHz, or 3 MHz. A non-integer frequency such as 1.5 MHz cannot be set.

Note 2. The frequency accuracy of FCLK must be ±3.5% while programming or erasing the flash memory. Confirm the frequency accuracy of the clock source.

Note 3. The lower-limit frequency of PCLKC is 4 MHz at 2.4 V or above and 1 MHz at below 2.4 V when the 14-bit A/D converter is in use.

Note 4. See section 9, Clock Generation Circuit in User's Manual for the relationship of frequencies between ICLK, PCLKA, PCLKB, PCLKC, PCLKD, FCLK, and BCLK.

| Table 2.19      | Operation frequency value in low-speed mode |

|-----------------|---------------------------------------------|

| Conditions: VCC | = AVCC0 = 1.8 to 5.5 V                      |

| ltem      |                                       |              | Symbol | Min      | Тур | Max | Unit |

|-----------|---------------------------------------|--------------|--------|----------|-----|-----|------|

| Operation | System clock (ICLK)*3                 | 1.8 to 5.5 V | f<br>  | 0.032768 | -   | 1   | MHz  |

| frequency | FlashIF clock (FCLK)*1, *3            | 1.8 to 5.5 V |        | 0.032768 | -   | 1   |      |

|           | Peripheral module clock (PCLKA)*3     | 1.8 to 5.5 V |        | -        | -   | 1   |      |

|           | Peripheral module clock (PCLKB)*3     | 1.8 to 5.5 V |        | -        | -   | 1   |      |

|           | Peripheral module clock (PCLKC)*2, *3 | 1.8 to 5.5 V |        | -        | -   | 1   |      |

|           | Peripheral module clock (PCLKD)*3     | 1.8 to 5.5 V |        | -        | -   | 1   |      |

|           | External bus clock (BCLK)*3           | 1.8 to 5.5 V | 1      | -        | -   | 1   |      |

|           | EBCLK pin output                      | 1.8 to 5.5 V | 1      | -        | -   | 1   |      |

Note 1. The lower-limit frequency of FCLK is 1 MHz while programming or erasing the flash memory.

Note 2. The lower-limit frequency of PCLKC is 1 MHz when the A/D converter is in use.

Note 3. See section 9, Clock Generation Circuit in User's Manual for the relationship of frequencies between ICLK, PCLKA, PCLKB, PCLKC, PCLKD, FCLK, and BCLK.

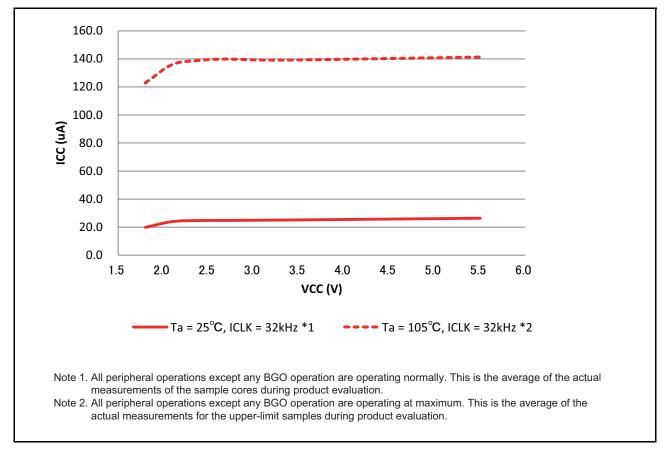

## 2.3.2 Clock Timing

### Table 2.22Clock timing (1/2)

| Item                                   | Symbol               | Min                | Тур     | Max    | Unit    | Test conditions |                 |

|----------------------------------------|----------------------|--------------------|---------|--------|---------|-----------------|-----------------|

| EBCLK pin output cycle time            | VCC = 2.7 V or above | t <sub>Bcyc</sub>  | 83.3    | -      | -       | ns              | Figure 2.26     |

|                                        | VCC = 1.8 V or above | -                  | 125     | -      | -       |                 |                 |

|                                        | VCC = 1.6 V or above |                    | 500     | -      | -       |                 |                 |

| EBCLK pin output high pulse            | VCC = 2.7 V or above | t <sub>CH</sub>    | 20      | -      | -       | ns              |                 |

| width                                  | VCC = 1.8 V or above | -                  | 30      | -      | -       |                 |                 |

|                                        | VCC = 1.6 V or above |                    | 150     | -      | -       |                 |                 |

| EBCLK pin output low pulse width       | VCC = 2.7 V or above | t <sub>CL</sub>    | 20      | -      | -       | ns              |                 |

|                                        | VCC = 1.8 V or above |                    | 30      | -      | -       |                 |                 |

|                                        | VCC = 1.6 V or above |                    | 150     | -      | -       |                 |                 |

| EBCLK pin output rise time             | VCC = 2.7 V or above | t <sub>Cr</sub>    | -       | -      | 15      | ns              |                 |

|                                        | VCC = 2.4 V or above |                    | -       | -      | 25      |                 |                 |

|                                        | VCC = 1.8 V or above |                    | -       | -      | 30      |                 |                 |

|                                        | VCC = 1.6 V or above | -                  | -       | -      | 50      |                 |                 |

| EBCLK pin output fall time             | VCC = 2.7 V or above | t <sub>Cf</sub>    | -       | -      | 15      | ns              |                 |

|                                        | VCC = 2.4 V or above |                    | -       | -      | 25      |                 |                 |

|                                        | VCC = 1.8 V or above | -                  | -       | -      | 30      |                 |                 |

|                                        | VCC = 1.6 V or above |                    | -       | -      | 50      |                 |                 |

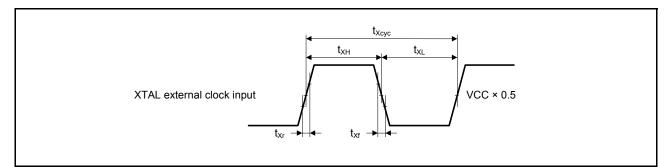

| EXTAL external clock input cycle til   | me                   | t <sub>Xcyc</sub>  | 50      | -      | -       | ns              | Figure 2.27     |

| EXTAL external clock input high pu     | lse width            | t <sub>XH</sub>    | 20      | -      | -       | ns              |                 |

| EXTAL external clock input low pul     | se width             | t <sub>XL</sub>    | 20      | -      | -       | ns              |                 |

| EXTAL external clock rising time       |                      | t <sub>Xr</sub>    | -       | -      | 5       | ns              |                 |

| EXTAL external clock falling time      |                      | t <sub>Xf</sub>    | -       | -      | 5       | ns              |                 |

| EXTAL external clock input wait tim    | ie*1                 | t <sub>EXWT</sub>  | 0.3     | -      | -       | μs              | -               |

| EXTAL external clock input frequer     | су                   | f <sub>EXTAL</sub> | -       | -      | 20      | MHz             | 2.4 ≤ VCC ≤ 5.5 |

|                                        |                      |                    | -       | -      | 8       |                 | 1.8 ≤ VCC < 2.4 |

|                                        |                      |                    | -       | -      | 1       |                 | 1.6 ≤ VCC < 1.8 |

| Main clock oscillator oscillation free | quency               | f <sub>MAIN</sub>  | 1       | -      | 20      | MHz             | 2.4 ≤ VCC ≤ 5.5 |

|                                        |                      |                    | 1       | -      | 8       |                 | 1.8 ≤ VCC < 2.4 |

|                                        |                      | 1                  | -       | 4      |         | 1.6 ≤ VCC < 1.8 |                 |

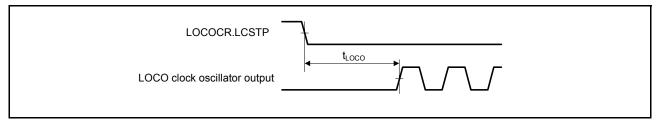

| LOCO clock oscillation frequency       |                      | fLOCO              | 27.8528 | 32.768 | 37.6832 | kHz             | -               |

| LOCO clock oscillation stabilization   | tLOCO                | -                  | -       | 100    | μs      | Figure 2.28     |                 |

| IWDT-dedicated clock oscillation fr    | equency              | filoco             | 12.75   | 15     | 17.25   | kHz             | -               |

| MOCO clock oscillation frequency       |                      | f <sub>MOCO</sub>  | 6.8     | 8      | 9.2     | MHz             | -               |

| MOCO clock oscillation stabilization   | n time               | t <sub>MOCO</sub>  | -       | -      | 1       | μs              | -               |

### Figure 2.27 XTAL external clock input timing

Figure 2.28 LOCO clock oscillation start timing

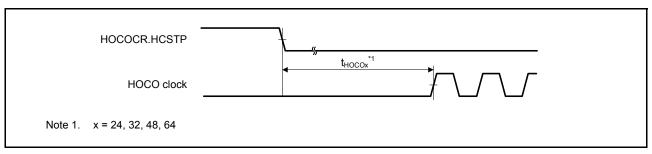

Figure 2.29 HOCO clock oscillation start timing (started by setting HOCOCR.HCSTP bit)

S3A7

## 2.3.6 Bus Timing

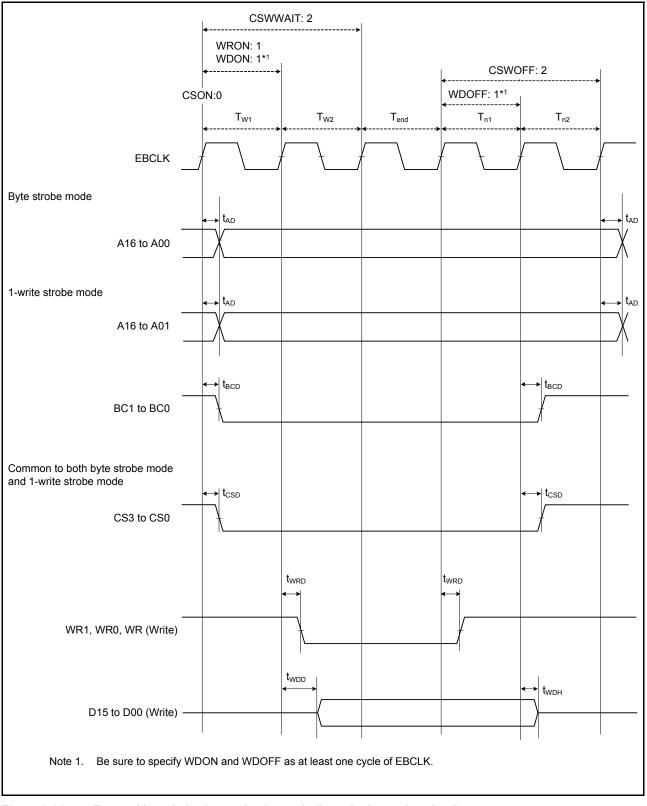

#### Table 2.31Bus timing (1)

Conditions: EBCLK pin ≤ 12 MHz (package with 145 to 100 pins) (BCLK: up to 24 MHz)

VCC = AVCC0 = 2.7 to 5.5 V

Output load conditions: V<sub>OH</sub> = VCC × 0.5, V<sub>OL</sub> = VCC × 0.5, C = 30 pF

| Item                 | Symbol           | Min | Max | Unit | Test conditions |

|----------------------|------------------|-----|-----|------|-----------------|

| Address delay        | t <sub>AD</sub>  | -   | 55  | ns   | Figure 2.38     |

| Byte control delay   | t <sub>BCD</sub> | -   | 55  | ns   | to Figure 2.41  |

| CS delay             | t <sub>CSD</sub> | -   | 55  | ns   |                 |

| RD delay             | t <sub>RSD</sub> | -   | 55  | ns   |                 |

| Read data setup time | t <sub>RDS</sub> | 37  | -   | ns   |                 |

| Read data hold time  | t <sub>RDH</sub> | 0   | -   | ns   |                 |

| WR delay             | t <sub>WRD</sub> | -   | 55  | ns   |                 |

| Write data delay     | t <sub>WDD</sub> | -   | 55  | ns   |                 |

| Write data hold time | t <sub>WDH</sub> | 0   | -   | ns   |                 |

| WAIT setup time      | t <sub>WTS</sub> | 37  | -   | ns   | Figure 2.42     |

| WAIT hold time       | t <sub>WTH</sub> | 0   | -   | ns   |                 |

#### Table 2.32 Bus timing (2)

Conditions: EBCLK pin  $\leq$  8 MHz (package with 145 to 100 pins) (BCLK: up to 8 MHz) VCC = AVCC0 = 2.4 to 2.7 V

Output load conditions:  $V_{OH}$  = VCC × 0.5,  $V_{OL}$  = VCC × 0.5, C = 30 pF

| ltem                 | Symbol           | Min | Max | Unit | Test conditions |

|----------------------|------------------|-----|-----|------|-----------------|

| Address delay        | t <sub>AD</sub>  | -   | 55  | ns   | Figure 2.38     |

| Byte control delay   | t <sub>BCD</sub> | -   | 55  | ns   | to Figure 2.41  |

| CS delay             | t <sub>CSD</sub> | -   | 55  | ns   |                 |

| RD delay             | t <sub>RSD</sub> | -   | 55  | ns   |                 |

| Read data setup time | t <sub>RDS</sub> | 45  | -   | ns   |                 |

| Read data hold time  | t <sub>RDH</sub> | 0   | -   | ns   |                 |

| WR delay             | t <sub>WRD</sub> | -   | 55  | ns   |                 |

| Write data delay     | t <sub>WDD</sub> | -   | 55  | ns   |                 |

| Write data hold time | t <sub>WDH</sub> | 0   | -   | ns   |                 |

| WAIT setup time      | t <sub>WTS</sub> | 45  | -   | ns   | Figure 2.42     |

| WAIT hold time       | t <sub>WTH</sub> | 0   | -   | ns   |                 |

### Table 2.33 Bus timing (3)

Conditions: EBCLK pin  $\leq$  4 MHz (package with 145 to 100 pins) (BCLK: up to 4 MHz)

VCC = AVCC0 = 1.8 to 2.4 V Output load conditions:  $V_{OH}$  = VCC × 0.5,  $V_{OL}$  = VCC × 0.5, C = 30 pF

| ltem                 | Symbol           | Min | Max | Unit | Test conditions |

|----------------------|------------------|-----|-----|------|-----------------|

| Address delay        | t <sub>AD</sub>  | -   | 90  | ns   | Figure 2.38     |

| Byte control delay   | t <sub>BCD</sub> | -   | 90  | ns   | to Figure 2.41  |

| CS delay             | t <sub>CSD</sub> | -   | 90  | ns   |                 |

| RD delay             | t <sub>RSD</sub> | -   | 90  | ns   |                 |

| Read data setup time | t <sub>RDS</sub> | 70  | -   | ns   |                 |

| Read data hold time  | t <sub>RDH</sub> | 0   | -   | ns   |                 |

| WR delay             | t <sub>WRD</sub> | -   | 90  | ns   |                 |

| Write data delay     | t <sub>WDD</sub> | -   | 90  | ns   |                 |

| Write data hold time | t <sub>WDH</sub> | 0   | -   | ns   |                 |

Figure 2.39 External bus timing/normal write cycle (bus clock synchronized)

#### Table 2.40 SPI timing (2/2)

Conditions: Middle drive output is selected in the Drive Strength Control in PmnPFS register -

| m |                               |             |                              | Symbol                                            | Min                   | Мах                         | Unit <sup>*1</sup> | Test conditions                      |

|---|-------------------------------|-------------|------------------------------|---------------------------------------------------|-----------------------|-----------------------------|--------------------|--------------------------------------|

| I | Data output delay             | Master      | 2.7 V or above               | t <sub>OD</sub>                                   | -                     | 14                          | ns                 | Figure 2.58 to                       |

|   |                               |             | 2.4 V or above               |                                                   | -                     | 20                          |                    | Figure 2.63<br>C = 30 <sub>P</sub> F |

|   |                               |             | 1.8 V or above               |                                                   | -                     | 25                          |                    | С – Збрі                             |

|   |                               |             | 1.6 V or above               |                                                   | -                     | 30                          |                    |                                      |

|   |                               | Slave       | 2.7 V or above               |                                                   | -                     | 50                          |                    |                                      |

|   |                               |             | 2.4 V or above               |                                                   | -                     | 60                          |                    |                                      |

|   |                               |             | 1.8 V or above               |                                                   | -                     | 85                          |                    |                                      |

|   |                               |             | 1.6 V or above               |                                                   | -                     | 110                         |                    |                                      |

|   | Data output hold              | Master      |                              | t <sub>OH</sub>                                   | 0                     | -                           | ns                 | IS                                   |

|   | time                          | Slave       |                              |                                                   | 0                     | -                           |                    |                                      |

|   | Successive transmission delay | i delay     | $t_{SPcyc}$ + 2 × $t_{Pcyc}$ | 8 × t <sub>SPcyc</sub><br>+ 2 × t <sub>Pcyc</sub> | ns                    |                             |                    |                                      |

|   | MOSI and MISO                 | Slave       | Slave                        |                                                   | 6 × t <sub>Pcyc</sub> | -                           |                    |                                      |

|   |                               | Output      | 2.7 V or above               | t <sub>Dr,</sub> t <sub>Df</sub>                  | -                     | 10                          | ns                 |                                      |

|   | rise and fall time            | d fall time | 2.4 V or above               | _                                                 | -                     | 15                          |                    |                                      |

|   |                               |             | 1.8 V or above               |                                                   | -                     | 20                          |                    |                                      |

|   |                               |             | 1.6 V or above               |                                                   | -                     | 30                          |                    |                                      |

|   |                               | Input       |                              |                                                   | -                     | 1                           | μs                 |                                      |

|   | SSL rise and fall             | Output      | 2.7 V or above               | t <sub>SSLr,</sub>                                | -                     | 10                          | ns                 |                                      |

|   | time                          |             | 2.4 V or above               | t <sub>SSLf</sub>                                 | -                     | 15                          |                    |                                      |

|   |                               |             | 1.8 V or above               |                                                   | -                     | 20                          |                    |                                      |

|   |                               |             | 1.6 V or above               |                                                   | -                     | 30                          |                    |                                      |

|   |                               | Input       |                              |                                                   | -                     | 1                           | μs                 |                                      |

|   | Slave access time             |             | 2.7 V or above               | t <sub>SA</sub>                                   | -                     | 2 × t <sub>Pcyc</sub> + 50  | ns                 | Figure 2.62 and                      |

|   |                               |             | 2.4 V or above               |                                                   | -                     | 2 × t <sub>Pcyc</sub> + 60  |                    | Figure 2.63<br>C = $30_{P}F$         |

|   | Slave output release          |             | 1.8 V or above               |                                                   | -                     | 2 × t <sub>Pcyc</sub> + 85  |                    | С – ЗОРГ                             |

|   |                               |             | 1.6 V or above               |                                                   | -                     | 2 × t <sub>Pcyc</sub> + 110 |                    |                                      |

|   |                               | time        | 2.7 V or above               | t <sub>REL</sub>                                  | -                     | $2 \times t_{Pcyc} + 50$    | ns                 |                                      |

|   |                               |             | 2.4 V or above               |                                                   | -                     | $2 \times t_{Pcyc} + 60$    |                    |                                      |

|   |                               |             | 1.8 V or above               |                                                   | -                     | 2 × t <sub>Pcyc</sub> + 85  |                    |                                      |

|   |                               |             | 1.6 V or above               |                                                   | -                     | 2 × t <sub>Pcyc</sub> + 110 |                    |                                      |

Note 1. t<sub>Pcyc</sub>: PCLKA cycle.

Note 2. N is set as an integer from 1 to 8 by the SPCKD register. Note 3. N is set as an integer from 1 to 8 by the SSLND register.

## 2.5 ADC14 Characteristics

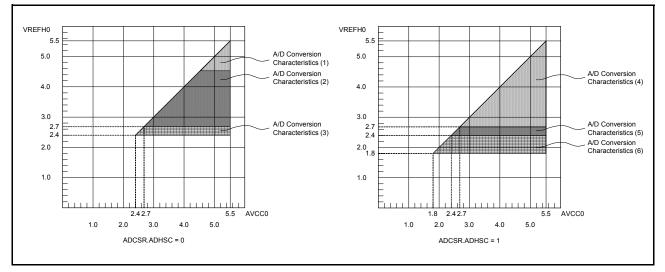

Figure 2.76 AVCC0 to VREFH0 voltage range

#### Table 2.48 A/D conversion characteristics (1) in high-speed mode (1/2)

Conditions: VCC = AVCC0 = 4.5 to 5.5 V, VREFH0 = 4.5 to 5.5 V, VSS = AVSS0 = VREFL0 = 0V Reference voltage range applied to the VREFH0 and VREFL0.

| Item                                                  |                                         |        | Min  | Тур   | Max    | Unit | Test conditions                                                       |

|-------------------------------------------------------|-----------------------------------------|--------|------|-------|--------|------|-----------------------------------------------------------------------|

| Frequency                                             |                                         |        | 1    | -     | 64     | MHz  | -                                                                     |

| Analog input capacitand                               | e                                       | Cs     | -    | -     | 15     | pF   | High-precision channel                                                |

|                                                       |                                         |        | -    | -     | 30     | pF   | Normal-precision channel                                              |

| Analog input resistance                               |                                         | Rs     | -    | -     | 2.5    | kΩ   | -                                                                     |

| Analog input voltage rai                              | nge                                     | Ain    | 0    | -     | VREFH0 | V    | -                                                                     |

| 12-bit mode                                           |                                         |        |      |       |        |      |                                                                       |

| Resolution                                            |                                         |        | -    | -     | 12     | Bit  | -                                                                     |

| Conversion time*1<br>(Operation at<br>PCLKC = 64 MHz) | Permissible<br>source imp<br>Max. = 0.3 | edance | 0.70 | -     | -      | μs   | High-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 0Dh   |

|                                                       |                                         |        | 1.13 | -     | -      | μs   | Normal-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                          | •                                       |        | -    | ±0.5  | ±4.5   | LSB  | High-precision channel                                                |

|                                                       |                                         |        |      |       | ±6.0   | LSB  | Other than above                                                      |

| Full-scale error                                      |                                         |        | -    | ±0.75 | ±4.5   | LSB  | High-precision channel                                                |

|                                                       |                                         |        |      |       | ±6.0   | LSB  | Other than above                                                      |

| Quantization error                                    |                                         |        | -    | ±0.5  | -      | LSB  | -                                                                     |

| Absolute accuracy                                     |                                         |        | -    | ±1.25 | ±5.0   | LSB  | High-precision channel                                                |

|                                                       |                                         |        |      |       | ±8.0   | LSB  | Other than above                                                      |

| DNL differential nonline                              | arity error                             |        | -    | ±1.0  | -      | LSB  | -                                                                     |

| INL integral nonlinearity                             | error                                   |        | -    | ±1.0  | ±3.0   | LSB  | -                                                                     |

| 14-bit mode                                           |                                         |        |      | •     |        | •    |                                                                       |

| Resolution                                            |                                         |        | -    | -     | 14     | Bit  | -                                                                     |

#### Table 2.49 A/D conversion characteristics (2) in high-speed mode (2/2)

Conditions: VCC = AVCC0 = 2.7 to 5.5 V, VREFH0 = 2.7 to 5.5 V, VSS = AVSS0 = VREFL0 = 0V Reference voltage range applied to the VREFH0 and VREFL0.

| Item                                                              |                                                         | Min  | Тур  | Max   | Unit | Test conditions                                                       |

|-------------------------------------------------------------------|---------------------------------------------------------|------|------|-------|------|-----------------------------------------------------------------------|

| Conversion time* <sup>1</sup><br>(Operation at<br>PCLKC = 48 MHz) | Permissible signal<br>source impedance<br>Max. = 0.3 kΩ | 1.06 | -    | -     | μs   | High-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 0Dh   |

|                                                                   |                                                         | 1.63 | -    | -     | μs   | Normal-precision channel<br>ADCSR.ADHSC = 0<br>ADSSTRn.SST[7:0] = 28h |

| Offset error                                                      |                                                         | -    | ±2.0 | ±18   | LSB  | High-precision channel                                                |

|                                                                   |                                                         |      |      | ±24.0 | LSB  | Other than above                                                      |

| Full-scale error                                                  |                                                         | -    | ±3.0 | ±18   | LSB  | High-precision channel                                                |

|                                                                   |                                                         |      |      | ±24.0 | LSB  | Other than above                                                      |

| Quantization error                                                |                                                         | -    | ±0.5 | -     | LSB  | -                                                                     |

| Absolute accuracy                                                 |                                                         | -    | ±5.0 | ±20   | LSB  | High-precision channel                                                |

|                                                                   |                                                         |      |      | ±32.0 | LSB  | Other than above                                                      |

| DNL differential nonline                                          | earity error                                            | -    | ±4.0 | -     | LSB  | -                                                                     |

| INL integral nonlinearit                                          | y error                                                 | -    | ±4.0 | ±12.0 | LSB  | -                                                                     |

Note: The characteristics apply when no pin functions other than 14-bit A/D converter input are used. Absolute accuracy does not include quantization errors. Offset error, full-scale error, DNL differential nonlinearity error, and INL integral nonlinearity error do not include quantization errors.

Note 1. The conversion time is the sum of the sampling time and the comparison time. The number of sampling states is indicated for the test conditions.

#### Table 2.50 A/D conversion characteristics (3) in high-speed mode (1/2)

Conditions: VCC = AVCC0 = 2.4 to 5.5 V, VREFH0 = 2.4 to 5.5 V, VSS = AVSS0 = VREFL0 = 0V Reference voltage range applied to the VREFH0 and VREFL0.

| Item                                                  |                                                |       | Min  | Тур   | Max    | Unit | Test conditions                                                       |  |

|-------------------------------------------------------|------------------------------------------------|-------|------|-------|--------|------|-----------------------------------------------------------------------|--|

| Frequency                                             |                                                |       | 1    | -     | 32     | MHz  | -                                                                     |  |

| Analog input capacitand                               | ce (                                           | Cs    | -    | -     | 15     | pF   | High-precision channel                                                |  |

|                                                       |                                                |       | -    | -     | 30     | pF   | Normal-precision channel                                              |  |

| Analog input resistance                               | e l                                            | Rs    | -    | -     | 2.5    | kΩ   | -                                                                     |  |