Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| <b>Details</b> Product Status | Obsolete                                                  |

|-------------------------------|-----------------------------------------------------------|

|                               | Obsolete                                                  |

|                               |                                                           |

| Core Processor                | HC08                                                      |

| Core Size                     | 8-Bit                                                     |

| Speed                         | -                                                         |

| Connectivity                  | -                                                         |

| Peripherals                   | -                                                         |

| Number of I/O                 | -                                                         |

| Program Memory Size           | 6KB (6K x 8)                                              |

| Program Memory Type           | FLASH                                                     |

| EEPROM Size                   | -                                                         |

| RAM Size                      | -                                                         |

| Voltage - Supply (Vcc/Vdd)    | -                                                         |

| Data Converters               | -                                                         |

| Oscillator Type               | External                                                  |

| Operating Temperature         | -40°C ~ 85°C (TA)                                         |

| Mounting Type                 | Surface Mount                                             |

| Package / Case                | 16-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package       | 16-SOIC                                                   |

| Purchase URL                  | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc908ql3cdwe |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| l able of | Contents                                                      |            |

|-----------|---------------------------------------------------------------|------------|

| 8.6       | IRQ Module During Break Interrupts                            | 86         |

| 8.7       | I/O Signals                                                   | 86         |

| 8.7.1     | IRQ Input Pins (IRQ)                                          | 86         |

| 8.8       | Registers                                                     | 87         |

|           | Chantar 0                                                     |            |

|           | Chapter 9 Keyboard Interrupt Module (KBI)                     |            |

| 9.1       | Introduction                                                  | 89         |

| 9.2       | Features                                                      |            |

| 9.3       | Functional Description                                        |            |

| 9.3.1     | Keyboard Operation                                            |            |

| 9.3.1.1   | MODEK = 1                                                     |            |

| 9.3.1.2   |                                                               |            |

| 9.3.2     | Keyboard Initialization                                       | 92         |

| 9.4       | Interrupts                                                    | 92         |

| 9.5       | Low-Power Modes                                               | 93         |

| 9.5.1     | Wait Mode                                                     |            |

| 9.5.2     | Stop Mode                                                     |            |

| 9.6       | KBI During Break Interrupts                                   | 93         |

| 9.7       | I/O Signals                                                   | 93         |

| 9.7.1     | KBI Input Pins (KBI5:KBI0)                                    |            |

| 9.8       | Registers                                                     | 93         |

| 9.8.1     | Keyboard Status and Control Register (KBSCR)                  |            |

| 9.8.2     | Keyboard Interrupt Enable Register (KBIER)                    | 95         |

| 9.8.3     | Keyboard Interrupt Polarity Register (KBIPR)                  | 95         |

|           | Chapter 10                                                    |            |

|           | Low-Voltage Inhibit (LVI)                                     |            |

| 10.1      | Introduction                                                  | 97         |

| 10.2      | Features                                                      | 97         |

| 10.3      | Functional Description                                        | 97         |

| 10.3.1    | Polled LVI Operation                                          |            |

| 10.3.2    | Forced Reset Operation                                        |            |

| 10.3.3    | LVI Hysteresis                                                | 98         |

| 10.3.4    | LVI Trip Selection                                            | 98         |

| 10.4      | LVI Interrupts                                                | 99         |

| 10.5      | Low-Power Modes                                               | 99         |

| 10.5.1    | Wait Mode                                                     | 99         |

| 10.5.2    | Stop Mode                                                     | 99         |

| 10.6      | Registers                                                     | 99         |

|           | Chapter 11                                                    |            |

|           | Oscillator Module (OSC)                                       |            |

| 11.1      | Introduction                                                  | 01         |

| 11.2      | Features1                                                     |            |

| 11.3      | Functional Description                                        |            |

|           | - anotonal Bosonphon                                          | <b>J</b> 1 |

|           | MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6 |            |

|           | moderiouseer moderiouseer moderiouseer bata dilect, liev. o   |            |

## **Table of Contents**

| 14.7.1       SLCTX — SLIC Transmit Pin.       139         14.7.2       SLCRX — SLIC Receive Pin.       139         14.8.1       SLIC Control Register 1       139         14.8.2       SLIC Control Register 2       140         14.8.3       SLIC Status Register       141         14.8.4       SLIC Bit Time Registers       142         14.8.5       SLIC Bit Time Registers       143         14.8.6       SLIC State Vector Register       144         14.8.6.1       LIN Mode Operation       144         14.8.6.2       Byte Transfer Mode Operation       144         14.8.7       SLIC Data Length Code Register       144         14.8.8       SLIC Identifier and Data Registers       149         14.9.9       Initialization/Application Information       150         14.9.1       LIN Message Frame Header       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field       150         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6.1       LIN Mose Initialization Procedure       151         14.9.6.2       Byte Transfer Mode Initialization       152                                                                                                     | 14.6 SLI  | IC During Break Interrupts              | 138 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------|-----|

| 14.7.2       SLCRX — SLIC Receive Pin       133         14.8. Registers       139         14.8.1       SLIC Control Register 1       139         14.8.2       SLIC Control Register 2       140         14.8.3       SLIC Prescaler Register       142         14.8.5       SLIC Bit Time Registers       142         14.8.5       SLIC Bit Time Registers       143         14.8.6.1       LIN Mode Operation       144         14.8.6.2       Byte Transfer Mode Operation       144         14.8.7       SLIC Data Length Code Register       148         14.8.8       SLIC Identifier and Data Registers       149         14.9.1       In Message Frame Header       150         14.9.1       LIN Data Field       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field       150         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7.1       LIN Message Headers       153         14.9.9.8       Handling Command                                                                                                                | 14.7 I/O  | Signals                                 | 139 |

| 14.7.2       SLCRX — SLIC Receive Pin       133         14.8. Registers       139         14.8.1       SLIC Control Register 1       139         14.8.2       SLIC Control Register 2       140         14.8.3       SLIC Prescaler Register       142         14.8.5       SLIC Bit Time Registers       142         14.8.5       SLIC Bit Time Registers       143         14.8.6.1       LIN Mode Operation       144         14.8.6.2       Byte Transfer Mode Operation       144         14.8.7       SLIC Data Length Code Register       148         14.8.8       SLIC Identifier and Data Registers       149         14.9.1       In Message Frame Header       150         14.9.1       LIN Data Field       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field       150         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7.1       LIN Message Headers       153         14.9.9.8       Handling Command                                                                                                                | 14.7.1    |                                         |     |

| 14.8.1     Registers     139       14.8.1     SLIC Control Register 1     139       14.8.2     SLIC Control Register 2     140       14.8.3     SLIC Status Register     141       14.8.4     SLIC Bit Time Registers     142       14.8.5     SLIC Bit Time Registers     144       14.8.6     SLIC State Vector Register     144       14.8.6.1     LIN Mode Operation     147       14.8.7     SLIC Identifier and Dode Register     144       14.8.8     SLIC Identifier and Data Registers     148       14.9     Initialization/Application Information     150       14.9.1     LIN Message Frame Header     150       14.9.2     LIN Data Field     150       14.9.3     LIN Checksum Field     151       14.9.4     SLIC Module Constraints     151       14.9.5     SLCSV Interrupt Handling     151       14.9.6     SLIC Module Initialization Procedure     151       14.9.6.1     LIN Mode Initialization Procedure     151       14.9.6.2     Byte Transfer Mode Initialization     151       14.9.7.2     Possible Errors on Message Frames     152       14.9.9.8     Handling LIN Message Headers     152       14.9.9.8     Handling Request LIN Message Frames     155                                                                                                    | 14.7.2    |                                         |     |

| 14.8.1       SLIC Control Register 1.       138         14.8.2       SLIC Control Register 2.       140         14.8.3       SLIC Status Register.       141         14.8.4       SLIC Pescaler Register.       142         14.8.5       SLIC Bit Time Registers.       142         14.8.6       SLIC State Vector Register       144         14.8.6.1       LIN Mode Operation       144         14.8.6.2       Byte Transfer Mode Operation       144         14.8.7       SLIC Data Length Code Register       148         14.8.8       SLIC Identifier and Data Registers.       149         14.9       Initialization/Application Information.       150         14.9.1       LIN Message Frame Header       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field       151         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6.1       LIN Mossage Headers       151         14.9.6.2       Byte Transfer Mode Initialization       151         14.9.7.1       LIN Message Headers       152         14.9.7.2       Possible Errors on Message Frames       155      <                                                                                                   | 14.8 Re   |                                         |     |

| 14.8.2       SLIC Control Register 2       140         14.8.3       SLIC Status Register       141         14.8.5       SLIC Bit Time Registers       142         14.8.6       SLIC State Vector Register       144         14.8.6.1       LIN Mode Operation       144         14.8.6.2       Byte Transfer Mode Operation       147         14.8.7       SLIC Data Length Code Register       148         14.8.8       SLIC Identifier and Data Registers       148         14.9.1       LIN Message Frame Header       150         14.9.1       LIN Data Field       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field       151         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6       LIN Mode Initialization Procedure       151         14.9.6       Byte Transfer Mode Initialization       151         14.9.7       Handling IM Message Headers       152         14.9.7.1       LIN Message Headers       153         14.9.9.2       Possible Errors on Message Frames       155 <t< td=""><td></td><td></td><td></td></t<>                                                                |           |                                         |     |

| 14.8.3     SLIC Status Register     141       14.8.4     SLIC Prescaler Register     142       14.8.5     SLIC Bit Time Registers     143       14.8.6.0     SLIC State Vector Register     144       14.8.6.1     LIN Mode Operation     144       14.8.7     SLIC Data Length Code Register     148       14.8.7     SLIC Identifier and Data Registers     149       14.9     Initialization/Application Information     150       14.9.1     LIN Message Frame Header     150       14.9.2     LIN Data Field     150       14.9.3     LIN Checksum Field     150       14.9.4     SLIC Module Constraints     151       14.9.5     SLCSV Interrupt Handling     151       14.9.6.1     LIN Mode Initialization Procedure     151       14.9.6.2     Byte Transfer Mode Initialization     152       14.9.7.1     LIN Message Headers     152       14.9.7.2     Possible Errors on Message Headers     154       14.9.7.2     Possible Errors on Message Frames     155       14.9.8.1     Standard Command Message Frames     155       14.9.8.2     Extended Command Message Frames     155       14.9.9.2     Extended Request Message Frames     156       14.9.9.3     Transmit Abort     161 <td>_</td> <td></td> <td></td>                                                        | _         |                                         |     |

| 14.8.4       SLIC Prescaler Registers.       142         14.8.5       SLIC Bit Time Registers.       143         14.8.6       SLIC State Vector Register       144         14.8.6.1       LIN Mode Operation       144         14.8.6.2       Byte Transfer Mode Operation       147         14.8.7       SLIC Data Length Code Register.       148         14.8.8       SLIC Identifier and Data Registers.       149         14.9.1       LIN Message Frame Header       150         14.9.1       LIN Data Field       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field.       151         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.1       LIN Mode Initialization Procedure       151         14.9.6.2       Byte Transfer Mode Initialization       151         14.9.7.1       LIN Message Headers       153         14.9.7.2       Possible Errors on Message Frames       155         14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames                                                                                        | _         |                                         |     |

| 14.8.5       SLIC Bit Time Registers.       143         14.8.6.1       LIN Mode Operation       144         14.8.6.2       Byte Transfer Mode Operation       147         14.8.7       SLIC Data Length Code Register       148         14.8.8       SLIC Identifier and Data Registers.       149         14.9.1       Initialization/Application Information.       150         14.9.1       LIN Message Frame Header       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field.       151         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7.1       LIN Message Headers       153         14.9.7.2       Possible Errors on Message Frames       155         14.9.8.3       Handling Command Message Frames       155         14.9.8.3       Possible Errors on Command Message Frames       155         14.9.9.1       Standard Command Message Frames       156         14.9.9.2       Extended Request Message Frames       158         14.9.9.1                                                                               |           |                                         |     |

| 14.8.6.5       SLIC State Vector Register       144         14.8.6.1       LIN Mode Operation       144         14.8.7       SLIC Data Length Code Register.       148         14.8.8       SLIC Identifier and Data Registers.       149         14.9.1       Initialization/Application Information       150         14.9.1       LIN Message Frame Header       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field       151         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.1       LIN Mode Initialization Procedure       151         14.9.6.2       LIN Mode Initialization       152         14.9.7       Handling LIN Message Headers       153         14.9.7.1       LIN Message Headers       153         14.9.8.2       Handling Command Message Frames       155         14.9.8.3       Standard Command Message Frames       155         14.9.8.1       Standard Command Message Frames       155         14.9.9.2       Handling Request LIN Message Frames       158         14.9.9.3       Transmit Ab                                                                            |           |                                         |     |

| 14.8.6.1       LIN Mode Operation       144         14.8.6.2       Byte Transfer Mode Operation       147         14.8.7       SLIC Data Length Code Register.       148         14.8.8       SLIC Identifier and Data Registers.       149         14.9.1       Initialization/Application Information       150         14.9.1       LIN Message Frame Header       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field       151         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.1       LIN Mode Initialization Procedure       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7.1       Handling LIN Message Headers       153         14.9.7.2       Possible Errors on Message Headers       153         14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames       155         14.9.8.3       Possible Errors on Command Message Data       158         14.9.9.1       Standard Request Message Frames       158         14                                                                   |           |                                         |     |

| 14.8.6.2       Byte Transfer Mode Operation       147         14.8.7       SLIC Data Length Code Register       148         14.8.8       SLIC Identifier and Data Registers       149         14.9.1       Initialization/Application Information       150         14.9.1       LIN Message Frame Header       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field       151         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.1       LIN Mode Initialization Procedure       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7.1       LIN Message Headers       153         14.9.7.2       Possible Errors on Message Frames       155         14.9.8.8       Handling Command Message Frames       155         14.9.8.1       Standard Command Message Frames       155         14.9.9.3       Possible Errors on Command Message Data       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       158         1                                                                   |           |                                         |     |

| 14.8.7       SLIC Data Length Code Register.       148         14.8.8       SLIC Identifier and Data Registers.       149         14.9.1       Initialization/Application Information.       150         14.9.1       LIN Message Frame Header       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field.       151         14.9.4       SLIC Module Constraints.       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.1       LIN Mode Initialization Procedure       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7.1       LIN Message Headers       153         14.9.7.2       Possible Errors on Message Headers       154         14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames       155         14.9.9.3       Topic Processor on Command Message Data       158         14.9.9.1       Standard Request IIN Message Frames       158         14.9.9.2       Extended Request Message Frames       158         14.9.9.4       Possible Errors on Request Message Data       161                                                        |           |                                         |     |

| 14.8.8       SLIC Identifier and Data Registers.       149         14.9.1       Initialization/Application Information.       150         14.9.1       LIN Message Frame Header.       150         14.9.2       LIN Data Field.       151         14.9.3       LIN Checksum Field.       151         14.9.4       SLIC Module Constraints.       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure.       151         14.9.6.1       LIN Mode Initialization       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7       Handling LIN Message Headers       153         14.9.7.1       LIN Message Headers       154         14.9.8       Handling Command Message Frames.       155         14.9.8       Handling Command Message Frames.       155         14.9.8.1       Standard Command Message Frames       155         14.9.9.2       Extended Command Message Frames       156         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       158         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible                                                                            |           | ·                                       |     |

| 14.9 Initialization/Application Information       150         14.9.1 LIN Message Frame Header       150         14.9.2 LIN Data Field       150         14.9.3 LIN Checksum Field       151         14.9.4 SLIC Module Constraints       151         14.9.5 SLCSV Interrupt Handling       151         14.9.6 SLIC Module Initialization Procedure       151         14.9.6.1 LIN Mode Initialization       151         14.9.6.2 Byte Transfer Mode Initialization       152         14.9.7 Handling LIN Message Headers       153         14.9.7.1 LIN Message Headers       153         14.9.8 Handling Command Message Frames       155         14.9.8 Handling Command Message Frames       155         14.9.8.1 Standard Command Message Frames       155         14.9.8.2 Extended Command Message Frames       157         14.9.9.3 Possible Errors on Command Message Data       158         14.9.9.1 Standard Request Message Frames       158         14.9.9.2 Extended Request Message Frames       160         14.9.9.1 Handling IMSG to Minimize Interrupts       161         14.9.10 Handling IMSG to Minimize Interrupts       161         14.9.11 Sleep and Wakeup Operation       161         14.9.12 Polling Operation       162         14.9.13 LIN Data Integrity Checkin |           |                                         |     |

| 14.9.1       LIN Message Frame Header       150         14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field       151         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.1       LIN Mode Initialization       151         14.9.7.2       Byte Transfer Mode Initialization       152         14.9.7.7       Handling LIN Message Headers       153         14.9.7.1       LIN Message Headers       154         14.9.8       Handling Command Message Frames       155         14.9.8       Handling Command Message Frames       155         14.9.8.2       Extended Command Message Frames       156         14.9.8.3       Possible Errors on Command Message Data       158         14.9.9.9       Handling Request LIN Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.4       Possible Errors on Request Message Data       161         14.9.9.5       Possible Errors on Request Message Data       161                                                                            |           |                                         |     |

| 14.9.2       LIN Data Field       150         14.9.3       LIN Checksum Field       151         14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.1       LIN Mode Initialization       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7       Handling LIN Message Headers       153         14.9.7.1       LIN Message Headers       154         14.9.7.2       Possible Errors on Message Frames       155         14.9.8       Handling Command Message Frames       155         14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames       157         14.9.9.3       Possible Errors on Command Message Data       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       158         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11                                                                          |           |                                         |     |

| 14.9.3       LIN Checksum Field.       151         14.9.4       SLIC Module Constraints.       151         14.9.5       SLCSV Interrupt Handling.       151         14.9.6       SLIC Module Initialization Procedure.       151         14.9.6.1       LIN Mode Initialization       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7       Handling LIN Message Headers       153         14.9.7.1       LIN Message Headers       154         14.9.7.2       Possible Errors on Message Frames.       155         14.9.8.1       Standard Command Message Frames.       155         14.9.8.2       Extended Command Message Frames       155         14.9.8.3       Possible Errors on Command Message Data       158         14.9.9       Handling Request LIN Message Frames       158         14.9.9       Handling Request Message Frames       158         14.9.9.2       Extended Request Message Frames       158         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       162                                                                     | _         |                                         |     |

| 14.9.4       SLIC Module Constraints       151         14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.1       LIN Mode Initialization       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7       Handling LIN Message Headers       153         14.9.7.1       LIN Message Headers       154         14.9.7.2       Possible Errors on Message Frames       155         14.9.8       Handling Command Message Frames       155         14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames       157         14.9.9.3       Possible Errors on Command Message Data       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.4       Possible Errors on Request Message Data       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation <td< td=""><td>=</td><td></td><td></td></td<> | =         |                                         |     |

| 14.9.5       SLCSV Interrupt Handling       151         14.9.6       SLIC Module Initialization Procedure       151         14.9.6.1       LIN Mode Initialization       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7       Handling LIN Message Headers       153         14.9.7.1       LIN Message Headers       154         14.9.7.2       Possible Errors on Message Headers       155         14.9.8       Handling Command Message Frames       155         14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames       157         14.9.9.3       Possible Errors on Command Message Data       158         14.9.9.1       Standard Request LIN Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       162         14.9.12       Polling Operation       163      <                                                       |           |                                         |     |

| 14.9.6       SLIC Module Initialization Procedure.       151         14.9.6.1       LIN Mode Initialization       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7       Handling LIN Message Headers       153         14.9.7.1       LIN Message Headers       153         14.9.7.2       Possible Errors on Message Headers       155         14.9.8       Handling Command Message Frames       155         14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames       157         14.9.9       Handling Request LIN Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       158         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.15       Byte Transfer Mode Operation       163 <t< td=""><td></td><td></td><td></td></t<>                    |           |                                         |     |

| 14.9.6.1       LIN Mode Initialization       151         14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7       Handling LIN Message Headers       153         14.9.7.1       LIN Message Headers       154         14.9.7.2       Possible Errors on Message Frames       155         14.9.8       Handling Command Message Frames       155         14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames       157         14.9.8.3       Possible Errors on Command Message Data       158         14.9.9.1       Standard Request LIN Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       158         14.9.9.4       Possible Errors on Request Message Data       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.15       Byte Transfer Mode Operation                                           |           |                                         |     |

| 14.9.6.2       Byte Transfer Mode Initialization       152         14.9.7       Handling LIN Message Headers       153         14.9.7.1       LIN Message Headers       154         14.9.7.2       Possible Errors on Message Headers       155         14.9.8       Handling Command Message Frames       155         14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames       157         14.9.8.3       Possible Errors on Command Message Data       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.16       Oscillator Trimming with SLIC       169                                                            |           |                                         |     |

| 14.9.7       Handling LIN Message Headers       153         14.9.7.1       LIN Message Headers       154         14.9.7.2       Possible Errors on Message Headers       155         14.9.8       Handling Command Message Frames       155         14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames       157         14.9.8.3       Possible Errors on Command Message Data       158         14.9.9       Handling Request LIN Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       163         14.9.16       Oscillator Trimming with SLIC       169 <tr< td=""><td></td><td></td><td></td></tr<>                   |           |                                         |     |

| 14.9.7.1       LIN Message Headers       154         14.9.7.2       Possible Errors on Message Headers       155         14.9.8       Handling Command Message Frames       155         14.9.8.1       Standard Command Message Frames       157         14.9.8.2       Extended Command Message Frames       157         14.9.8.3       Possible Errors on Command Message Data       158         14.9.9       Handling Request LIN Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       163         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Filter Operation       170                                                                   |           |                                         |     |

| 14.9.7.2       Possible Errors on Message Headers       155         14.9.8       Handling Command Message Frames       155         14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames       157         14.9.8.3       Possible Errors on Command Message Data       158         14.9.9       Handling Request LIN Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       165         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Filter Operation       170         14.9.17.1       Digital Filter Operation       170 </td <td></td> <td></td> <td></td>                          |           |                                         |     |

| 14.9.8       Handling Command Message Frames.       155         14.9.8.1       Standard Command Message Frames.       155         14.9.8.2       Extended Command Message Frames.       157         14.9.8.3       Possible Errors on Command Message Data.       158         14.9.9       Handling Request LIN Message Frames.       158         14.9.9.1       Standard Request Message Frames.       158         14.9.9.2       Extended Request Message Frames.       160         14.9.9.3       Transmit Abort.       161         14.9.9.4       Possible Errors on Request Message Data.       161         14.9.10       Handling IMSG to Minimize Interrupts.       161         14.9.11       Sleep and Wakeup Operation.       162         14.9.12       Polling Operation.       162         14.9.13       LIN Data Integrity Checking Methods.       162         14.9.14       High-Speed LIN Operation.       163         14.9.15       Byte Transfer Mode Operation.       165         14.9.16       Oscillator Trimming with SLIC.       169         14.9.17       Digital Receive Filter.       170         14.9.17.1       Digital Filter Operation.       170                                                                                                                 |           |                                         |     |

| 14.9.8.1       Standard Command Message Frames       155         14.9.8.2       Extended Command Message Frames       157         14.9.8.3       Possible Errors on Command Message Data       158         14.9.9       Handling Request LIN Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       165         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Receive Filter       170         14.9.17.1       Digital Filter Operation       170                                                                                                                                                                                                  |           |                                         |     |

| 14.9.8.2       Extended Command Message Frames       157         14.9.8.3       Possible Errors on Command Message Data       158         14.9.9       Handling Request LIN Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       165         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Receive Filter       170         14.9.17.1       Digital Filter Operation       170          14.9.17.1       Digital Filter Operation       170                                                                                                                                                                                                       |           |                                         |     |

| 14.9.8.3       Possible Errors on Command Message Data       158         14.9.9       Handling Request LIN Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       163         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Receive Filter       170         14.9.17.1       Digital Filter Operation       170                                                                                                                                                                                                                                                                                                                                    |           | · · · · · · · · · · · · · · · · · · ·   |     |

| 14.9.9       Handling Request LIN Message Frames       158         14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       165         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Receive Filter       170         14.9.17.1       Digital Filter Operation       170                                                                                                                                                                                                                                                                                                                                                                                                             |           |                                         |     |

| 14.9.9.1       Standard Request Message Frames       158         14.9.9.2       Extended Request Message Frames       160         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       165         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Receive Filter       170         14.9.17.1       Digital Filter Operation       170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14.9.8.3  | · · · · · · · · · · · · · · · · · · ·   |     |

| 14.9.9.2       Extended Request Message Frames       160         14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       165         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Receive Filter       170         14.9.17.1       Digital Filter Operation       170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14.9.9    | Handling Request LIN Message Frames     | 158 |

| 14.9.9.3       Transmit Abort       161         14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       165         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Receive Filter       170         14.9.17.1       Digital Filter Operation       170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14.9.9.1  |                                         |     |

| 14.9.9.4       Possible Errors on Request Message Data       161         14.9.10       Handling IMSG to Minimize Interrupts       161         14.9.11       Sleep and Wakeup Operation       161         14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       165         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Receive Filter       170         14.9.17.1       Digital Filter Operation       170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14.9.9.2  | Extended Request Message Frames         | 160 |

| 14.9.10Handling IMSG to Minimize Interrupts16114.9.11Sleep and Wakeup Operation16114.9.12Polling Operation16214.9.13LIN Data Integrity Checking Methods16214.9.14High-Speed LIN Operation16314.9.15Byte Transfer Mode Operation16514.9.16Oscillator Trimming with SLIC16914.9.17Digital Receive Filter17014.9.17.1Digital Filter Operation170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 14.9.9.3  |                                         |     |

| 14.9.11Sleep and Wakeup Operation16114.9.12Polling Operation16214.9.13LIN Data Integrity Checking Methods16214.9.14High-Speed LIN Operation16314.9.15Byte Transfer Mode Operation16514.9.16Oscillator Trimming with SLIC16914.9.17Digital Receive Filter17014.9.17.1Digital Filter Operation170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14.9.9.4  | Possible Errors on Request Message Data | 161 |

| 14.9.12       Polling Operation       162         14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       165         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Receive Filter       170         14.9.17.1       Digital Filter Operation       170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 14.9.10   | Handling IMSG to Minimize Interrupts    | 161 |

| 14.9.13       LIN Data Integrity Checking Methods       162         14.9.14       High-Speed LIN Operation       163         14.9.15       Byte Transfer Mode Operation       165         14.9.16       Oscillator Trimming with SLIC       169         14.9.17       Digital Receive Filter       170         14.9.17.1       Digital Filter Operation       170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14.9.11   | Sleep and Wakeup Operation              | 161 |

| 14.9.14High-Speed LIN Operation.16314.9.15Byte Transfer Mode Operation.16514.9.16Oscillator Trimming with SLIC16914.9.17Digital Receive Filter17014.9.17.1Digital Filter Operation170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14.9.12   | Polling Operation                       | 162 |

| 14.9.15Byte Transfer Mode Operation.16514.9.16Oscillator Trimming with SLIC16914.9.17Digital Receive Filter17014.9.17.1Digital Filter Operation170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14.9.13   | LIN Data Integrity Checking Methods     | 162 |

| 14.9.16Oscillator Trimming with SLIC16914.9.17Digital Receive Filter17014.9.17.1Digital Filter Operation170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14.9.14   | High-Speed LIN Operation                | 163 |

| 14.9.16Oscillator Trimming with SLIC16914.9.17Digital Receive Filter17014.9.17.1Digital Filter Operation170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14.9.15   |                                         |     |

| 14.9.17       Digital Receive Filter       170         14.9.17.1       Digital Filter Operation       170                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14.9.16   | Oscillator Trimming with SLIC           | 169 |

| 14.9.17.1 Digital Filter Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14.9.17   |                                         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14.9.17.1 |                                         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14.9.17.2 |                                         |     |

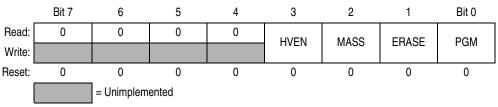

Figure 2-2. Control, Status, and Data Registers (Sheet 7 of 7)

**Table 2-1. Vector Addresses**

| Vector Priority | Vector    | Address           | Vector                         |

|-----------------|-----------|-------------------|--------------------------------|

| Lowest          | IF22-IF16 | \$FFD0,1-\$FFDC,D | Unused vectors                 |

| <b>^</b>        | IF15      | \$FFDE,F          | ADC conversion complete vector |

|                 | IF14      | \$FFE0,1          | Keyboard vector                |

|                 | IF13      | \$FFE2,3          | Unused vector                  |

|                 | IF12      | \$FFE4,5          | Unused vector                  |

|                 | IF11      | \$FFE6,7          | Unused vector                  |

|                 | IF10      | \$FFE8,9          | Unused vector                  |

|                 | IF9       | \$FFEA,B          | SLIC vector                    |

|                 | IF8       | \$FFFC,D          | Unused vector                  |

|                 | IF7       | \$FFEE,F          | Unused vector                  |

|                 | IF6       | \$FFF0,1          | Unused vector                  |

|                 | IF5       | \$FFF2,3          | TIM overflow vector            |

|                 | IF4       | \$FFF4,5          | TIM channel 1 vector           |

|                 | IF3       | \$FFF6,7          | TIM channel 0 vector           |

|                 | IF2       | \$FFF8,9          | Unused vector                  |

|                 | IF1       | \$FFFA,B          | ĪRQ vector                     |

|                 | _         | \$FFFC,D          | SWI vector                     |

| Highest         | _         | \$FFFE,F          | Reset vector                   |

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

Memory

## 2.5 Random-Access Memory (RAM)

This MCU includes static RAM. The locations in RAM below \$0100 can be accessed using the more efficient direct addressing mode, and any single bit in this area can be accessed with the bit manipulation instructions (BCLR, BSET, BRCLR, and BRSET). Locating the most frequently accessed program variables in this area of RAM is preferred.

The RAM retains data when the MCU is in low-power wait or stop mode. At power-on, the contents of RAM are uninitialized. RAM data is unaffected by any reset provided that the supply voltage does not drop below the minimum value for RAM retention.

For compatibility with older M68HC05 MCUs, the HC08 resets the stack pointer to \$00FF. In the devices that have RAM above \$00FF, it is usually best to reinitialize the stack pointer to the top of the RAM so the direct page RAM can be used for frequently accessed RAM variables and bit-addressable program variables.

Include the following 2-instruction sequence in your reset initialization routine (where RamLast is equated to the highest address of the RAM).

| LDHX #RamLast+1 ;point one past RA TXS ;SP<-(H:X-1) |

|-----------------------------------------------------|

|-----------------------------------------------------|

## 2.6 FLASH Memory (FLASH)

The FLASH memory is intended primarily for program storage. In-circuit programming allows the operating program to be loaded into the FLASH memory after final assembly of the application product. It is possible to program the entire array through the single-wire monitor mode interface. Because no special voltages are needed for FLASH erase and programming operations, in-application programming is also possible through other software-controlled communication paths.

This subsection describes the operation of the embedded FLASH memory. The FLASH memory can be read, programmed, and erased from the internal  $V_{DD}$  supply. The program and erase operations are enabled through the use of an internal charge pump.

The minimum size of FLASH memory that can be erased is 64 bytes; and the maximum size of FLASH memory that can be programmed in a program cycle is 32 bytes (a row). Program and erase operations are facilitated through control bits in the FLASH control register (FLCR). Details for these operations appear later in this section.

#### NOTE

An erased bit reads as a 1 and a programmed bit reads as a 0. A security feature prevents viewing of the FLASH contents.<sup>(1)</sup>

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

<sup>1.</sup> No security feature is absolutely secure. However, Freescale's strategy is to make reading or copying the FLASH difficult for unauthorized users.

35

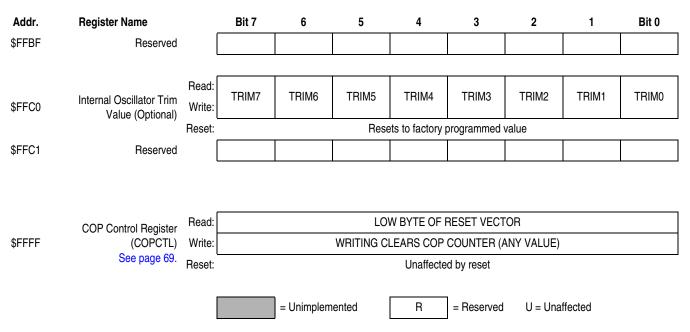

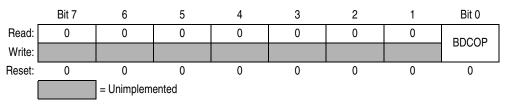

## 2.6.1 FLASH Control Register

The FLASH control register (FLCR) controls FLASH program and erase operations.

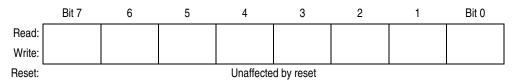

Figure 2-3. FLASH Control Register (FLCR)

## **HVEN** — High Voltage Enable Bit

This read/write bit enables high voltage from the charge pump to the memory for either program or erase operation. It can only be set if either PGM =1 or ERASE =1 and the proper sequence for program or erase is followed.

- 1 = High voltage enabled to array and charge pump on

- 0 = High voltage disabled to array and charge pump off

#### MASS — Mass Erase Control Bit

This read/write bit configures the memory for mass erase operation.

- 1 = Mass erase operation selected

- 0 = Mass erase operation unselected

## **ERASE** — Erase Control Bit

This read/write bit configures the memory for erase operation. ERASE is interlocked with the PGM bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Erase operation selected

- 0 = Erase operation unselected

## **PGM** — Program Control Bit

This read/write bit configures the memory for program operation. PGM is interlocked with the ERASE bit such that both bits cannot be equal to 1 or set to 1 at the same time.

- 1 = Program operation selected

- 0 = Program operation unselected

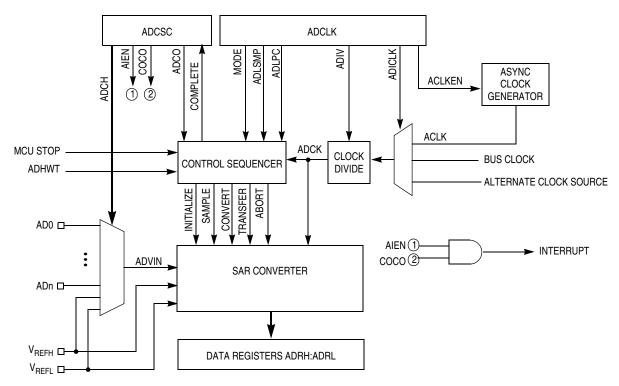

Figure 3-2. ADC10 Block Diagram

The ADC10 can perform an analog-to-digital conversion on one of the software selectable channels. The output of the input multiplexer (ADVIN) is converted by a successive approximation algorithm into a 10-bit digital result. When the conversion is completed, the result is placed in the data registers (ADRH and ADRL). In 8-bit mode, the result is rounded to 8 bits and placed in ADRL. The conversion complete flag is then set and an interrupt is generated if the interrupt has been enabled.

## 3.3.1 Clock Select and Divide Circuit

The clock select and divide circuit selects one of three clock sources and divides it by a configurable value to generate the input clock to the converter (ADCK). The clock can be selected from one of the following sources:

- The asynchronous clock source (ACLK) This clock source is generated from a dedicated clock source which is enabled when the ADC10 is converting and the clock source is selected by setting the ACLKEN bit. When the ADLPC bit is clear, this clock operates from 1-2 MHz; when ADLPC is set it operates at 0.5–1 MHz. This clock is not disabled in STOP and allows conversions in stop mode for lower noise operation.

- Alternate Clock Source This clock source is equal to the external oscillator clock or a four times the bus clock. The alternate clock source is MCU specific, see 3.1 Introduction to determine source and availability of this clock source option. This clock is selected when ADICLK and ACLKEN are both low.

- The bus clock This clock source is equal to the bus frequency. This clock is selected when ADICLK is high and ACLKEN is low.

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6 Freescale Semiconductor 45

#### **Central Processor Unit (CPU)**

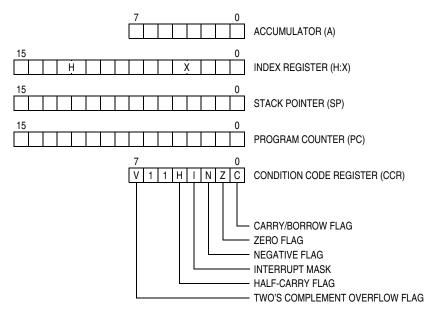

Figure 7-1. CPU Registers

## 7.3.1 Accumulator

The accumulator is a general-purpose 8-bit register. The CPU uses the accumulator to hold operands and the results of arithmetic/logic operations.

Figure 7-2. Accumulator (A)

## 7.3.2 Index Register

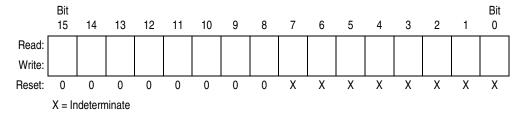

The 16-bit index register allows indexed addressing of a 64-Kbyte memory space. H is the upper byte of the index register, and X is the lower byte. H:X is the concatenated 16-bit index register.

In the indexed addressing modes, the CPU uses the contents of the index register to determine the conditional address of the operand.

The index register can serve also as a temporary data storage location.

Figure 7-3. Index Register (H:X)

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

# Chapter 8 External Interrupt (IRQ)

## 8.1 Introduction

The IRQ (external interrupt) module provides a maskable interrupt input.