Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | HC08                                                                 |

| Core Size                  | 8-Bit                                                                |

| Speed                      | -                                                                    |

| Connectivity               | -                                                                    |

| Peripherals                | -                                                                    |

| Number of I/O              | •                                                                    |

| Program Memory Size        | 6KB (6K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | •                                                                    |

| RAM Size                   | -                                                                    |

| Voltage - Supply (Vcc/Vdd) | •                                                                    |

| Data Converters            | •                                                                    |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 16-TSSOP (0.173", 4.40mm Width)                                      |

| Supplier Device Package    | 16-TSSOP                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908ql3mdte |

## **Revision History**

## **Revision History (Sheet 2 of 2)**

| Date                                      | Revision<br>Level | Description                                                                                                                                                              | Page<br>Number(s) |  |  |

|-------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|

|                                           |                   | Figure 2-2. Control, Status, and Data Registers Corrected reset state for the FLASH Block Protect Register. Corrected reset value for the Internal Oscillator Time Value | 33<br>34          |  |  |

|                                           |                   | Table 7-1. Instruction Set Summary — Added WAIT instruction                                                                                                              | 83                |  |  |

|                                           |                   | 11.8.1 Oscillator Status and Control Register — Revised description of ECGON bit for clarity                                                                             | 117               |  |  |

|                                           |                   | Table 13-3. Interrupt Sources — Corrected address locations for SLIC, KBI, and ADC                                                                                       | 140               |  |  |

|                                           |                   | 14.3.5 SLIC Wait (Core Specific) — Revised description for clarity                                                                                                       | 144               |  |  |

|                                           |                   | 14.3.7 SLIC Stop (Core Specific) — Revised description for clarity                                                                                                       | 144               |  |  |

| March,                                    |                   | 14.6.6.2 Byte Transfer Mode Operation — Revised definition of Receiver Buffer Overrun Error                                                                              | 156               |  |  |

| 2004                                      | 2.0               | 14.7.1 LIN Message Frame Header — Revised third paragraph of description                                                                                                 | 161               |  |  |

|                                           |                   | 14.14 Sleep and Wakeup Operation — Revised second paragraph of description                                                                                               | 174               |  |  |

|                                           |                   | 15.8 Input/Output Signals — Corrected reference from PTA0/TCH) to PTB0/TCH0                                                                                              | 196               |  |  |

|                                           |                   | 15.8.2 TIM Channel I/O Pins (PTB0/TCH0 and PTA1/TCH1) — Corrected reference to from PTA0/TCH) to PTB0/TCH0                                                               | 196               |  |  |

|                                           |                   | Figure 16-1. Block Diagram Highlighting BRK and MON Blocks — Added                                                                                                       | 206               |  |  |

|                                           |                   | 17.5 5-V DC Electrical Characteristics — Updated table notes                                                                                                             | 227               |  |  |

|                                           |                   | 17.8 5-V Oscillator Characteristics — Updated table notes                                                                                                                | 230               |  |  |

|                                           |                   | 17.9 3.3-V DC Electrical Characteristics — Updated table notes                                                                                                           | 231               |  |  |

| June,<br>2004 3.0 Modular sections rework |                   | Modular sections reworked for clarity.                                                                                                                                   | Throughout        |  |  |

|                                           |                   | Updated to final Freescale format. Corrections per email review. Replaced ADC chapter with latest.                                                                       | Throughout        |  |  |

|                                           |                   | Table 1-3. Function Priority in Shared Pins — Updated entry for PTA2                                                                                                     | 23                |  |  |

| December,<br>2004                         | 4.0               | Figure 1-2. MCU Pin Assignments — Corrected pin assignments for the TSSOP packages.                                                                                      | 21                |  |  |

| 2004                                      |                   | 17.11 Oscillator Characteristics — Updated deviation from trimmed internal oscillator specifications.                                                                    | 210               |  |  |

|                                           |                   | 17.8 3.3-V DC Electrical Characteristics — Corrected capacitance values                                                                                                  | 208               |  |  |

|                                           |                   | 17.11 Oscillator Characteristics — Corrected Note 8                                                                                                                      | 211               |  |  |

|                                           |                   | 13.4.1 External Pin Reset — Corrected location of RSTEN bit from CONFIG1 to CONFIG2.                                                                                     | 120               |  |  |

| August,<br>2005                           | 5.0               | 13.4.2 Active Resets from Internal Sources — Corrected location of RSTEN bit from CONFIG1 to CONFIG2.                                                                    | 120               |  |  |

|                                           |                   | Chapter 18 Ordering Information and Mechanical Specifications — Replaced case outlines with appropriate 98A drawing.                                                     | 219               |  |  |

| September,<br>2005                        | 6.0               | Figure 2-1. Memory Map — Corrected address labels.                                                                                                                       | 26                |  |  |

## MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

## **Table of Contents**

## Chapter 1 General Description

|                    | Gonordi Bosonphon                          |    |

|--------------------|--------------------------------------------|----|

| 1.1                | Introduction                               | 17 |

| 1.2                | Features                                   | 17 |

| 1.3                | MCU Block Diagram                          | 19 |

|                    | Pin Functions                              |    |

| 1.5                | Pin Function Priority                      |    |

| 1.0                |                                            |    |

|                    | Chapter 2                                  |    |

|                    | Memory                                     |    |

| 2.1                | Introduction                               | 25 |

| 2.2                | Unimplemented Memory Locations             | 25 |

| 2.3                | Reserved Memory Locations                  | 25 |

| 2.4                | Direct Page Registers                      |    |

| 2.5                | Random-Access Memory (RAM)                 | 34 |

| 2.6                | FLASH Memory (FLASH)                       |    |

| 2.6.1              | FLASH Control Register                     |    |

| 2.6.2              | FLASH Page Erase Operation                 |    |

| 2.6.3              | FLASH Mass Erase Operation                 | 37 |

| 2.6.4              | FLASH Program Operation                    |    |

| 2.6.5              | FLASH Protection                           |    |

| 2.6.6              | FLASH Block Protect Register               | 40 |

|                    | Chapter 3                                  |    |

|                    | Analog-to-Digital Converter (ADC10) Module |    |

| 3.1                | Introduction                               | 43 |

| 3.2                | Features                                   |    |

| 3.3                | Functional Description                     |    |

| 3.3.1              | Clock Select and Divide Circuit            |    |

| 3.3.2              | Input Select and Pin Control               | 46 |

| 3.3.3              | Conversion Control                         | 46 |

| 3.3.3.1            | Initiating Conversions                     | 46 |

| 3.3.3.2            |                                            |    |

| 3.3.3.3            |                                            |    |

| 3.3.3.4            |                                            |    |

| 3.3.4              | Sources of Error                           |    |

| 3.3.4.1            | Sampling Error                             |    |

| 3.3.4.2<br>3.3.4.3 |                                            |    |

| 3.3.4.4            |                                            |    |

| 0.0.4.4            | Code Width and Quantization End            | 73 |

## **Table of Contents**

## Chapter 15 Timer Interface Module (TIM)

| 15.1    | Introduction                             | 173 |

|---------|------------------------------------------|-----|

| 15.2    | Features                                 | 173 |

| 15.3    | Functional Description                   | 173 |

| 15.3.1  | TIM Counter Prescaler                    | 173 |

| 15.3.2  | Input Capture                            | 174 |

| 15.3.3  | Output Compare                           | 174 |

| 15.3.3. | 1 Unbuffered Output Compare              | 175 |

| 15.3.3. |                                          |     |

| 15.3.4  | Pulse Width Modulation (PWM)             |     |

| 15.3.4. |                                          |     |

| 15.3.4. |                                          |     |

| 15.3.4. |                                          |     |

| 15.4    | Interrupts                               | 179 |

| 15.5    | Low-Power Modes                          | 179 |

| 15.5.1  | Wait Mode                                | 179 |

| 15.5.2  | Stop Mode                                | 179 |

| 15.6    | TIM During Break Interrupts              | 179 |

| 15.7    | I/O Signals                              | 179 |

| 15.7.1  | TIM Channel I/O Pins (TCH1:TCH0)         |     |

| 15.7.2  | TIM Clock Pin (TCLK)                     | 180 |

| 15.8    | Registers                                | 180 |

| 15.8.1  | TIM Status and Control Register          |     |

| 15.8.2  | TIM Counter Registers                    | 181 |

| 15.8.3  | TIM Counter Modulo Registers             |     |

| 15.8.4  | TIM Channel Status and Control Registers | 183 |

| 15.8.5  | TIM Channel Registers                    | 185 |

|         | Chapter 16                               |     |

|         | Chapter 16 Development Support           |     |

| 16.1    | Introduction                             | 187 |

| 16.2    | Break Module (BRK)                       |     |

| 16.2.1  | Functional Description                   |     |

| 16.2.1. | ·                                        |     |

| 16.2.1. |                                          |     |

| 16.2.1. |                                          |     |

| 16.2.2  | Break Module Registers                   |     |

| 16.2.2. |                                          |     |

| 16.2.2. |                                          |     |

| 16.2.2. |                                          |     |

| 16.2.2. |                                          |     |

| 16.2.2. |                                          |     |

| 16.2.3  | Low-Power Modes                          |     |

- Power-on reset

- Memory mapped I/O registers

- Power saving stop and wait modes

- Available packages:

- 16-pin small outline integrated circuit (SOIC) package

- 16-pin thin shrink small outline package (TSSOP)

## Features of the CPU08 include the following:

- Enhanced HC05 programming model

- Extensive loop control functions

- 16 addressing modes (eight more than the HC05)

- 16-bit index register and stack pointer

- Memory-to-memory data transfers

- Fast 8 × 8 multiply instruction

- Fast 16/8 divide instruction

- Binary-coded decimal (BCD) instructions

- Optimization for controller applications

- Efficient C language support

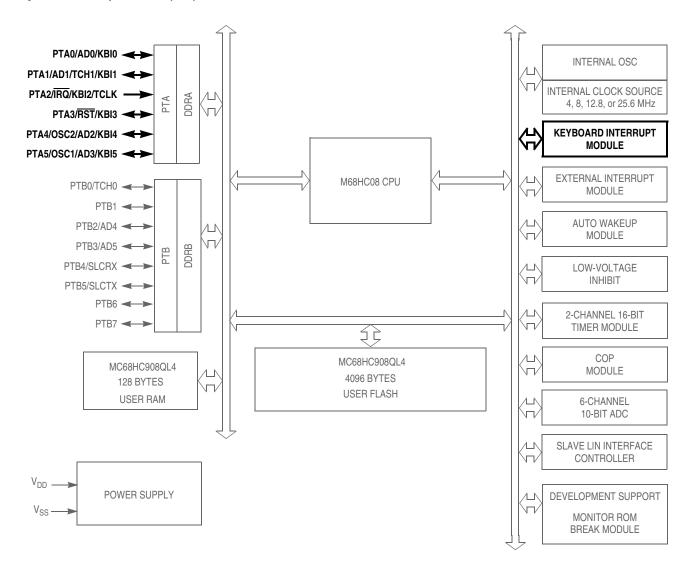

## 1.3 MCU Block Diagram

Figure 1-1 shows the structure of the MC68HC908QL4.

## 1.4 Pin Functions

Table 1-2 provides a description of the pin functions.

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

#### Memory

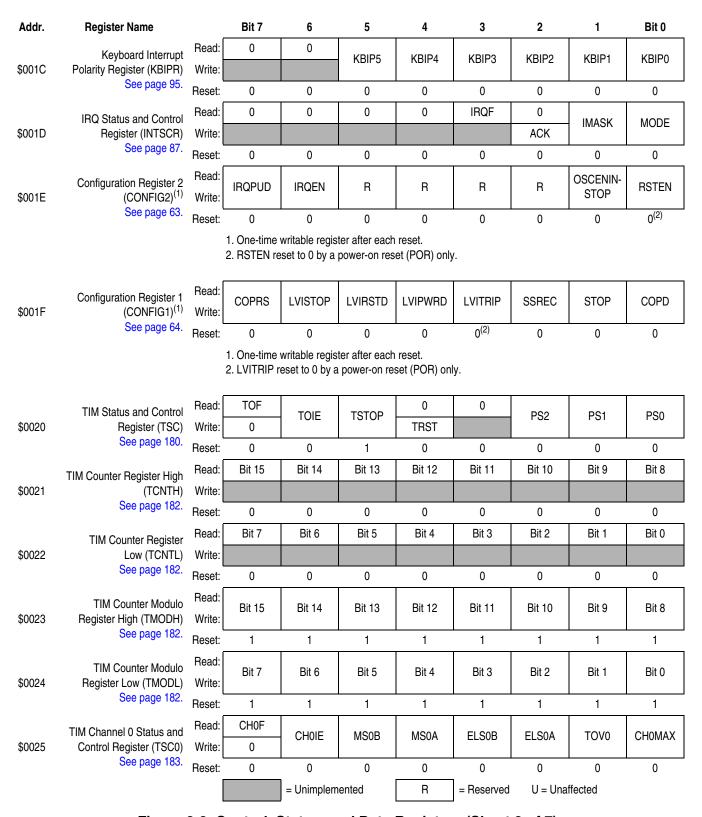

Figure 2-2. Control, Status, and Data Registers (Sheet 2 of 7)

## **AWUIE** — Auto Wakeup Interrupt Enable Bit

This read/write bit enables the auto wakeup interrupt input to latch interrupt requests. Reset clears AWUIE.

- 1 = Auto wakeup enabled as interrupt input

- 0 = Auto wakeup not enabled as interrupt input

#### NOTE

KBIE5–KBIE0 bits are not used in conjuction with the auto wakeup feature. For a description of these bits, see 9.8.2 Keyboard Interrupt Enable Register (KBIER).

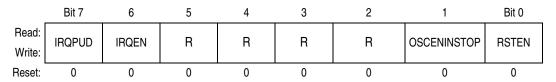

## 4.6.4 Configuration Register 2

The configuration register 2 (CONFIG2), is used to allow the bus clock source to run in STOP. In this case, the clock, BUSCLKX4 will be used to drive the AWU request generator.

Figure 4-5. Configuration Register 2 (CONFIG2)

## OSCENINSTOP — Oscillator Enable in Stop Mode Bit

OSCENINSTOP, when set, will allow the bus clock source (BUSCLKX4) to generate clocks for the AWU in stop mode. See 11.8.1 Oscillator Status and Control Register for information on enabling the external clock sources.

- 1 = Oscillator enabled to operate during stop mode

- 0 = Oscillator disabled during stop mode

## NOTE

IRQPUD, IRQEN, and RSTEN bits are not used in conjuction with the auto wakeup feature. For a description of these bits, see Chapter 5 Configuration Register (CONFIG).

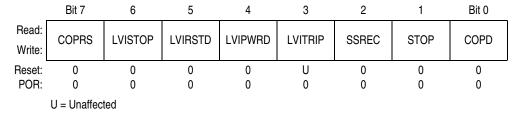

## 4.6.5 Configuration Register 1

The configuration register 1 (CONFIG1), is used to select the period for the AWU. The timeout will be based on the COPRS bit along with the clock source for the AWU.

Figure 4-6. Configuration Register 1 (CONFIG1)

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

#### **Computer Operating Properly (COP)**

The COP counter is a free-running 6-bit counter preceded by the 12-bit system integration module (SIM) counter. If not cleared by software, the COP counter overflows and generates an asynchronous reset after 262,128 or 8176 BUSCLKX4 cycles; depending on the state of the COP rate select bit, COPRS, in configuration register 1. With a 262,128 BUSCLKX4 cycle overflow option, the internal 12.8-MHz oscillator gives a COP timeout period of 20.48 ms. Writing any value to location \$FFFF before an overflow occurs prevents a COP reset by clearing the COP counter and stages 12–5 of the SIM counter.

#### NOTE

Service the COP immediately after reset and before entering or after exiting stop mode to guarantee the maximum time before the first COP counter overflow.

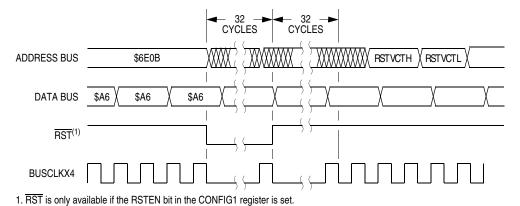

A COP reset pulls the  $\overline{RST}$  pin low (if the RSTEN bit is set in the CONFIG1 register) for  $32 \times BUSCLKX4$  cycles and sets the COP bit in the reset status register (RSR). See 13.8.1 SIM Reset Status Register.

#### NOTE

Place COP clearing instructions in the main program and not in an interrupt subroutine. Such an interrupt subroutine could keep the COP from generating a reset even while the main program is not working properly.

## 6.3 I/O Signals

The following paragraphs describe the signals shown in Figure 6-1.

## 6.3.1 BUSCLKX4

BUSCLKX4 is the oscillator output signal. BUSCLKX4 frequency is equal to the crystal frequency or the RC-oscillator frequency.

#### 6.3.2 STOP Instruction

The STOP instruction clears the SIM counter.

## 6.3.3 COPCTL Write

Writing any value to the COP control register (COPCTL) (see Figure 6-2) clears the COP counter and clears stages 12–5 of the SIM counter. Reading the COP control register returns the low byte of the reset vector.

#### 6.3.4 Power-On Reset

The power-on reset (POR) circuit in the SIM clears the SIM counter  $4096 \times BUSCLKX4$  cycles after power up.

## 6.3.5 Internal Reset

An internal reset clears the SIM counter and the COP counter.

## 6.3.6 COPD (COP Disable)

The COPD signal reflects the state of the COP disable bit (COPD) in the configuration register (CONFIG). See Chapter 5 Configuration Register (CONFIG).

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

## **Central Processor Unit (CPU)**

Table 7-1. Instruction Set Summary (Sheet 5 of 6)

| Source                                                                                                 | Operation Description                                          |                                                                                                                                                                                                                                 |    |          | Effect<br>on CCR |          |          | Address<br>Mode | Opcode                                              | Operand                                          | les                                             |                                      |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----------|------------------|----------|----------|-----------------|-----------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                                   | - CP - C - C - C - C - C - C - C - C - C                       |                                                                                                                                                                                                                                 | ٧  | Н        | I                | N        | z        | С               | Add                                                 | Opc                                              | Ope                                             | Cycles                               |

| PULA                                                                                                   | Pull A from Stack                                              | $SP \leftarrow (SP + 1); Pull (A)$                                                                                                                                                                                              | -  | _        | _                | -        | _        | _               | INH                                                 | 86                                               |                                                 | 2                                    |

| PULH                                                                                                   | Pull H from Stack                                              | $SP \leftarrow (SP + 1); Pull (H)$                                                                                                                                                                                              | -  | -        | _                | -        | -        | _               | INH                                                 | 8A                                               |                                                 | 2                                    |

| PULX                                                                                                   | Pull X from Stack                                              | $SP \leftarrow (SP + 1); Pull(X)$                                                                                                                                                                                               | -  | -        | _                | -        | _        | -               | INH                                                 | 88                                               |                                                 | 2                                    |

| ROL opr<br>ROLA<br>ROLX<br>ROL opr,X<br>ROL ,X<br>ROL opr,SP                                           | Rotate Left through Carry                                      | b7 b0                                                                                                                                                                                                                           | 1  | _        | ı                | <b>‡</b> | ‡        | ‡               | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 39<br>49<br>59<br>69<br>79<br>9E69               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| ROR opr<br>RORA<br>RORX<br>ROR opr,X<br>ROR ,X<br>ROR opr,SP                                           | Rotate Right through Carry                                     | b7 b0                                                                                                                                                                                                                           | 1  | _        | 1                | 1        | <b>‡</b> | ‡               | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1               | 36<br>46<br>56<br>66<br>76<br>9E66               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| RSP                                                                                                    | Reset Stack Pointer                                            | $SP \leftarrow \$FF$                                                                                                                                                                                                            | _  | _        | 1                | _        | -        | _               | INH                                                 | 9C                                               |                                                 | 1                                    |

| RTI                                                                                                    | Return from Interrupt                                          | $\begin{array}{l} SP \leftarrow (SP) + 1;  Pull  (CCR) \\ SP \leftarrow (SP) + 1;  Pull  (A) \\ SP \leftarrow (SP) + 1;  Pull  (X) \\ SP \leftarrow (SP) + 1;  Pull  (PCH) \\ SP \leftarrow (SP) + 1;  Pull  (PCL) \end{array}$ | 1  | <b>‡</b> | 1                | ţ        | ţ        | <b>‡</b>        | INH                                                 | 80                                               |                                                 | 7                                    |

| RTS                                                                                                    | Return from Subroutine                                         | $SP \leftarrow SP + 1$ ; Pull (PCH)<br>$SP \leftarrow SP + 1$ ; Pull (PCL)                                                                                                                                                      | -  | -        | 1                | _        | _        | -               | INH                                                 | 81                                               |                                                 | 4                                    |

| SBC #opr<br>SBC opr<br>SBC opr<br>SBC opr,X<br>SBC opr,X<br>SBC,X<br>SBC,X<br>SBC opr,SP<br>SBC opr,SP | Subtract with Carry                                            | $A \leftarrow (A) - (M) - (C)$                                                                                                                                                                                                  | Į. | _        | -                | 1        | ‡        | ‡               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A2<br>B2<br>C2<br>D2<br>E2<br>F2<br>9EE2<br>9ED2 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 23443245                             |

| SEC                                                                                                    | Set Carry Bit                                                  | C ← 1                                                                                                                                                                                                                           | _  | -        | _                | -        | _        | 1               | INH                                                 | 99                                               |                                                 | 1                                    |

| SEI                                                                                                    | Set Interrupt Mask                                             | I ← 1                                                                                                                                                                                                                           | _  | -        | 1                | -        | _        | -               | INH                                                 | 9B                                               |                                                 | 2                                    |

| STA opr<br>STA opr,<br>STA opr,X<br>STA opr,X<br>STA,X<br>STA opr,SP<br>STA opr,SP                     | Store A in M                                                   | $M \leftarrow (A)$                                                                                                                                                                                                              | 0  | _        | _                | 1        | ‡        | _               | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | B7<br>C7<br>D7<br>E7<br>F7<br>9EE7<br>9ED7       | dd<br>hh II<br>ee ff<br>ff<br>ee ff             | 3<br>4<br>4<br>3<br>2<br>4<br>5      |

| STHX opr                                                                                               | Store H:X in M                                                 | (M:M + 1) ← (H:X)                                                                                                                                                                                                               | 0  | -        | _                | 1        | 1        | -               | DIR                                                 | 35                                               | dd                                              | 4                                    |

| STOP                                                                                                   | Enable Interrupts, Stop Processing, Refer to MCU Documentation | $I \leftarrow 0;  Stop   Processing$                                                                                                                                                                                            | -  | -        | 0                | -        | -        | -               | INH                                                 | 8E                                               |                                                 | 1                                    |

| STX opr<br>STX opr<br>STX opr,X<br>STX opr,X<br>STX,X<br>STX opr,SP<br>STX opr,SP                      | Store X in M                                                   | $M \leftarrow (X)$                                                                                                                                                                                                              | 0  | _        | ı                | 1        | ‡        | _               | DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2        | BF<br>CF<br>DF<br>EF<br>FF<br>9EEF<br>9EDF       | dd<br>hh II<br>ee ff<br>ff<br>ee ff             | 3<br>4<br>4<br>3<br>2<br>4<br>5      |

| SUB #opr<br>SUB opr<br>SUB opr<br>SUB opr,X<br>SUB opr,X<br>SUB,X<br>SUB opr,SP<br>SUB opr,SP          | Subtract                                                       | $A \leftarrow (A) - (M)$                                                                                                                                                                                                        | Î  | _        | ı                | 1        | ‡        | ‡               | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2 | A0<br>B0<br>C0<br>D0<br>E0<br>F0<br>9EE0<br>9ED0 |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

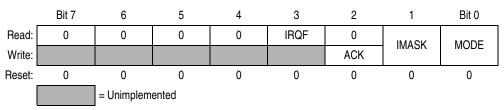

## 8.8 Registers

The IRQ status and control register (INTSCR) controls and monitors operation of the IRQ module. The INTSCR:

- Shows the state of the IRQ flag

- Clears the IRQ latch

- Masks the IRQ interrupt request

- Controls triggering sensitivity of the IRQ interrupt pin

Figure 8-3. IRQ Status and Control Register (INTSCR)

## IRQF — IRQ Flag Bit

This read-only status bit is set when the IRQ interrupt is pending.

- $1 = \overline{IRQ}$  interrupt pending

- $0 = \overline{IRQ}$  interrupt not pending

## ACK — IRQ Interrupt Request Acknowledge Bit

Writing a 1 to this write-only bit clears the IRQ latch. ACK always reads 0.

## IMASK — IRQ Interrupt Mask Bit

Writing a 1 to this read/write bit disables the IRQ interrupt request.

- 1 = IRQ interrupt request disabled

- 0 = IRQ interrupt request enabled

## MODE — IRQ Edge/Level Select Bit

This read/write bit controls the triggering sensitivity of the IRQ pin.

- $1 = \overline{IRQ}$  interrupt request on falling edges and low levels

- 0 = IRQ interrupt request on falling edges only

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

## **Keyboard Interrupt Module (KBI)**

RST, IRQ: Pins have internal pull up device

All port pins have programmable pull up device (pullup/down on port A)

PTA[0:5]: Higher current sink and source capability

Figure 9-1. Block Diagram Highlighting KBI Block and Pins

## 11.6 OSC During Break Interrupts

There are no status flags associated with the OSC module.

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. The BCFE bit in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the break, the bit cannot change during the break state as long as BCFE is cleared. After the break, doing the second step clears the status bit.

## 11.7 I/O Signals

The OSC shares its pins with general-purpose input/output (I/O) port pins. See Figure 11-1 for port location of these shared pins.

## 11.7.1 Oscillator Input Pin (OSC1)

The OSC1 pin is an input to the crystal oscillator amplifier, an input to the RC oscillator circuit, or an input from an external clock source.

When the OSC is configured for internal oscillator, the OSC1 pin can be used as a general-purpose input/output (I/O) port pin or other alternative pin function.

## 11.7.2 Oscillator Output Pin (OSC2)

For the XTAL oscillator option, the OSC2 pin is the output of the crystal oscillator amplifier.

When the OSC is configured for internal oscillator, external clock, or RC, the OSC2 pin can be used as a general-purpose I/O port pin or other alternative pin function. When the oscillator is configured for internal or RC, the OSC2 pin can be used to output BUSCLKX4.

Option

OSC2 Pin Function

XTAL oscillator

Inverting OSC1

External clock

General-purpose I/O or alternative pin function

Internal oscillator or OSC2EN = 0: General-purpose I/O or alternative pin function OSC2EN = 1: BUSCLKX4 output

Table 11-1. OSC2 Pin Function

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

Input/Output Ports (PORTS)

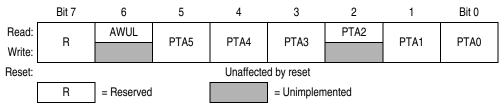

## 12.2.1 Port A Data Register

The port A data register (PTA) contains a data latch for each of the six port A pins.

Figure 12-1. Port A Data Register (PTA)

## PTA[5:0] — Port A Data Bits

These read/write bits are software programmable. Data direction of each port A pin is under the control of the corresponding bit in data direction register A. Reset has no effect on port A data.

### AWUL — Auto Wakeup Latch Data Bit

This is a read-only bit which has the value of the auto wakeup interrupt request latch. The wakeup request signal is generated internally (see Chapter 4 Auto Wakeup Module (AWU)). There is no PTA6 port nor any of the associated bits such as PTA6 data register, pullup/down enable or direction.

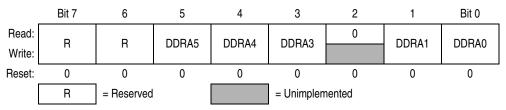

## 12.2.2 Data Direction Register A

Data direction register A (DDRA) determines whether each port A pin is an input or an output. Writing a 1 to a DDRA bit enables the output buffer for the corresponding port A pin; a 0 disables the output buffer.

Figure 12-2. Data Direction Register A (DDRA)

## DDRA[5:0] — Data Direction Register A Bits

These read/write bits control port A data direction. Reset clears DDRA[5:0], configuring all port A pins as inputs.

- 1 = Corresponding port A pin configured as output

- 0 = Corresponding port A pin configured as input

#### NOTE

Avoid glitches on port A pins by writing to the port A data register before changing data direction register A bits from 0 to 1.

Figure 12-3 shows the port A I/O logic.

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6 112 Freescale Semiconductor

## 13.7.1 Wait Mode

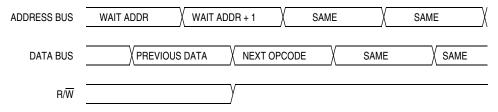

In wait mode, the CPU clocks are inactive while the peripheral clocks continue to run. Figure 13-14 shows the timing for wait mode entry.

NOTE: Previous data can be operand data or the WAIT opcode, depending on the last instruction.

Figure 13-14. Wait Mode Entry Timing

A module that is active during wait mode can wake up the CPU with an interrupt if the interrupt is enabled. Stacking for the interrupt begins one cycle after the WAIT instruction during which the interrupt occurred. In wait mode, the CPU clocks are inactive. Refer to the wait mode subsection of each module to see if the module is active or inactive in wait mode. Some modules can be programmed to be active in wait mode.

Wait mode can also be exited by a reset (or break in emulation mode). A break interrupt during wait mode sets the SIM break stop/wait bit, SBSW, in the break status register (BSR). If the COP disable bit, COPD, in the configuration register is 0, then the computer operating properly module (COP) is enabled and remains active in wait mode.

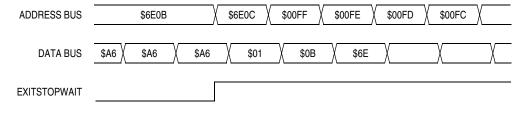

Figure 13-15 and Figure 13-16 show the timing for wait recovery.

NOTE: EXITSTOPWAIT =  $\overline{RST}$  pin OR CPU interrupt

Figure 13-15. Wait Recovery from Interrupt

Figure 13-16. Wait Recovery from Internal Reset

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

either transmit or receive these bytes, depending upon the user code interpretation of the identifier byte. Data is always transmitted into the data field least significant byte (LSB) first.

The SLIC module can automatically handle up to 64 bytes in extended LIN message frames without significantly changing program execution.

## 14.9.3 LIN Checksum Field

The checksum field is a data integrity measure for LIN message frames, used to signal errors in data consistency. The LIN 1.3 checksum calculation only covers the data field, but the SLIC module also supports an enhanced checksum calculation which also includes the identifier field. For more information on the checksum calculation, refer to 14.9.13 LIN Data Integrity Checking Methods.

## 14.9.4 SLIC Module Constraints

In designing a practical module, certain reasonable constraints must be placed on the LIN message traffic which are not necessarily explicitly specified in the LIN specification. The SLIC module presumes that:

Timeout for no-bus-activity = 1 second.

## 14.9.5 SLCSV Interrupt Handling

Each change of state of the SLIC module is encoded in the SLIC state vector register (SLCSV). This is an efficient method of handling state changes, indicating to the user not only the current status of the SLIC module, but each state change will also generate an interrupt (if SLIC interrupts are enabled). For more detailed information on the SLCSV, please refer to 14.8.6 SLIC State Vector Register.

In the software diagrams in the following subsections, when an interrupt is shown, the first step must always be reading SLCSV to determine what is the current status of the SLIC module. Likewise, when the diagrams indicate to "EXIT ISR", the final step to exiting the interrupt service routine is to clear the SLCF interrupt flag. This can only be done if the SLCSV has first been read, and in the case that data has been received (such as an ID byte or command message data) the SLCD has been read at least one time.

After SLCSV is read, it will switch to the next pending state, so the user must be sure it is copied only once into a software variable at the beginning of the interrupt service routine to avoid inadvertently clearing a pending interrupt source. Additional decisions based on this value must be made from the software variable, rather than from the SLCSV itself.

After exiting the ISR, normal application code may resume. If the diagram indicates to "RETURN TO IDLE," it indicates that all processing for the current message frame has been completed. If an error was detected and the corresponding error code loaded into the SLCSV, any pending data in the data buffer will be flushed out and the SLIC returned to its idle state, seeking out the next message frame header.

## 14.9.6 SLIC Module Initialization Procedure

#### 14.9.6.1 LIN Mode Initialization

The SLIC module does not require very much initialization, due to its self-synchronizing design. Because no prior knowledge of the bit rate is required to synchronize to the LIN bus, no programming of bit rate is required.

At initialization time, the user must configure:

- SLIC prescale register (SLIC digital receive filter adjustment).

- Wait clock mode operation.

## MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

#### Slave LIN Interface Controller (SLIC) Module

The SLIC clock is the same as the CPU bus clock. The module is designed to provide better than 1% bit rate accuracy at the lowest value of the SLIC clock frequency and the accuracy improves as the SLIC clock frequency is increased. For this reason, it is advantageous to choose the fastest SLIC clock which is still within the acceptable operating range of the SLIC. Because the SLIC may be used with MCUs with internal oscillators, the tolerance of the oscillator must be taken into account to ensure that SLIC clock frequency does not exceed the bounds of the SLIC clock operating range. This is especially important if the user wishes to use the oscillator untrimmed, where process variations might result in MCU frequency offsets of ±25%.

The acceptable range of SLIC clock frequencies is 2–8 MHz to guarantee LIN operations with greater than 1.5% accuracy across the 1–20 kbps range of LIN bit rates. The user must ensure that the fastest possible SLIC clock frequency never exceeds 8 MHz or that the slowest possible SLIC clock never falls below 2 MHz under worst case conditions. This would include, for example, oscillator frequency variations due to untrimmed oscillator tolerance, temperature variation, or supply voltage variation.

To initialize the SLIC module into LIN operating mode, the user must perform the following steps prior to needing to receive any LIN message traffic. These steps assume the MCU has been reset either by a power-on reset (POR) or any other MCU reset mechanism.

The steps for SLIC Initialization for LIN operation are:

- Write SLCC1 to clear INITREQ.

- 2. When INITACK = 0. write SLCC1 & SLCC2 with desired values for:

- a. SLCWCM Wait clock mode (default = leaving SLIC clock running when in CPU wait).

- 3. Write SLCP to set up prescalers for:

- a. RXFP Digital receive filter clock prescaler (default = SLIC divided by 3).

- 4. Enable the SLIC module by writing SLCC2:

- a. SLCE = 1 to place SLIC module into run mode.

- b. BTM = 0 to disable byte transfer mode (default).

- 5. Write SLCC1 to enable SLIC interrupts (if desired).

## 14.9.6.2 Byte Transfer Mode Initialization

Bit rate synchronization is handled automatically in LIN mode, using the synchronization data contained in each LIN message to derive the desired bit rate. In byte transfer mode (BTM = 1); however, the user must set up the bit rate for communications using the clock selection, prescaler, and SLCBT.

More information on byte transfer mode is described in 14.9.15 Byte Transfer Mode Operation, including the performance parameters on recommended maximum speeds, bit time resolution, and oscillator tolerance requirements.

After the desired settings of prescalers and bit time are determined, the SLIC Initialization for BTM operation is virtually identical to that of LIN operation.

#### The steps are:

- Write SLCC1 to clear INITREQ.

- 2. When INITACK = 0, write SLCC2 with desired values for:

- a. SLCWCM Wait clock mode (default = leaving SLIC clock running when in CPU wait).

- 3. Write SLCICP to set up prescalers for:

- a. RXFP Digital receive filter clock prescaler (default = SLIC divided by 3).

#### NOTE

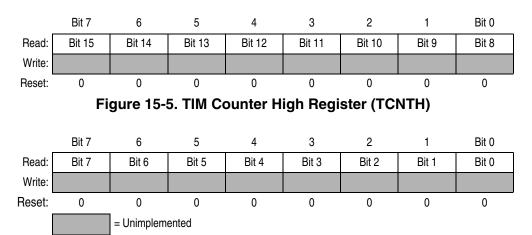

If you read TCNTH during a break interrupt, be sure to unlatch TCNTL by reading TCNTL before exiting the break interrupt. Otherwise, TCNTL retains the value latched during the break.

Figure 15-6. TIM Counter Low Register (TCNTL)

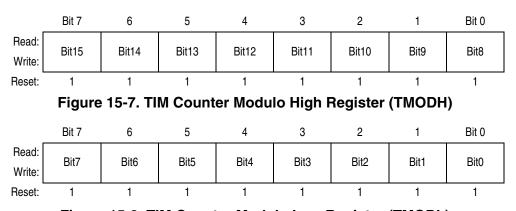

## 15.8.3 TIM Counter Modulo Registers

The read/write TIM modulo registers contain the modulo value for the counter. When the counter reaches the modulo value, the overflow flag (TOF) becomes set, and the counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (TMODH) inhibits the TOF bit and overflow interrupts until the low byte (TMODL) is written. Reset sets the TIM counter modulo registers.

Figure 15-8. TIM Counter Modulo Low Register (TMODL)

## NOTE

Reset the counter before writing to the TIM counter modulo registers.

182 Freescale Semiconductor

MC68HC908QL4 • MC68HC908QL3 • MC68HC908QL2 Data Sheet, Rev. 6

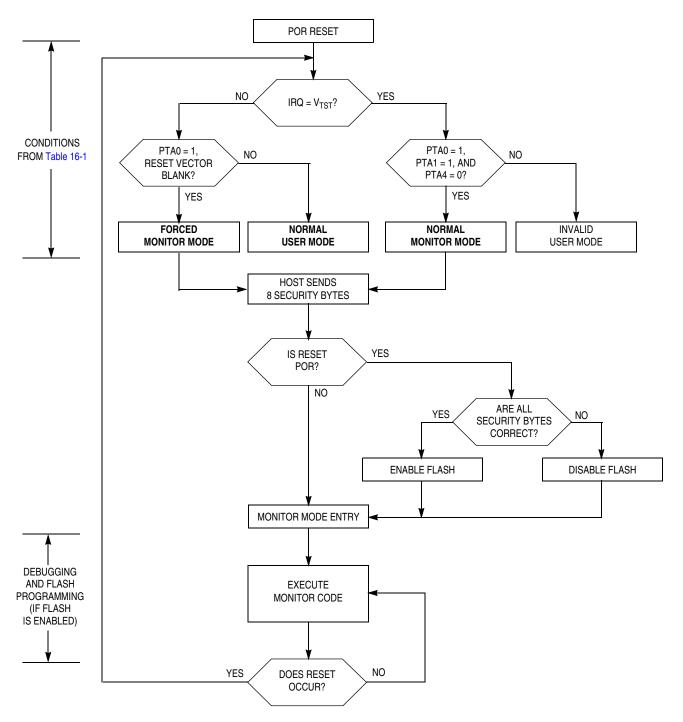

Figure 16-9. Simplified Monitor Mode Entry Flowchart

## **Electrical Specifications**

| Characteristic                       | Conditions  | Symbol          | Min  | Typ <sup>(1)</sup> | Max  | Unit | Comment                    |  |

|--------------------------------------|-------------|-----------------|------|--------------------|------|------|----------------------------|--|

| Integral non-linearity               | 10-bit mode | INL             | 0    | ±0.5               | _    | LSB  |                            |  |

| integral non-linearity               | 8-bit mode  | IINL            | 0    | ±0.3               | _    | LOD  |                            |  |

| Zero-scale error                     | 10-bit mode | Е               | 0    | ±0.5 —             |      | LSB  |                            |  |

| Zero-scale error                     | 8-bit mode  | E <sub>ZS</sub> | 0    | ±0.3               | _    | LOD  | $V_{ADIN} = V_{SS}$        |  |

| Full-scale error                     | 10-bit mode | E <sub>FS</sub> | 0    | ±0.5               | _    | LSB  | - V                        |  |

|                                      | 8-bit mode  |                 | 0    | ±0.3               | _    | LOD  | $V_{ADIN} = V_{DD}$        |  |

| Quantization error                   | 10-bit mode | EQ              | _    | _                  | ±0.5 | LSB  | 8-bit mode is              |  |

| Quantization enoi                    | 8-bit mode  | □Q              | _    | _                  | ±0.5 | LOD  | not truncated              |  |

| Input leakage error                  | 10-bit mode | _               | 0    | ±0.2               | ±5   | LSB  | Pad leakage <sup>(5)</sup> |  |

| iliput leakage elloi                 | 8-bit mode  | E <sub>IL</sub> | 0    | ±0.1               | ±1.2 | LOD  | * R <sub>AS</sub>          |  |

| Bandgap voltage input <sup>(6)</sup> |             | V <sub>BG</sub> | 1.17 | 1.245              | 1.32 | V    |                            |  |

<sup>1.</sup> Typical values assume  $V_{DD}$  = 5.0 V, temperature = 25°C,  $f_{ADCK}$  = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

2. Incremental I<sub>DD</sub> added to MCU mode current.

3. Values are based on characterization results, not tested in production.

4. Reference the ADC module specification for more information on calculating conversion times.

5. Based on typical input pad leakage current.

6. LVI must be enabled, (LVIPWRD = 0, in CONFIG1). Voltage input to ADCH4:0 = \$1A, an ADC conversion on this channel allows user to determine supply voltage.

# **Chapter 18 Ordering Information and Mechanical Specifications**

## 18.1 Introduction

This section provides ordering information for the MC68HC908QL4, MC68HC908QL3, and MC68HC908QL2 along with the dimensions for:

- 16-pin small outline integrated circuit (SOIC) package

- 16-pin thin shrink small outline package (TSSOP)

## 18.2 MC Order Numbers

Table 18-1. MC Order Numbers

| MC Order Number | ADC | FLASH Memory | Package   |

|-----------------|-----|--------------|-----------|

| MC908QL4        | Yes | 4096 bytes   | 16-pins   |

| MC908QL3        | No  | 4096 bytes   | SOIC,     |

| MC908QL2        | Yes | 2048 bytes   | and TSSOP |

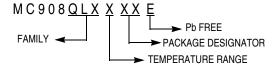

Temperature and package designators:

$C = -40^{\circ}C \text{ to } +85^{\circ}C$

$V = -40^{\circ}C \text{ to } +105^{\circ}C$

$M = -40^{\circ}C \text{ to } + 125^{\circ}C$

DW = Small outline integrated circuit package (SOIC)

DT = Thin shrink small outline package (TSSOP)

Figure 18-1. Device Numbering System

## 18.3 Package Dimensions

Refer to the following pages for detailed package dimensions.

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### E-mail:

support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

## Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street

Tai Po Industrial Estate

Tai Po, N.T., Hong Kong

+800 2666 8080

support.asia@freescale.com

For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405

Denver, Colorado 80217

1-800-441-2447 or 303-675-2140

Fax: 303-675-2150

LDCForFreescaleSemiconductor@hibbertgroup.com

RoHS-compliant and/or Pb- free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb- free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale.s Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2005. All rights reserved.