Welcome to **E-XFL.COM**

Understanding <u>Embedded - CPLDs (Complex Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

### **Applications of Embedded - CPLDs**

| Details                         |                                                           |

|---------------------------------|-----------------------------------------------------------|

| Product Status                  | Obsolete                                                  |

| Programmable Type               | In System Programmable                                    |

| Delay Time tpd(1) Max           | 15 ns                                                     |

| Voltage Supply - Internal       | 4.75V ~ 5.25V                                             |

| Number of Logic Elements/Blocks | 20                                                        |

| Number of Macrocells            | 320                                                       |

| Number of Gates                 | 6000                                                      |

| Number of I/O                   | 60                                                        |

| Operating Temperature           | 0°C ~ 70°C (TA)                                           |

| Mounting Type                   | Surface Mount                                             |

| Package / Case                  | 84-LCC (J-Lead)                                           |

| Supplier Device Package         | 84-PLCC (29.31x29.31)                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/epm9320lc84-15 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

All MAX 9000 device packages provide four dedicated inputs for global control signals with large fan-outs. Each I/O pin has an associated I/O cell register with a clock enable control on the periphery of the device. As outputs, these registers provide fast clock-to-output times; as inputs, they offer quick setup times.

MAX 9000 EPLDs provide 5.0-V in-system programmability (ISP). This feature allows the devices to be programmed and reprogrammed on the printed circuit board (PCB) for quick and efficient iterations during design development and debug cycles. MAX 9000 devices are guaranteed for 100 program and erase cycles.

MAX 9000 EPLDs contain 320 to 560 macrocells that are combined into groups of 16 macrocells, called logic array blocks (LABs). Each macrocell has a programmable-AND/fixed-OR array and a configurable register with independently programmable clock, clock enable, clear, and preset functions. For increased flexibility, each macrocell offers a dual-output structure that allows the register and the product terms to be used independently. This feature allows register-rich and combinatorial-intensive designs to be implemented efficiently. The dual-output structure of the MAX 9000 macrocell also improves logic utilization, thus increasing the effective capacity of the devices. To build complex logic functions, each macrocell can be supplemented with both shareable expander product terms and high-speed parallel expander product terms to provide up to 32 product terms per macrocell.

The MAX 9000 family provides programmable speed/power optimization. Speed-critical portions of a design can run at high speed/full power, while the remaining portions run at reduced speed/low power. This speed/power optimization feature enables the user to configure one or more macrocells to operate at 50% or less power while adding only a nominal timing delay. MAX 9000 devices also provide an option that reduces the slew rate of the output buffers, minimizing noise transients when non-speed-critical signals are switching. MAX 9000 devices offer the MultiVolt feature, which allows output drivers to be set for either 3.3-V or 5.0-V operation in mixed-voltage systems.

The MAX 9000 family is supported by Altera's MAX+PLUS II development system, a single, integrated software package that offers schematic, text—including VHDL, Verilog HDL, and the Altera Hardware Description Language (AHDL)—and waveform design entry, compilation and logic synthesis, simulation and timing analysis, and device programming. The MAX+PLUS II software provides EDIF 2 0 0 and 3 0 0, LPM, and other interfaces for additional design entry and simulation support from other industry-standard PC- and UNIX-workstation-based EDA tools. The MAX+PLUS II software runs on Windows-based PCs as well as Sun SPARCstation, HP 9000 Series 700/800, and IBM RISC System/6000 workstations.

For more information on development tools, see the MAX+PLUS II Programmable Logic Development System & Software Data Sheet.

# Functional Description

MAX 9000 devices use a third-generation MAX architecture that yields both high performance and a high degree of utilization for most applications. The MAX 9000 architecture includes the following elements:

- Logic array blocks

- Macrocells

- Expander product terms (shareable and parallel)

- FastTrack Interconnect

- Dedicated inputs

- I/O cells

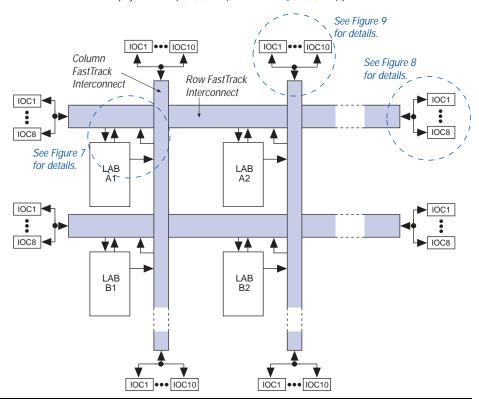

Figure 1 shows a block diagram of the MAX 9000 architecture.

#### Macrocells

The MAX 9000 macrocell consists of three functional blocks: the product terms, the product-term select matrix, and the programmable register. The macrocell can be individually configured for both sequential and combinatorial logic operation. See Figure 3.

LAB Local Array Global Global 33 Row Clear Clocks FastTrack Parallel Interconnect 2 Expanders Inputs Macrocell Register Programmable (from Other Input Select Bypass Register Macrocells) To Row or Column FastTrack Clock/ Interconnect Product-(11) Enable ENA Select Select Matrix Clear Select 1 Local Array Feedback 16 Local 16 Shareable Feedbacks Expander Product

Figure 3. MAX 9000 Macrocell & Local Array

Combinatorial logic is implemented in the local array, which provides five product terms per macrocell. The product-term select matrix allocates these product terms for use as either primary logic inputs (to the  $\mbox{OR}$  and  $\mbox{MOR}$  gates) to implement combinatorial functions, or as secondary inputs to the macrocell's register clear, preset, clock, and clock enable control functions. Two kinds of expander product terms ("expanders") are available to supplement macrocell logic resources:

- Shareable expanders, which are inverted product terms that are fed back into the logic array

- Parallel expanders, which are product terms borrowed from adjacent macrocells

The MAX+PLUS II software automatically optimizes product-term allocation according to the logic requirements of the design.

For registered functions, each macrocell register can be individually programmed for D, T, JK, or SR operation with programmable clock control. The flipflop can also be bypassed for combinatorial operation. During design entry, the user specifies the desired register type; the MAX+PLUS II software then selects the most efficient register operation for each registered function to optimize resource utilization.

Each programmable register can be clocked in three different modes:

- By either global clock signal. This mode achieves the fastest clock-tooutput performance.

- By a global clock signal and enabled by an active-high clock enable. This mode provides an enable on each flipflop while still achieving the fast clock-to-output performance of the global clock.

- By an array clock implemented with a product term. In this mode, the flipflop can be clocked by signals from buried macrocells or I/O pins.

Two global clock signals are available. As shown in Figure 2, these global clock signals can be the true or the complement of either of the global clock pins (DIN1 and DIN2).

Each register also supports asynchronous preset and clear functions. As shown in Figure 3, the product-term select matrix allocates product terms to control these operations. Although the product-term-driven preset and clear inputs to registers are active high, active-low control can be obtained by inverting the signal within the logic array. In addition, each register clear function can be individually driven by the dedicated global clear pin (DIN3). The global clear can be programmed for active-high or active-low operation.

All MAX 9000 macrocells offer a dual-output structure that provides independent register and combinatorial logic output within the same macrocell. This function is implemented by a process called register packing. When register packing is used, the product-term select matrix allocates one product term to the D input of the register, while the remaining product terms can be used to implement unrelated combinatorial logic. Both the registered and the combinatorial output of the macrocell can feed either the FastTrack Interconnect or the LAB local array.

Figure 6. MAX 9000 Device Interconnect Resources

Each LAB is named on the basis of its physical row (A, B, C, etc.) and column (1, 2, 3, etc.) position within the device.

The LABs within MAX 9000 devices are arranged into a matrix of columns and rows. Table 5 shows the number of columns and rows in each MAX 9000 device.

| Table 5. MAX 9000 Rows & Columns |      |         |  |  |  |  |

|----------------------------------|------|---------|--|--|--|--|

| Devices                          | Rows | Columns |  |  |  |  |

| EPM9320, EPM9320A                | 4    | 5       |  |  |  |  |

| EPM9400                          | 5    | 5       |  |  |  |  |

| EPM9480                          | 6    | 5       |  |  |  |  |

| EPM9560, EPM9560A                | 7    | 5       |  |  |  |  |

A row interconnect channel can be fed by the output of the macrocell through a 4-to-1 multiplexer that the macrocell shares with three column channels. If the multiplexer is used for a macrocell-to-row connection, the three column signals can access another row channel via an additional 3-to-1 multiplexer. Within any LAB, the multiplexers provide all 48 column channels with access to 32 row channels.

#### Row-to-I/O Cell Connections

Figure 8 illustrates the connections between row interconnect channels and IOCs. An input signal from an IOC can drive two separate row channels. When an IOC is used as an output, the signal is driven by a 10-to-1 multiplexer that selects the row channels. Each end of the row channel feeds up to eight IOCs on the periphery of the device.

Figure 8. MAX 9000 Row-to-IOC Connections

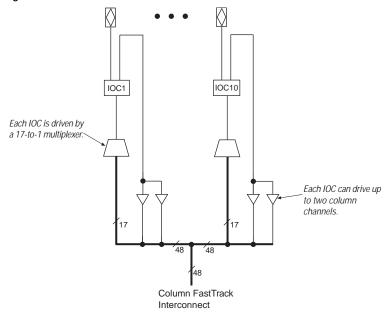

#### Column-to-I/O Cell Connections

Each end of a column channel has up to 10 IOCs (see Figure 9). An input signal from an IOC can drive two separate column channels. When an IOC is used as an output, the signal is driven by a 17-to-1 multiplexer that selects the column channels.

Figure 9. MAX 9000 Column-to-IOC Connections

### **Dedicated Inputs**

In addition to the general-purpose I/O pins, MAX 9000 devices have four dedicated input pins. These dedicated inputs provide low-skew, device-wide signal distribution to the LABs and IOCs in the device, and are typically used for global clock, clear, and output enable control signals. The global control signals can feed the macrocell or IOC clock and clear inputs, as well as the IOC output enable. The dedicated inputs can also be used as general-purpose data inputs because they can feed the row FastTrack Interconnect (see Figure 2 on page 7).

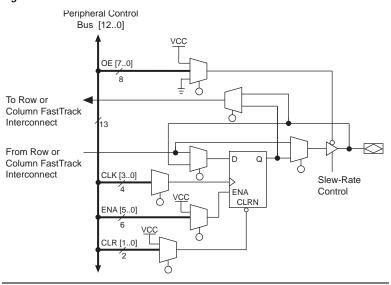

#### I/O Cells

Figure 10 shows the IOC block diagram. Signals enter the MAX 9000 device from either the I/O pins that provide general-purpose input capability or from the four dedicated inputs. The IOCs are located at the ends of the row and column interconnect channels.

Figure 10. MAX 9000 IOC

I/O pins can be used as input, output, or bidirectional pins. Each IOC has an IOC register with a clock enable input. This register can be used either as an input register for external data that requires fast setup times, or as an output register for data that requires fast clock-to-output performance. The IOC register clock enable allows the global clock to be used for fast clock-to-output performance, while maintaining the flexibility required for selective clocking.

The clock, clock enable, clear, and output enable controls for the IOCs are provided by a network of I/O control signals. These signals can be supplied by either the dedicated input pins or internal logic. The IOC control-signal paths are designed to minimize the skew across the device. All control-signal sources are buffered onto high-speed drivers that drive the signals around the periphery of the device. This "peripheral bus" can be configured to provide up to eight output enable signals, up to four clock signals, up to six clock enable signals, and up to two clear signals. Table 6 on page 18 shows the sources that drive the peripheral bus and how the IOC control signals share the peripheral bus.

The output buffer in each IOC has an adjustable output slew rate that can be configured for low-noise or high-speed performance. A slower slew rate reduces board-level noise and adds a nominal timing delay to the output buffer delay ( $t_{OD}$ ) parameter. The fast slew rate should be used for speed-critical outputs in systems that are adequately protected against noise. Designers can specify the slew rate on a pin-by-pin basis during design entry or assign a default slew rate to all pins on a global basis. The slew rate control affects both rising and falling edges of the output signals.

| Table 6. Peripheral Bus Sources |                     |            |            |                     |  |  |  |

|---------------------------------|---------------------|------------|------------|---------------------|--|--|--|

| Peripheral Control              |                     | Sou        | ırce       |                     |  |  |  |

| Signal                          | EPM9320<br>EPM9320A | EPM9400    | EPM9480    | EPM9560<br>EPM9560A |  |  |  |

| OE0/ENA0                        | Row C               | Row E      | Row F      | Row G               |  |  |  |

| OE1/ENA1                        | Row B               | Row E      | Row F      | Row F               |  |  |  |

| OE2/ENA2                        | Row A               | Row E      | Row E      | Row E               |  |  |  |

| OE3/ENA3                        | Row B               | Row B      | Row B      | Row B               |  |  |  |

| OE4/ENA4                        | Row A               | Row A      | Row A      | Row A               |  |  |  |

| OE5                             | Row D               | Row D      | Row D      | Row D               |  |  |  |

| OE6                             | Row C               | Row C      | Row C      | Row C               |  |  |  |

| OE7/CLR1                        | Row B/GOE           | Row B/GOE  | Row B/GOE  | Row B/GOE           |  |  |  |

| CLR0/ENA5                       | Row A/GCLR          | Row A/GCLR | Row A/GCLR | Row A/GCLR          |  |  |  |

| CLK0                            | GCLK1               | GCLK1      | GCLK1      | GCLK1               |  |  |  |

| CLK1                            | GCLK2               | GCLK2      | GCLK2      | GCLK2               |  |  |  |

| CLK2                            | Row D               | Row D      | Row D      | Row D               |  |  |  |

| CLK3                            | Row C               | Row C      | Row C      | Row C               |  |  |  |

# Output Configuration

The MAX 9000 device architecture supports the MultiVolt I/O interface feature, which allows MAX 9000 devices to interface with systems of differing supply voltages. The 5.0-V devices in all packages can be set for 3.3-V or 5.0-V I/O pin operation. These devices have one set of  $V_{CC}$  pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

The VCCINT pins must always be connected to a 5.0-V power supply. With a 5.0-V  $V_{\rm CCINT}$  level, input voltages are at TTL levels and are therefore compatible with 3.3-V and 5.0-V inputs.

By combining the pulse and shift times for each of the programming stages, the program or verify time can be derived as a function of the TCK frequency, the number of devices, and specific target device(s). Because different ISP-capable devices have a different number of EEPROM cells, both the total fixed and total variable times are unique for a single device.

### Programming a Single MAX 9000 Device

The time required to program a single MAX 9000 device in-system can be calculated from the following formula:

$$t_{PROG} = t_{PPULSE} + \frac{Cycle_{PTCK}}{f_{TCK}}$$

where:  $t_{PROG} = t_{PPULSE}$  = Programming time  $t_{PPULSE} = t_{PPULSE}$  = Sum of the fixed times to erase, program, and

verify the EEPROM cells

Cycle<sub>PTCK</sub> = Number of TCK cycles to program a device

$f_{TCK}$  = TCK frequency

The ISP times for a stand-alone verification of a single MAX 9000 device can be calculated from the following formula:

$$t_{VER} = t_{VPULSE} + \frac{Cycle_{VTCK}}{f_{TCK}}$$

where:  $t_{VER}$  = Verify time

$t_{VPULSE}$  = Sum of the fixed times to verify the EEPROM cells

$Cycle_{VTCK}$  = Number of TCK cycles to verify a device

The programming times described in Tables 7 through 9 are associated with the worst-case method using the ISP algorithm.

| Table 7. MAX 9000 t <sub>PULSE</sub> & Cycle <sub>TCK</sub> Values |                         |                       |                         |                       |  |  |  |

|--------------------------------------------------------------------|-------------------------|-----------------------|-------------------------|-----------------------|--|--|--|

| Device                                                             | Progra                  | ımming                | Stand-Alone             | e Verification        |  |  |  |

|                                                                    | t <sub>PPULSE</sub> (s) | Cycle <sub>PTCK</sub> | t <sub>VPULSE</sub> (s) | Cycle <sub>VTCK</sub> |  |  |  |

| EPM9320<br>EPM9320A                                                | 11.79                   | 2,966,000             | 0.15                    | 1,806,000             |  |  |  |

| EPM9400                                                            | 12.00                   | 3,365,000             | 0.15                    | 2,090,000             |  |  |  |

| EPM9480                                                            | 12.21                   | 3,764,000             | 0.15                    | 2,374,000             |  |  |  |

| EPM9560<br>EPM9560A                                                | 12.42                   | 4,164,000             | 0.15                    | 2,658,000             |  |  |  |

Tables 8 and 9 show the in-system programming and stand alone verification times for several common test clock frequencies.

| Table 8. MAX 9000 In-System Programming Times for Different Test Clock Frequencies |        |                  |       |       |         |         |         |        |       |

|------------------------------------------------------------------------------------|--------|------------------|-------|-------|---------|---------|---------|--------|-------|

| Device                                                                             |        | f <sub>TCK</sub> |       |       |         |         |         |        | Units |

|                                                                                    | 10 MHz | 5 MHz            | 2 MHz | 1 MHz | 500 kHz | 200 kHz | 100 kHz | 50 kHz |       |

| EPM9320<br>EPM9320A                                                                | 12.09  | 12.38            | 13.27 | 14.76 | 17.72   | 26.62   | 41.45   | 71.11  | S     |

| EPM9400                                                                            | 12.34  | 12.67            | 13.68 | 15.37 | 18.73   | 28.83   | 45.65   | 79.30  | S     |

| EPM9480                                                                            | 12.59  | 12.96            | 14.09 | 15.98 | 19.74   | 31.03   | 49.85   | 87.49  | S     |

| EPM9560<br>EPM9560A                                                                | 12.84  | 13.26            | 14.50 | 16.59 | 20.75   | 33.24   | 54.06   | 95.70  | S     |

| Table 9. MAX 9000 Stand-Alone Verification Times for Different Test Clock Frequencies |        |       |       |       |         |         |         |        |       |

|---------------------------------------------------------------------------------------|--------|-------|-------|-------|---------|---------|---------|--------|-------|

| Device                                                                                |        |       |       | f     | TCK     |         |         |        | Units |

|                                                                                       | 10 MHz | 5 MHz | 2 MHz | 1 MHz | 500 kHz | 200 kHz | 100 kHz | 50 kHz |       |

| EPM9320<br>EPM9320A                                                                   | 0.33   | 0.52  | 1.06  | 1.96  | 3.77    | 9.18    | 18.21   | 36.27  | S     |

| EPM9400                                                                               | 0.36   | 0.57  | 1.20  | 2.24  | 4.33    | 10.60   | 21.05   | 41.95  | S     |

| EPM9480                                                                               | 0.39   | 0.63  | 1.34  | 2.53  | 4.90    | 12.02   | 23.89   | 47.63  | S     |

| EPM9560<br>EPM9560A                                                                   | 0.42   | 0.69  | 1.48  | 2.81  | 5.47    | 13.44   | 26.73   | 53.31  | S     |

The instruction register length for MAX 9000 devices is 10 bits. EPM9320A and EPM9560A devices support a 16-bit UESCODE register. Tables 11 and 12 show the boundary-scan register length and device IDCODE information for MAX 9000 devices.

| Table 11. MAX 9000 Boundary-Scan Register Length |     |  |  |  |  |

|--------------------------------------------------|-----|--|--|--|--|

| Device Boundary-Scan Register Length             |     |  |  |  |  |

| EPM9320, EPM9320A                                | 504 |  |  |  |  |

| EPM9400                                          | 552 |  |  |  |  |

| EPM9480                                          | 600 |  |  |  |  |

| EPM9560, EPM9560A                                | 648 |  |  |  |  |

| Table 12. 32-Bit MAX 9000 Device IDCODE Note (1) |                     |                              |                                   |              |  |  |  |

|--------------------------------------------------|---------------------|------------------------------|-----------------------------------|--------------|--|--|--|

| Device                                           |                     | IDCODE (32 Bits)             |                                   |              |  |  |  |

|                                                  | Version<br>(4 Bits) | Part Number<br>(16 Bits) (2) | Manufacturer's Identity (11 Bits) | 1<br>(1 Bit) |  |  |  |

| EPM9320A (3)                                     | 0000                | 1001 0011 0010 0000          | 00001101110                       | 1            |  |  |  |

| EPM9400                                          | 0000                | 1001 0100 0000 0000          | 00001101110                       | 1            |  |  |  |

| EPM9480                                          | 0000                | 1001 0100 1000 0000          | 00001101110                       | 1            |  |  |  |

| EPM9560A (3)                                     | 0000                | 1001 0101 0110 0000          | 00001101110                       | 1            |  |  |  |

#### Notes:

- (1) The IDCODE's least significant bit (LSB) is always 1.

- (2) The most significant bit (MSB) is on the left.

- (3) Although the EPM9320A and EPM9560A devices support the IDCODE instruction, the EPM9320 and EPM9560 devices do not.

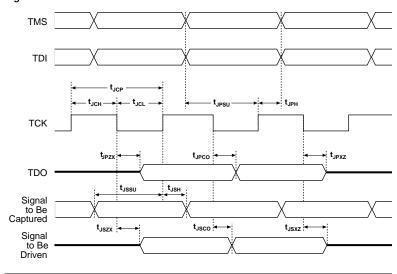

Figure 11 shows the timing requirements for the JTAG signals.

Figure 11. MAX 9000 JTAG Waveforms

Table 13 shows the JTAG timing parameters and values for MAX 9000 devices.

| Table 1           | Table 13. JTAG Timing Parameters & Values for MAX 9000 Devices |     |     |      |  |  |  |  |  |

|-------------------|----------------------------------------------------------------|-----|-----|------|--|--|--|--|--|

| Symbol            | Parameter                                                      | Min | Max | Unit |  |  |  |  |  |

| t <sub>JCP</sub>  | TCK clock period                                               | 100 |     | ns   |  |  |  |  |  |

| t <sub>JCH</sub>  | TCK clock high time                                            | 50  |     | ns   |  |  |  |  |  |

| t <sub>JCL</sub>  | TCK clock low time                                             | 50  |     | ns   |  |  |  |  |  |

| t <sub>JPSU</sub> | JTAG port setup time                                           | 20  |     | ns   |  |  |  |  |  |

| t <sub>JPH</sub>  | JTAG port hold time                                            | 45  |     | ns   |  |  |  |  |  |

| t <sub>JPCO</sub> | JTAG port clock to output                                      |     | 25  | ns   |  |  |  |  |  |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output                       |     | 25  | ns   |  |  |  |  |  |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance                       |     | 25  | ns   |  |  |  |  |  |

| t <sub>JSSU</sub> | Capture register setup time                                    | 20  |     | ns   |  |  |  |  |  |

| t <sub>JSH</sub>  | Capture register hold time                                     | 45  |     | ns   |  |  |  |  |  |

| t <sub>JSCO</sub> | Update register clock to output                                |     | 25  | ns   |  |  |  |  |  |

| t <sub>JSZX</sub> | Update register high impedance to valid output                 |     | 25  | ns   |  |  |  |  |  |

| t <sub>JSXZ</sub> | Update register valid output to high impedance                 |     | 25  | ns   |  |  |  |  |  |

For detailed information on JTAG operation in MAX 9000 devices, refer to Application Note 39 (IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices).

# Operating Conditions

Tables 14 through 20 provide information on absolute maximum ratings, recommended operating conditions, operating conditions, and capacitance for MAX 9000 devices.

| Table 14. MAX 9000 Device Absolute Maximum Ratings   Note (1) |                                             |                                    |      |     |      |  |  |  |

|---------------------------------------------------------------|---------------------------------------------|------------------------------------|------|-----|------|--|--|--|

| Symbol                                                        | Parameter                                   | Conditions                         | Min  | Max | Unit |  |  |  |

| V <sub>CC</sub>                                               | Supply voltage                              | With respect to ground (2)         | -2.0 | 7.0 | V    |  |  |  |

| VI                                                            | DC input voltage                            |                                    | -2.0 | 7.0 | V    |  |  |  |

| V <sub>CCISP</sub>                                            | Supply voltage during in-system programming |                                    | -2.0 | 7.0 | ٧    |  |  |  |

| I <sub>OUT</sub>                                              | DC output current, per pin                  |                                    | -25  | 25  | mA   |  |  |  |

| T <sub>STG</sub>                                              | Storage temperature                         | No bias                            | -65  | 150 | ° C  |  |  |  |

| T <sub>AMB</sub>                                              | Ambient temperature                         | Under bias                         | -65  | 135 | ° C  |  |  |  |

| TJ                                                            | Junction temperature                        | Ceramic packages, under bias       |      | 150 | ° C  |  |  |  |

|                                                               |                                             | PQFP and RQFP packages, under bias |      | 135 | ° C  |  |  |  |

| Table 1            | Table 15. MAX 9000 Device Recommended Operating Conditions |                    |                |                          |      |  |  |  |

|--------------------|------------------------------------------------------------|--------------------|----------------|--------------------------|------|--|--|--|

| Symbol             | Parameter                                                  | Conditions         | Min            | Max                      | Unit |  |  |  |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers        | (3), (4)           | 4.75<br>(4.50) | 5.25<br>(5.50)           | V    |  |  |  |

| V <sub>CCIO</sub>  | Supply voltage for output drivers, 5.0-V operation         | (3), (4)           | 4.75<br>(4.50) | 5.25<br>(5.50)           | ٧    |  |  |  |

|                    | Supply voltage for output drivers, 3.3-V operation         | (3), (4)           | 3.00<br>(3.00) | 3.60<br>(3.60)           | ٧    |  |  |  |

| V <sub>CCISP</sub> | Supply voltage during in-system programming                |                    | 4.75           | 5.25                     | V    |  |  |  |

| V <sub>I</sub>     | Input voltage                                              |                    | -0.5           | V <sub>CCINT</sub> + 0.5 | ٧    |  |  |  |

| Vo                 | Output voltage                                             |                    | 0              | V <sub>CCIO</sub>        | V    |  |  |  |

| T <sub>A</sub>     | Ambient temperature                                        | For commercial use | 0              | 70                       | ° C  |  |  |  |

|                    |                                                            | For industrial use | -40            | 85                       | ° C  |  |  |  |

| T <sub>J</sub>     | Junction temperature                                       | For commercial use | 0              | 90                       | ° C  |  |  |  |

|                    |                                                            | For industrial use | -40            | 105                      | ° C  |  |  |  |

| t <sub>R</sub>     | Input rise time                                            |                    |                | 40                       | ns   |  |  |  |

| t <sub>F</sub>     | Input fall time                                            |                    |                | 40                       | ns   |  |  |  |

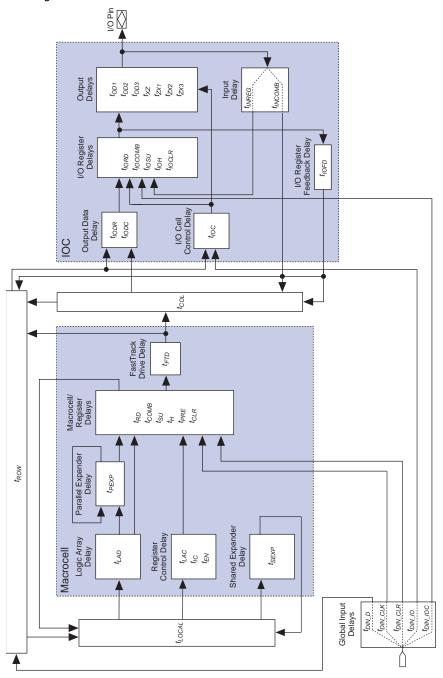

### **Timing Model**

The continuous, high-performance FastTrack Interconnect ensures predictable performance and accurate simulation and timing analysis. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and hence have unpredictable performance. Timing simulation and delay prediction are available with the MAX+PLUS II Simulator and Timing Analyzer, or with industry-standard EDA tools. The Simulator offers both pre-synthesis functional simulation to evaluate logic design accuracy and post-synthesis timing simulation with 0.1-ns resolution. The Timing Analyzer provides point-to-point timing delay information, setup and hold time prediction, and device-wide performance analysis.

The MAX 9000 timing model in Figure 14 shows the delays that correspond to various paths and functions in the circuit. This model contains three distinct parts: the macrocell, IOC, and interconnect, including the row and column FastTrack Interconnect and LAB local array paths. Each parameter shown in Figure 14 is expressed as a worst-case value in the internal timing characteristics tables in this data sheet. Hand-calculations that use the MAX 9000 timing model and these timing parameters can be used to estimate MAX 9000 device performance.

For more information on calculating MAX 9000 timing delays, see *Application Note 77 (Understanding MAX 9000 Timing).*

Figure 14. MAX 9000 Timing Model

| Table 24             | 1. Interconnect Delays                     |            |     |     |       |       |     |     |      |

|----------------------|--------------------------------------------|------------|-----|-----|-------|-------|-----|-----|------|

| Symbol               | Parameter                                  | Conditions |     |     | Speed | Grade |     |     | Unit |

|                      |                                            |            |     | 10  | -1    | 15    | -2  | 20  |      |

|                      |                                            |            | Min | Max | Min   | Max   | Min | Max |      |

| t <sub>LOCAL</sub>   | LAB local array delay                      |            |     | 0.5 |       | 0.5   |     | 0.5 | ns   |

| t <sub>ROW</sub>     | FastTrack row delay                        | (6)        |     | 0.9 |       | 1.4   |     | 2.0 | ns   |

| t <sub>COL</sub>     | FastTrack column delay                     | (6)        |     | 0.9 |       | 1.7   |     | 3.0 | ns   |

| t <sub>DIN_D</sub>   | Dedicated input data delay                 |            |     | 4.0 |       | 4.5   |     | 5.0 | ns   |

| t <sub>DIN_CLK</sub> | Dedicated input clock delay                |            |     | 2.7 |       | 3.5   |     | 4.0 | ns   |

| t <sub>DIN_CLR</sub> | Dedicated input clear delay                |            |     | 4.5 |       | 5.0   |     | 5.5 | ns   |

| t <sub>DIN_IOC</sub> | Dedicated input I/O register clock delay   |            |     | 2.5 |       | 3.5   |     | 4.5 | ns   |

| t <sub>DIN_IO</sub>  | Dedicated input I/O register control delay |            |     | 5.5 |       | 6.0   |     | 6.5 | ns   |

#### Notes to tables:

- These values are specified under the MAX 9000 device recommended operating conditions, shown in Table 15 on page 27.

- See Application Note 77 (Understanding MAX 9000 Timing) for more information on test conditions for t<sub>PD1</sub> and t<sub>PD2</sub> delays.

- (3) This parameter is a guideline that is sample-tested only. It is based on extensive device characterization. This parameter applies for both global and array clocking as well as both macrocell and I/O cell registers.

- (4) Measured with a 16-bit loadable, enabled, up/down counter programmed in each LAB.

- (5) The  $t_{LPA}$  parameter must be added to the  $t_{LOCAL}$  parameter for macrocells running in low-power mode.

- (6) The t<sub>ROW</sub>, t<sub>COL</sub>, and t<sub>IOC</sub> delays are worst-case values for typical applications. Post-compilation timing simulation or timing analysis is required to determine actual worst-case performance.

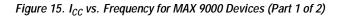

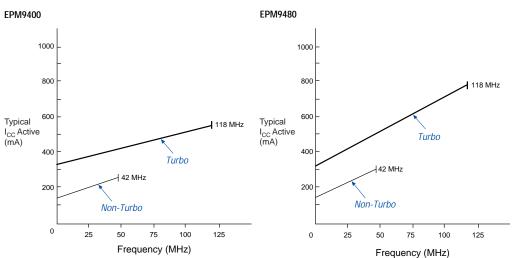

## Power Consumption

The supply power (P) versus frequency ( $f_{MAX}$ ) for MAX 9000 devices can be calculated with the following equation:

$$P = P_{INT} + P_{IO} = I_{CCINT} \times V_{CC} + P_{IO}$$

The  $P_{\rm IO}$  value, which depends on the device output load characteristics and switching frequency, can be calculated using the guidelines given in *Application Note 74 (Evaluating Power for Altera Devices)*. The  $I_{\rm CCINT}$  value depends on the switching frequency and the application logic.

The I<sub>CCINT</sub> value is calculated with the following equation:

$$I_{CCINT} = (A \times MC_{TON}) + [B \times (MC_{DEV} - MC_{TON})] + (C \times MC_{USED} \times f_{MAX} \times tog_{LC})$$

#### Notes:

- (1) All pins not listed are user I/O pins.

- (2) Perform a complete thermal analysis before committing a design to this device package. See Application Note 74 (Evaluating Power for Altera Devices).

- (3) EPM9320A devices are not offered in this package.

- (4) During in-system programming, each device's VPP pin must be connected to the 5.0-V power supply. During normal device operation, the VPP pin is pulled up internally and can be connected to the 5.0-V supply or left unconnected.

- (5) The user I/O pin count includes dedicated input pins and all I/O pins.

| Table 27. EPM9400 Dedicated Pin-Outs Note (1) |                                       |                                                                                                                                                |                                                                                                                                              |

|-----------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                      | 84-Pin PLCC (2)                       | 208-Pin RQFP                                                                                                                                   | 240-Pin RQFP                                                                                                                                 |

| DIN1 (GCLK1)                                  | 2                                     | 182                                                                                                                                            | 210                                                                                                                                          |

| DIN2 (GCLK2)                                  | 1                                     | 183                                                                                                                                            | 211                                                                                                                                          |

| DIN3 (GCLR)                                   | 12                                    | 153                                                                                                                                            | 187                                                                                                                                          |

| DIN4 (GOE)                                    | 74                                    | 4                                                                                                                                              | 234                                                                                                                                          |

| TCK                                           | 43                                    | 78                                                                                                                                             | 91                                                                                                                                           |

| TMS                                           | 54                                    | 49                                                                                                                                             | 68                                                                                                                                           |

| TDI                                           | 42                                    | 79                                                                                                                                             | 92                                                                                                                                           |

| TDO                                           | 31                                    | 108                                                                                                                                            | 114                                                                                                                                          |

| GND                                           | 6, 13, 20, 26, 27, 47, 60, 66, 69, 73 | 14, 20, 24, 31, 35, 41, 42,<br>43, 44, 46, 47, 66, 85, 102,<br>110, 113, 114, 115, 116,<br>118, 121, 122, 132, 133,<br>143, 152, 170, 189, 206 | 5, 14, 25, 34, 45, 54, 65,<br>66, 81, 96, 110, 115, 126,<br>127, 146, 147, 166, 167,<br>186, 200, 216, 229                                   |

| VCCINT (5.0 V only)                           | 16, 23, 30, 56, 63, 70                | 10, 19, 30, 45, 112, 128, 139, 148                                                                                                             | 4, 24, 44, 64, 117, 137, 157, 177                                                                                                            |

| VCCIO (3.3 or 5.0 V)                          | 17, 37, 59, 80                        | 5, 25, 36, 55, 72, 91, 111, 127, 138, 159, 176, 195                                                                                            | 15, 35, 55, 73, 86, 101,<br>116, 136, 156, 176, 192,<br>205, 220, 235                                                                        |

| No Connect (N.C.)                             | _                                     | 6, 7, 8, 9, 11, 12, 13, 109, 144, 145, 146, 147, 149, 150, 151                                                                                 | 1, 2, 3, 6, 7, 8, 9, 10, 11, 12, 13, 168, 169, 170, 171, 172, 173, 174, 175, 178, 179, 180, 181, 182, 183, 184, 185, 236, 237, 238, 239, 240 |

| VPP (3)                                       | 55                                    | 48                                                                                                                                             | 67                                                                                                                                           |

| Total User I/O Pins (4)                       | 59                                    | 139                                                                                                                                            | 159                                                                                                                                          |

#### Notes:

- (1) All pins not listed are user I/O pins.

- (2) Perform a complete thermal analysis before committing a design to this device package. See *Application Note 74* (Evaluating Power for Altera Devices) for more information.

- (3) During in-system programming, each device's VPP pin must be connected to the 5.0-V power supply. During normal device operation, the VPP pin is pulled up internally and can be connected to the 5.0-V supply or left unconnected.

- (4) The user I/O pin count includes dedicated input pins and all I/O pins.

| Table 28. EPM9480 Dedicated Pin-Outs Note (1) |                                                                                                                                    |                                                                                                            |  |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|

| Pin Name                                      | 208-Pin RQFP                                                                                                                       | 240-Pin RQFP                                                                                               |  |

| DIN1 (GCLK1)                                  | 182                                                                                                                                | 210                                                                                                        |  |

| DIN2 (GCLK2)                                  | 183                                                                                                                                | 211                                                                                                        |  |

| DIN3 (GCLR)                                   | 153                                                                                                                                | 187                                                                                                        |  |

| DIN4 (GOE)                                    | 4                                                                                                                                  | 234                                                                                                        |  |

| TCK                                           | 78                                                                                                                                 | 91                                                                                                         |  |

| TMS                                           | 49                                                                                                                                 | 68                                                                                                         |  |

| TDI                                           | 79                                                                                                                                 | 92                                                                                                         |  |

| TDO                                           | 108                                                                                                                                | 114                                                                                                        |  |

| GND                                           | 14, 20, 24, 31, 35, 41, 42, 43, 44, 46, 47, 66, 85, 102, 110, 113, 114, 115, 116, 118, 121, 122, 132, 133, 143, 152, 170, 189, 206 | 5, 14, 25, 34, 45, 54, 65,<br>66, 81, 96, 110, 115, 126,<br>127, 146, 147, 166, 167,<br>186, 200, 216, 229 |  |

| VCCINT (5.0 V only)                           | 10, 19, 30, 45, 112, 128, 139, 148                                                                                                 | 4, 24, 44, 64, 117, 137,<br>157, 177                                                                       |  |

| VCCIO (3.3 or 5.0 V)                          | 5, 25, 36, 55, 72, 91, 111, 127, 138, 159, 176, 195                                                                                | 15, 35, 55, 73, 86, 101,<br>116, 136, 156, 176, 192,<br>205, 220, 235                                      |  |

| No Connect (N.C.)                             | 6, 7, 8, 9, 109, 149, 150,<br>151                                                                                                  | 1, 2, 3, 178, 179, 180,<br>181, 182, 183, 184, 185,<br>236, 237, 238, 239, 240                             |  |

| VPP (2)                                       | 48                                                                                                                                 | 67                                                                                                         |  |

| Total User I/O Pins (3)                       | 146                                                                                                                                | 175                                                                                                        |  |

#### Notes:

- (1) All pins not listed are user I/O pins.

- (2) During in-system programming, each device's VPP pin must be connected to the 5.0-V power supply. During normal device operation, the VPP pin is pulled up internally and can be connected to the 5.0-V supply or left unconnected.

- (3) The user I/O pin count includes dedicated input pins and all I/O pins.