Welcome to **E-XFL.COM**

**Understanding Embedded - CPLDs (Complex Programmable Logic Devices)**

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixed-function ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

### **Applications of Embedded - CPLDs**

| Details                         |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Obsolete                                                    |

| Programmable Type               | In System Programmable                                      |

| Delay Time tpd(1) Max           | 10 ns                                                       |

| Voltage Supply - Internal       | 4.75V ~ 5.25V                                               |

| Number of Logic Elements/Blocks | 35                                                          |

| Number of Macrocells            | 560                                                         |

| Number of Gates                 | 12000                                                       |

| Number of I/O                   | 191                                                         |

| Operating Temperature           | 0°C ~ 70°C (TA)                                             |

| Mounting Type                   | Surface Mount                                               |

| Package / Case                  | 240-BFQFP Exposed Pad                                       |

| Supplier Device Package         | 240-RQFP (32x32)                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/intel/epm9560arc240-10 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## General Description

The MAX 9000 family of in-system-programmable, high-density, high-performance EPLDs is based on Altera's third-generation MAX architecture. Fabricated on an advanced CMOS technology, the EEPROM-based MAX 9000 family provides 6,000 to 12,000 usable gates, pin-to-pin delays as fast as 10 ns, and counter speeds of up to 144 MHz. The -10 speed grade of the MAX 9000 family is compliant with the *PCI Local Bus Specification, Revision 2.2.* Table 3 shows the speed grades available for MAX 9000 devices.

| Table 3. MAX 9000 Speed Grade Availability |     |             |     |  |  |  |  |

|--------------------------------------------|-----|-------------|-----|--|--|--|--|

| Device                                     |     | Speed Grade |     |  |  |  |  |

|                                            | -10 | -15         | -20 |  |  |  |  |

| EPM9320                                    |     | ✓           | ✓   |  |  |  |  |

| EPM9320A                                   | ✓   |             |     |  |  |  |  |

| EPM9400                                    |     | ✓           | ✓   |  |  |  |  |

| EPM9480                                    |     | ✓           | ✓   |  |  |  |  |

| EPM9560                                    |     | ✓           | ✓   |  |  |  |  |

| EPM9560A                                   | ✓   |             |     |  |  |  |  |

Table 4 shows the performance of MAX 9000 devices for typical functions.

| Table 4. MAX 9000 Performance Note (1) |                 |            |           |         |     |  |  |  |

|----------------------------------------|-----------------|------------|-----------|---------|-----|--|--|--|

| Application                            | Macrocells Used |            | Units     |         |     |  |  |  |

|                                        |                 | -10        | -15       | -20     |     |  |  |  |

| 16-bit loadable counter                | 16              | 144        | 118       | 100     | MHz |  |  |  |

| 16-bit up/down counter                 | 16              | 144        | 118       | 100     | MHz |  |  |  |

| 16-bit prescaled counter               | 16              | 144        | 118       | 100     | MHz |  |  |  |

| 16-bit address decode                  | 1               | 5.6 (10)   | 7.9 (15)  | 10 (20) | ns  |  |  |  |

| 16-to-1 multiplexer                    | 1               | 7.7 (12.1) | 10.9 (18) | 16 (26) | ns  |  |  |  |

### Note:

(1) Internal logic array block (LAB) performance is shown. Numbers in parentheses show external delays from row input pin to row I/O pin.

The MAX 9000 architecture supports high-density integration of system-level logic functions. It easily integrates multiple programmable logic devices ranging from PALs, GALs, and 22V10s to field-programmable gate array (FPGA) devices and EPLDs.

All MAX 9000 device packages provide four dedicated inputs for global control signals with large fan-outs. Each I/O pin has an associated I/O cell register with a clock enable control on the periphery of the device. As outputs, these registers provide fast clock-to-output times; as inputs, they offer quick setup times.

MAX 9000 EPLDs provide 5.0-V in-system programmability (ISP). This feature allows the devices to be programmed and reprogrammed on the printed circuit board (PCB) for quick and efficient iterations during design development and debug cycles. MAX 9000 devices are guaranteed for 100 program and erase cycles.

MAX 9000 EPLDs contain 320 to 560 macrocells that are combined into groups of 16 macrocells, called logic array blocks (LABs). Each macrocell has a programmable-AND/fixed-OR array and a configurable register with independently programmable clock, clock enable, clear, and preset functions. For increased flexibility, each macrocell offers a dual-output structure that allows the register and the product terms to be used independently. This feature allows register-rich and combinatorial-intensive designs to be implemented efficiently. The dual-output structure of the MAX 9000 macrocell also improves logic utilization, thus increasing the effective capacity of the devices. To build complex logic functions, each macrocell can be supplemented with both shareable expander product terms and high-speed parallel expander product terms to provide up to 32 product terms per macrocell.

The MAX 9000 family provides programmable speed/power optimization. Speed-critical portions of a design can run at high speed/full power, while the remaining portions run at reduced speed/low power. This speed/power optimization feature enables the user to configure one or more macrocells to operate at 50% or less power while adding only a nominal timing delay. MAX 9000 devices also provide an option that reduces the slew rate of the output buffers, minimizing noise transients when non-speed-critical signals are switching. MAX 9000 devices offer the MultiVolt feature, which allows output drivers to be set for either 3.3-V or 5.0-V operation in mixed-voltage systems.

The MAX 9000 family is supported by Altera's MAX+PLUS II development system, a single, integrated software package that offers schematic, text—including VHDL, Verilog HDL, and the Altera Hardware Description Language (AHDL)—and waveform design entry, compilation and logic synthesis, simulation and timing analysis, and device programming. The MAX+PLUS II software provides EDIF 2 0 0 and 3 0 0, LPM, and other interfaces for additional design entry and simulation support from other industry-standard PC- and UNIX-workstation-based EDA tools. The MAX+PLUS II software runs on Windows-based PCs as well as Sun SPARCstation, HP 9000 Series 700/800, and IBM RISC System/6000 workstations.

For more information on development tools, see the MAX+PLUS II Programmable Logic Development System & Software Data Sheet.

# Functional Description

MAX 9000 devices use a third-generation MAX architecture that yields both high performance and a high degree of utilization for most applications. The MAX 9000 architecture includes the following elements:

- Logic array blocks

- Macrocells

- Expander product terms (shareable and parallel)

- FastTrack Interconnect

- Dedicated inputs

- I/O cells

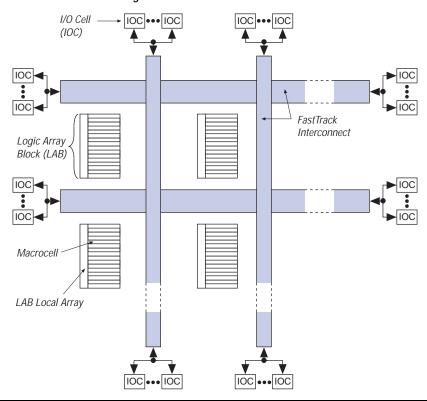

Figure 1 shows a block diagram of the MAX 9000 architecture.

Figure 1. MAX 9000 Device Block Diagram

### Logic Array Blocks

The MAX 9000 architecture is based on linking high-performance, flexible logic array modules called logic array blocks (LABs). LABs consist of 16-macrocell arrays that are fed by the LAB local array, as shown in Figure 2 on page 7. Multiple LABs are linked together via the FastTrack Interconnect, a series of fast, continuous channels that run the entire length and width of the device. The I/O pins are supported by I/O cells (IOCs) located at the end of each row (horizontal) and column (vertical) path of the FastTrack Interconnect.

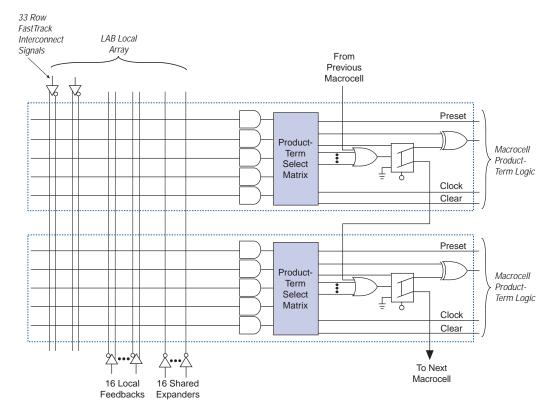

Each LAB is fed by 33 inputs from the row interconnect and 16 feedback signals from the macrocells within the LAB. All of these signals are available within the LAB in their true and inverted form. In addition, 16 shared expander product terms ("expanders") are available in their inverted form, for a total of 114 signals that feed each product term in the LAB. Each LAB is also fed by two low-skew global clocks and one global clear that can be used for register control signals in all 16 macrocells.

For registered functions, each macrocell register can be individually programmed for D, T, JK, or SR operation with programmable clock control. The flipflop can also be bypassed for combinatorial operation. During design entry, the user specifies the desired register type; the MAX+PLUS II software then selects the most efficient register operation for each registered function to optimize resource utilization.

Each programmable register can be clocked in three different modes:

- By either global clock signal. This mode achieves the fastest clock-tooutput performance.

- By a global clock signal and enabled by an active-high clock enable. This mode provides an enable on each flipflop while still achieving the fast clock-to-output performance of the global clock.

- By an array clock implemented with a product term. In this mode, the flipflop can be clocked by signals from buried macrocells or I/O pins.

Two global clock signals are available. As shown in Figure 2, these global clock signals can be the true or the complement of either of the global clock pins (DIN1 and DIN2).

Each register also supports asynchronous preset and clear functions. As shown in Figure 3, the product-term select matrix allocates product terms to control these operations. Although the product-term-driven preset and clear inputs to registers are active high, active-low control can be obtained by inverting the signal within the logic array. In addition, each register clear function can be individually driven by the dedicated global clear pin (DIN3). The global clear can be programmed for active-high or active-low operation.

All MAX 9000 macrocells offer a dual-output structure that provides independent register and combinatorial logic output within the same macrocell. This function is implemented by a process called register packing. When register packing is used, the product-term select matrix allocates one product term to the D input of the register, while the remaining product terms can be used to implement unrelated combinatorial logic. Both the registered and the combinatorial output of the macrocell can feed either the FastTrack Interconnect or the LAB local array.

### Parallel Expanders

Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions. Parallel expanders allow up to 20 product terms to directly feed the macrocell OR logic, with five product terms provided by the macrocell and 15 parallel expanders provided by neighboring macrocells in the LAB. Figure 5 shows how parallel expanders can feed the neighboring macrocell.

Figure 5. MAX 9000 Parallel Expanders

Unused product terms in a macrocell can be allocated to a neighboring macrocell.

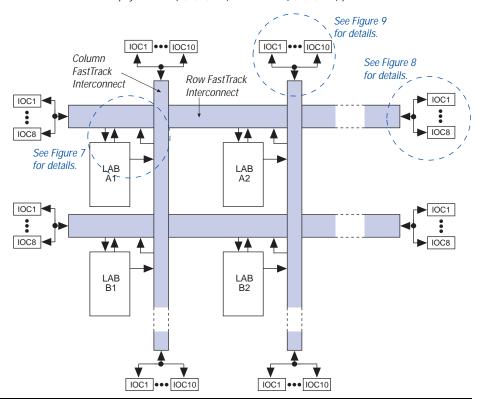

Figure 6. MAX 9000 Device Interconnect Resources

Each LAB is named on the basis of its physical row (A, B, C, etc.) and column (1, 2, 3, etc.) position within the device.

The LABs within MAX 9000 devices are arranged into a matrix of columns and rows. Table 5 shows the number of columns and rows in each MAX 9000 device.

| Table 5. MAX 9000 Rows & Columns |      |         |  |  |  |

|----------------------------------|------|---------|--|--|--|

| Devices                          | Rows | Columns |  |  |  |

| EPM9320, EPM9320A                | 4    | 5       |  |  |  |

| EPM9400                          | 5    | 5       |  |  |  |

| EPM9480                          | 6    | 5       |  |  |  |

| EPM9560, EPM9560A                | 7    | 5       |  |  |  |

Each row of LABs has a dedicated row interconnect that routes signals both into and out of the LABs in the row. The row interconnect can then drive I/O pins or feed other LABs in the device. Each row interconnect has a total of 96 channels. Figure 7 shows how a macrocell drives the row and column interconnect.

48 Column Channels 96 Row Channels Each macrocell drives one row channel. LAB Dual-output -Macrocell 1 macrocell feeds both FastTrack Interconnect and LAB local array. Macrocell 2 To LAB Each macrocell drives one Local Array of three column channels. Additional multiplexer provides column-to-row path if macrocell drives row channel.

Figure 7. MAX 9000 LAB Connections to Row & Column Interconnect

Each macrocell in the LAB can drive one of three separate column interconnect channels. The column channels run vertically across the entire device, and are shared by the macrocells in the same column. The MAX+PLUS II Compiler optimizes connections to a column channel automatically.

A row interconnect channel can be fed by the output of the macrocell through a 4-to-1 multiplexer that the macrocell shares with three column channels. If the multiplexer is used for a macrocell-to-row connection, the three column signals can access another row channel via an additional 3-to-1 multiplexer. Within any LAB, the multiplexers provide all 48 column channels with access to 32 row channels.

### Row-to-I/O Cell Connections

Figure 8 illustrates the connections between row interconnect channels and IOCs. An input signal from an IOC can drive two separate row channels. When an IOC is used as an output, the signal is driven by a 10-to-1 multiplexer that selects the row channels. Each end of the row channel feeds up to eight IOCs on the periphery of the device.

Row FastTrack Interconnect

96

10

10

10C1

Property of the property of the

Figure 8. MAX 9000 Row-to-IOC Connections

### Column-to-I/O Cell Connections

Each end of a column channel has up to 10 IOCs (see Figure 9). An input signal from an IOC can drive two separate column channels. When an IOC is used as an output, the signal is driven by a 17-to-1 multiplexer that selects the column channels.

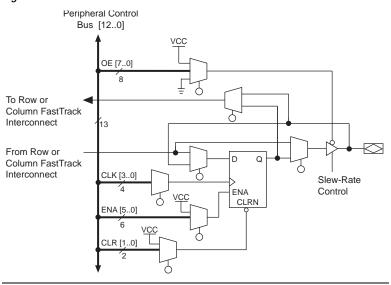

Figure 10. MAX 9000 IOC

I/O pins can be used as input, output, or bidirectional pins. Each IOC has an IOC register with a clock enable input. This register can be used either as an input register for external data that requires fast setup times, or as an output register for data that requires fast clock-to-output performance. The IOC register clock enable allows the global clock to be used for fast clock-to-output performance, while maintaining the flexibility required for selective clocking.

The clock, clock enable, clear, and output enable controls for the IOCs are provided by a network of I/O control signals. These signals can be supplied by either the dedicated input pins or internal logic. The IOC control-signal paths are designed to minimize the skew across the device. All control-signal sources are buffered onto high-speed drivers that drive the signals around the periphery of the device. This "peripheral bus" can be configured to provide up to eight output enable signals, up to four clock signals, up to six clock enable signals, and up to two clear signals. Table 6 on page 18 shows the sources that drive the peripheral bus and how the IOC control signals share the peripheral bus.

The programming times described in Tables 7 through 9 are associated with the worst-case method using the ISP algorithm.

| Table 7. MAX 9000 t <sub>PULSE</sub> & Cycle <sub>TCK</sub> Values |                         |                       |                         |                       |  |  |  |

|--------------------------------------------------------------------|-------------------------|-----------------------|-------------------------|-----------------------|--|--|--|

| Device                                                             | Progra                  | ımming                | Stand-Alone             | e Verification        |  |  |  |

|                                                                    | t <sub>PPULSE</sub> (s) | Cycle <sub>PTCK</sub> | t <sub>VPULSE</sub> (s) | Cycle <sub>VTCK</sub> |  |  |  |

| EPM9320<br>EPM9320A                                                | 11.79                   | 2,966,000             | 0.15                    | 1,806,000             |  |  |  |

| EPM9400                                                            | 12.00                   | 3,365,000             | 0.15                    | 2,090,000             |  |  |  |

| EPM9480                                                            | 12.21                   | 3,764,000             | 0.15                    | 2,374,000             |  |  |  |

| EPM9560<br>EPM9560A                                                | 12.42                   | 4,164,000             | 0.15                    | 2,658,000             |  |  |  |

Tables 8 and 9 show the in-system programming and stand alone verification times for several common test clock frequencies.

| Table 8. MAX 9000 In-System Programming Times for Different Test Clock Frequencies |        |                  |       |       |         |         |         |        |       |

|------------------------------------------------------------------------------------|--------|------------------|-------|-------|---------|---------|---------|--------|-------|

| Device                                                                             |        | f <sub>TCK</sub> |       |       |         |         |         |        | Units |

|                                                                                    | 10 MHz | 5 MHz            | 2 MHz | 1 MHz | 500 kHz | 200 kHz | 100 kHz | 50 kHz |       |

| EPM9320<br>EPM9320A                                                                | 12.09  | 12.38            | 13.27 | 14.76 | 17.72   | 26.62   | 41.45   | 71.11  | S     |

| EPM9400                                                                            | 12.34  | 12.67            | 13.68 | 15.37 | 18.73   | 28.83   | 45.65   | 79.30  | S     |

| EPM9480                                                                            | 12.59  | 12.96            | 14.09 | 15.98 | 19.74   | 31.03   | 49.85   | 87.49  | S     |

| EPM9560<br>EPM9560A                                                                | 12.84  | 13.26            | 14.50 | 16.59 | 20.75   | 33.24   | 54.06   | 95.70  | S     |

| Table 9. MAX 9000 Stand-Alone Verification Times for Different Test Clock Frequencies |        |                  |       |       |         |         |         |        |       |

|---------------------------------------------------------------------------------------|--------|------------------|-------|-------|---------|---------|---------|--------|-------|

| Device                                                                                |        | f <sub>TCK</sub> |       |       |         |         |         |        | Units |

|                                                                                       | 10 MHz | 5 MHz            | 2 MHz | 1 MHz | 500 kHz | 200 kHz | 100 kHz | 50 kHz |       |

| EPM9320<br>EPM9320A                                                                   | 0.33   | 0.52             | 1.06  | 1.96  | 3.77    | 9.18    | 18.21   | 36.27  | S     |

| EPM9400                                                                               | 0.36   | 0.57             | 1.20  | 2.24  | 4.33    | 10.60   | 21.05   | 41.95  | S     |

| EPM9480                                                                               | 0.39   | 0.63             | 1.34  | 2.53  | 4.90    | 12.02   | 23.89   | 47.63  | S     |

| EPM9560<br>EPM9560A                                                                   | 0.42   | 0.69             | 1.48  | 2.81  | 5.47    | 13.44   | 26.73   | 53.31  | S     |

# Programming with External Hardware

MAX 9000 devices can be programmed on Windows-based PCs with an Altera Logic Programmer card, the Master Programming Unit (MPU), and the appropriate device adapter. The MPU performs continuity checking to ensure adequate electrical contact between the adapter and the device.

For more information, see the Altera Programming Hardware Data Sheet.

The MAX+PLUS II software can use text- or waveform-format test vectors created with the MAX+PLUS II Text Editor or Waveform Editor to test a programmed device. For added design verification, designers can perform functional testing to compare the functional behavior of a MAX 9000 device with the results of simulation.

Data I/O, BP Microsystems, and other programming hardware manufacturers also provide programming support for Altera devices.

For more information, see Programming Hardware Manufacturers.

## IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

MAX 9000 devices support JTAG BST circuitry as specified by IEEE Std. 1149.1-1990. Table 10 describes the JTAG instructions supported by the MAX 9000 family. The pin-out tables starting on page 38 show the location of the JTAG control pins for each device. If the JTAG interface is not required, the JTAG pins are available as user I/O pins.

| Table 10. MAX 9000 | Table 10. MAX 9000 JTAG Instructions                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| JTAG Instruction   | Description                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| SAMPLE/PRELOAD     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern output at the device pins.                                                                                                    |  |  |  |  |  |  |

| EXTEST             | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                                                        |  |  |  |  |  |  |

| BYPASS             | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through a selected device to adjacent devices during normal device operation.                                                                                  |  |  |  |  |  |  |

| IDCODE             | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be shifted out of TDO. Supported by the EPM9320A, EPM9400, EPM9480, and EPM9560A devices only.                                                                                          |  |  |  |  |  |  |

| UESCODE            | Selects the user electronic signature (UESCODE) register and allows the UESCODE to be shifted out of TDO serially. This instruction is supported by MAX 9000A devices only.                                                                                                   |  |  |  |  |  |  |

| ISP Instructions   | These instructions are used when programming MAX 9000 devices via the JTAG ports with the BitBlaster or ByteBlasterMV download cable, or using a Jam File (.jam), Jam Byte-Code File (.jbc), or Serial Vector Format (.svf) File via an embedded processor or test equipment. |  |  |  |  |  |  |

| Table 16. MAX 9000 Device DC Operating Conditions    Notes (5), (6) |                                                 |                                                               |                         |                          |      |  |  |  |

|---------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------|-------------------------|--------------------------|------|--|--|--|

| Symbol                                                              | Parameter                                       | Conditions                                                    | Min                     | Max                      | Unit |  |  |  |

| V <sub>IH</sub>                                                     | High-level input voltage                        | (7)                                                           | 2.0                     | V <sub>CCINT</sub> + 0.5 | ٧    |  |  |  |

| V <sub>IL</sub>                                                     | Low-level input voltage                         |                                                               | -0.5                    | 0.8                      | V    |  |  |  |

| -                                                                   | 5.0-V high-level TTL output voltage             | I <sub>OH</sub> = -4 mA DC, V <sub>CCIO</sub> = 4.75 V (8)    | 2.4                     |                          | V    |  |  |  |

|                                                                     | 3.3-V high-level TTL output voltage             | I <sub>OH</sub> = -4 mA DC, V <sub>CCIO</sub> = 3.00 V (8)    | 2.4                     |                          | V    |  |  |  |

|                                                                     | 3.3-V high-level CMOS output voltage            | $I_{OH} = -0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V } (8)$ | V <sub>CCIO</sub> – 0.2 |                          | V    |  |  |  |

| V <sub>OL</sub>                                                     | 5.0-V low level TTL output voltage              | I <sub>OL</sub> = 12 mA DC, V <sub>CCIO</sub> = 4.75 V (8)    |                         | 0.45                     | V    |  |  |  |

|                                                                     | 3.3-V low-level TTL output voltage              | I <sub>OL</sub> = 12 mA DC, V <sub>CCIO</sub> = 3.00 V (8)    |                         | 0.45                     | V    |  |  |  |

|                                                                     | 3.3-V low-level CMOS output voltage             | I <sub>OL</sub> = 0.1 mA DC, V <sub>CCIO</sub> = 3.00 V (8)   |                         | 0.2                      | V    |  |  |  |

| I <sub>I</sub>                                                      | I/O pin leakage current of dedicated input pins | V <sub>I</sub> = -0.5 to 5.5 V (9)                            | -10                     | 10                       | μА   |  |  |  |

| I <sub>OZ</sub>                                                     | Tri-state output off-state current              | $V_1 = -0.5 \text{ to } 5.5 \text{ V}$                        | -40                     | 40                       | μΑ   |  |  |  |

| Table 1           | Table 17. MAX 9000 Device Capacitance: EPM9320, EPM9400, EPM9480 & EPM9560 Devices         Note (10) |                                    |     |     |      |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------|------------------------------------|-----|-----|------|--|--|--|

| Symbol            | Parameter                                                                                            | Conditions                         | Min | Max | Unit |  |  |  |

| C <sub>DIN1</sub> | Dedicated input capacitance                                                                          | V <sub>IN</sub> = 0 V, f = 1.0 MHz |     | 18  | pF   |  |  |  |

| C <sub>DIN2</sub> | Dedicated input capacitance                                                                          | V <sub>IN</sub> = 0 V, f = 1.0 MHz |     | 18  | pF   |  |  |  |

| C <sub>DIN3</sub> | Dedicated input capacitance                                                                          | V <sub>IN</sub> = 0 V, f = 1.0 MHz |     | 17  | pF   |  |  |  |

| C <sub>DIN4</sub> | Dedicated input capacitance                                                                          | V <sub>IN</sub> = 0 V, f = 1.0 MHz |     | 20  | pF   |  |  |  |

| C <sub>I/O</sub>  | I/O pin capacitance                                                                                  | V <sub>IN</sub> = 0 V, f = 1.0 MHz |     | 12  | pF   |  |  |  |

| Table 1           | 8. MAX 9000A Device Capacitan | Note (10)                          |     |     |      |

|-------------------|-------------------------------|------------------------------------|-----|-----|------|

| Symbol            | Parameter                     | Conditions                         | Min | Max | Unit |

| C <sub>DIN1</sub> | Dedicated input capacitance   | V <sub>IN</sub> = 0 V, f = 1.0 MHz |     | 16  | pF   |

| C <sub>DIN2</sub> | Dedicated input capacitance   | V <sub>IN</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |

| C <sub>DIN3</sub> | Dedicated input capacitance   | V <sub>IN</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |

| C <sub>DIN4</sub> | Dedicated input capacitance   | V <sub>IN</sub> = 0 V, f = 1.0 MHz |     | 12  | pF   |

| C <sub>I/O</sub>  | I/O pin capacitance           | V <sub>IN</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |

| Table 19. MAX 9000 Device Typical I <sub>CC</sub> Supply Current Values |                                                            |                                          |         |         |         |         |      |  |

|-------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------|---------|---------|---------|---------|------|--|

| Symbol                                                                  | Parameter                                                  | Conditions                               | EPM9320 | EPM9400 | EPM9480 | EPM9560 | Unit |  |

| I <sub>CC1</sub>                                                        | $I_{CC}$ supply current (low-power mode, standby, typical) | V <sub>I</sub> = ground,<br>no load (11) | 106     | 132     | 140     | 146     | mA   |  |

| Table 23            | 3. IOC Delays                                                                              |            |             |     |     |      |     |      |    |

|---------------------|--------------------------------------------------------------------------------------------|------------|-------------|-----|-----|------|-----|------|----|

| Symbol              | Parameter                                                                                  | Conditions | Speed Grade |     |     |      |     | Unit |    |

|                     |                                                                                            |            | -10         |     | -15 |      | -20 |      |    |

|                     |                                                                                            | Min        | Max         | Min | Max | Min  | Max |      |    |

| t <sub>IODR</sub>   | I/O row output data delay                                                                  |            |             | 0.2 |     | 0.2  |     | 1.5  | ns |

| t <sub>IODC</sub>   | I/O column output data delay                                                               |            |             | 0.4 |     | 0.2  |     | 1.5  | ns |

| t <sub>IOC</sub>    | I/O control delay                                                                          | (6)        |             | 0.5 |     | 1.0  |     | 2.0  | ns |

| t <sub>IORD</sub>   | I/O register clock-to-output delay                                                         |            |             | 0.6 |     | 1.0  |     | 1.5  | ns |

| t <sub>IOCOMB</sub> | I/O combinatorial delay                                                                    |            |             | 0.2 |     | 1.0  |     | 1.5  | ns |

| t <sub>IOSU</sub>   | I/O register setup time before clock                                                       |            | 2.0         |     | 4.0 |      | 5.0 |      | ns |

| t <sub>IOH</sub>    | I/O register hold time after clock                                                         |            | 1.0         |     | 1.0 |      | 1.0 |      | ns |

| t <sub>IOCLR</sub>  | I/O register clear delay                                                                   |            |             | 1.5 |     | 3.0  |     | 3.0  | ns |

| t <sub>IOFD</sub>   | I/O register feedback delay                                                                |            |             | 0.0 |     | 0.0  |     | 0.5  | ns |

| t <sub>INREG</sub>  | I/O input pad and buffer to I/O register delay                                             |            |             | 3.5 |     | 4.5  |     | 5.5  | ns |

| t <sub>INCOMB</sub> | I/O input pad and buffer to row and column delay                                           |            |             | 1.5 |     | 2.0  |     | 2.5  | ns |

| t <sub>OD1</sub>    | Output buffer and pad delay,<br>Slow slew rate = off,<br>V <sub>CCIO</sub> = 5.0 V         | C1 = 35 pF |             | 1.8 |     | 2.5  |     | 2.5  | ns |

| t <sub>OD2</sub>    | Output buffer and pad delay,<br>Slow slew rate = off,<br>V <sub>CCIO</sub> = 3.3 V         | C1 = 35 pF |             | 2.3 |     | 3.5  |     | 3.5  | ns |

| t <sub>OD3</sub>    | Output buffer and pad delay,<br>Slow slew rate = on,<br>V <sub>CCIO</sub> = 5.0 V or 3.3 V | C1 = 35 pF |             | 8.3 |     | 10.0 |     | 10.5 | ns |

| t <sub>XZ</sub>     | Output buffer disable delay                                                                | C1 = 5 pF  |             | 2.5 |     | 2.5  |     | 2.5  | ns |

| t <sub>ZX1</sub>    | Output buffer enable delay,<br>Slow slew rate = off,<br>V <sub>CCIO</sub> = 5.0 V          | C1 = 35 pF |             | 2.5 |     | 2.5  |     | 2.5  | ns |

| t <sub>ZX2</sub>    | Output buffer enable delay,<br>Slow slew rate = off,<br>V <sub>CCIO</sub> = 3.3 V          | C1 = 35 pF |             | 3.0 |     | 3.5  |     | 3.5  | ns |

| $t_{ZX3}$           | Output buffer enable delay,<br>Slow slew rate = on,<br>V <sub>CCIO</sub> = 3.3 V or 5.0 V  | C1 = 35 pF |             | 9.0 |     | 10.0 |     | 10.5 | ns |

| Table 24. Interconnect Delays |                                            |            |             |     |     |     |     |     |      |

|-------------------------------|--------------------------------------------|------------|-------------|-----|-----|-----|-----|-----|------|

| Symbol                        | Parameter                                  | Conditions | Speed Grade |     |     |     |     |     | Unit |

|                               |                                            |            | -10         |     | -15 |     | -20 |     |      |

|                               |                                            |            | Min         | Max | Min | Max | Min | Max | 1    |

| t <sub>LOCAL</sub>            | LAB local array delay                      |            |             | 0.5 |     | 0.5 |     | 0.5 | ns   |

| t <sub>ROW</sub>              | FastTrack row delay                        | (6)        |             | 0.9 |     | 1.4 |     | 2.0 | ns   |

| t <sub>COL</sub>              | FastTrack column delay                     | (6)        |             | 0.9 |     | 1.7 |     | 3.0 | ns   |

| t <sub>DIN_D</sub>            | Dedicated input data delay                 |            |             | 4.0 |     | 4.5 |     | 5.0 | ns   |

| t <sub>DIN_CLK</sub>          | Dedicated input clock delay                |            |             | 2.7 |     | 3.5 |     | 4.0 | ns   |

| t <sub>DIN_CLR</sub>          | Dedicated input clear delay                |            |             | 4.5 |     | 5.0 |     | 5.5 | ns   |

| t <sub>DIN_IOC</sub>          | Dedicated input I/O register clock delay   |            |             | 2.5 |     | 3.5 |     | 4.5 | ns   |

| t <sub>DIN_IO</sub>           | Dedicated input I/O register control delay |            |             | 5.5 |     | 6.0 |     | 6.5 | ns   |

### Notes to tables:

- These values are specified under the MAX 9000 device recommended operating conditions, shown in Table 15 on page 27.

- See Application Note 77 (Understanding MAX 9000 Timing) for more information on test conditions for t<sub>PD1</sub> and t<sub>PD2</sub> delays.

- (3) This parameter is a guideline that is sample-tested only. It is based on extensive device characterization. This parameter applies for both global and array clocking as well as both macrocell and I/O cell registers.

- (4) Measured with a 16-bit loadable, enabled, up/down counter programmed in each LAB.

- (5) The  $t_{LPA}$  parameter must be added to the  $t_{LOCAL}$  parameter for macrocells running in low-power mode.

- (6) The t<sub>ROW</sub>, t<sub>COL</sub>, and t<sub>IOC</sub> delays are worst-case values for typical applications. Post-compilation timing simulation or timing analysis is required to determine actual worst-case performance.

## Power Consumption

The supply power (P) versus frequency ( $f_{MAX}$ ) for MAX 9000 devices can be calculated with the following equation:

$$P = P_{INT} + P_{IO} = I_{CCINT} \times V_{CC} + P_{IO}$$

The  $P_{\rm IO}$  value, which depends on the device output load characteristics and switching frequency, can be calculated using the guidelines given in *Application Note 74 (Evaluating Power for Altera Devices)*. The  $I_{\rm CCINT}$  value depends on the switching frequency and the application logic.

The I<sub>CCINT</sub> value is calculated with the following equation:

$$I_{CCINT} = (A \times MC_{TON}) + [B \times (MC_{DEV} - MC_{TON})] + (C \times MC_{USED} \times f_{MAX} \times tog_{LC})$$

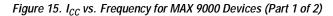

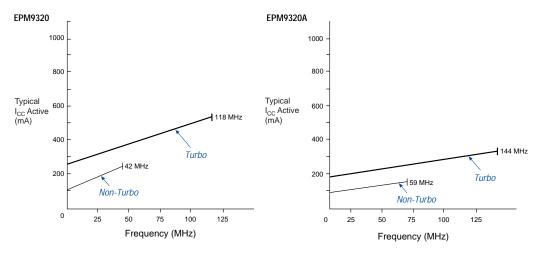

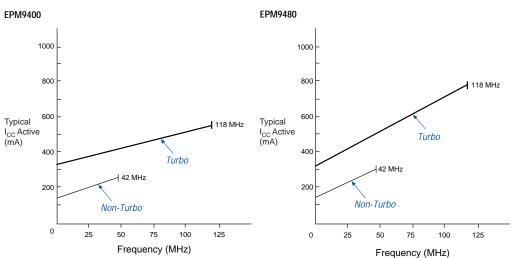

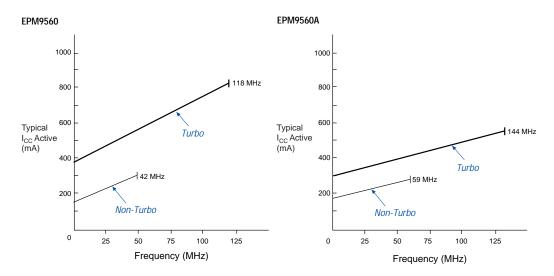

Figure 15. I<sub>CC</sub> vs. Frequency for MAX 9000 Devices (Part 2 of 2)

### Device Pin-Outs

Tables 26 through 29 show the dedicated pin names and numbers for each EPM9320, EPM9320A, EPM9400, EPM9480, EPM9560, and EPM9560A device package.

| Table 26. EP    | Table 26. EPM9320 & EPM9320A Dedicated Pin-Outs (Part 1 of 2) Note (1) |              |                 |             |  |  |  |  |

|-----------------|------------------------------------------------------------------------|--------------|-----------------|-------------|--|--|--|--|

| Pin Name        | 84-Pin PLCC (2)                                                        | 208-Pin RQFP | 280-Pin PGA (3) | 356-Pin BGA |  |  |  |  |

| DIN1<br>(GCLK1) | 1                                                                      | 182          | V10             | AD13        |  |  |  |  |

| DIN2<br>(GCLK2) | 84                                                                     | 183          | U10             | AF14        |  |  |  |  |

| DIN3 (GCLR)     | 13                                                                     | 153          | V17             | AD1         |  |  |  |  |

| DIN4 (GOE)      | 72                                                                     | 4            | W2              | AC24        |  |  |  |  |

| TCK             | 43                                                                     | 78           | A9              | A18         |  |  |  |  |

| TMS             | 55                                                                     | 49           | D6              | E23         |  |  |  |  |

| TDI             | 42                                                                     | 79           | C11             | A13         |  |  |  |  |

| TDO             | 30                                                                     | 108          | A18             | D3          |  |  |  |  |

### Notes:

- (1) All pins not listed are user I/O pins.

- (2) Perform a complete thermal analysis before committing a design to this device package. See Application Note 74 (Evaluating Power for Altera Devices).

- (3) EPM9320A devices are not offered in this package.

- (4) During in-system programming, each device's VPP pin must be connected to the 5.0-V power supply. During normal device operation, the VPP pin is pulled up internally and can be connected to the 5.0-V supply or left unconnected.

- (5) The user I/O pin count includes dedicated input pins and all I/O pins.

| Table 27. EPM9400 Ded   | licated Pin-Outs Note (1)             |                                                                                                                                    |                                                                                                                                              |

|-------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                | 84-Pin PLCC (2)                       | 208-Pin RQFP                                                                                                                       | 240-Pin RQFP                                                                                                                                 |

| DIN1 (GCLK1)            | 2                                     | 182                                                                                                                                | 210                                                                                                                                          |

| DIN2 (GCLK2)            | 1                                     | 183                                                                                                                                | 211                                                                                                                                          |

| DIN3 (GCLR)             | 12                                    | 153                                                                                                                                | 187                                                                                                                                          |

| DIN4 (GOE)              | 74                                    | 4                                                                                                                                  | 234                                                                                                                                          |

| TCK                     | 43                                    | 78                                                                                                                                 | 91                                                                                                                                           |

| TMS                     | 54                                    | 49                                                                                                                                 | 68                                                                                                                                           |

| TDI                     | 42                                    | 79                                                                                                                                 | 92                                                                                                                                           |

| TDO                     | 31                                    | 108                                                                                                                                | 114                                                                                                                                          |

| GND                     | 6, 13, 20, 26, 27, 47, 60, 66, 69, 73 | 14, 20, 24, 31, 35, 41, 42, 43, 44, 46, 47, 66, 85, 102, 110, 113, 114, 115, 116, 118, 121, 122, 132, 133, 143, 152, 170, 189, 206 | 5, 14, 25, 34, 45, 54, 65,<br>66, 81, 96, 110, 115, 126,<br>127, 146, 147, 166, 167,<br>186, 200, 216, 229                                   |

| VCCINT (5.0 V only)     | 16, 23, 30, 56, 63, 70                | 10, 19, 30, 45, 112, 128, 139, 148                                                                                                 | 4, 24, 44, 64, 117, 137,<br>157, 177                                                                                                         |

| VCCIO (3.3 or 5.0 V)    | 17, 37, 59, 80                        | 5, 25, 36, 55, 72, 91, 111, 127, 138, 159, 176, 195                                                                                | 15, 35, 55, 73, 86, 101,<br>116, 136, 156, 176, 192,<br>205, 220, 235                                                                        |

| No Connect (N.C.)       | _                                     | 6, 7, 8, 9, 11, 12, 13, 109, 144, 145, 146, 147, 149, 150, 151                                                                     | 1, 2, 3, 6, 7, 8, 9, 10, 11, 12, 13, 168, 169, 170, 171, 172, 173, 174, 175, 178, 179, 180, 181, 182, 183, 184, 185, 236, 237, 238, 239, 240 |

| VPP (3)                 | 55                                    | 48                                                                                                                                 | 67                                                                                                                                           |

| Total User I/O Pins (4) | 59                                    | 139                                                                                                                                | 159                                                                                                                                          |

### Notes:

- (1) All pins not listed are user I/O pins.

- (2) Perform a complete thermal analysis before committing a design to this device package. See *Application Note 74* (Evaluating Power for Altera Devices) for more information.

- (3) During in-system programming, each device's VPP pin must be connected to the 5.0-V power supply. During normal device operation, the VPP pin is pulled up internally and can be connected to the 5.0-V supply or left unconnected.

- (4) The user I/O pin count includes dedicated input pins and all I/O pins.

| Pin Name                | 208-Pin RQFP                                                                                                                                            | 240-Pin RQFP                                                                                                     | 280-Pin PGA (2)                                                                                                                                                                    | 304-Pin RQFP (2)                                                                                     | 356-Pin BGA                                                                                                                                                                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIN1<br>(GCLK1)         | 182                                                                                                                                                     | 210                                                                                                              | V10                                                                                                                                                                                | 266                                                                                                  | AD13                                                                                                                                                                                                                               |

| DIN2<br>(GCLK2)         | 183                                                                                                                                                     | 211                                                                                                              | U10                                                                                                                                                                                | 267                                                                                                  | AF14                                                                                                                                                                                                                               |

| DIN3 (GCLR)             | 153                                                                                                                                                     | 187                                                                                                              | V17                                                                                                                                                                                | 237                                                                                                  | AD1                                                                                                                                                                                                                                |

| DIN4 (GOE)              | 4                                                                                                                                                       | 234                                                                                                              | W2                                                                                                                                                                                 | 296                                                                                                  | AC24                                                                                                                                                                                                                               |

| TCK                     | 78                                                                                                                                                      | 91                                                                                                               | A9                                                                                                                                                                                 | 114                                                                                                  | A18                                                                                                                                                                                                                                |

| TMS                     | 49                                                                                                                                                      | 68                                                                                                               | D6                                                                                                                                                                                 | 85                                                                                                   | E23                                                                                                                                                                                                                                |

| TDI                     | 79                                                                                                                                                      | 92                                                                                                               | C11                                                                                                                                                                                | 115                                                                                                  | A13                                                                                                                                                                                                                                |

| TDO                     | 108                                                                                                                                                     | 114                                                                                                              | A18                                                                                                                                                                                | 144                                                                                                  | D3                                                                                                                                                                                                                                 |

| GND                     | 14, 20, 24, 31, 35,<br>41, 42, 43, 44, 46,<br>47, 66, 85, 102,<br>110, 113, 114,<br>115, 116, 118,<br>121, 122, 132,<br>133, 143, 152,<br>170, 189, 206 | 5, 14, 25, 34, 45,<br>54, 65, 66, 81, 96,<br>110, 115, 126,<br>127, 146, 147,<br>166, 167, 186,<br>200, 216, 229 | D4, D5, D16, E4,<br>E5, E6, E15, E16,<br>F5, F15, G5, G15,<br>H5, H15, J5, J15,<br>K5, K15, L5, L15,<br>M5, M15, N5,<br>N15, P4, P5, P15,<br>P16, R4, R5, R15,<br>R16, T4, T5, T16 | 13, 22, 33, 42, 53, 62, 73, 74, 102, 121, 138, 155, 166, 167, 186, 187, 206, 207, 226, 254, 273, 290 | A9, A22, A25,<br>A26, B25, B26,<br>D2, E1, E26, F2,<br>G1, G25, G26,<br>H2, J1, J25, J26,<br>K2, L26, M26, N1<br>N25, P26, R2, T1<br>U2, U26, V1, V25<br>W25, Y26, AA2,<br>AB1, AB26,<br>AC26, AE1, AF1,<br>AF2, AF4, AF7,<br>AF20 |

| VCCINT<br>(5.0 V only)  | 10, 19, 30, 45,<br>112, 128, 139,<br>148                                                                                                                | 4, 24, 44, 64, 117,<br>137, 157, 177                                                                             | D15, E8, E10,<br>E12, E14, R7, R9,<br>R11, R13, R14,<br>T14                                                                                                                        | 12, 32, 52, 72,<br>157, 177, 197,<br>217                                                             | D26, F1, H1, K26<br>N26, P1, U1,<br>W26, AE26,<br>AF25, AF26                                                                                                                                                                       |

| VCCIO<br>(3.3 or 5.0 V) | 5, 25, 36, 55, 72,<br>91, 111, 127, 138,<br>159, 176, 195                                                                                               | 15, 35, 55, 73, 86, 101, 116, 136, 156, 176, 192, 205, 220, 235                                                  | D14, E7, E9, E11,<br>E13, R6, R8, R10,<br>R12, T13, T15                                                                                                                            | 3, 23, 43, 63, 91,<br>108, 127, 156,<br>176, 196, 216,<br>243, 260, 279                              | A1, A2, A21, B1,<br>B10, B24, D1,<br>H26, K1, M25,<br>R1, V26, AA1,<br>AC25, AF5, AF8,<br>AF19                                                                                                                                     |