Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                             |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, CapSense, LCD, POR, PWM, WDT                         |

| Number of I/O              | 27                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 8K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x10b Slope, 16x12b SAR; D/A 2xIDAC                                     |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 32-UFQFN Exposed Pad                                                         |

| Supplier Device Package    | 32-QFN (5x5)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c4146lqi-s432t |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| Functional Definition                  | 4  |

|----------------------------------------|----|

| CPU and Memory Subsystem               | 4  |

| System Resources                       |    |

| Analog Blocks                          | 5  |

| Fixed Function Digital                 | 5  |

| GPIO                                   |    |

| Special Function Peripherals           | 6  |

| Pinouts                                | 7  |

| Alternate Pin Functions                | 9  |

| Power                                  | 11 |

| Mode 1: 1.8 V to 5.5 V External Supply | 11 |

| Mode 2: 1.8 V ±5% External Supply      | 11 |

| Development Support                    | 12 |

| Documentation                          | 12 |

| Online                                 | 12 |

| Tools                                  | 12 |

| Electrical Specifications              | 13 |

| Absolute Maximum Ratings               | 13 |

| Device Level Specifications            | 13 |

| Analog Peripherals                     |    |

|                                        |    |

| Digital Peripherals                     | 25 |

|-----------------------------------------|----|

| Memory                                  |    |

| System Resources                        | 28 |

| Ordering Information                    | 31 |

| Packaging                               | 34 |

| Package Diagrams                        |    |

| Acronyms                                | 38 |

| Document Conventions                    | 40 |

| Units of Measure                        |    |

| Revision History                        | 41 |

| Sales, Solutions, and Legal Information | 42 |

| Worldwide Sales and Design Support      | 42 |

| Products                                |    |

| PSoC® Solutions                         | 42 |

| Cypress Developer Community             |    |

| Technical Support                       |    |

|                                         |    |

### Reset

The PSoC 4100S can be reset from a variety of sources including a software reset. Reset events are asynchronous and guarantee reversion to a known state. The reset cause is recorded in a register, which is sticky through reset and allows software to determine the cause of the reset. An XRES pin is reserved for external reset by asserting it active low. The XRES pin has an internal pull-up resistor that is always enabled.

### Analog Blocks

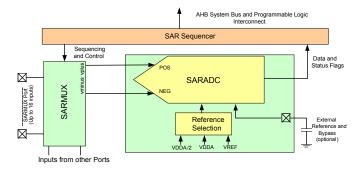

### 12-bit SAR ADC

The 12-bit, 1-Msps SAR ADC can operate at a maximum clock rate of 18 MHz and requires a minimum of 18 clocks at that frequency to do a 12-bit conversion.

The Sample-and-Hold (S/H) aperture is programmable allowing the gain bandwidth requirements of the amplifier driving the SAR inputs, which determine its settling time, to be relaxed if required. It is possible to provide an external bypass (through a fixed pin location) for the internal reference amplifier.

The SAR is connected to a fixed set of pins through an 8-input sequencer. The sequencer cycles through selected channels autonomously (sequencer scan) with zero switching overhead (that is, aggregate sampling bandwidth is equal to 1 Msps whether it is for a single channel or distributed over several channels). The sequencer switching is effected through a state machine or through firmware driven switching. A feature provided by the sequencer is buffering of each channel to reduce CPU interrupt service requirements. To accommodate signals with varying source impedance and frequency, it is possible to have different sample times programmable for each channel. Also, signal range specification through a pair of range registers (low and high range values) is implemented with a corresponding out-of-range interrupt if the digitized value exceeds the programmed range; this allows fast detection of out-of-range values without the necessity of having to wait for a sequencer scan to be completed and the CPU to read the values and check for out-of-range values in software.

The SAR is not available in Deep Sleep mode as it requires a high-speed clock (up to 18 MHz). The SAR operating range is 1.71 V to 5.5 V.

### Figure 3. SAR ADC

### Two Opamps (Continuous-Time Block; CTB)

The PSoC 4100S has two opamps with Comparator modes which allow most common analog functions to be performed on-chip eliminating external components; PGAs, Voltage Buffers, Filters, Trans-Impedance Amplifiers, and other functions can be realized, in some cases with external passives. saving power, cost, and space. The on-chip opamps are designed with enough bandwidth to drive the Sample-and-Hold circuit of the ADC without requiring external buffering.

#### Low-power Comparators (LPC)

The PSoC 4100S has a pair of low-power comparators, which can also operate in Deep Sleep modes. This allows the analog system blocks to be disabled while retaining the ability to monitor external voltage levels during low-power modes. The comparator outputs are normally synchronized to avoid metastability unless operating in an asynchronous power mode where the system wake-up circuit is activated by a comparator switch event. The LPC outputs can be routed to pins.

### Current DACs

The PSoC 4100S has two IDACs, which can drive any of the pins on the chip. These IDACs have programmable current ranges.

#### Analog Multiplexed Buses

The PSoC 4100S has two concentric independent buses that go around the periphery of the chip. These buses (called amux buses) are connected to firmware-programmable analog switches that allow the chip's internal resources (IDACs, comparator) to connect to any pin on the I/O Ports.

### **Programmable Digital Blocks**

The Programmable I/O (Smart I/O) block is a fabric of switches and LUTs that allows Boolean functions to be performed in signals being routed to the pins of a GPIO port. The Smart I/O can perform logical operations on input pins to the chip and on signals going out as outputs.

### **Fixed Function Digital**

### Timer/Counter/PWM (TCPWM) Block

The TCPWM block consists of a 16-bit counter with user-programmable period length. There is a capture register to record the count value at the time of an event (which may be an I/O event), a period register that is used to either stop or auto-reload the counter when its count is equal to the period register, and compare registers to generate compare value signals that are used as PWM duty cycle outputs. The block also provides true and complementary outputs with programmable offset between them to allow use as dead-band programmable complementary PWM outputs. It also has a Kill input to force outputs to a predetermined state; for example, this is used in motor drive systems when an over-current state is indicated and the PWM driving the FETs needs to be shut off immediately with no time for software intervention. There are five TCPWM blocks in the PSoC 4100S.

#### Serial Communication Block (SCB)

The PSoC 4100S has three serial communication blocks, which can be programmed to have SPI, I2C, or UART functionality.

**I<sup>2</sup>C Mode**: The hardware I<sup>2</sup>C block implements a full multi-master and slave interface (it is capable of multi-master arbitration). This block is capable of operating at speeds of up to 400 kbps (Fast Mode) and has flexible buffering options to reduce interrupt overhead and latency for the CPU. It also

## Table 1. Pin List (continued)

| 48-1 | QFP  | 44-T | QFP  | 40- | QFN  | 32-QFN |      | 35- | CSP  |

|------|------|------|------|-----|------|--------|------|-----|------|

| Pin  | Name | Pin  | Name | Pin | Name | Pin    | Name | Pin | Name |

| 19   | P3.6 | 17   | P3.6 | 16  | P3.6 |        |      |     |      |

| 20   | P3.7 | 18   | P3.7 | 17  | P3.7 |        |      |     |      |

| 21   | VDDD | 19   | VDDD |     |      |        |      |     |      |

| 22   | P4.0 | 20   | P4.0 | 18  | P4.0 | 13     | P4.0 | B1  | P4.0 |

| 23   | P4.1 | 21   | P4.1 | 19  | P4.1 | 14     | P4.1 | B2  | P4.1 |

| 24   | P4.2 | 22   | P4.2 | 20  | P4.2 | 15     | P4.2 | A2  | P4.2 |

| 25   | P4.3 | 23   | P4.3 | 21  | P4.3 | 16     | P4.3 | A1  | P4.3 |

Notes: Pins 11, 15, 26, and 27 are No Connects (NC) on the 48-pin TQFP.

Descriptions of the Power pins are as follows:

VDDD: Power supply for the digital section.

VDDA: Power supply for the analog section.

VSSD, VSSA: Ground pins for the digital and analog sections respectively.

VCCD: Regulated digital supply (1.8 V ±5%)

VDD: Power supply to all sections of the chip

VSS: Ground for all sections of the chip

# **Alternate Pin Functions**

Each Port pin has can be assigned to one of multiple functions; it can, for instance, be an analog I/O, a digital peripheral function, an LCD pin, or a CapSense pin. The pin assignments are shown in the following table.

| Port/Pin | Analog                                      | Smart I/O      | Alternate Function 1  | Alternate Function 2 | Alternate Function 3 | Deep Sleep 1     | Deep Sleep 2         |

|----------|---------------------------------------------|----------------|-----------------------|----------------------|----------------------|------------------|----------------------|

| P0.0     | lpcomp.in_p[0]                              |                |                       |                      | tcpwm.tr_in[0]       | scb[2].i2c_scl:0 | scb[0].spi_select1:0 |

| P0.1     | lpcomp.in_n[0]                              |                |                       |                      | tcpwm.tr_in[1]       | scb[2].i2c_sda:0 | scb[0].spi_select2:0 |

| P0.2     | lpcomp.in_p[1]                              |                |                       |                      |                      |                  | scb[0].spi_select3:0 |

| P0.3     | lpcomp.in_n[1]                              |                |                       |                      |                      |                  | scb[2].spi_select0   |

| P0.4     | wco.wco_in                                  |                |                       | scb[1].uart_rx:0     | scb[2].uart_rx:0     | scb[1].i2c_scl:0 | scb[1].spi_mosi:1    |

| P0.5     | wco.wco_out                                 |                |                       | scb[1].uart_tx:0     | scb[2].uart_tx:0     | scb[1].i2c_sda:0 | scb[1].spi_miso:1    |

| P0.6     |                                             |                | srss.ext_clk          | scb[1].uart_cts:0    | scb[2].uart_tx:1     |                  | scb[1].spi_clk:1     |

| P0.7     |                                             |                | tcpwm.line[0]:2       | scb[1].uart_rts:0    |                      |                  | scb[1].spi_select0:1 |

| P1.0     | ctb0_oa0+                                   |                | tcpwm.line[2]:1       | scb[0].uart_rx:1     |                      | scb[0].i2c_scl:0 | scb[0].spi_mosi:1    |

| P1.1     | ctb0_oa0-                                   |                | tcpwm.line_compl[2]:1 | scb[0].uart_tx:1     |                      | scb[0].i2c_sda:0 | scb[0].spi_miso:1    |

| P1.2     | ctb0_oa0_out                                |                | tcpwm.line[3]:1       | scb[0].uart_cts:1    | tcpwm.tr_in[2]       | scb[2].i2c_scl:1 | scb[0].spi_clk:1     |

| P1.3     | ctb0_oa1_out                                |                | tcpwm.line_compl[3]:1 | scb[0].uart_rts:1    | tcpwm.tr_in[3]       | scb[2].i2c_sda:1 | scb[0].spi_select0:1 |

| P1.4     | ctb0_oa1-                                   |                |                       |                      |                      |                  | scb[0].spi_select1:1 |

| P1.5     | ctb0_oa1+                                   |                |                       |                      |                      |                  | scb[0].spi_select2:1 |

| P1.6     | ctb0_oa0+                                   |                |                       |                      |                      |                  | scb[0].spi_select3:1 |

| P1.7     | ctb0_oa1+<br>sar_ext_vref0<br>sar_ext_vref1 |                |                       |                      |                      |                  | scb[2].spi_clk       |

| P2.0     | sarmux[0]                                   | prgio[0].io[0] | tcpwm.line[4]:0       | csd.comp             | tcpwm.tr_in[4]       | scb[1].i2c_scl:1 | scb[1].spi_mosi:2    |

| P2.1     | sarmux[1]                                   | prgio[0].io[1] | tcpwm.line_compl[4]:0 |                      | tcpwm.tr_in[5]       | scb[1].i2c_sda:1 | scb[1].spi_miso:2    |

| P2.2     | sarmux[2]                                   | prgio[0].io[2] |                       |                      |                      |                  | scb[1].spi_clk:2     |

| P2.3     | sarmux[3]                                   | prgio[0].io[3] |                       |                      |                      |                  | scb[1].spi_select0:2 |

# **Development Support**

The PSoC 4100S family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit www.cypress.com/go/psoc4 to find out more.

### Documentation

A suite of documentation supports the PSoC 4100S family to ensure that you can find answers to your questions quickly. This section contains a list of some of the key documents.

**Software User Guide**: A step-by-step guide for using PSoC Creator. The software user guide shows you how the PSoC Creator build process works in detail, how to use source control with PSoC Creator, and much more.

**Component Datasheets**: The flexibility of PSoC allows the creation of new peripherals (components) long after the device has gone into production. Component data sheets provide all of the information needed to select and use a particular component, including a functional description, API documentation, example code, and AC/DC specifications.

Application Notes: PSoC application notes discuss a particular application of PSoC in depth; examples include brushless DC motor control and on-chip filtering. Application notes often include example projects in addition to the application note document.

**Technical Reference Manual**: The Technical Reference Manual (TRM) contains all the technical detail you need to use a PSoC device, including a complete description of all PSoC registers. The TRM is available in the Documentation section at www.cypress.com/psoc4.

### Online

In addition to print documentation, the Cypress PSoC forums connect you with fellow PSoC users and experts in PSoC from around the world, 24 hours a day, 7 days a week.

### Tools

With industry standard cores, programming, and debugging interfaces, the PSoC 4100S family is part of a development tool ecosystem. Visit us at www.cypress.com/go/psoccreator for the latest information on the revolutionary, easy to use PSoC Creator IDE, supported third party compilers, programmers, debuggers, and development kits.

## Table 3. DC Specifications (continued)

Typical values measured at V\_DD = 3.3 V and 25  $^\circ\text{C}.$

| Spec ID#                                         | Parameter                               | Description                                       | Min | Тур | Max | Units | Details/<br>Conditions             |  |  |

|--------------------------------------------------|-----------------------------------------|---------------------------------------------------|-----|-----|-----|-------|------------------------------------|--|--|

| Sleep Mode, VDDD = 1.8 V to 5.5 V (Regulator on) |                                         |                                                   |     |     |     |       |                                    |  |  |

| SID22                                            | IDD17                                   | I <sup>2</sup> C wakeup WDT, and Comparators on   | _   | 1.7 | 2.2 | mA    | 6 MHZ. Max is at 85 °C and 5.5 V.  |  |  |

| SID25                                            | IDD20                                   | I <sup>2</sup> C wakeup, WDT, and Comparators on. | _   | 2.2 | 2.5 |       | 12 MHZ. Max is at 85 °C and 5.5 V. |  |  |

| Sleep Mode, V                                    | <sub>DDD</sub> = 1.71 V to              | 1.89 V (Regulator bypassed)                       |     |     |     |       |                                    |  |  |

| SID28                                            | IDD23                                   | I <sup>2</sup> C wakeup, WDT, and Comparators on  | _   | 0.7 | 0.9 | mA    | 6 MHZ. Max is at 85 °C and 5.5 V.  |  |  |

| SID28A                                           | IDD23A                                  | I <sup>2</sup> C wakeup, WDT, and Comparators on  | _   | 1   | 1.2 | mA    | 12 MHZ. Max is at 85 °C and 5.5 V. |  |  |

| Deep Sleep Mo                                    | ode, V <sub>DD</sub> = 1.8 \            | / to 3.6 V (Regulator on)                         |     |     |     |       |                                    |  |  |

| SID31                                            | I <sub>DD26</sub>                       | I <sup>2</sup> C wakeup and WDT on                | _   | 2.5 | 60  | μA    | Max is at 3.6 V<br>and 85 °C.      |  |  |

| Deep Sleep Mo                                    | ode, V <sub>DD</sub> = 3.6 \            | / to 5.5 V (Regulator on)                         |     |     |     |       |                                    |  |  |

| SID34                                            | I <sub>DD29</sub>                       | I <sup>2</sup> C wakeup and WDT on                | _   | 2.5 | 60  | μA    | Max is at 5.5 V<br>and 85 °C.      |  |  |

| Deep Sleep Mo                                    | ode, V <sub>DD</sub> = V <sub>CCI</sub> | $_{\rm D}$ = 1.71 V to 1.89 V (Regulator bypasse  | ed) |     |     |       |                                    |  |  |

| SID37                                            | I <sub>DD32</sub>                       | I <sup>2</sup> C wakeup and WDT on                | _   | 2.5 | 65  | μA    | Max is at 1.89 V<br>and 85 °C.     |  |  |

| XRES Current                                     | XRES Current                            |                                                   |     |     |     |       |                                    |  |  |

| SID307                                           | I <sub>DD_XR</sub>                      | Supply current while XRES asserted                | _   | 2   | 5   | mA    | _                                  |  |  |

## Table 4. AC Specifications

| Spec ID#             | Parameter              | Description                 | Min | Тур | Max | Units | Details/<br>Conditions      |

|----------------------|------------------------|-----------------------------|-----|-----|-----|-------|-----------------------------|

| SID48                | F <sub>CPU</sub>       | CPU frequency               | DC  | -   | 48  | MHz   | $1.71 \leq V_{DD} \leq 5.5$ |

| SID49 <sup>[3]</sup> | T <sub>SLEEP</sub>     | Wakeup from Sleep mode      | -   | 0   | _   | μs    |                             |

| SID50 <sup>[3]</sup> | T <sub>DEEPSLEEP</sub> | Wakeup from Deep Sleep mode | -   | 35  | -   | μο    |                             |

### Table 6. GPIO AC Specifications

(Guaranteed by Characterization) (continued)

| Spec ID# | Parameter            | Description                                                                         | Min | Тур | Max  | Units | Details/<br>Conditions                    |

|----------|----------------------|-------------------------------------------------------------------------------------|-----|-----|------|-------|-------------------------------------------|

| SID73    | T <sub>FALLS</sub>   | Fall time in slow strong mode                                                       | 10  | _   | 60   | _     | 3.3 V V <sub>DDD</sub> , Cload =<br>25 pF |

| SID74    | F <sub>GPIOUT1</sub> | GPIO F <sub>OUT</sub> ; 3.3 V $\leq$ V <sub>DDD</sub> $\leq$ 5.5 V Fast strong mode | _   | -   | 33   |       | 90/10%, 25 pF load,<br>60/40 duty cycle   |

| SID75    | F <sub>GPIOUT2</sub> | GPIO F <sub>OUT</sub> ; 1.71 V≤ V <sub>DDD</sub> ≤ 3.3 V<br>Fast strong mode        | _   | -   | 16.7 |       | 90/10%, 25 pF load,<br>60/40 duty cycle   |

| SID76    | F <sub>GPIOUT3</sub> | GPIO F <sub>OUT</sub> ; 3.3 V $\leq$ V <sub>DDD</sub> $\leq$ 5.5 V Slow strong mode | _   | _   | 7    |       | 90/10%, 25 pF load,<br>60/40 duty cycle   |

| SID245   | F <sub>GPIOUT4</sub> | GPIO $F_{OUT}$ ; 1.71 V $\leq$ V <sub>DDD</sub> $\leq$ 3.3 V Slow strong mode.      | _   | -   | 3.5  | -     | 90/10%, 25 pF load,<br>60/40 duty cycle   |

| SID246   | F <sub>GPIOIN</sub>  | GPIO input operating frequency; 1.71 V $\leq$ V <sub>DDD</sub> $\leq$ 5.5 V         | _   | -   | 48   |       | 90/10% V <sub>IO</sub>                    |

XRES

## Table 7. XRES DC Specifications

| Spec ID#             | Parameter            | Description                                                       | Min                  | Тур | Max                 | Units | Details/<br>Conditions                                      |

|----------------------|----------------------|-------------------------------------------------------------------|----------------------|-----|---------------------|-------|-------------------------------------------------------------|

| SID77                | V <sub>IH</sub>      | Input voltage high threshold                                      | $0.7 \times V_{DDD}$ | -   | -                   | V     | CMOS Input                                                  |

| SID78                | V <sub>IL</sub>      | Input voltage low threshold                                       | -                    | -   | $0.3\times V_{DDD}$ | v     |                                                             |

| SID79                | R <sub>PULLUP</sub>  | Pull-up resistor                                                  | -                    | 60  | -                   | kΩ    | -                                                           |

| SID80                | C <sub>IN</sub>      | Input capacitance                                                 | -                    | -   | 7                   | pF    | -                                                           |

| SID81 <sup>[5]</sup> | V <sub>HYSXRES</sub> | Input voltage hysteresis                                          | -                    | 100 | -                   | mV    | Typical hysteresis is<br>200 mV for V <sub>DD</sub> > 4.5 V |

| SID82                | I <sub>DIODE</sub>   | Current through protection diode to $V_{\text{DD}}/V_{\text{SS}}$ | _                    | _   | 100                 | μA    |                                                             |

### Table 8. XRES AC Specifications

| Spec ID#              | Parameter               | Description                     | Min | Тур | Max | Units | Details/<br>Conditions |

|-----------------------|-------------------------|---------------------------------|-----|-----|-----|-------|------------------------|

| SID83 <sup>[5]</sup>  | T <sub>RESETWIDTH</sub> | Reset pulse width               | 1   | -   | -   | μs    | -                      |

| BID194 <sup>[5]</sup> | T <sub>RESETWAKE</sub>  | Wake-up time from reset release | -   | -   | 2.7 | ms    | -                      |

## Table 9. CTBm Opamp Specifications (continued)

| Spec ID# | Parameter             | Description                                              | Min   | Тур  | Max                   | Units   | Details/<br>Conditions                                                                    |

|----------|-----------------------|----------------------------------------------------------|-------|------|-----------------------|---------|-------------------------------------------------------------------------------------------|

|          |                       | General opamp specs for both internal and external modes |       | 1    |                       | 1       |                                                                                           |

| SID281   | V <sub>IN</sub>       | Charge-pump on, V <sub>DDA</sub> = 2.7 V                 | -0.05 | _    | V <sub>DDA</sub> -0.2 | v       | -                                                                                         |

| SID282   | V <sub>CM</sub>       | Charge-pump on, V <sub>DDA</sub> = 2.7 V                 | -0.05 | _    | V <sub>DDA</sub> -0.2 |         | _                                                                                         |

|          | V <sub>OUT</sub>      | V <sub>DDA</sub> = 2.7 V                                 |       |      | 1                     | 1       |                                                                                           |

| SID283   | V <sub>OUT_1</sub>    | power=hi, lload=10 mA                                    | 0.5   | _    | V <sub>DDA</sub> -0.5 |         | _                                                                                         |

| SID284   | V <sub>OUT_2</sub>    | power=hi, lload=1 mA                                     | 0.2   | -    | V <sub>DDA</sub> -0.2 | v       | _                                                                                         |

| SID285   | V <sub>OUT_3</sub>    | power=med, lload=1 mA                                    | 0.2   | _    | V <sub>DDA</sub> -0.2 | v       | _                                                                                         |

| SID286   | V <sub>OUT_4</sub>    | power=lo, lload=0.1 mA                                   | 0.2   | _    | V <sub>DDA</sub> -0.2 |         | _                                                                                         |

| SID288   | V <sub>OS_TR</sub>    | Offset voltage, trimmed                                  | -1.0  | ±0.5 | 1.0                   |         | High mode, input 0 V<br>to V <sub>DDA</sub> -0.2 V                                        |

| SID288A  | V <sub>OS_TR</sub>    | Offset voltage, trimmed                                  | _     | ±1   | -                     | mV      | Medium mode, input<br>0 V to V <sub>DDA</sub> -0.2 V                                      |

| SID288B  | V <sub>OS_TR</sub>    | Offset voltage, trimmed                                  | -     | ±2   | -                     |         | Low mode, input 0 V<br>to V <sub>DDA</sub> -0.2 V                                         |

| SID290   | V <sub>OS_DR_TR</sub> | Offset voltage drift, trimmed                            | -10   | ±3   | 10                    | μV/C    | High mode                                                                                 |

| SID290A  | V <sub>OS_DR_TR</sub> | Offset voltage drift, trimmed                            | _     | ±10  | -                     |         | Medium mode                                                                               |

| SID290B  | V <sub>OS_DR_TR</sub> | Offset voltage drift, trimmed                            | _     | ±10  | _                     | μV/C    | Low mode                                                                                  |

| SID291   | CMRR                  | DC                                                       | 70    | 80   | _                     |         | Input is 0 V to<br>V <sub>DDA</sub> -0.2 V, Output is<br>0.2 V to V <sub>DDA</sub> -0.2 V |

| SID292   | PSRR                  | At 1 kHz, 10-mV ripple                                   | 70    | 85   | _                     | dB      | $V_{DDD}$ = 3.6 V,<br>high-power mode,<br>input is 0.2 V to<br>$V_{DDA}$ -0.2 V           |

|          | Noise                 |                                                          |       |      |                       |         |                                                                                           |

| SID294   | VN2                   | Input-referred, 1 kHz, power=Hi                          | _     | 72   | _                     |         | 3                                                                                         |

| SID295   | VN3                   | Input-referred, 10 kHz,<br>power=Hi                      | _     | 28   | _                     | nV/rtHz | Input and output are at 0.2 V to V <sub>DDA</sub> -0.2 V                                  |

| SID296   | VN4                   | Input-referred, 100 kHz,<br>power=Hi                     | _     | 15   | _                     |         | Input and output are at 0.2 V to V <sub>DDA</sub> -0.2 V                                  |

| SID297   | C <sub>LOAD</sub>     | Stable up to max. load.<br>Performance specs at 50 pF.   | -     | _    | 125                   | pF      | _                                                                                         |

| SID298   | SLEW_RATE             | Cload = 50 pF, Power = High,<br>$V_{DDA}$ = 2.7 V        | 6     | _    | -                     | V/µs    | _                                                                                         |

### Table 9. CTBm Opamp Specifications (continued)

| Spec ID#  | Parameter               | Description            | Min | Тур | Мах | Units | Details/<br>Conditions                                        |

|-----------|-------------------------|------------------------|-----|-----|-----|-------|---------------------------------------------------------------|

| SID_DS_7  | G <sub>BW_HI_M1</sub>   | Mode 1, High current   | _   | 4   | -   |       | 20-pF load, no DC<br>load 0.2 V to<br>V <sub>DDA</sub> -0.2 V |

| SID_DS_8  | G <sub>BW_MED_M1</sub>  | Mode 1, Medium current | _   | 2   | _   |       | 20-pF load, no DC<br>load 0.2 V to<br>V <sub>DDA</sub> -0.2 V |

| SID_DS_9  | G <sub>BW_LOW_M!</sub>  | Mode 1, Low current    | _   | 0.5 | _   | -<br> | 20-pF load, no DC<br>load 0.2 V to<br>V <sub>DDA</sub> -0.2 V |

| SID_DS_10 | G <sub>BW_HI_M2</sub>   | Mode 2, High current   | _   | 0.5 | _   | MHz   | 20-pF load, no DC<br>load 0.2 V to<br>V <sub>DDA</sub> -0.2 V |

| SID_DS_11 | G <sub>BW_MED_M2</sub>  | Mode 2, Medium current | _   | 0.2 | _   |       | 20-pF load, no DC<br>load 0.2 V to<br>V <sub>DDA</sub> -0.2 V |

| SID_DS_12 | G <sub>BW_Low_M2</sub>  | Mode 2, Low current    | _   | 0.1 | _   |       | 20-pF load, no DC<br>load 0.2 V to<br>V <sub>DDA</sub> -0.2 V |

| SID_DS_13 | V <sub>OS_HI_M1</sub>   | Mode 1, High current   | -   | 5   | -   |       | With trim 25 °C, 0.2 V to $V_{DDA}$ -0.2 V                    |

| SID_DS_14 | V <sub>OS_MED_M1</sub>  | Mode 1, Medium current | -   | 5   | -   |       | With trim 25 °C, 0.2 V<br>to V <sub>DDA</sub> -0.2 V          |

| SID_DS_15 | V <sub>OS_LOW_M2</sub>  | Mode 1, Low current    | -   | 5   | -   |       | With trim 25 °C, 0.2 V<br>to V <sub>DDA</sub> -0.2 V          |

| SID_DS_16 | V <sub>OS_HI_M2</sub>   | Mode 2, High current   | -   | 5   | -   | mV    | With trim 25 °C, 0.2V<br>to V <sub>DDA</sub> -0.2 V           |

| SID_DS_17 | V <sub>OS_MED_M2</sub>  | Mode 2, Medium current | _   | 5   | -   |       | With trim 25 °C, 0.2 V<br>to V <sub>DDA</sub> -0.2 V          |

| SID_DS_18 | V <sub>OS_LOW_M2</sub>  | Mode 2, Low current    | -   | 5   | -   |       | With trim 25 °C, 0.2 V<br>to V <sub>DDA</sub> -0.2 V          |

| SID_DS_19 | I <sub>OUT_HI_M!</sub>  | Mode 1, High current   | -   | 10  | -   |       | Output is 0.5 V to<br>V <sub>DDA</sub> -0.5 V                 |

| SID_DS_20 | IOUT_MED_M1             | Mode 1, Medium current | -   | 10  | -   |       | Output is 0.5 V to<br>V <sub>DDA</sub> -0.5 V                 |

| SID_DS_21 | I <sub>OUT_LOW_M1</sub> | Mode 1, Low current    | _   | 4   | -   | - mA  | Output is 0.5 V to<br>V <sub>DDA</sub> -0.5 V                 |

| SID_DS_22 | I <sub>OUT_HI_M2</sub>  | Mode 2, High current   | -   | 1   | -   |       |                                                               |

| SID_DS_23 | I <sub>OU_MED_M2</sub>  | Mode 2, Medium current | _   | 1   | -   |       |                                                               |

| SID_DS_24 | I <sub>OU_LOW_M2</sub>  | Mode 2, Low current    | _   | 0.5 | -   |       |                                                               |

Note 6. Guaranteed by characterization.

## Table 13. SAR Specifications (continued)

| Spec ID# | Parameter      | Description                                                            | Min      | Тур | Мах              | Units | Details/<br>Conditions                        |

|----------|----------------|------------------------------------------------------------------------|----------|-----|------------------|-------|-----------------------------------------------|

| SID99    | A_OFFSET       | Input offset voltage                                                   | _        | -   | 2                | mV    | Measured with<br>1-V reference                |

| SID100   | A_ISAR         | Current consumption                                                    | -        | -   | 1                | mA    |                                               |

| SID101   | A_VINS         | Input voltage range - single ended                                     | $V_{SS}$ | -   | V <sub>DDA</sub> | V     |                                               |

| SID102   | A_VIND         | Input voltage range - differential[                                    | $V_{SS}$ | -   | V <sub>DDA</sub> | V     |                                               |

| SID103   | A_INRES        | Input resistance                                                       | -        | -   | 2.2              | KΩ    |                                               |

| SID104   | A_INCAP        | Input capacitance                                                      | -        | -   | 10               | pF    |                                               |

| SID260   | VREFSAR        | Trimmed internal reference to SAR                                      | -        | -   | TBD              | V     |                                               |

| SAR ADC  | AC Specificati | ions                                                                   |          |     |                  |       | •                                             |

| SID106   | A_PSRR         | Power supply rejection ratio                                           | 70       | -   | -                | dB    |                                               |

| SID107   | A_CMRR         | Common mode rejection ratio                                            | 66       | -   | -                | dB    | Measured at 1 V                               |

| SID108   | A_SAMP         | Sample rate                                                            | -        | -   | 1                | Msps  |                                               |

| SID109   | A_SNR          | Signal-to-noise and distortion ratio (SINAD)                           | 65       | -   | -                | dB    | F <sub>IN</sub> = 10 kHz                      |

| SID110   | A_BW           | Input bandwidth without aliasing                                       | -        | -   | A_samp/2         | kHz   |                                               |

| SID111   | A_INL          | Integral non linearity. $V_{DD}$ = 1.71 to 5.5, 1 Msps                 | -1.7     | -   | 2                | LSB   | $V_{REF}$ = 1 to $V_{DD}$                     |

| SID111A  | A_INL          | Integral non linearity. V <sub>DDD</sub> = 1.71 to 3.6, 1 Msps         | -1.5     | -   | 1.7              | LSB   | V <sub>REF</sub> = 1.71 to<br>V <sub>DD</sub> |

| SID111B  | A_INL          | Integral non linearity. $V_{DD}$ = 1.71 to 5.5, 500 ksps               | -1.5     | -   | 1.7              | LSB   | V <sub>REF</sub> = 1 to V <sub>DD</sub>       |

| SID112   | A_DNL          | Differential non linearity. V <sub>DD</sub> = 1.71 to 5.5,<br>1 Msps   | –1       | -   | 2.2              | LSB   | $V_{REF}$ = 1 to $V_{DD}$                     |

| SID112A  | A_DNL          | Differential non linearity. V <sub>DD</sub> = 1.71 to 3.6,<br>1 Msps   | –1       | -   | 2                | LSB   | V <sub>REF</sub> = 1.71 to<br>V <sub>DD</sub> |

| SID112B  | A_DNL          | Differential non linearity. V <sub>DD</sub> = 1.71 to 5.5,<br>500 ksps | -1       | -   | 2.2              | LSB   | $V_{REF}$ = 1 to $V_{DD}$                     |

| SID113   | A_THD          | Total harmonic distortion                                              | -        | -   | -65              | dB    | Fin = 10 kHz                                  |

| SID261   | FSARINTRE<br>F | SAR operating speed without external ref. bypass                       | _        | _   | 100              | ksps  | 12-bit resolution                             |

## Table 14. CSD and IDAC Specifications (continued)

| SPEC ID# | Parameter     | Description                                          | Min | Тур | Max | Units | Details / Conditions                                                        |

|----------|---------------|------------------------------------------------------|-----|-----|-----|-------|-----------------------------------------------------------------------------|

| SID315G  | IDAC3CRT23    | Output current of IDAC in 8-bit mode in medium range | 69  | -   | 82  | μA    | LSB = 300-nA typ.                                                           |

| SID315H  | IDAC3CRT33    | Output current of IDAC in 8-bit mode in high range   | 540 | -   | 660 | μA    | LSB = 2.4-µA typ.                                                           |

| SID320   | IDACOFFSET    | All zeroes input                                     | -   | -   | 1   | LSB   | Polarity set by Source or<br>Sink. Offset is 2 LSBs for<br>37.5 nA/LSB mode |

| SID321   | IDACGAIN      | Full-scale error less offset                         | -   | -   | ±10 | %     |                                                                             |

| SID322   | IDACMISMATCH1 | Mismatch between IDAC1 and IDAC2 in Low mode         | -   | -   | 9.2 | LSB   | LSB = 37.5-nA typ.                                                          |

| SID322A  | IDACMISMATCH2 | Mismatch between IDAC1 and IDAC2 in Medium mode      | -   | -   | 5.6 | LSB   | LSB = 300-nA typ.                                                           |

| SID322B  | IDACMISMATCH3 | Mismatch between IDAC1 and IDAC2 in High mode        | -   | -   | 6.8 | LSB   | LSB = 2.4-µA typ.                                                           |

| SID323   | IDACSET8      | Settling time to 0.5 LSB for 8-bit IDAC              | -   | -   | 10  | μs    | Full-scale transition. No external load.                                    |

| SID324   | IDACSET7      | Settling time to 0.5 LSB for 7-bit IDAC              | -   | -   | 10  | μs    | Full-scale transition. No external load.                                    |

| SID325   | CMOD          | External modulator capacitor.                        | -   | 2.2 | -   | nF    | 5-V rating, X7R or NP0 cap.                                                 |

## Table 15. 10-bit CapSense ADC Specifications

| Spec ID# | Parameter | Description                                                                                                              | Min              | Тур | Max       | Units | Details/<br>Conditions                                                                            |

|----------|-----------|--------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----------|-------|---------------------------------------------------------------------------------------------------|

| SIDA94   | A_RES     | Resolution                                                                                                               | -                | -   | 10        | bits  | Auto-zeroing is required every millisecond                                                        |

| SIDA95   | A_CHNLS_S | Number of channels - single ended                                                                                        | -                | -   | 16        |       | Defined by AMUX Bus.                                                                              |

| SIDA97   | A-MONO    | Monotonicity                                                                                                             | -                | -   | -         | Yes   |                                                                                                   |

| SIDA98   | A_GAINERR | Gain error                                                                                                               | -                | -   | ±2        | %     | In $V_{REF}$ (2.4 V) mode<br>with $V_{DDA}$ bypass<br>capacitance of 10 $\mu$ F                   |

| SIDA99   | A_OFFSET  | Input offset voltage                                                                                                     | _                | -   | 3         | mV    | In $V_{REF}$ (2.4 V) mode<br>with $V_{DDA}$ bypass<br>capacitance of 10 $\mu$ F                   |

| SIDA100  | A_ISAR    | Current consumption                                                                                                      | -                | -   | 0.25      | mA    |                                                                                                   |

| SIDA101  | A_VINS    | Input voltage range - single ended                                                                                       | V <sub>SSA</sub> | -   | $V_{DDA}$ | V     |                                                                                                   |

| SIDA103  | A_INRES   | Input resistance                                                                                                         | _                | 2.2 | -         | KΩ    |                                                                                                   |

| SIDA104  | A_INCAP   | Input capacitance                                                                                                        | _                | 20  | -         | pF    |                                                                                                   |

| SIDA106  | A_PSRR    | Power supply rejection ratio                                                                                             | _                | 60  | _         | dB    | In $V_{REF}$ (2.4 V) mode<br>with $V_{DDA}$ bypass<br>capacitance of 10 $\mu$ F                   |

| SIDA107  | A_TACQ    | Sample acquisition time                                                                                                  | -                | 1   | -         | μs    |                                                                                                   |

| SIDA108  | A_CONV8   | Conversion time for 8-bit resolution at<br>conversion rate = Fhclk/(2 <sup>^</sup> (N+2)).<br>Clock frequency = 48 MHz.  | _                | -   | 21.3      | μs    | Does not include acqui-<br>sition time. Equivalent to<br>44.8 ksps including<br>acquisition time. |

| SIDA108A | A_CONV10  | Conversion time for 10-bit resolution at<br>conversion rate = Fhclk/(2 <sup>^</sup> (N+2)).<br>Clock frequency = 48 MHz. | _                | _   | 85.3      | μs    | Does not include acqui-<br>sition time. Equivalent to<br>11.6 ksps including<br>acquisition time. |

| Table 15. 10-bit CapSense ADC Specifications (continued | Table 15. | 10-bit CapSense | <b>ADC Specifications</b> | (continued) |

|---------------------------------------------------------|-----------|-----------------|---------------------------|-------------|

|---------------------------------------------------------|-----------|-----------------|---------------------------|-------------|

| Spec ID# | Parameter | Description                                  | Min | Тур | Мах  | Units | Details/<br>Conditions                                                                       |

|----------|-----------|----------------------------------------------|-----|-----|------|-------|----------------------------------------------------------------------------------------------|

| SIDA109  | A_SND     | Signal-to-noise and Distortion ratio (SINAD) | -   | 61  | _    |       | With 10-Hz input sine<br>wave, external 2.4-V<br>reference, V <sub>REF</sub> (2.4 V)<br>mode |

| SIDA110  | A_BW      | Input bandwidth without aliasing             | -   | -   | 22.4 | KHz   | 8-bit resolution                                                                             |

| SIDA111  | A_INL     | Integral Non Linearity. 1 ksps               | _   | _   | 2    | LSB   | V <sub>REF</sub> = 2.4 V or greater                                                          |

| SIDA112  | A_DNL     | Differential Non Linearity. 1 ksps           | _   | -   | 1    | LSB   |                                                                                              |

## **Digital Peripherals**

Timer Counter Pulse-Width Modulator (TCPWM)

### Table 16. TCPWM Specifications

| Spec ID      | Parameter             | Description                         | Min  | Тур | Max | Units | Details/Conditions                                                                                    |

|--------------|-----------------------|-------------------------------------|------|-----|-----|-------|-------------------------------------------------------------------------------------------------------|

| SID.TCPWM.1  | ITCPWM1               | Block current consumption at 3 MHz  | -    | -   | 45  |       | All modes (TCPWM)                                                                                     |

| SID.TCPWM.2  | ITCPWM2               | Block current consumption at 12 MHz | -    | -   | 155 | μA    | All modes (TCPWM)                                                                                     |

| SID.TCPWM.2A | ITCPWM3               | Block current consumption at 48 MHz | -    | -   | 650 |       | All modes (TCPWM)                                                                                     |

| SID.TCPWM.3  | TCPWM <sub>FREQ</sub> | Operating frequency                 | _    | -   | Fc  | MHz   | Fc max = CLK_SYS<br>Maximum = 48 MHz                                                                  |

| SID.TCPWM.4  | TPWM <sub>ENEXT</sub> | Input trigger pulse width           | 2/Fc | -   | -   |       | For all trigger events <sup>[7]</sup>                                                                 |

| SID.TCPWM.5  | TPWM <sub>EXT</sub>   | Output trigger pulse widths         | 2/Fc | -   | _   |       | Minimum possible width<br>of Overflow, Underflow,<br>and CC (Counter equals<br>Compare value) outputs |

| SID.TCPWM.5A | TC <sub>RES</sub>     | Resolution of counter               | 1/Fc | _   | _   | ns    | Minimum time between successive counts                                                                |

| SID.TCPWM.5B | PWM <sub>RES</sub>    | PWM resolution                      | 1/Fc | -   | _   |       | Minimum pulse width of<br>PWM Output                                                                  |

| SID.TCPWM.5C | Q <sub>RES</sub>      | Quadrature inputs resolution        | 1/Fc | _   | _   |       | Minimum pulse width<br>between Quadrature<br>phase inputs                                             |

# ľC

# Table 17. Fixed I<sup>2</sup>C DC Specifications<sup>[8]</sup>

| Spec ID | Parameter         | Description                                 | Min | Тур | Max | Units | <b>Details/Conditions</b> |

|---------|-------------------|---------------------------------------------|-----|-----|-----|-------|---------------------------|

| SID149  | I <sub>I2C1</sub> | Block current consumption at 100 kHz        | -   | -   | 50  |       | -                         |

| SID150  | I <sub>I2C2</sub> | Block current consumption at 400 kHz        | -   | -   | 135 | μA    | _                         |

| SID151  | I <sub>I2C3</sub> | Block current consumption at 1 Mbps         | -   | -   | 310 |       | _                         |

| SID152  | I <sub>I2C4</sub> | I <sup>2</sup> C enabled in Deep Sleep mode | -   | -   | 1.4 |       |                           |

# Table 18. Fixed I<sup>2</sup>C AC Specifications<sup>[8]</sup>

| Spec ID | Parameter         | Description | Min | Тур | Max | Units | <b>Details/Conditions</b> |

|---------|-------------------|-------------|-----|-----|-----|-------|---------------------------|

| SID153  | F <sub>I2C1</sub> | Bit rate    | -   | -   | 1   | Msps  | _                         |

Notes

7. Trigger events can be Stop, Start, Reload, Count, Capture, or Kill depending on which mode of operation is selected.

#### Note

8. Guaranteed by characterization.

# Table 21. UART DC Specifications<sup>[9]</sup>

| Spec ID | Parameter          | Description                            | Min | Тур | Max | Units | Details/Conditions |

|---------|--------------------|----------------------------------------|-----|-----|-----|-------|--------------------|

| SID160  | I <sub>UART1</sub> | Block current consumption at 100 Kbps  | Ι   | -   | 55  | μA    | -                  |

| SID161  | I <sub>UART2</sub> | Block current consumption at 1000 Kbps | _   | _   | 312 | μA    | _                  |

# Table 22. UART AC Specifications<sup>[9]</sup>

| Spec ID | Parameter         | Description | Min | Тур | Max | Units | Details/Conditions |

|---------|-------------------|-------------|-----|-----|-----|-------|--------------------|

| SID162  | F <sub>UART</sub> | Bit rate    | _   |     | 1   | Mbps  | _                  |

# Table 23. LCD Direct Drive DC Specifications<sup>[9]</sup>

| Spec ID | Parameter             | Description                                   | Min | Тур | Max  | Units | Details/Conditions                       |

|---------|-----------------------|-----------------------------------------------|-----|-----|------|-------|------------------------------------------|

| SID154  | ILCDLOW               | Operating current in low power mode           | -   | 5   | -    | μA    | $16\times4$ small segment disp. at 50 Hz |

| SID155  | C <sub>LCDCAP</sub>   | LCD capacitance per<br>segment/common driver  | -   | 500 | 5000 | pF    | -                                        |

| SID156  | LCD <sub>OFFSET</sub> | Long-term segment offset                      | -   | 20  | -    | mV    | -                                        |

| SID157  | I <sub>LCDOP1</sub>   | LCD system operating current<br>Vbias = 5 V   | -   | 2   | -    | m۸    | $32 \times 4$ segments. 50 Hz. 25 °C     |

| SID158  | I <sub>LCDOP2</sub>   | LCD system operating current<br>Vbias = 3.3 V | _   | 2   | _    | mA    | $32 \times 4$ segments. 50 Hz. 25 °C     |

# Table 24. LCD Direct Drive AC Specifications<sup>[9]</sup>

| Spec ID | Parameter        | Description    | Min | Тур | Max | Units | Details/Conditions |

|---------|------------------|----------------|-----|-----|-----|-------|--------------------|

| SID159  | F <sub>LCD</sub> | LCD frame rate | 10  | 50  | 150 | Hz    | _                  |

# **Ordering Information**

The marketing part numbers for the PSoC 4100S family are listed in the following table.

|          | MPN                                  | Features            |            |           |              |     |                | Featur         | es                   |                |              |            |            |          | Package                 |        |        |         |         |

|----------|--------------------------------------|---------------------|------------|-----------|--------------|-----|----------------|----------------|----------------------|----------------|--------------|------------|------------|----------|-------------------------|--------|--------|---------|---------|

| Category |                                      | Max CPU Speed (MHz) | Flash (KB) | SRAM (KB) | Opamp (CTBm) | CSD | 10-bit CSD ADC | 12-bit SAR ADC | ADC Sample Rate      | LP Comparators | TCPWM Blocks | SCB Blocks | Smart I/Os | GPIO     | 35-WLCSP (0.35mm pitch) | 32-QFN | 40-QFN | 48-TQFP | 44-TQFP |

|          | CY8C4124FNI-S403                     | 24                  | 16         | 4         | 2            | 0   | 1              | 0              |                      | 2              | 5            | 2          | 8          | 31       | Х                       |        |        |         |         |

|          | CY8C4124FNI-S413                     | 24                  | 16         | 4         | 2            | 1   | 1              | 0              |                      | 2              | 5            | 2          | 16         | 31       | Х                       |        |        |         |         |

|          | CY8C4124LQI-S412                     | 24                  | 16         | 4         | 2            | 1   | 1              | 0              |                      | 2              | 5            | 2          | 16         | 27       |                         | Х      |        |         |         |

|          | CY8C4124LQI-S413                     | 24                  | 16         | 4         | 2            | 1   | 1              | 0              |                      | 2              | 5            | 2          | 16         | 34       |                         |        | Х      |         |         |

| 4124     | CY8C4124AZI-S413                     | 24                  | 16         | 4         | 2            | 1   | 1              | 0              |                      | 2              | 5            | 2          | 16         | 36       |                         |        |        | Х       |         |

|          | CY8C4124FNI-S433                     | 24                  | 16         | 4         | 2            | 1   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 31       | Х                       |        |        |         |         |

|          | CY8C4124LQI-S432                     | 24                  | 16         | 4         | 2            | 1   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 27       |                         | Х      |        |         |         |

|          | CY8C4124LQI-S433                     | 24                  | 16         | 4         | 2            | 1   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 34       |                         |        | Х      |         |         |

|          | CY8C4124AZI-S433                     | 24                  | 16         | 4         | 2            | 1   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 36       |                         |        |        | Х       |         |

|          | CY8C4125FNI-S423                     | 24                  | 32         | 4         | 2            | 0   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 31       | Х                       |        |        |         |         |

|          | CY8C4125LQI-S422                     | 24                  | 32         | 4         | 2            | 0   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 27       |                         | Х      |        |         |         |

|          | CY8C4125LQI-S423                     | 24                  | 32         | 4         | 2            | 0   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 34       |                         |        | Х      |         |         |

|          | CY8C4125AZI-S423                     | 24                  | 32         | 4         | 2            | 0   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 36       |                         |        |        | Х       |         |

|          | CY8C4125AXI-S423                     | 24                  | 32         | 4         | 2            | 0   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 36       |                         |        |        |         | Х       |

|          | CY8C4125FNI-S413                     | 24                  | 32         | 4         | 2            | 1   | 1              | 0              |                      | 2              | 5            | 2          | 16         | 31       | Х                       |        |        |         |         |

| 4125     | CY8C4125LQI-S412                     | 24                  | 32         | 4         | 2            | 1   | 1              | 0              |                      | 2              | 5            | 2          | 16         | 27       |                         | Х      |        |         |         |

|          | CY8C4125LQI-S413                     | 24                  | 32         | 4         | 2            | 1   | 1              | 0              |                      | 2              | 5            | 2          | 16         | 34       |                         |        | Х      |         |         |

|          | CY8C4125AZI-S413                     | 24                  | 32         | 4         | 2            | 1   | 1              | 0              |                      | 2              | 5            | 2          | 16         | 36       |                         |        |        | Х       |         |

|          | CY8C4125FNI-S433                     | 24                  | 32         | 4         | 2            | 1   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 31       | Х                       |        |        |         |         |

|          | CY8C4125LQI-S432                     | 24                  | 32         | 4         | 2            | 1   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 27       |                         | Х      |        | -       |         |

|          | CY8C4125LQI-S433                     | 24                  | 32         | 4         | 2            | 1   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 34       |                         |        | Х      |         |         |

|          | CY8C4125AZI-S433                     | 24                  | 32         | 4         | 2            | 1   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 36       |                         |        |        | Х       |         |

|          | CY8C4125AXI-S433                     | 24                  | 32         | 4         | 2            | 1   | 1              | 1              | 806 ksps             | 2              | 5            | 2          | 16         | 36       |                         |        |        | X       | Х       |

|          | CY8C4126AZI-S423                     | 24                  | 64         | 8         | 2            | 0   | 1              | 1              | 806 ksps             | 2              | 5<br>5       | 3          | 16         | 36       |                         |        |        | Х       | v       |

| 4126     | CY8C4126AXI-S423<br>CY8C4126AZI-S433 | 24<br>24            | 64<br>64   | 8<br>8    | 2            | 0   | 1              | 1<br>1         | 806 ksps<br>806 ksps | 2              | 5<br>5       | 3          | 16<br>16   | 36<br>36 |                         |        |        | х       | Х       |

|          | CY8C4126AXI-S433                     | 24                  | 64         | 0<br>8    | 2            | 1   | 1              | 1              | 806 ksps             | 2              | 5            | 3          | 16         | 36       |                         |        |        | ^       | x       |

|          | CY8C4145AZI-S423                     | 48                  | 32         | 0<br>4    | 2            | 0   | 1              | 1              | 1 Msps               | 2              | 5            | 2          | 16         | 36       |                         |        |        | х       | ^       |

| 4145     | CY8C4145AXI-S423                     | 48                  | 32         | 4         | 2            | 0   | 1              | 1              | 1 Msps               | 2              | 5            | 2          | 16         | 36       |                         |        |        | ~       | х       |

| - 1-0    | CY8C4145AXI-S423                     | 48                  | 32         | 4         | 2            | 1   | 1              | 1              | 1 Msps               | 2              | 5            | 2          | 16         | 36       |                         |        |        |         | ×       |

|          | CY8C4146FNI-S423                     | 48                  | 64         | 8         | 2            | 0   | 1              | 1              | 1 Msps               | 2              | 5            | 3          | 16         | 31       | х                       |        |        |         | ^       |

|          | CY8C4146LQI-S422                     | 48                  | 64         | 8         | 2            | 0   | 1              | 1              | 1 Msps               | 2              | 5            | 3          | 16         | 27       | ~                       | х      |        |         |         |

|          | CY8C4146LQI-S422                     | 40                  | 64         | 8         | 2            | 0   | 1              | 1              | 1 Msps               | 2              | 5            | 3          | 16         | 34       |                         | ~      | х      |         |         |

|          | CY8C4146AZI-S423                     | 48                  | 64         | 8         | 2            | 0   | 1              | 1              | 1 Msps               | 2              | 5            | 3          | 16         | 36       |                         |        | ~      | х       |         |

|          | CY8C4146AXI-S423                     | 48                  | 64         | 8         | 2            | 0   | 1              | 1              | 1 Msps               | 2              | 5            | 3          | 16         | 36       |                         |        |        |         | х       |

| 4146     | CY8C4146FNI-S433                     | 48                  | 64         | 8         | 2            | 1   | 1              | 1              | 1 Msps               | 2              | 5            | 3          | 16         | 31       | Х                       |        |        |         |         |

|          | CY8C4146LQI-S432                     | 48                  | 64         | 8         | 2            | 1   | 1              | 1              | 1 Msps               | 2              | 5            | 3          | 16         | 27       | -                       | Х      |        |         |         |

|          | CY8C4146LQI-S433                     | 48                  | 64         | 8         | 2            | 1   | 1              | 1              | 1 Msps               | 2              | 5            | 3          | 16         | 34       |                         |        | х      |         |         |

|          | CY8C4146AZI-S433                     | 48                  | 64         | 8         | 2            | 1   | 1              | 1              | 1 Msps               | 2              | 5            | 3          | 16         | 36       |                         |        |        | Х       |         |

|          | CY8C4146AXI-S433                     | 48                  | 64         | 8         | 2            | 1   | 1              | 1              | 1 Msps               | 2              | 5            | 3          | 16         | 36       |                         |        |        |         | х       |

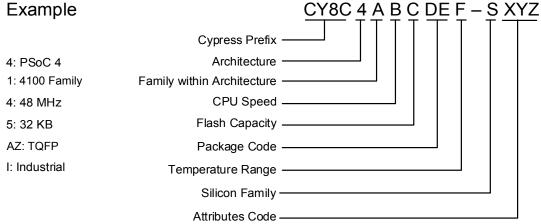

| Field | Description       | Values  | Meaning                                    |

|-------|-------------------|---------|--------------------------------------------|

| CY8C  | Cypress Prefix    |         |                                            |

| 4     | Architecture      | 4       | PSoC 4                                     |

| А     | Family            | 1       | 4100 Family                                |

| В     | CPU Speed         | 2       | 24 MHz                                     |

|       |                   | 4       | 48 MHz                                     |

| С     | Flash Capacity    | 4       | 16 KB                                      |

|       |                   | 5       | 32 KB                                      |

|       |                   | 6       | 64 KB                                      |

|       |                   | 7       | 128 KB                                     |

| DE    | Package Code      | AX      | TQFP (0.8mm pitch)                         |

|       |                   | AZ      | TQFP (0.5mm pitch)                         |

|       |                   | LQ      | QFN                                        |

|       |                   | PV      | SSOP                                       |

|       |                   | FN      | CSP                                        |

| F     | Temperature Range | I       | Industrial                                 |

| S     | Silicon Family    | S       | PSoC 4A-S1, PSoC 4A-S2                     |

|       |                   | М       | PSoC 4A-M                                  |

|       |                   | L       | PSoC 4A-L                                  |

|       |                   | BL      | PSoC 4A-BLE                                |

| XYZ   | Attributes Code   | 000-999 | Code of feature set in the specific family |

The nomenclature used in the preceding table is based on the following part numbering convention:

The following is an example of a part number:

# Example

# Packaging

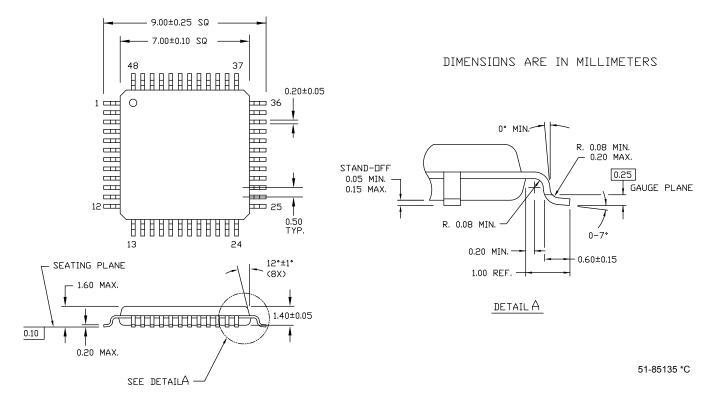

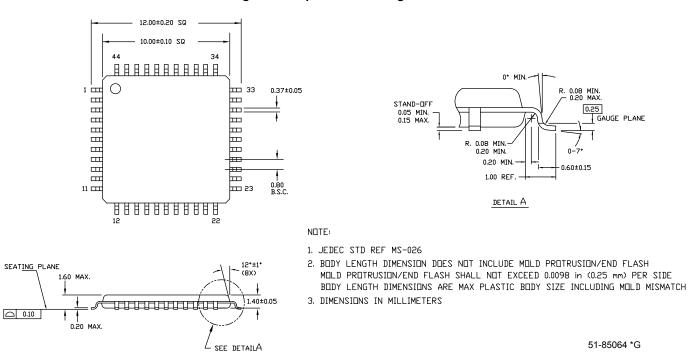

The PSoC 4100S will be offered in 48-pin TQFP, 44-pin TQFP, 40-pin QFN, 32-pin QFN, and 35-ball WLCSP packages. Package dimensions and Cypress drawing numbers are in the following table.

## Table 38. Package List

| Spec ID# | Package       | Description                                   | Package Dwg |

|----------|---------------|-----------------------------------------------|-------------|

| BID20    | 48-pin TQFP   | 7 × 7 × 1.4-mm height with 0.5-mm pitch       | 51-85135    |

| BID20A   | 44-pin TQFP   | 10 × 10 × 1.6-mm height with 0.8-mm pitch     | 51-85064    |

| BID27    | 40-pin QFN    | 6 × 6 × 0.6-mm height with 0.5-mm pitch       | 001-80659   |

| BID34A   | 32-pin QFN    | 5 × 5 × 0.6-mm height with 0.5-mm pitch       | 001-42168   |

| BID34D   | 35-ball WLCSP | 2.6 × 2.1 × 0.48-mm height with 0.35-mm pitch | 002-09958   |

### Table 39. Package Thermal Characteristics

| Parameter | Description                    | Package       | Min | Тур  | Max | Units   |

|-----------|--------------------------------|---------------|-----|------|-----|---------|

| TA        | Operating Ambient temperature  |               | -40 | 25   | 85  | °C      |

| TJ        | Operating junction temperature |               | -40 | -    | 100 | °C      |

| Tja       | Package θ <sub>JA</sub>        | 48-pin TQFP   | -   | 74.8 | -   | °C/Watt |

| TJC       | Package θ <sub>JC</sub>        | 48-pin TQFP   | -   | 35.7 | -   | °C/Watt |

| Tja       | Package θ <sub>JA</sub>        | 44-pin TQFP   | -   | 57.2 | -   | °C/Watt |

| TJC       | Package θ <sub>JC</sub>        | 44-pin TQFP   | -   | 17.5 | -   | °C/Watt |

| Tja       | Package θ <sub>JA</sub>        | 40-pin QFN    | -   | 17.8 | -   | °C/Watt |

| TJC       | Package θ <sub>JC</sub>        | 40-pin QFN    | -   | 2.8  | -   | °C/Watt |

| Tja       | Package θ <sub>JA</sub>        | 32-pin QFN    | -   | 19.9 | -   | °C/Watt |

| TJC       | Package θ <sub>JC</sub>        | 32-pin QFN    | -   | 4.3  | -   | °C/Watt |

| Tja       | Package θ <sub>JA</sub>        | 35-ball WLCSP | -   | 43   | -   | °C/Watt |

| TJC       | Package θ <sub>JC</sub>        | 35-ball WLCSP | _   | 0.3  | -   | °C/Watt |

### Table 40. Solder Reflow Peak Temperature

| Package | e Maximum Peak<br>Temperature | laximum Time at Peak Temperature |

|---------|-------------------------------|----------------------------------|

| All     | 260 °C                        | 30 seconds                       |

### Table 41. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-020

| Package          | MSL   |

|------------------|-------|

| All except WLCSP | MSL 3 |

| 35-ball WLCSP    | MSL 1 |

## **Package Diagrams**

# Acronyms

## Table 42. Acronyms Used in this Document

| Acronym | Description                                                                                           |

|---------|-------------------------------------------------------------------------------------------------------|

| abus    | analog local bus                                                                                      |

| ADC     | analog-to-digital converter                                                                           |

| AG      | analog global                                                                                         |

| АНВ     | AMBA (advanced microcontroller bus<br>architecture) high-performance bus, an ARM<br>data transfer bus |

| ALU     | arithmetic logic unit                                                                                 |

| AMUXBUS | analog multiplexer bus                                                                                |

| API     | application programming interface                                                                     |

| APSR    | application program status register                                                                   |

| ARM®    | advanced RISC machine, a CPU architecture                                                             |

| ATM     | automatic thump mode                                                                                  |

| BW      | bandwidth                                                                                             |

| CAN     | Controller Area Network, a communications protocol                                                    |

| CMRR    | common-mode rejection ratio                                                                           |

| CPU     | central processing unit                                                                               |

| CRC     | cyclic redundancy check, an error-checking protocol                                                   |

| DAC     | digital-to-analog converter, see also IDAC, VDAC                                                      |

| DFB     | digital filter block                                                                                  |

| DIO     | digital input/output, GPIO with only digital capabilities, no analog. See GPIO.                       |

| DMIPS   | Dhrystone million instructions per second                                                             |

| DMA     | direct memory access, see also TD                                                                     |

| DNL     | differential nonlinearity, see also INL                                                               |

| DNU     | do not use                                                                                            |

| DR      | port write data registers                                                                             |

| DSI     | digital system interconnect                                                                           |

| DWT     | data watchpoint and trace                                                                             |

| ECC     | error correcting code                                                                                 |

| ECO     | external crystal oscillator                                                                           |

| EEPROM  | electrically erasable programmable read-only memory                                                   |

| EMI     | electromagnetic interference                                                                          |

| EMIF    | external memory interface                                                                             |

| EOC     | end of conversion                                                                                     |

| EOF     | end of frame                                                                                          |

| EPSR    | execution program status register                                                                     |

| ESD     | electrostatic discharge                                                                               |

### Table 42. Acronyms Used in this Document (continued)

| Acronym                  | Description                                            |

|--------------------------|--------------------------------------------------------|

| ETM                      | embedded trace macrocell                               |

| FIR                      | finite impulse response, see also IIR                  |

| FPB                      | flash patch and breakpoint                             |

| FS                       | full-speed                                             |