Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 80MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, SWPMI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                     |

| Number of I/O              | 39                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                              |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 49-UFBGA, WLCSP                                                           |

| Supplier Device Package    | 49-WLCSP (3.14x3.13)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l431cby6tr   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                  |                  |                  |                      |                        | Stop             |                   |                  | op 2              | - | ndby              | 1 | down              |      |

|----------------------------------|------------------|------------------|----------------------|------------------------|------------------|-------------------|------------------|-------------------|---|-------------------|---|-------------------|------|

| Peripheral                       | Run              | Sleep            | Low-<br>power<br>run | Low-<br>power<br>sleep | -                | Wakeup capability | -                | Wakeup capability | - | Wakeup capability | - | Wakeup capability | VBAT |

| Low-power UART<br>(LPUART)       | 0                | 0                | 0                    | 0                      | O <sup>(6)</sup> | O <sup>(6)</sup>  | O <sup>(6)</sup> | O <sup>(6)</sup>  | - | -                 | - | -                 | -    |

| I2Cx (x=1,2)                     | 0                | 0                | 0                    | 0                      | O <sup>(7)</sup> | O <sup>(7)</sup>  | -                | -                 | - | -                 | - | -                 | -    |

| I2C3                             | 0                | 0                | 0                    | 0                      | O <sup>(7)</sup> | O <sup>(7)</sup>  | O <sup>(7)</sup> | O <sup>(7)</sup>  | - | -                 | - | -                 | -    |

| SPIx (x=1,2,3)                   | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| CAN                              | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| SDMMC1                           | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| SWPMI1                           | 0                | 0                | 0                    | 0                      | -                | 0                 | -                | -                 | - | -                 | - | -                 | -    |

| SAlx (x=1)                       | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| ADCx (x=1)                       | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| DACx (x=1,2)                     | 0                | 0                | 0                    | 0                      | 0                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| VREFBUF                          | 0                | 0                | 0                    | 0                      | 0                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| OPAMPx (x=1)                     | 0                | 0                | 0                    | 0                      | 0                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| COMPx (x=1,2)                    | 0                | 0                | 0                    | 0                      | 0                | 0                 | 0                | 0                 | - | -                 | - | -                 | -    |

| Temperature sensor               | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| Timers (TIMx)                    | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| Low-power timer 1<br>(LPTIM1)    | 0                | 0                | 0                    | 0                      | 0                | 0                 | 0                | 0                 | - | -                 | - | -                 | -    |

| Low-power timer 2<br>(LPTIM2)    | 0                | 0                | 0                    | 0                      | 0                | 0                 | -                | -                 | - | -                 | - | -                 | -    |

| Independent<br>watchdog (IWDG)   | 0                | 0                | 0                    | 0                      | 0                | 0                 | 0                | 0                 | 0 | 0                 | - | -                 | -    |

| Window watchdog<br>(WWDG)        | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| SysTick timer                    | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| Touch sensing controller (TSC)   | 0                | 0                | 0                    | 0                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

| Random number<br>generator (RNG) | O <sup>(8)</sup> | O <sup>(8)</sup> | -                    | -                      | -                | -                 | -                | -                 | - | -                 | - | -                 | -    |

### Table 4. Functionalities depending on the working mode<sup>(1)</sup> (continued)

|                      |     |       | -                    | -                      |      |                   | -   |                   |     |                   | -    |                   |      |

|----------------------|-----|-------|----------------------|------------------------|------|-------------------|-----|-------------------|-----|-------------------|------|-------------------|------|

|                      |     |       |                      |                        | Stop | o 0/1             | Sto | op 2              | Sta | ndby              | Shut | down              |      |

| Peripheral           | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | -    | Wakeup capability | -   | Wakeup capability | -   | Wakeup capability | -    | Wakeup capability | VBAT |

| CRC calculation unit | 0   | 0     | 0                    | 0                      | -    | -                 | -   | -                 | -   | -                 | -    | -                 | -    |

| GPIOs                | 0   | 0     | 0                    | 0                      | 0    | 0                 | 0   | 0                 | (9) | 5<br>pins<br>(10) | (11) | 5<br>pins<br>(10) | -    |

### Table 4. Functionalities depending on the working mode<sup>(1)</sup> (continued)

1. Legend: Y = Yes (Enable). O = Optional (Disable by default. Can be enabled by software). - = Not available.

2. The Flash can be configured in power-down mode. By default, it is not in power-down mode.

- 3. The SRAM clock can be gated on or off.

- 4. SRAM2 content is preserved when the bit RRS is set in PWR\_CR3 register.

- Some peripherals with wakeup from Stop capability can request HSI16 to be enabled. In this case, HSI16 is woken up by the peripheral, and only feeds the peripheral which requested it. HSI16 is automatically put off when the peripheral does not need it anymore.

- 6. UART and LPUART reception is functional in Stop mode, and generates a wakeup interrupt on Start, address match or received frame event.

- 7. I2C address detection is functional in Stop mode, and generates a wakeup interrupt in case of address match.

- 8. Voltage scaling Range 1 only.

- 9. I/Os can be configured with internal pull-up, pull-down or floating in Standby mode.

- 10. The I/Os with wakeup from Standby/Shutdown capability are: PA0, PC13, PE6, PA2, PC5.

- 11. I/Os can be configured with internal pull-up, pull-down or floating in Shutdown mode but the configuration is lost when exiting the Shutdown mode.

### 3.9.5 Reset mode

In order to improve the consumption under reset, the I/Os state under and after reset is "analog state" (the I/O schmitt trigger is disable). In addition, the internal reset pull-up is deactivated when the reset source is internal.

### 3.9.6 VBAT operation

The VBAT pin allows to power the device VBAT domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present. The VBAT pin supplies the RTC with LSE and the backup registers. Three anti-tamper detection pins are available in VBAT mode.

VBAT operation is automatically activated when V<sub>DD</sub> is not present.

An internal VBAT battery charging circuit is embedded and can be activated when  $\mathsf{V}_{\mathsf{DD}}$  is present.

*Note:* When the microcontroller is supplied from VBAT, external interrupts and RTC alarm/events do not exit it from VBAT operation.

DocID028800 Rev 1

### 3.10 Interconnect matrix

Several peripherals have direct connections between them. This allows autonomous communication between peripherals, saving CPU resources thus power supply consumption. In addition, these hardware connections allow fast and predictable latency.

Depending on peripherals, these interconnections can operate in Run, Sleep, low-power run and sleep, Stop 0, Stop 1 and Stop 2 modes.

| Interconnect source                                                                       | Interconnect<br>destination | Interconnect action                                                | Run | Sleep | Low-power run | Low-power sleep | Stop 0 / Stop 1 | Stop 2   |

|-------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------|-----|-------|---------------|-----------------|-----------------|----------|

|                                                                                           | TIMx                        | Timers synchronization or chaining                                 | Y   | Y     | Y             | Y               | -               | -        |

| TIMx                                                                                      | ADCx<br>DACx                | Conversion triggers                                                | Y   | Y     | Y             | Y               | -               | -        |

|                                                                                           | DMA                         | Memory to memory transfer trigger                                  | Y   | Υ     | Υ             | Y               | -               | -        |

|                                                                                           | COMPx                       | Comparator output blanking                                         | Y   | Y     | Υ             | Y               | -               | -        |

| TIM15/TIM16                                                                               | IRTIM                       | Infrared interface output generation                               | Y   | Y     | Υ             | Y               | -               | -        |

| COMPx                                                                                     | TIM1<br>TIM2                | Timer input channel, trigger, break from analog signals comparison | Y   | Y     | Y             | Y               | -               | -        |

|                                                                                           | LPTIMERx                    | Low-power timer triggered by analog signals comparison             | Y   | Y     | Y             | Y               | Y               | Y<br>(1) |

| ADCx                                                                                      | TIM1                        | Timer triggered by analog watchdog                                 | Y   | Y     | Υ             | Y               | -               | -        |

|                                                                                           | TIM16                       | Timer input channel from RTC events                                | Υ   | Υ     | Υ             | Y               | -               | -        |

| RTC                                                                                       | LPTIMERx                    | Low-power timer triggered by RTC alarms or tampers                 | Y   | Y     | Y             | Y               | Y               | Y<br>(1) |

| All clocks sources (internal and external)                                                | TIM2<br>TIM15, 16           | Clock source used as input channel for RC measurement and trimming | Y   | Y     | Y             | Y               | -               | -        |

| CSS<br>CPU (hard fault)<br>RAM (parity error)<br>Flash memory (ECC error)<br>COMPx<br>PVD | TIM1<br>TIM15,16            | Timer break                                                        | Y   | Y     | Y             | Y               | _               | -        |

Table 5. STM32L431xx peripherals interconnect matrix

### 3.22 Timers and watchdogs

The STM32L431xx includes one advanced control timers, up to five general-purpose timers, two basic timers, two low-power timers, two watchdog timers and a SysTick timer. The table below compares the features of the advanced control, general purpose and basic timers.

| Timer type          | Timer      | Counter resolution | Counter<br>type      | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>outputs |  |  |  |  |  |

|---------------------|------------|--------------------|----------------------|---------------------------------------|------------------------------|---------------------------------|--------------------------|--|--|--|--|--|

| Advanced control    | TIM1       | 16-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | 3                        |  |  |  |  |  |

| General-<br>purpose | TIM2       | 32-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                       |  |  |  |  |  |

| General-<br>purpose | TIM15      | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 2                               | 1                        |  |  |  |  |  |

| General-<br>purpose | TIM16      | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 1                               | 1                        |  |  |  |  |  |

| Basic               | TIM6, TIM7 | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                       |  |  |  |  |  |

Table 9. Timer feature comparison

### 3.22.1 Advanced-control timer (TIM1)

The advanced-control timer can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as complete general-purpose timers. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

Many features are shared with those of the general-purpose TIMx timers (described in *Section 3.22.2*) using the same architecture, so the advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

### 3.23 Real-time clock (RTC) and backup registers

The RTC is an independent BCD timer/counter. It supports the following features:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format.

- Automatic correction for 28, 29 (leap year), 30, and 31 days of the month.

- Two programmable alarms.

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 0.95 ppm resolution, to compensate for quartz crystal inaccuracy.

- Three anti-tamper detection pins with programmable filter.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event, or by a switch to VBAT mode.

- 17-bit auto-reload wakeup timer (WUT) for periodic events with programmable resolution and period.

The RTC and the 32 backup registers are supplied through a switch that takes power either from the  $V_{DD}$  supply when present or from the VBAT pin.

The backup registers are 32-bit registers used to store 128 bytes of user application data when VDD power is not present. They are not reset by a system or power reset, or when the device wakes up from Standby or Shutdown mode.

The RTC clock sources can be:

- A 32.768 kHz external crystal (LSE)

- An external resonator or oscillator (LSE)

- The internal low power RC oscillator (LSI, with typical frequency of 32 kHz)

- The high-speed external clock (HSE) divided by 32.

The RTC is functional in VBAT mode and in all low-power modes when it is clocked by the LSE. When clocked by the LSI, the RTC is not functional in VBAT mode, but is functional in all low-power modes except Shutdown mode.

All RTC events (Alarm, WakeUp Timer, Timestamp or Tamper) can generate an interrupt and wakeup the device from the low-power modes.

# 3.26 Low-power universal asynchronous receiver transmitter (LPUART)

The device embeds one Low-Power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock, and can wakeup the system from Stop mode using baudrates up to 220 Kbaud. The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

|                 |        |                 | Pi      | n Nu    | mbe    | ər      |         |          |                                          | -        | 0             |       | Pin function                                                                                                                      | IS                                                  |

|-----------------|--------|-----------------|---------|---------|--------|---------|---------|----------|------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| <b>UFQFPN32</b> | LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                               | Additional functions                                |

| 8               | 12     | 12              | E5      | F6      | 16     | F3      | 25      | K3       | PA2                                      | I/O      | FT_a          | -     | TIM2_CH3, USART2_TX,<br>LPUART1_TX,<br>QUADSPI_BK1_NCS,<br>COMP2_OUT,<br>TIM15_CH1, EVENTOUT                                      | COMP2_INM,<br>ADC1_IN7,<br>WKUP4,<br>LSCO           |

| 9               | 13     | 13              | E4      | G6      | 17     | G3      | 26      | L3       | PA3                                      | I/O      | TT_a          | -     | TIM2_CH4, USART2_RX,<br>LPUART1_RX,<br>QUADSPI_CLK,<br>SAI1_MCLK_A,<br>TIM15_CH2, EVENTOUT                                        | OPAMP1_<br>VOUT,<br>COMP2_INP,<br>ADC1_IN8          |

| -               | -      | -               | -       | H8      | 18     | C2      | 27      | E3       | VSS                                      | S        | -             | -     | -                                                                                                                                 | -                                                   |

| -               | -      | -               | -       | H7      | 19     | D2      | 28      | H3       | VDD                                      | S        | -             | -     | -                                                                                                                                 | -                                                   |

| 10              | 14     | 14              | G6      | E5      | 20     | H3      | 29      | М3       | PA4                                      | I/O      | TT_a          | -     | SPI1_NSS, SPI3_NSS,<br>USART2_CK,<br>SAI1_FS_B,<br>LPTIM2_OUT,<br>EVENTOUT                                                        | COMP1_INM,<br>COMP2_INM,<br>ADC1_IN9,<br>DAC1_OUT1  |

| 11              | 15     | 15              | F5      | F5      | 21     | F4      | 30      | K4       | PA5                                      | I/O      | TT_a          | -     | TIM2_CH1, TIM2_ETR,<br>SPI1_SCK,<br>LPTIM2_ETR,<br>EVENTOUT                                                                       | COMP1_INM,<br>COMP2_INM,<br>ADC1_IN10,<br>DAC1_OUT2 |

| 12              | 16     | 16              | F4      | G5      | 22     | G4      | 31      | L4       | PA6                                      | I/O      | FT_a          | -     | TIM1_BKIN, SPI1_MISO,<br>COMP1_OUT,<br>USART3_CTS,<br>LPUART1_CTS,<br>QUADSPI_BK1_IO3,<br>TIM1_BKIN_COMP2,<br>TIM16_CH1, EVENTOUT | ADC1_IN11                                           |

| 13              | 17     | 17              | F3      | H6      | 23     | H4      | 32      | M4       | PA7                                      | I/O      | FT_fa         | -     | TIM1_CH1N, I2C3_SCL,<br>SPI1_MOSI,<br>QUADSPI_BK1_IO2,<br>COMP2_OUT,<br>EVENTOUT                                                  | ADC1_IN12                                           |

| -               | -      | -               | -       | D4      | 24     | H5      | 33      | K5       | PC4                                      | I/O      | FT_a          | -     | USART3_TX,<br>EVENTOUT                                                                                                            | COMP1_INM,<br>ADC1_IN13                             |

| -               | -      | -               | -       | E4      | 25     | H6      | 34      | L5       | PC5                                      | I/O      | FT_a          | -     | USART3_RX,<br>EVENTOUT                                                                                                            | COMP1_INP,<br>ADC1_IN14,<br>WKUP5                   |

Table 14. STM32L431xx pin definitions (continued)

| S   |

|-----|

|     |

| _   |

|     |

| <   |

|     |

| ω   |

| Ň   |

|     |

|     |

| 4   |

| 7.7 |

| ω   |

| _   |

| _   |

| ~   |

| ~   |

| ~   |

| ~   |

|     |

Pinouts and pin description

|        |      | Tabl              | e 15. Alternate      | function AF0 t | o AF7 (for AF8      | 8 to AF15 see <mark>Ta</mark> | <mark>ble 16</mark> ) (contir | nued)     |                              |

|--------|------|-------------------|----------------------|----------------|---------------------|-------------------------------|-------------------------------|-----------|------------------------------|

|        |      | AF0               | AF1                  | AF2            | AF3                 | AF4                           | AF5                           | AF6       | AF7                          |

| Po     | ort  | SYS_AF            | TIM1/TIM2/<br>LPTIM1 | TIM1/TIM2      | USART2              | 12C1/12C2/12C3                | SPI1/SPI2                     | SPI3      | USART1/<br>USART2/<br>USART3 |

|        | PB0  | -                 | TIM1_CH2N            | -              | -                   | -                             | SPI1_NSS                      | -         | USART3_CK                    |

|        | PB1  | -                 | TIM1_CH3N            | -              | -                   | -                             | -                             | -         | USART3_RTS_<br>DE            |

| Port B | PB2  | RTC_OUT           | LPTIM1_OUT           | -              | -                   | I2C3_SMBA                     | -                             | -         | -                            |

|        | PB3  | JTDO-<br>TRACESWO | TIM2_CH2             | -              | -                   | -                             | SPI1_SCK                      | SPI3_SCK  | USART1_RTS_<br>DE            |

|        | PB4  | NJTRST            | -                    | -              | -                   | I2C3_SDA                      | SPI1_MISO                     | SPI3_MISO | USART1_CTS                   |

|        | PB5  | -                 | LPTIM1_IN1           | -              | -                   | I2C1_SMBA                     | SPI1_MOSI                     | SPI3_MOSI | USART1_CK                    |

|        | PB6  | -                 | LPTIM1_ETR           | -              | -                   | I2C1_SCL                      | -                             | -         | USART1_TX                    |

|        | PB7  | -                 | LPTIM1_IN2           | -              | -                   | I2C1_SDA                      | -                             | -         | USART1_RX                    |

|        | PB8  | -                 | -                    | -              | -                   | I2C1_SCL                      | -                             | -         | -                            |

|        | PB9  | -                 | IR_OUT               | -              | -                   | I2C1_SDA                      | SPI2_NSS                      | -         | -                            |

|        | PB10 | -                 | TIM2_CH3             | -              | -                   | I2C2_SCL                      | SPI2_SCK                      | -         | USART3_TX                    |

| Port B | PB11 | -                 | TIM2_CH4             | -              | -                   | I2C2_SDA                      | -                             | -         | USART3_RX                    |

|        | PB12 | -                 | TIM1_BKIN            | -              | TIM1_BKIN_<br>COMP2 | I2C2_SMBA                     | SPI2_NSS                      | -         | USART3_CK                    |

|        | PB13 | -                 | TIM1_CH1N            | -              | -                   | I2C2_SCL                      | SPI2_SCK                      | -         | USART3_CTS                   |

|        | PB14 | -                 | TIM1_CH2N            | -              | -                   | I2C2_SDA                      | SPI2_MISO                     | -         | USART3_RTS_<br>DE            |

|        | PB15 | RTC_REFIN         | TIM1_CH3N            | -              | -                   | -                             | SPI2_MOSI                     | -         | -                            |

DocID028800 Rev 1

65/200

5

| Bus  | Boundary address          | Size(bytes) | Peripheral |

|------|---------------------------|-------------|------------|

|      | 0x4001 3000 - 0x4001 33FF | 1 KB        | SPI1       |

|      | 0x4001 2C00 - 0x4001 2FFF | 1 KB        | TIM1       |

|      | 0x4001 2800 - 0x4001 2BFF | 1 KB        | SDMMC1     |

|      | 0x4001 2000 - 0x4001 27FF | 2 KB        | Reserved   |

| 4002 | 0x4001 1C00 - 0x4001 1FFF | 1 KB        | FIREWALL   |

| APB2 | 0x4001 0800- 0x4001 1BFF  | 5 KB        | Reserved   |

|      | 0x4001 0400 - 0x4001 07FF | 1 KB        | EXTI       |

|      | 0x4001 0200 - 0x4001 03FF |             | COMP       |

|      | 0x4001 0030 - 0x4001 01FF | 1 KB        | VREFBUF    |

|      | 0x4001 0000 - 0x4001 002F |             | SYSCFG     |

|      | 0x4000 9800 - 0x4000 FFFF | 26 KB       | Reserved   |

|      | 0x4000 9400 - 0x4000 97FF | 1 KB        | LPTIM2     |

|      | 0x4000 8C00 - 0x4000 93FF | 2 KB        | Reserved   |

|      | 0x4000 8800 - 0x4000 8BFF | 1 KB        | SWPMI1     |

|      | 0x4000 8400 - 0x4000 87FF | 1 KB        | Reserved   |

|      | 0x4000 8000 - 0x4000 83FF | 1 KB        | LPUART1    |

|      | 0x4000 7C00 - 0x4000 7FFF | 1 KB        | LPTIM1     |

|      | 0x4000 7800 - 0x4000 7BFF | 1 KB        | OPAMP      |

|      | 0x4000 7400 - 0x4000 77FF | 1 KB        | DAC        |

|      | 0x4000 7000 - 0x4000 73FF | 1 KB        | PWR        |

|      | 0x4000 6800 - 0x4000 6FFF | 2 KB        | Reserved   |

| APB1 | 0x4000 6400 - 0x4000 67FF | 1 KB        | CAN1       |

| APDI | 0x4000 6000 - 0x4000 63FF | 1 KB        | CRS        |

|      | 0x4000 5C00- 0x4000 5FFF  | 1 KB        | I2C3       |

|      | 0x4000 5800 - 0x4000 5BFF | 1 KB        | I2C2       |

|      | 0x4000 5400 - 0x4000 57FF | 1 KB        | I2C1       |

|      | 0x4000 4C00 - 0x4000 53FF | 2 KB        | Reserved   |

|      | 0x4000 4800 - 0x4000 4BFF | 1 KB        | USART3     |

|      | 0x4000 4400 - 0x4000 47FF | 1 KB        | USART2     |

|      | 0x4000 4000 - 0x4000 43FF | 1 KB        | Reserved   |

|      | 0x4000 3C00 - 0x4000 3FFF | 1 KB        | SPI3       |

|      | 0x4000 3800 - 0x4000 3BFF | 1 KB        | SPI2       |

|      | 0x4000 3400 - 0x4000 37FF | 1 KB        | Reserved   |

|      | 0x4000 3000 - 0x4000 33FF | 1 KB        | IWDG       |

| Table 17. STM32L431xx memory map and peripheral register boundary addresses | Table 17. STM32L | .431xx memory ma | p and p | peripheral re | eqister b | oundary | addresses |

|-----------------------------------------------------------------------------|------------------|------------------|---------|---------------|-----------|---------|-----------|

|-----------------------------------------------------------------------------|------------------|------------------|---------|---------------|-----------|---------|-----------|

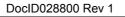

Figure 19. V<sub>REFINT</sub> versus temperature

### 6.3.8 Internal clock source characteristics

The parameters given in *Table 47* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*. The provided curves are characterization results, not tested in production.

### High-speed internal (HSI16) RC oscillator

| Symbol                                   | Parameter                                                | Conditions                                    | Min   | Тур | Мах   | Unit |

|------------------------------------------|----------------------------------------------------------|-----------------------------------------------|-------|-----|-------|------|

| f <sub>HSI16</sub>                       | HSI16 Frequency                                          | V <sub>DD</sub> =3.0 V, T <sub>A</sub> =30 °C | 15.88 | -   | 16.08 | MHz  |

| TRIM                                     | HSI16 user trimming step                                 | Trimming code is not a multiple of 64         | 0.2   | 0.3 | 0.4   | %    |

|                                          |                                                          | Trimming code is a multiple of 64             | -4    | -6  | -8    | 70   |

| DuCy(HSI16) <sup>(2)</sup>               | Duty Cycle                                               | -                                             | 45    | -   | 55    | %    |

| A_ (HSI16)                               | HSI16 oscillator frequency                               | T <sub>A</sub> = 0 to 85 °C                   | -1    | -   | 1     | %    |

| ∆ <sub>Temp</sub> (HSI16)                | drift over temperature                                   | T <sub>A</sub> = -40 to 125 °C                | -2    | -   | 1.5   | %    |

| ∆ <sub>VDD</sub> (HSI16)                 | HSI16 oscillator frequency<br>drift over V <sub>DD</sub> | V <sub>DD</sub> =1.62 V to 3.6 V              | -0.1  | -   | 0.05  | %    |

| t <sub>su</sub> (HSI16) <sup>(2)</sup>   | HSI16 oscillator start-up time                           | -                                             | -     | 0.8 | 1.2   | μs   |

| t <sub>stab</sub> (HSI16) <sup>(2)</sup> | HSI16 oscillator<br>stabilization time                   | -                                             | -     | 3   | 5     | μs   |

| I <sub>DD</sub> (HSI16) <sup>(2)</sup>   | HSI16 oscillator power<br>consumption                    | -                                             | -     | 155 | 190   | μA   |

| Table 47. HSI16 os | cillator characteristics <sup>(1)</sup> | ) |

|--------------------|-----------------------------------------|---|

|--------------------|-----------------------------------------|---|

1. Guaranteed by characterization results.

2. Guaranteed by design.

| Symbol                    | Parameter                                        | Conditions                                        | Min                                                             | Тур | Мах     | Unit               |

|---------------------------|--------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------|-----|---------|--------------------|

|                           | <b>T</b> .:                                      | CKMODE = 00                                       | 1.5                                                             | 2   | 2.5     |                    |

|                           | Trigger conversion<br>latency Regular and        | CKMODE = 01                                       | -                                                               | -   | 2.0     | 1 /5               |

| t <sub>LATR</sub>         | injected channels without conversion abort       | CKMODE = 10                                       | -                                                               | -   | 2.25    | 1/f <sub>ADC</sub> |

|                           |                                                  | CKMODE = 11                                       | -                                                               | -   | 2.125   |                    |

|                           | Trigger conversion                               | CKMODE = 00                                       | 2.5                                                             | 3   | 3.5     |                    |

| +                         | Trigger conversion<br>latency Injected channels  | CKMODE = 01                                       | -                                                               | -   | 3.0     | 1 /F               |

| <sup>t</sup> LATRINJ      | aborting a regular conversion                    | CKMODE = 10                                       | -                                                               | -   | 3.25    | 1/f <sub>ADC</sub> |

|                           |                                                  | CKMODE = 11                                       | -                                                               | -   | 3.125   |                    |

| +                         | Sompling time                                    | f <sub>ADC</sub> = 80 MHz                         | 0.03125                                                         | -   | 8.00625 | μs                 |

| t <sub>s</sub>            | Sampling time                                    | -                                                 | 2.5                                                             | -   | 640.5   | 1/f <sub>ADC</sub> |

| t <sub>ADCVREG_STUP</sub> | ADC voltage regulator start-up time              | -                                                 | -                                                               | -   | 20      | μs                 |

|                           | Total conversion time                            | f <sub>ADC</sub> = 80 MHz<br>Resolution = 12 bits | 0.1875                                                          | -   | 8.1625  | μs                 |

| t <sub>CONV</sub>         | (including sampling time)                        | Resolution = 12 bits                              | ts + 12.5 cycles for<br>successive approximation<br>= 15 to 653 |     |         | 1/f <sub>ADC</sub> |

|                           |                                                  | fs = 5 Msps                                       | -                                                               | 730 | 830     |                    |

| I <sub>DDA</sub> (ADC)    | ADC consumption from the V <sub>DDA</sub> supply | fs = 1 Msps                                       | -                                                               | 160 | 220     | μA                 |

|                           |                                                  | fs = 10 ksps                                      | -                                                               | 16  | 50      |                    |

|                           | ADC consumption from                             | fs = 5 Msps                                       | -                                                               | 130 | 160     |                    |

| I <sub>DDV_S</sub> (ADC)  | the V <sub>REF+</sub> single ended               | fs = 1 Msps                                       | -                                                               | 30  | 40      | μA                 |

|                           | mode                                             | fs = 10 ksps                                      | -                                                               | 0.6 | 2       |                    |

|                           | ADC consumption from                             | fs = 5 Msps                                       | -                                                               | 260 | 310     |                    |

| I <sub>DDV_D</sub> (ADC)  | the V <sub>REF+</sub> differential               | fs = 1 Msps                                       | -                                                               | 60  | 70      | μA                 |

|                           | mode                                             | fs = 10 ksps                                      | -                                                               | 1.3 | 3       |                    |

Table 64. ADC characteristics<sup>(1) (2)</sup> (continued)

1. Guaranteed by design

2. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V.

V<sub>REF+</sub> can be internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> can be internally connected to V<sub>SSA</sub>, depending on the package. Refer to Section 4: Pinouts and pin description for further details.

| Symbol                 | Parameter                                                                                                                                                                |                                                                     | onditions                                                                | ,<br>Min | Тур                                | Max                                | Unit |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------|----------|------------------------------------|------------------------------------|------|

|                        | Sampling time in sample<br>and hold mode (code<br>transition between the<br>lowest input code and the<br>highest input code when<br>DACOUT reaches final<br>value ±1LSB) | DAC_OUT                                                             | DAC output buffer<br>ON, C <sub>SH</sub> = 100 nF                        | -        | 0.7                                | 3.5                                | me   |

|                        |                                                                                                                                                                          | pin connected                                                       | DAC output buffer<br>OFF, C <sub>SH</sub> = 100 nF                       | -        | 10.5                               | 18                                 | ms   |

| t <sub>SAMP</sub>      |                                                                                                                                                                          | DAC_OUT<br>pin not<br>connected<br>(internal<br>connection<br>only) | DAC output buffer<br>OFF                                                 | -        | 2                                  | 3.5                                | μs   |

| I <sub>leak</sub>      | Output leakage current                                                                                                                                                   | Sample and ho DAC_OUT pin                                           |                                                                          | -        | -                                  | _(3)                               | nA   |

| Cl <sub>int</sub>      | Internal sample and hold capacitor                                                                                                                                       |                                                                     | -                                                                        | 5.2      | 7                                  | 8.8                                | pF   |

| t <sub>TRIM</sub>      | Middle code offset trim time                                                                                                                                             | DAC output bu                                                       | ffer ON                                                                  | 50       | -                                  | -                                  | μs   |

| V.                     | Middle code offset for 1                                                                                                                                                 | V <sub>REF+</sub> = 3.6 V                                           | -                                                                        | 1500     | -                                  | μV                                 |      |

| V <sub>offset</sub>    | trim code step                                                                                                                                                           | V <sub>REF+</sub> = 1.8 V                                           | <sub>F+</sub> = 1.8 V                                                    |          | 750                                | -                                  | μv   |

|                        |                                                                                                                                                                          | DAC output                                                          | No load, middle<br>code (0x800)                                          | -        | 315                                | 500                                |      |

|                        |                                                                                                                                                                          | buffer ON                                                           | No load, worst code<br>(0xF1C)                                           | -        | 450                                | 670                                |      |

| I <sub>DDA</sub> (DAC) | DAC consumption from<br>V <sub>DDA</sub>                                                                                                                                 | DAC output No load, middle                                          |                                                                          | -        | 0.2                                | μA                                 |      |

|                        |                                                                                                                                                                          | Sample and hold mode, C <sub>SH</sub> =<br>100 nF                   |                                                                          | -        | 315 x<br>Ton/(Ton<br>+Toff)<br>(4) | 670 x<br>Ton/(Ton<br>+Toff)<br>(4) |      |

|                        |                                                                                                                                                                          | DAC output                                                          | No load, middle<br>code (0x800)                                          | -        | 185                                | 240                                |      |

|                        | DAC consumption from<br>V <sub>REF+</sub>                                                                                                                                | buffer ON                                                           | No load, worst code<br>(0xF1C)                                           | -        | 340                                | 400                                |      |

| I <sub>DDV</sub> (DAC) |                                                                                                                                                                          | DAC output<br>buffer OFF                                            | No load, middle<br>code (0x800)                                          | -        | 155                                | 205                                |      |

|                        |                                                                                                                                                                          |                                                                     | Sample and hold mode, buffer ON,<br>C <sub>SH</sub> = 100 nF, worst case |          | 185 x<br>Ton/(Ton<br>+Toff)<br>(4) | 400 x<br>Ton/(Ton<br>+Toff)<br>(4) | μA   |

|                        |                                                                                                                                                                          |                                                                     | old mode, buffer OFF,<br>worst case                                      | _        | 155 x<br>Ton/(Ton<br>+Toff)<br>(4) | 205 x<br>Ton/(Ton<br>+Toff)<br>(4) |      |

Table 70. DAC characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design.

2. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

| Symbol                         | Parameter             | Conditions                 | Min | Тур | Мах | Unit |

|--------------------------------|-----------------------|----------------------------|-----|-----|-----|------|

|                                | VREFBUF               | I <sub>load</sub> = 0 μA   | -   | 16  | 25  |      |

| I <sub>DDA</sub> (VREF<br>BUF) | consumption           | I <sub>load</sub> = 500 μA | -   | 18  | 30  | μA   |

| ,                              | from V <sub>DDA</sub> | I <sub>load</sub> = 4 mA   | -   | 35  | 50  |      |

Table 72. VREFBUF characteristics<sup>(1)</sup> (continued)

1. Guaranteed by design, unless otherwise specified.

2. In degraded mode, the voltage reference buffer can not maintain accurately the output voltage which will follow (V<sub>DDA</sub> - drop voltage).

3. Guaranteed by test in production.

4. The capacitive load must include a 100 nF capacitor in order to cut-off the high frequency noise.

5. To correctly control the VREFBUF inrush current during start-up phase and scaling change, the  $V_{DDA}$  voltage should be in the range [2.4 V to 3.6 V] and [2.8 V to 3.6 V] respectively for  $V_{RS}$  = 0 and  $V_{RS}$  = 1.

| Cumhal |        | millimeters |        |        | inches <sup>(1)</sup> |        |  |

|--------|--------|-------------|--------|--------|-----------------------|--------|--|

| Symbol | Min    | Тур         | Мах    | Min    | Тур                   | Мах    |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |  |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |  |

| D      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |  |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |  |

| D3     | -      | 12.000      | -      | -      | 0.4724                | -      |  |

| E      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |  |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |  |

| E3     | -      | 12.000      | -      | -      | 0.4724                | -      |  |

| е      | -      | 0.500       | -      | -      | 0.0197                | -      |  |

| L      | 0.450  | 0.600       | 0.750  | 0.0177 | 0.0236                | 0.0295 |  |

| L1     | -      | 1.000       | -      | -      | 0.0394                | -      |  |

| k      | 0.0°   | 3.5°        | 7.0°   | 0.0°   | 3.5°                  | 7.0°   |  |

| ссс    | -      | -           | 0.080  | -      | -                     | 0.0031 |  |

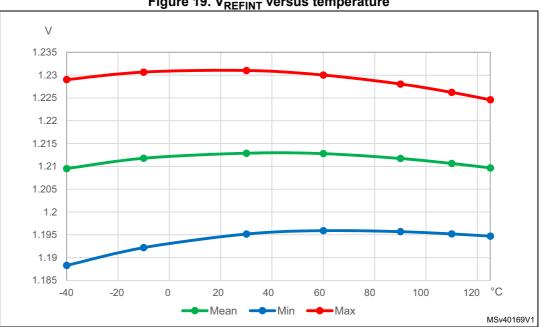

| Table 89. LQPF100 - 100-pin, 14 x 14 mm low-profile quad flat package |

|-----------------------------------------------------------------------|

| mechanical data (continued)                                           |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

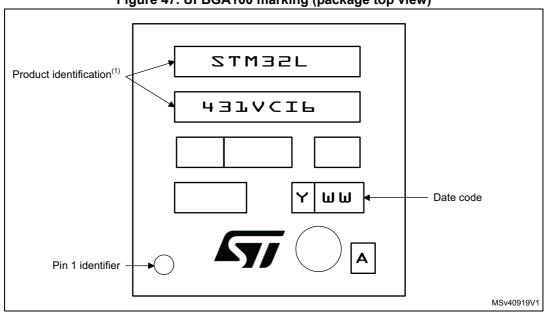

Figure 47. UFBGA100 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

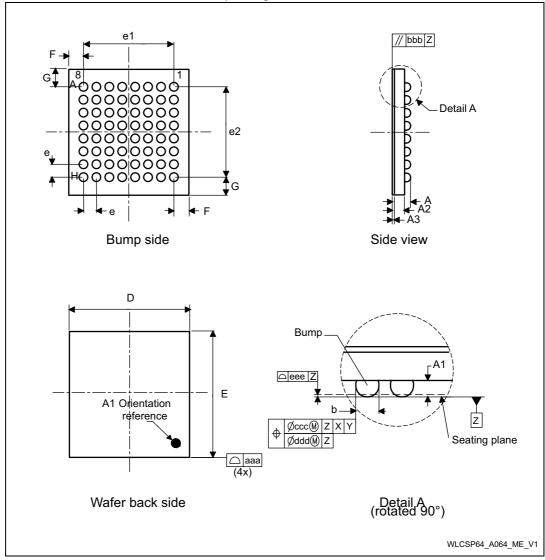

### 7.5 WLCSP64 package information

Figure 54. WLCSP64 - 64-ball, 3.141 x 3.127 mm, 0.35 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

## Table 95. WLCSP64 - 64-ball, 3.141 x 3.127 mm, 0.35 mm pitch wafer level chip scale package mechanical data

| Symbol            | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|-------------------|-------------|-------|-------|-----------------------|--------|--------|

| Symbol            | Min         | Тур   | Max   | Min                   | Тур    | Мах    |

| А                 | 0.516       | 0.546 | 0.576 | 0.0203                | 0.0215 | 0.0227 |

| A1                | -           | 0.166 | -     | -                     | 0.0065 | -      |

| A2                | -           | 0.380 | -     | -                     | 0.0150 | -      |

| A3 <sup>(2)</sup> | -           | 0.025 | -     | -                     | 0.0010 | -      |

|                  | package mechanical data (continued) |             |       |                       |        |        |

|------------------|-------------------------------------|-------------|-------|-----------------------|--------|--------|

| Symbol           |                                     | millimeters |       | inches <sup>(1)</sup> |        |        |

| Symbol           | Min                                 | Тур         | Мах   | Min                   | Тур    | Max    |

| b <sup>(3)</sup> | 0.190                               | 0.220       | 0.250 | 0.0075                | 0.0087 | 0.0098 |

| D                | 3.106                               | 3.141       | 3.176 | 0.1223                | 0.1237 | 0.1250 |

| E                | 3.092                               | 3.127       | 3.162 | 0.1217                | 0.1231 | 0.1245 |

| е                | -                                   | 0.350       | -     | -                     | 0.0138 | -      |

| e1               | -                                   | 2.450       | -     | -                     | 0.0965 | -      |

| e2               | -                                   | 2.450       | -     | -                     | 0.0965 | -      |

| F                | -                                   | 0.3455      | -     | -                     | 0.0136 | -      |

| G                | -                                   | 0.3385      | -     | -                     | 0.0133 | -      |

| aaa              | -                                   | -           | 0.100 | -                     | -      | 0.0039 |

| bbb              | -                                   | -           | 0.100 | -                     | -      | 0.0039 |

| ссс              | -                                   | -           | 0.100 | -                     | -      | 0.0039 |

| ddd              | -                                   | -           | 0.050 | -                     | -      | 0.0020 |

| eee              | -                                   | -           | 0.050 | -                     | -      | 0.0020 |

## Table 95. WLCSP64 - 64-ball, 3.141 x 3.127 mm, 0.35 mm pitch wafer level chip scale package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

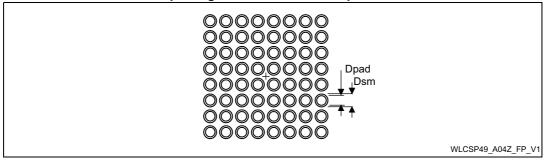

## Figure 55. WLCSP64 - 64-ball, 3.141 x 3.127 mm, 0.35 mm pitch wafer level chip scale package recommended footprint

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.35 mm                                                          |

| Dpad              | 0.210 mm                                                         |

| Dsm               | 0.275 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.235 mm                                                         |

| Stencil thickness | 0.100 mm                                                         |

DocID028800 Rev 1

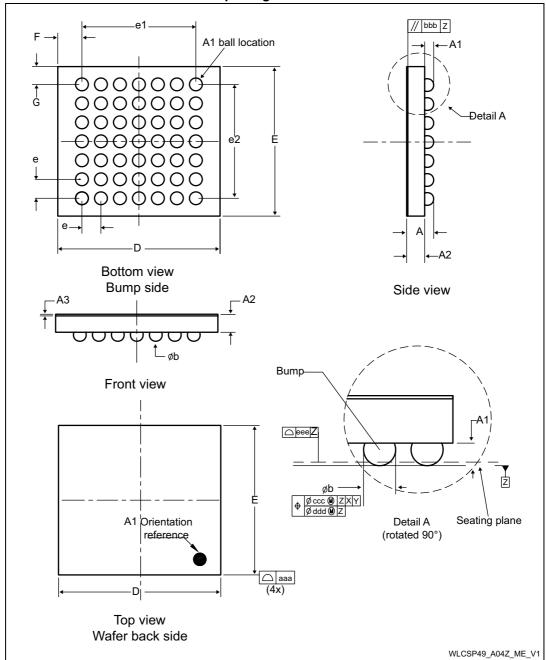

### 7.6 WLCSP49 package information

Figure 57. WLCSP49 - 49-ball, 3.141 x 3.127 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

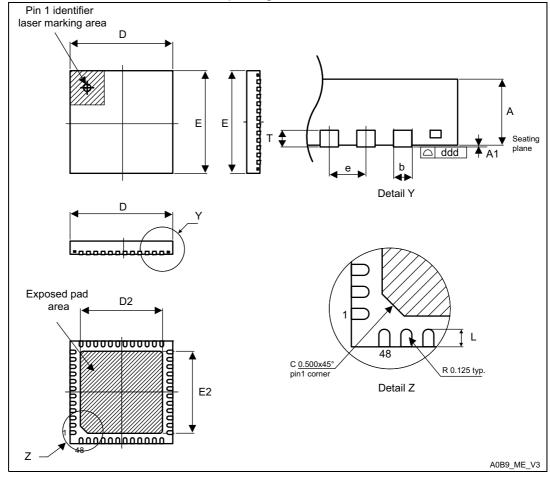

### 7.8 UFQFPN48 package information

Figure 63. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.