Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 20000                      |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 80MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, SWPMI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                     |

| Number of I/O              | 39                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                              |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-LQFP                                                                   |

| Supplier Device Package    | 48-LQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l431cct6     |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.10 Interconnect matrix

Several peripherals have direct connections between them. This allows autonomous communication between peripherals, saving CPU resources thus power supply consumption. In addition, these hardware connections allow fast and predictable latency.

Depending on peripherals, these interconnections can operate in Run, Sleep, low-power run and sleep, Stop 0, Stop 1 and Stop 2 modes.

| Interconnect source                                                                       | Interconnect<br>destination | Interconnect action                                                | Run | Sleep | Low-power run | Low-power sleep | Stop 0 / Stop 1 | Stop 2   |

|-------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------------|-----|-------|---------------|-----------------|-----------------|----------|

|                                                                                           | TIMx                        | Timers synchronization or chaining                                 | Y   | Y     | Y             | Y               | -               | -        |

| TIMx                                                                                      | ADCx<br>DACx                | Conversion triggers                                                | Y   | Y     | Y             | Y               | -               | -        |

|                                                                                           | DMA                         | Memory to memory transfer trigger                                  | Y   | Y     | Υ             | Y               | -               | -        |

|                                                                                           | COMPx                       | Comparator output blanking                                         | Y   | Y     | Y             | Y               | -               | -        |

| TIM15/TIM16                                                                               | IRTIM                       | Infrared interface output generation                               | Y   | Y     | Υ             | Y               | -               | -        |

| COMPx                                                                                     | TIM1<br>TIM2                | Timer input channel, trigger, break from analog signals comparison |     |       | Y             | Y               | -               | -        |

|                                                                                           | LPTIMERx                    | Low-power timer triggered by analog signals comparison             |     |       | Y             | Y               | Y               | Y<br>(1) |

| ADCx                                                                                      | TIM1                        | Timer triggered by analog watchdog                                 | Y   | Y     | Υ             | Y               | -               | -        |

|                                                                                           | TIM16                       | Timer input channel from RTC events                                | Υ   | Υ     | Υ             | Y               | -               | -        |

| RTC                                                                                       | LPTIMERx                    | Low-power timer triggered by RTC alarms or tampers                 | Y   | Y     | Y             | Y               | Y               | Y<br>(1) |

| All clocks sources (internal and external)                                                | TIM2<br>TIM15, 16           | Clock source used as input channel for RC measurement and trimming | Y   | Y     | Y             | Y               | -               | -        |

| CSS<br>CPU (hard fault)<br>RAM (parity error)<br>Flash memory (ECC error)<br>COMPx<br>PVD | TIM1<br>TIM15,16            | Timer break                                                        | Y   | Y     | Y             | Y               | _               | -        |

Table 5. STM32L431xx peripherals interconnect matrix

# 3.19 Operational amplifier (OPAMP)

The STM32L431xx embeds one operational amplifier with external or internal follower routing and PGA capability.

The operational amplifier features:

- Low input bias current

- Low offset voltage

- Low-power mode

- Rail-to-rail input

# 3.20 Touch sensing controller (TSC)

The touch sensing controller provides a simple solution for adding capacitive sensing functionality to any application. Capacitive sensing technology is able to detect finger presence near an electrode which is protected from direct touch by a dielectric (glass, plastic, ...). The capacitive variation introduced by the finger (or any conductive object) is measured using a proven implementation based on a surface charge transfer acquisition principle.

The touch sensing controller is fully supported by the STMTouch touch sensing firmware library which is free to use and allows touch sensing functionality to be implemented reliably in the end application.

The main features of the touch sensing controller are the following:

- Proven and robust surface charge transfer acquisition principle

- Supports up to 21 capacitive sensing channels

- Up to 3 capacitive sensing channels can be acquired in parallel offering a very good response time

- Spread spectrum feature to improve system robustness in noisy environments

- Full hardware management of the charge transfer acquisition sequence

- Programmable charge transfer frequency

- Programmable sampling capacitor I/O pin

- Programmable channel I/O pin

- Programmable max count value to avoid long acquisition when a channel is faulty

- Dedicated end of acquisition and max count error flags with interrupt capability

- One sampling capacitor for up to 3 capacitive sensing channels to reduce the system components

- Compatible with proximity, touchkey, linear and rotary touch sensor implementation

- Designed to operate with STMTouch touch sensing firmware library

# 3.21 Random number generator (RNG)

All devices embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

DocID028800 Rev 1

*Note:* The number of capacitive sensing channels is dependent on the size of the packages and subject to I/O availability.

- Transmission

- Three transmit mailboxes

- Configurable transmit priority

- Reception

- Two receive FIFOs with three stages

- 14 Scalable filter banks

- Identifier list feature

- Configurable FIFO overrun

- Time-triggered communication option

- Disable automatic retransmission mode

- 16-bit free running timer

- Time Stamp sent in last two data bytes

- Management

- Maskable interrupts

- Software-efficient mailbox mapping at a unique address space

# 3.31 Secure digital input/output and MultiMediaCards Interface (SDMMC)

The card host interface (SDMMC) provides an interface between the APB peripheral bus and MultiMediaCards (MMCs), SD memory cards and SDIO cards.

The SDMMC features include the following:

- Full compliance with MultiMediaCard System Specification Version 4.2. Card support for three different databus modes: 1-bit (default), 4-bit and 8-bit

- Full compatibility with previous versions of MultiMediaCards (forward compatibility)

- Full compliance with SD Memory Card Specifications Version 2.0

- Full compliance with SD I/O Card Specification Version 2.0: card support for two different databus modes: 1-bit (default) and 4-bit

- Data transfer up to 48 MHz for the 8 bit mode

- Data write and read with DMA capability

# 3.32 Clock recovery system (CRS)

The STM32L431xx devices embed a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

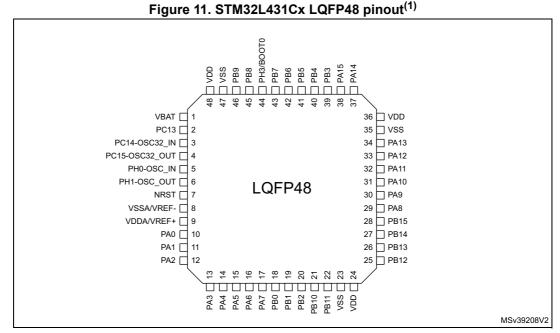

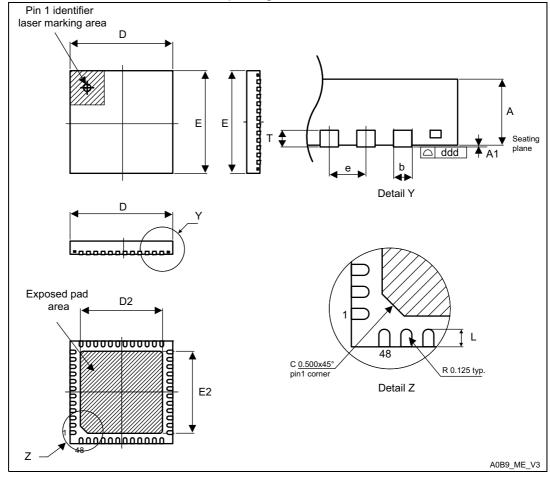

1. The above figure shows the package top view.

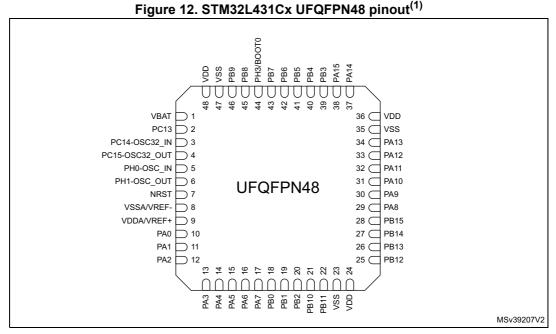

1. The above figure shows the package top view.

|                 |        |                 | Pi      | n Nu    | mbe    | ər      |         |          |                                          | _        | 0             |       | Pin function                                                                                                                      | IS                                                  |

|-----------------|--------|-----------------|---------|---------|--------|---------|---------|----------|------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| <b>UFQFPN32</b> | LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                               | Additional functions                                |

| 8               | 12     | 12              | E5      | F6      | 16     | F3      | 25      | K3       | PA2                                      | I/O      | FT_a          | -     | TIM2_CH3, USART2_TX,<br>LPUART1_TX,<br>QUADSPI_BK1_NCS,<br>COMP2_OUT,<br>TIM15_CH1, EVENTOUT                                      | COMP2_INM,<br>ADC1_IN7,<br>WKUP4,<br>LSCO           |

| 9               | 13     | 13              | E4      | G6      | 17     | G3      | 26      | L3       | PA3                                      | I/O      | TT_a          | -     | TIM2_CH4, USART2_RX,<br>LPUART1_RX,<br>QUADSPI_CLK,<br>SAI1_MCLK_A,<br>TIM15_CH2, EVENTOUT                                        | OPAMP1_<br>VOUT,<br>COMP2_INP,<br>ADC1_IN8          |

| -               | -      | -               | -       | H8      | 18     | C2      | 27      | E3       | VSS                                      | S        | -             | -     | -                                                                                                                                 | -                                                   |

| -               | -      | -               | -       | H7      | 19     | D2      | 28      | H3       | VDD                                      | S        | -             | -     | -                                                                                                                                 | -                                                   |

| 10              | 14     | 14              | G6      | E5      | 20     | H3      | 29      | М3       | PA4                                      | I/O      | TT_a          | -     | SPI1_NSS, SPI3_NSS,<br>USART2_CK,<br>SAI1_FS_B,<br>LPTIM2_OUT,<br>EVENTOUT                                                        | COMP1_INM,<br>COMP2_INM,<br>ADC1_IN9,<br>DAC1_OUT1  |

| 11              | 15     | 15              | F5      | F5      | 21     | F4      | 30      | K4       | PA5                                      | I/O      | TT_a          | -     | TIM2_CH1, TIM2_ETR,<br>SPI1_SCK,<br>LPTIM2_ETR,<br>EVENTOUT                                                                       | COMP1_INM,<br>COMP2_INM,<br>ADC1_IN10,<br>DAC1_OUT2 |

| 12              | 16     | 16              | F4      | G5      | 22     | G4      | 31      | L4       | PA6                                      | I/O      | FT_a          | -     | TIM1_BKIN, SPI1_MISO,<br>COMP1_OUT,<br>USART3_CTS,<br>LPUART1_CTS,<br>QUADSPI_BK1_IO3,<br>TIM1_BKIN_COMP2,<br>TIM16_CH1, EVENTOUT | ADC1_IN11                                           |

| 13              | 17     | 17              | F3      | H6      | 23     | H4      | 32      | M4       | PA7                                      | I/O      | FT_fa         | -     | TIM1_CH1N, I2C3_SCL,<br>SPI1_MOSI,<br>QUADSPI_BK1_IO2,<br>COMP2_OUT,<br>EVENTOUT                                                  | ADC1_IN12                                           |

| -               | -      | -               | -       | D4      | 24     | H5      | 33      | K5       | PC4                                      | I/O      | FT_a          | -     | USART3_TX,<br>EVENTOUT                                                                                                            | COMP1_INM,<br>ADC1_IN13                             |

| -               | -      | -               | -       | E4      | 25     | H6      | 34      | L5       | PC5                                      | I/O      | FT_a          | -     | USART3_RX,<br>EVENTOUT                                                                                                            | COMP1_INP,<br>ADC1_IN14,<br>WKUP5                   |

Table 14. STM32L431xx pin definitions (continued)

| S          |

|------------|

| <b>~</b> ? |

|            |

| ~          |

|            |

| C S        |

|            |

|            |

|            |

| Ä          |

|            |

| ω          |

| -          |

| XX         |

|            |

| ×          |

Pinouts and pin description

|        |      | AF8         | AF9        | AF10                | AF11 | AF12                                  | AF13        | AF14                        | AF15     |  |

|--------|------|-------------|------------|---------------------|------|---------------------------------------|-------------|-----------------------------|----------|--|

| Po     | ort  | LPUART1     | CAN1/TSC   | QUADSPI             |      | SDMMC1/<br>COMP1/<br>COMP2/<br>SWPMI1 | SAI1        | TIM2/TIM15/<br>TIM16/LPTIM2 | EVENTOUT |  |

|        | PA0  | -           | -          | -                   | -    | COMP1_OUT                             | SAI1_EXTCLK | TIM2_ETR                    | EVENTOUT |  |

|        | PA1  | -           | -          | -                   |      | -                                     | -           | TIM15_CH1N                  | EVENTOUT |  |

|        | PA2  | LPUART1_TX  | -          | QUADSPI_<br>BK1_NCS |      | COMP2_OUT                             | -           | TIM15_CH1                   | EVENTOUT |  |

|        | PA3  | LPUART1_RX  | -          | QUADSPI_CLK         |      | -                                     | SAI1_MCLK_A | TIM15_CH2                   | EVENTOUT |  |

|        | PA4  | -           | -          | -                   | -    | -                                     | SAI1_FS_B   | LPTIM2_OUT                  | EVENTOUT |  |

|        | PA5  | -           | -          | -                   | -    | -                                     | -           | LPTIM2_ETR                  | EVENTOUT |  |

|        | PA6  | LPUART1_CTS | -          | QUADSPI_<br>BK1_IO3 |      | TIM1_BKIN_<br>COMP2                   | -           | TIM16_CH1                   | EVENTOUT |  |

| Port A | PA7  | -           | -          | QUADSPI_<br>BK1_IO2 |      | COMP2_OUT                             | -           | -                           | EVENTOUT |  |

|        | PA8  | -           | -          | -                   |      | SWPMI1_IO                             | SAI1_SCK_A  | LPTIM2_OUT                  | EVENTOUT |  |

|        | PA9  | -           | -          | -                   |      | -                                     | SAI1_FS_A   | TIM15_BKIN                  | EVENTOUT |  |

|        | PA10 | -           | -          |                     |      | -                                     | SAI1_SD_A   | -                           | EVENTOUT |  |

|        | PA11 | -           | CAN1_RX    |                     | -    | TIM1_BKIN2_<br>COMP1                  | -           | -                           | EVENTOUT |  |

|        | PA12 | -           | CAN1_TX    |                     | -    | -                                     | -           | -                           | EVENTOUT |  |

|        | PA13 | -           | -          |                     | -    | SWPMI1_TX                             | SAI1_SD_B   | -                           | EVENTOUT |  |

|        | PA14 | -           | -          | -                   | -    | SWPMI1_RX                             | SAI1_FS_B   | -                           | EVENTOUT |  |

|        | PA15 | -           | TSC_G3_IO1 | -                   |      | SWPMI1_<br>SUSPEND                    | -           | -                           | EVENTOUT |  |

DocID028800 Rev 1

5

69/200

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

## 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = V_{DDA} = 3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

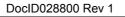

## 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 15*.

#### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 16.

| Symbol                               | Ratings                                                                           | Max                  | Unit |

|--------------------------------------|-----------------------------------------------------------------------------------|----------------------|------|

| $\Sigma IV_{DD}$                     | Total current into sum of all V <sub>DD</sub> power lines (source) <sup>(1)</sup> | 140                  |      |

| ΣIV <sub>SS</sub>                    | Total current out of sum of all $V_{SS}$ ground lines (sink) <sup>(1)</sup>       | 140                  |      |

| IV <sub>DD(PIN)</sub>                | Maximum current into each V <sub>DD</sub> power pin (source) <sup>(1)</sup>       | 100                  |      |

| IV <sub>SS(PIN)</sub>                | Maximum current out of each $V_{SS}$ ground pin $(sink)^{(1)}$                    | 100                  |      |

|                                      | Output current sunk by any I/O and control pin except FT_f                        | 20                   |      |

| I <sub>IO(PIN)</sub>                 | Output current sunk by any FT_f pin                                               | 20                   |      |

|                                      | Output current sourced by any I/O and control pin                                 | 20                   | mA   |

| ΣI                                   | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>      | 100                  |      |

| $\Sigma I_{IO(PIN)}$                 | Total output current sourced by sum of all I/Os and control $pins^{(2)}$          | 100                  |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on FT_xxx, TT_xx, RST and B pins, except PA4, PA5                | -5/+0 <sup>(4)</sup> |      |

| . /                                  | Injected current on PA4, PA5                                                      | -5/0                 |      |

| Σ I <sub>INJ(PIN)</sub>              | Total injected current (sum of all I/Os and control pins) <sup>(5)</sup>          | 25                   | 1    |

#### Table 19. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ,  $V_{BAT}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supplies, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

3. Positive injection (when  $V_{IN} > V_{DDIOx}$ ) is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

A negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer also to *Table 18: Voltage characteristics* for the maximum allowed input voltage values.

When several inputs are submitted to a current injection, the maximum ∑|I<sub>INJ(PIN)</sub>| is the absolute sum of the negative injected currents (instantaneous values).

#### Table 20. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 150         | °C   |

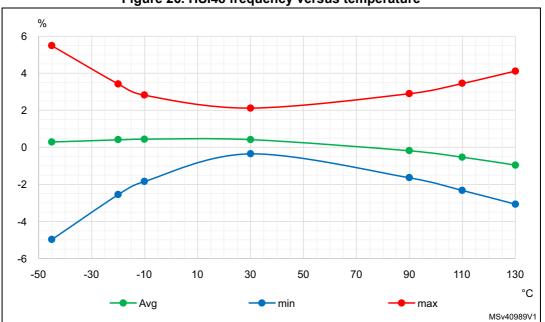

Figure 26. HSI48 frequency versus temperature

#### Low-speed internal (LSI) RC oscillator

| Table 50. L | SI oscillator | characteristics <sup>(1)</sup> |

|-------------|---------------|--------------------------------|

|-------------|---------------|--------------------------------|

| Symbol                                 | Parameter                            | Conditions                                      |       | Тур | Max   | Unit  |

|----------------------------------------|--------------------------------------|-------------------------------------------------|-------|-----|-------|-------|

| f <sub>LSI</sub>                       |                                      | V <sub>DD</sub> = 3.0 V, T <sub>A</sub> = 30 °C | 31.04 | -   | 32.96 | kHz   |

|                                        | LSI Frequency                        | $V_{DD}$ = 1.62 to 3.6 V, TA = -40 to 125 °C    | 29.5  | -   | 34    | KI IZ |

| t <sub>SU</sub> (LSI) <sup>(2)</sup>   | LSI oscillator start-<br>up time     | -                                               | -     | 80  | 130   | μs    |

| t <sub>STAB</sub> (LSI) <sup>(2)</sup> | LSI oscillator<br>stabilization time | 5% of final frequency                           | -     | 125 | 180   | μs    |

| I <sub>DD</sub> (LSI) <sup>(2)</sup>   | LSI oscillator power consumption     | -                                               | -     | 110 | 180   | nA    |

1. Guaranteed by characterization results.

2. Guaranteed by design.

## 6.3.9 PLL characteristics

The parameters given in *Table 51* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 21: General operating conditions*.

| Symbol              | Parameter                      | Conditions | Min | Тур | Max | Unit |

|---------------------|--------------------------------|------------|-----|-----|-----|------|

| f <sub>PLL_IN</sub> | PLL input clock <sup>(2)</sup> | -          | 4   | -   | 16  | MHz  |

|                     | PLL input clock duty cycle     | -          | 45  | -   | 55  | %    |

Table 51. PLL, PLLSAI1 characteristics<sup>(1)</sup>

|             | Table 60. Abc accuracy - Innited test conditions 3. A A (continued) |                                      |              |                          |     |      |     |    |  |  |

|-------------|---------------------------------------------------------------------|--------------------------------------|--------------|--------------------------|-----|------|-----|----|--|--|

| Sym-<br>bol | Parameter                                                           | C                                    | Min          | Тур                      | Max | Unit |     |    |  |  |

|             |                                                                     | al Sampling rate $\leq 5.33$ Msps, - | Single       | Fast channel (max speed) | -   | -69  | -67 |    |  |  |

|             | Total                                                               |                                      | ended        | Slow channel (max speed) | -   | -71  | -67 |    |  |  |

| THD         | harmonic<br>distortion                                              |                                      |              | Fast channel (max speed) | -   | -72  | -71 | dB |  |  |

|             |                                                                     | 3.6 V,<br>Voltage scaling Range 1    | Differential | Slow channel (max speed) | -   | -72  | -71 |    |  |  |

#### Table 68. ADC accuracy - limited test conditions $3^{(1)(2)(3)}$ (continued)

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

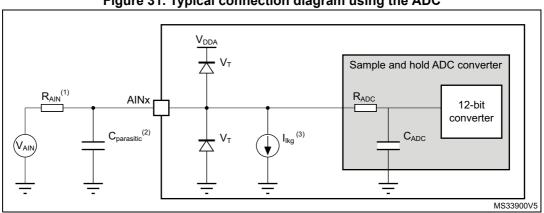

Figure 31. Typical connection diagram using the ADC

- Refer to Table 64: ADC characteristics for the values of  $\mathsf{R}_{AIN},\,\mathsf{R}_{ADC}$  and  $\mathsf{C}_{ADC}$ 1.

- $C_{\text{parasitic}}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (refer to *Table 59: I/O static characteristics* for the value of the pad capacitance). A high  $C_{\text{parasitic}}$  value will downgrade conversion accuracy. To remedy this,  $f_{\text{ADC}}$  should be reduced. 2.

- 3. Refer to Table 59: I/O static characteristics for the values of Ilkg.

#### **General PCB design guidelines**

Power supply decoupling should be performed as shown in Figure 17: Power supply scheme. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

#### 3. Refer to Table 59: I/O static characteristics.

4. Ton is the Refresh phase duration. Toff is the Hold phase duration. Refer to RM0392 reference manual for more details.

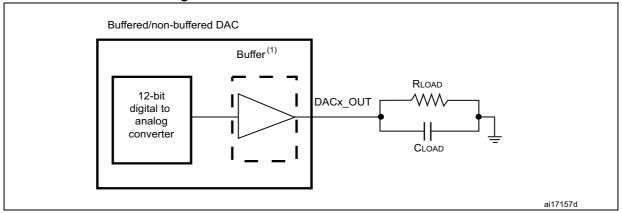

#### Figure 32. 12-bit buffered / non-buffered DAC

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

| Symbol    | Parameter                                          | Conditio                                              | ns                        | Min | Тур | Мах | Unit |

|-----------|----------------------------------------------------|-------------------------------------------------------|---------------------------|-----|-----|-----|------|

| DNL       | Differential non                                   | DAC output buffer ON                                  |                           | -   | -   | ±2  |      |

| DINL      | linearity <sup>(2)</sup>                           | DAC output buffer OFF                                 |                           | -   | -   | ±2  |      |

| -         | monotonicity                                       | 10 bits                                               | guaranteed                |     |     |     |      |

| INL       | Integral non                                       | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ         |                           | -   | -   | ±4  |      |

| INL       | linearity <sup>(3)</sup>                           | DAC output buffer OFF<br>CL ≤ 50 pF, no RL            | -                         | -   | ±4  |     |      |

|           | Offset error at code 0x800 <sup>(3)</sup>          |                                                       | V <sub>REF+</sub> = 3.6 V | _   | -   | ±12 |      |

| Offset    |                                                    |                                                       | V <sub>REF+</sub> = 1.8 V | -   | -   | ±25 | LSB  |

|           |                                                    | DAC output buffer OFF<br>CL ≤ 50 pF, no RL            |                           | -   | -   | ±8  |      |

| Offset1   | Offset error at code 0x001 <sup>(4)</sup>          | DAC output buffer OFF $CL \leq 50 \text{ pF}$ , no RL |                           | -   | -   | ±5  |      |

| OffsetCal | Offset Error at<br>code 0x800<br>after calibration | DAC output buffer ON                                  | V <sub>REF+</sub> = 3.6 V | -   | -   | ±5  |      |

| Unserval  |                                                    | CL ≤ 50 pF, RL ≥ 5 kΩ                                 | V <sub>REF+</sub> = 1.8 V | -   | -   | ±7  |      |

## Table 71. DAC accuracy<sup>(1)</sup>

#### Voltage reference buffer characteristics 6.3.19

| Table 72. VREFBUF characteristics <sup>(1)</sup> |                                                                                                 |                                                              |                            |                          |       |                                         |         |    |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------|--------------------------|-------|-----------------------------------------|---------|----|

| Symbol                                           | Parameter                                                                                       | Conditio                                                     | ons                        | Min                      | Тур   | Max                                     | Unit    |    |

|                                                  |                                                                                                 | Normal made                                                  | V <sub>RS</sub> = 0        | 2.4                      | -     | 3.6                                     |         |    |

| M                                                | Analog supply                                                                                   | Normal mode                                                  | V <sub>RS</sub> = 1        | 2.8                      | -     | 3.6                                     |         |    |

| V <sub>DDA</sub>                                 | voltage                                                                                         | Degraded mode <sup>(2)</sup>                                 | V <sub>RS</sub> = 0        | 1.65                     | -     | 2.4                                     |         |    |

|                                                  |                                                                                                 |                                                              | V <sub>RS</sub> = 1        | 1.65                     | -     | 2.8                                     | V       |    |

|                                                  |                                                                                                 | Normal mode                                                  | V <sub>RS</sub> = 0        | 2.046 <sup>(3)</sup>     | 2.048 | 2.049 <sup>(3)</sup>                    | v       |    |

| V <sub>REFBUF</sub> _                            | Voltage reference                                                                               | Normai mode                                                  | V <sub>RS</sub> = 1        | 2.498 <sup>(3)</sup>     | 2.5   | 2.502 <sup>(3)</sup>                    |         |    |

| OUT                                              | output                                                                                          | Degraded mode <sup>(2)</sup>                                 | V <sub>RS</sub> = 0        | V <sub>DDA</sub> -150 mV | -     | V <sub>DDA</sub>                        |         |    |

|                                                  |                                                                                                 | Degraded mode                                                | V <sub>RS</sub> = 1        | V <sub>DDA</sub> -150 mV | -     | V <sub>DDA</sub>                        |         |    |

| TRIM                                             | Trim step resolution                                                                            | -                                                            | -                          | -                        | ±0.05 | ±0.1                                    | %       |    |

| CL                                               | Load capacitor                                                                                  | -                                                            | -                          | 0.5                      | 1     | 1.5                                     | μF      |    |

| esr                                              | Equivalent<br>Serial Resistor<br>of Cload                                                       |                                                              |                            | -                        | -     | 2                                       | Ω       |    |

| I <sub>load</sub>                                | Static load current                                                                             |                                                              |                            | -                        | -     | 4                                       | mA      |    |

| 1                                                | Line regulation                                                                                 | 281/51/ 5361/                                                | I <sub>load</sub> = 500 μA | -                        | 200   | 1000                                    | nnm\/   |    |

| I <sub>line_reg</sub>                            |                                                                                                 | $2.0 V \leq V_{\text{DDA}} \leq 3.0 V$                       | I <sub>load</sub> = 4 mA   | -                        | 100   | 500                                     | ppm/V   |    |

| l <sub>load_reg</sub>                            | Load<br>regulation                                                                              | 500 $\mu$ A $\leq$ I <sub>load</sub> $\leq$ 4 mA Normal mode |                            | -                        | 50    | 500                                     | ppm/mA  |    |

| T                                                | Temperature<br>coefficient                                                                      | -40 °C < T <sub>J</sub> < +125 °C                            | ;                          | -                        | -     | T <sub>coeff</sub> _<br>vrefint +<br>50 | ppm/ °C |    |

| T <sub>Coeff</sub>                               |                                                                                                 | 0 °C < T <sub>J</sub> < +50 °C                               |                            | -                        | -     | T <sub>coeff</sub><br>vrefint +<br>50   | ppm/ C  |    |

| PSRR                                             | Power supply                                                                                    | Power supply DC                                              |                            |                          | 40    | 60                                      | -       | dB |

| FORK                                             | rejection                                                                                       | 100 kHz                                                      | 100 kHz                    |                          | 40    | -                                       | uБ      |    |

|                                                  | Start-up time                                                                                   | CL = 0.5 µF <sup>(4)</sup>                                   |                            |                          | -     | 300                                     | 350     |    |

| t <sub>START</sub>                               |                                                                                                 | CL = 1.1 μF <sup>(4)</sup>                                   |                            | -                        | 500   | 650                                     | μs      |    |

|                                                  |                                                                                                 | $CL = 1.5 \ \mu F^{(4)}$                                     |                            | -                        | 650   | 800                                     |         |    |

| I <sub>INRUSH</sub>                              | Control of<br>maximum DC<br>current drive<br>on VREFBUF_<br>OUT during<br>start-up phase<br>(5) | -                                                            | -                          | -                        | 8     | -                                       | mA      |    |

# (1)

Г

Т

٦

Т

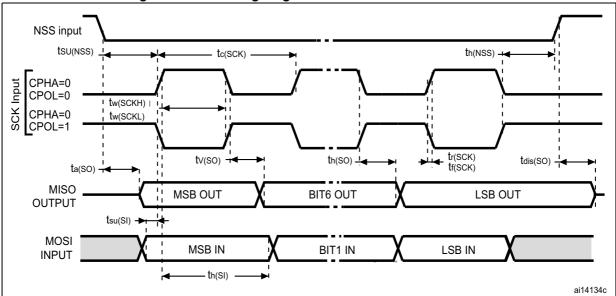

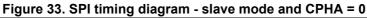

#### **SPI characteristics**

Unless otherwise specified, the parameters given in *Table 82* for SPI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and supply voltage conditions summarized in *Table 21: General operating conditions*.

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                       | Parameter                | Conditions                                                                              | Min                              | Тур               | Max                  | Unit |

|----------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------|----------------------------------|-------------------|----------------------|------|

|                                              |                          | Master mode receiver/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1    |                                  |                   | 40                   |      |

|                                              | SPI clock frequency      | Master mode receiver/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1   |                                  |                   | 16                   |      |

|                                              |                          | Master mode transmitter<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1            |                                  |                   | 40                   |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    |                          | Slave mode receiver<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                | -                                | -                 | 40                   | MHz  |

|                                              |                          | Slave mode transmitter/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  |                                  |                   | 37 <sup>(2)</sup>    |      |

|                                              |                          | Slave mode transmitter/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 |                                  |                   | 20 <sup>(2)</sup>    |      |

|                                              |                          | Voltage Range 2                                                                         |                                  |                   | 13                   |      |

| t <sub>su(NSS)</sub>                         | NSS setup time           | Slave mode, SPI prescaler = 2                                                           | 4 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |

| t <sub>h(NSS)</sub>                          | NSS hold time            | Slave mode, SPI prescaler = 2                                                           | 2 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time    | Master mode                                                                             | T <sub>PCLK</sub> -2             | T <sub>PCLK</sub> | T <sub>PCLK</sub> +2 | ns   |

| t <sub>su(MI)</sub>                          | Data input setup time    | Master mode                                                                             | 4                                | -                 | -                    | ns   |

| t <sub>su(SI)</sub>                          |                          | Slave mode                                                                              | 1.5                              | -                 | -                    | 115  |

| t <sub>h(MI)</sub>                           | Data input hold time     | Master mode                                                                             | 6.5                              | -                 | -                    | ns   |

| t <sub>h(SI)</sub>                           |                          | Slave mode                                                                              | 1.5                              | -                 | -                    | 115  |

| t <sub>a(SO)</sub>                           | Data output access time  | Slave mode                                                                              | 9                                | -                 | 36                   | ns   |

| t <sub>dis(SO)</sub>                         | Data output disable time | Slave mode                                                                              | 9                                | -                 | 16                   | ns   |

| Table | 82. | SPI | characteristics <sup>(</sup> | 1) |

|-------|-----|-----|------------------------------|----|

|-------|-----|-----|------------------------------|----|

| Symbol             | Parameter              | Conditions                                                   | Min | Тур  | Max  | Unit |

|--------------------|------------------------|--------------------------------------------------------------|-----|------|------|------|

|                    | Data output valid time | Slave mode 2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  | -   | 12.5 | 13.5 |      |

| t <sub>v(SO)</sub> |                        | Slave mode 1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 | -   | 12.5 | 24   | ns   |

|                    |                        | Slave mode 1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 2 | -   | 12.5 | 33   |      |

| t <sub>v(MO)</sub> |                        | Master mode                                                  | -   | 4.5  | 6    |      |

| t <sub>h(SO)</sub> | Data output hold time  | Slave mode                                                   | 7   | -    | -    | ns   |

| t <sub>h(MO)</sub> |                        | Master mode                                                  | 0   | -    | -    | 115  |

## Table 82. SPI characteristics<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

2. Maximum frequency in Slave transmitter mode is determined by the sum of  $t_{v(SO)}$  and  $t_{su(MI)}$  which has to fit into SCK low or high phase preceding the SCK sampling edge. This value can be achieved when the SPI communicates with a master having  $t_{su(MI)} = 0$  while Duty(SCK) = 50 %.

| Symbol |       | millimeters |       |        |        |        |

|--------|-------|-------------|-------|--------|--------|--------|

|        | Min   | Тур         | Мах   | Min    | Тур    | Мах    |

| А      | -     | -           | 1.600 | -      | -      | 0.0630 |

| A1     | 0.050 | -           | 0.150 | 0.0020 | -      | 0.0059 |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551 | 0.0571 |

| b      | 0.170 | 0.220       | 0.270 | 0.0067 | 0.0087 | 0.0106 |

| с      | 0.090 | -           | 0.200 | 0.0035 | -      | 0.0079 |

| D      | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543 | 0.3622 |

| D1     | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756 | 0.2835 |

| D3     | -     | 5.500       | -     | -      | 0.2165 | -      |

| E      | 8.800 | 9.000       | 9.200 | 0.3465 | 0.3543 | 0.3622 |

| E1     | 6.800 | 7.000       | 7.200 | 0.2677 | 0.2756 | 0.2835 |

| E3     | -     | 5.500       | -     | -      | 0.2165 | -      |

| е      | -     | 0.500       | -     | -      | 0.0197 | -      |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236 | 0.0295 |

| L1     | -     | 1.000       | -     | -      | 0.0394 | -      |

| k      | 0°    | 3.5°        | 7°    | 0°     | 3.5°   | 7°     |

| CCC    | -     | -           | 0.080 | -      | -      | 0.0031 |

| Table 99. LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package |

|-------------------------------------------------------------------|

| mechanical data                                                   |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 7.8 UFQFPN48 package information

Figure 63. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package outline

1. Drawing is not to scale.

- 2. All leads/pads should also be soldered to the PCB to improve the lead/pad solder joint life.

- 3. There is an exposed die pad on the underside of the UFQFPN package. It is recommended to connect and solder this back-side pad to PCB ground.

## 7.10 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 21: General operating conditions*.

The maximum chip-junction temperature,  $\mathsf{T}_{\mathsf{J}}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma \; ((\mathsf{V}_{\mathsf{DDIOx}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V<sub>OL</sub> / I<sub>OL</sub> and V<sub>OH</sub> / I<sub>OH</sub> of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                         | Value | Unit |  |  |  |

|---------------|-----------------------------------------------------------------------------------|-------|------|--|--|--|

|               | <b>Thermal resistance junction-ambient</b><br>UFQFPN48 - 7 × 7 mm / 0.5 mm pitch  | 33    |      |  |  |  |

|               | <b>Thermal resistance junction-ambient</b><br>LQFP48 - 7 × 7 mm / 0.5 mm pitch    | 57    | °C/W |  |  |  |

|               | Thermal resistance junction-ambient<br>WLCSP49 3.141 x 3.127 / 0.4 mm pitch       | 48    |      |  |  |  |

| Θ             | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch         | 46    |      |  |  |  |

| $\Theta_{JA}$ | <b>Thermal resistance junction-ambient</b><br>UFBGA64 - 5 × 5 mm / 0.5 mm pitch   | 65    | CIW  |  |  |  |

|               | Thermal resistance junction-ambient<br>WLCSP64 3.141 x 3.127 / 0.35 mm pitch      | 46    |      |  |  |  |

|               | <b>Thermal resistance junction-ambient</b><br>LQFP100 - 14 × 14 mm / 0.5 mm pitch | 42    |      |  |  |  |

|               | <b>Thermal resistance junction-ambient</b><br>UFBGA100 - 7 × 7 mm / 0.5 mm pitch  | 57    |      |  |  |  |

Table 102. Package thermal characteristics

## 7.10.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

# 8 Part numbering

| Table 103. STM32L431xx or                             | dering info  | orma | tion so | chem | ne |   |   |    |

|-------------------------------------------------------|--------------|------|---------|------|----|---|---|----|

| Example:                                              | STM32        | L    | 431     | С    | С  | Т | 6 | TR |

| Device family                                         |              |      |         |      |    |   |   |    |

| STM32 = ARM <sup>®</sup> based 32-bit microcontroller |              |      |         |      |    |   |   |    |

|                                                       |              |      |         |      |    |   |   |    |

| Product type                                          |              |      |         |      |    |   |   |    |

| L = ultra-low-power                                   |              |      |         |      |    |   |   |    |

|                                                       |              |      |         |      |    |   |   |    |

| Device subfamily                                      |              |      |         |      |    |   |   |    |

| 431: STM32L431xx                                      |              |      |         |      |    |   |   |    |

|                                                       |              |      |         |      |    |   |   |    |

| Pin count                                             |              |      |         |      |    |   |   |    |

| K = 32 pins                                           |              |      |         |      |    |   |   |    |

| C = 48 pins                                           |              |      |         |      |    |   |   |    |

| R = 64 pins                                           |              |      |         |      |    |   |   |    |

| V = 100 pins                                          |              |      |         |      |    |   |   |    |

|                                                       |              |      |         |      |    |   |   |    |

| Flash memory size                                     |              |      |         |      |    |   |   |    |

| B = 128 kB of Flash memory                            |              |      |         |      |    |   |   |    |

| C = 256 KB of Flash memory                            |              |      |         |      |    |   |   |    |

|                                                       |              |      |         |      |    |   |   |    |

| Package                                               |              |      |         |      |    |   |   |    |

| T = LQFP ECOPACK <sup>®</sup> 2                       |              |      |         |      |    |   |   |    |

| U = QFN ECOPACK®2                                     |              |      |         |      |    |   |   |    |

| I = UFBGA ECOPACK®2                                   |              |      |         |      |    |   |   |    |

| $Y = CSP ECOPACK^{®}2$                                |              |      |         |      |    |   |   |    |

| Temperature range                                     |              |      |         |      |    |   |   |    |

| 6 = Industrial temperature range, -40 to 85 °C (105   | S°C junction | )    |         |      |    |   |   |    |

| 7 = Industrial temperature range, -40 to 105 °C (12   |              |      |         |      |    |   |   |    |

| 3 = Industrial temperature range, -40 to 125 °C (13   | -            | -    |         |      |    |   |   |    |

|                                                       |              | ,    |         |      |    |   |   |    |

| Packing                                               |              |      |         |      |    |   |   |    |

TR = tape and reel

xxx = programmed parts

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID028800 Rev 1