Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 80MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, SWPMI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                     |

| Number of I/O              | 39                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                              |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-LQFP                                                                   |

| Supplier Device Package    | 48-LQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l431cct6tr   |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|               | package recommended footprint                                                      | 173 |

|---------------|------------------------------------------------------------------------------------|-----|

| Figure 47.    | UFBGA100 marking (package top view)                                                | 174 |

| Figure 48.    | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package outline                  | 175 |

| Figure 49.    | LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat package                          |     |

|               | recommended footprint                                                              | 176 |

| Figure 50.    | LQFP64 marking (package top view)                                                  | 177 |

| Figure 51.    | UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid array |     |

|               | package outline                                                                    | 178 |

| Figure 52.    | UFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch ultra profile fine pitch ball grid array |     |

|               | package recommended footprint                                                      |     |

| Figure 53.    | UFBGA64 marking (package top view)                                                 | 180 |

| Figure 54.    | WLCSP64 - 64-ball, 3.141 x 3.127 mm, 0.35 mm pitch wafer level chip scale          |     |

|               | package outline                                                                    | 181 |

| Figure 55.    | WLCSP64 - 64-ball, 3.141 x 3.127 mm, 0.35 mm pitch wafer level chip scale          |     |

|               | package recommended footprint                                                      |     |

| Figure 56.    | WLCSP64 marking (package top view)                                                 | 183 |

| Figure 57.    | WLCSP49 - 49-ball, 3.141 x 3.127 mm, 0.4 mm pitch wafer level chip scale           |     |

|               | package outline                                                                    | 184 |

| Figure 58.    | WLCSP49 - 49-ball, 3.141 x 3.127 mm, 0.4 mm pitch wafer level chip scale           |     |

|               | package recommended footprint                                                      |     |

| Figure 59.    | WLCSP49 marking (package top view)                                                 |     |

| Figure 60.    | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                    | 187 |

| Figure 61.    | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package                            |     |

|               | recommended footprint                                                              |     |

| Figure 62.    | LQFP48 marking (package top view)                                                  | 189 |

| Figure 63.    | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat          |     |

|               | package outline.                                                                   | 190 |

| Figure 64.    | UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat          |     |

|               | package recommended footprint                                                      |     |

| Figure 65.    | UFQFPN48 marking (package top view)                                                | 192 |

| Figure 66.    | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat            |     |

|               | package outline.                                                                   | 192 |

| Figure 67.    | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat            |     |

| <b>-</b> ; oc | package recommended footprint                                                      |     |

| Figure 68.    | UFQFPN32 marking (package top view)                                                |     |

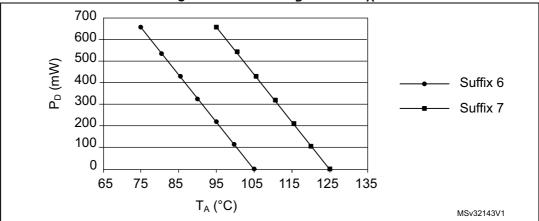

| Figure 69.    | LQFP64 P <sub>D</sub> max vs. T <sub>A</sub>                                       | 197 |

# 3 Functional overview

# 3.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processor is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU 32-bit RISC processor features exceptional codeefficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU speeds up software development by using metalanguage development tools, while avoiding saturation.

With its embedded ARM core, the STM32L431xx family is compatible with all ARM tools and software.

*Figure 1* shows the general block diagram of the STM32L431xx family devices.

# 3.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 processors. It balances the inherent performance advantage of the ARM<sup>®</sup> Cortex<sup>®</sup>-M4 over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor near 100 DMIPS performance at 80MHz, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 64-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 80 MHz.

# 3.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

### 3.9.3 Voltage regulator

Two embedded linear voltage regulators supply most of the digital circuitries: the main regulator (MR) and the low-power regulator (LPR).

- The MR is used in the Run and Sleep modes and in the Stop 0 mode.

- The LPR is used in Low-Power Run, Low-Power Sleep, Stop 1 and Stop 2 modes. It is also used to supply the 16 Kbyte SRAM2 in Standby with RAM2 retention.

- Both regulators are in power-down in Standby and Shutdown modes: the regulator output is in high impedance, and the kernel circuitry is powered down thus inducing zero consumption.

The ultralow-power STM32L431xx supports dynamic voltage scaling to optimize its power consumption in run mode. The voltage from the Main Regulator that supplies the logic (VCORE) can be adjusted according to the system's maximum operating frequency.

There are two power consumption ranges:

- Range 1 with the CPU running at up to 80 MHz.

- Range 2 with a maximum CPU frequency of 26 MHz. All peripheral clocks are also limited to 26 MHz.

The VCORE can be supplied by the low-power regulator, the main regulator being switched off. The system is then in Low-power run mode.

Low-power run mode with the CPU running at up to 2 MHz. Peripherals with independent clock can be clocked by HSI16.

### 3.9.4 Low-power modes

The ultra-low-power STM32L431xx supports seven low-power modes to achieve the best compromise between low-power consumption, short startup time, available peripherals and available wakeup sources:

By default, the microcontroller is in Run mode after a system or a power Reset. It is up to the user to select one of the low-power modes described below:

Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

• Low-power run mode

This mode is achieved with VCORE supplied by the low-power regulator to minimize the regulator's operating current. The code can be executed from SRAM or from Flash, and the CPU frequency is limited to 2 MHz. The peripherals with independent clock can be clocked by HSI16.

• Low-power sleep mode

This mode is entered from the low-power run mode. Only the CPU clock is stopped. When wakeup is triggered by an event or an interrupt, the system reverts to the lowpower run mode.

### • Stop 0, Stop 1 and Stop 2 modes

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the VCORE domain are stopped, the PLL, the MSI

| Calibration value name | Description                                                                                            | Memory address            |  |  |  |  |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|--|--|--|--|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C (± 5 °C), $V_{DDA} = V_{REF+} = 3.0 V (\pm 10 mV)$  | 0x1FFF 75A8 - 0x1FFF 75A9 |  |  |  |  |  |  |  |  |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 130 °C (± 5 °C), $V_{DDA} = V_{REF+} = 3.0 V (\pm 10 mV)$ | 0x1FFF 75CA - 0x1FFF 75CB |  |  |  |  |  |  |  |  |

Table 7. Temperature sensor calibration values

## 3.15.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference (VREFINT) provides a stable (bandgap) voltage output for the ADC and Comparators. VREFINT is internally connected to the ADC1\_IN0 input channel. The precise voltage of VREFINT is individually measured for each part by ST during production test and stored in the system memory area. It is accessible in read-only mode.

| Calibration value name | Description                                                                                                        | Memory address            |

|------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------|

| VREFINT                | Raw data acquired at a<br>temperature of 30 °C (± 5 °C),<br>V <sub>DDA</sub> = V <sub>REF+</sub> = 3.0 V (± 10 mV) | 0x1FFF 75AA - 0x1FFF 75AB |

| Table 8. Internal voltage reference | calibration values |

|-------------------------------------|--------------------|

|-------------------------------------|--------------------|

## 3.15.3 V<sub>BAT</sub> battery voltage monitoring

This embedded hardware feature allows the application to measure the V<sub>BAT</sub> battery voltage using the internal ADC channel ADC1\_IN18. As the V<sub>BAT</sub> voltage may be higher than VDDA, and thus outside the ADC input range, the VBAT pin is internally connected to a bridge divider by 3. As a consequence, the converted digital value is one third the V<sub>BAT</sub> voltage.

# 3.16 Digital to analog converter (DAC)

Two 12-bit buffered DAC channels can be used to convert digital signals into analog voltage signal outputs. The chosen design structure is composed of integrated resistor strings and an amplifier in inverting configuration.

This digital interface supports the following features:

- Up to two DAC output channels

- 8-bit or 12-bit output mode

- Buffer offset calibration (factory and user trimming)

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

# 3.22 Timers and watchdogs

The STM32L431xx includes one advanced control timers, up to five general-purpose timers, two basic timers, two low-power timers, two watchdog timers and a SysTick timer. The table below compares the features of the advanced control, general purpose and basic timers.

| Timer type          | Timer      | Counter resolution | Counter<br>type      | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>outputs |  |  |  |  |

|---------------------|------------|--------------------|----------------------|---------------------------------------|------------------------------|---------------------------------|--------------------------|--|--|--|--|

| Advanced control    | TIM1       | 16-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | 3                        |  |  |  |  |

| General-<br>purpose | TIM2       | 32-bit             | Up, down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                       |  |  |  |  |

| General-<br>purpose | TIM15      | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 2                               | 1                        |  |  |  |  |

| General-<br>purpose | TIM16      | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 1                               | 1                        |  |  |  |  |

| Basic               | TIM6, TIM7 | 16-bit             | Up                   | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                       |  |  |  |  |

Table 9. Timer feature comparison

## 3.22.1 Advanced-control timer (TIM1)

The advanced-control timer can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as complete general-purpose timers. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

Many features are shared with those of the general-purpose TIMx timers (described in *Section 3.22.2*) using the same architecture, so the advanced-control timer can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

# 3.26 Low-power universal asynchronous receiver transmitter (LPUART)

The device embeds one Low-Power UART. The LPUART supports asynchronous serial communication with minimum power consumption. It supports half duplex single wire communication and modem operations (CTS/RTS). It allows multiprocessor communication.

The LPUART has a clock domain independent from the CPU clock, and can wakeup the system from Stop mode using baudrates up to 220 Kbaud. The wake up events from Stop mode are programmable and can be:

- Start bit detection

- Any received data frame

- A specific programmed data frame

Only a 32.768 kHz clock (LSE) is needed to allow LPUART communication up to 9600 baud. Therefore, even in Stop mode, the LPUART can wait for an incoming frame while having an extremely low energy consumption. Higher speed clock can be used to reach higher baudrates.

LPUART interface can be served by the DMA controller.

|                 |        |                 | Pi      | n Nu    | mbe    | ər      |         |          |                                          |          |               |            | Pin functions                                       |                                            |  |  |

|-----------------|--------|-----------------|---------|---------|--------|---------|---------|----------|------------------------------------------|----------|---------------|------------|-----------------------------------------------------|--------------------------------------------|--|--|

| <b>UFQFPN32</b> | LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes      | Alternate functions                                 | Additional functions                       |  |  |

| -               | -      | -               | -       | -       | -      | -       | 1       | B2       | PE2                                      | I/O      | FT            | -          | TRACECK,<br>TSC_G7_IO1,<br>SAI1_MCLK_A,<br>EVENTOUT | -                                          |  |  |

| -               | -      | -               | -       | -       | -      | -       | 2       | A1       | PE3                                      | I/O      | FT            | -          | TRACED0,<br>TSC_G7_IO2,<br>SAI1_SD_B, EVENTOUT      | -                                          |  |  |

| -               | -      | 1               | -       | -       | -      | -       | 3       | B1       | PE4                                      | I/O      | FT            | -          | TRACED1,<br>TSC_G7_IO3,<br>SAI1_FS_A, EVENTOUT      | -                                          |  |  |

| -               | -      | -               | -       | -       | -      | -       | 4       | C2       | PE5                                      | I/O      | FT            | -          | TRACED2,<br>TSC_G7_IO4,<br>SAI1_SCK_A,<br>EVENTOUT  | -                                          |  |  |

| -               | -      | -               | -       | -       | -      | -       | 5       | D2       | PE6                                      | I/O      | FT            | -          | TRACED3, SAI1_SD_A,<br>EVENTOUT                     | RTC_TAMP3,<br>WKUP3                        |  |  |

| -               | 1      | 1               | B6      | B7      | 1      | B2      | 6       | E2       | VBAT                                     | S        | -             | -          | -                                                   | -                                          |  |  |

| -               | 2      | 2               | B7      | B8      | 2      | A2      | 7       | C1       | PC13                                     | I/O      | FT            | (1)<br>(2) | EVENTOUT                                            | RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT,<br>WKUP2 |  |  |

| 2               | 3      | 3               | C7      | C8      | 3      | A1      | 8       | D1       | PC14-<br>OSC32_I<br>N (PC14)             | I/O      | FT            | (1)<br>(2) | EVENTOUT                                            | OSC32_IN                                   |  |  |

| 3               | 4      | 4               | C6      | C7      | 4      | B1      | 9       | E1       | PC15-<br>OSC32_<br>OUT<br>(PC15)         | I/O      | FT            | (1)<br>(2) | EVENTOUT                                            | OSC32_OUT                                  |  |  |

| -               | -      | -               | -       | -       | -      | I       | 10      | F2       | VSS                                      | S        | -             | -          | -                                                   | -                                          |  |  |

| -               | -      | -               | -       | -       | -      | -       | 11      | G2       | VDD                                      | S        | -             | -          | -                                                   | -                                          |  |  |

| -               | 5      | 5               | D7      | D8      | 5      | C1      | 12      | F1       | PH0-<br>OSC_<br>IN (PH0)                 | I/O      | FT            | -          | EVENTOUT                                            | OSC_IN                                     |  |  |

| -               | 6      | 6               | D6      | D7      | 6      | D1      | 13      | G1       | PH1-<br>OSC_<br>OUT<br>(PH1)             | I/O      | FT            | -          | EVENTOUT                                            | OSC_OUT                                    |  |  |

| 4               | 7      | 7               | D5      | D6      | 7      | E1      | 14      | H2       | NRST                                     | I/O      | RST           | -          | -                                                   | -                                          |  |  |

Table 14. STM32L431xx pin definitions

|                 |        |                 | Pi      | n Nu    | mbe    | ər      |         |          |                                          | -        | <u>A</u>      |       | Pin functions                                                                                                                                                 |                      |  |  |

|-----------------|--------|-----------------|---------|---------|--------|---------|---------|----------|------------------------------------------|----------|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| <b>UFQFPN32</b> | LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                           | Additional functions |  |  |

| -               | -      | -               | -       | -       | -      | -       | 46      | M12      | PE15                                     | I/O      | FT            | -     | TIM1_BKIN,<br>TIM1_BKIN_COMP1,<br>SPI1_MOSI,<br>QUADSPI_BK1_IO3,<br>EVENTOUT                                                                                  | -                    |  |  |

| -               | 21     | 21              | E3      | H4      | 29     | G7      | 47      | L10      | PB10                                     | I/O      | FT_f          | -     | TIM2_CH3, I2C2_SCL,<br>SPI2_SCK, USART3_TX,<br>LPUART1_RX,<br>TSC_SYNC,<br>QUADSPI_CLK,<br>COMP1_OUT,<br>SAI1_SCK_A,<br>EVENTOUT                              | -                    |  |  |

| -               | 22     | 22              | F2      | H3      | 30     | H7      | 48      | L11      | PB11                                     | I/O      | FT_f          | -     | TIM2_CH4, I2C2_SDA,<br>USART3_RX,<br>LPUART1_TX,<br>QUADSPI_BK1_NCS,<br>COMP2_OUT,<br>EVENTOUT                                                                | -                    |  |  |

| 16              | 23     | 23              | G2      | H2      | 31     | D6      | 49      | F12      | VSS                                      | S        | -             | -     | -                                                                                                                                                             | -                    |  |  |

| 17              | 24     | 24              | G1      | H1      | 32     | E6      | 50      | G12      | VDD                                      | S        | -             | -     | -                                                                                                                                                             | -                    |  |  |

| -               | 25     | 25              | F1      | G3      | 33     | H8      | 51      | L12      | PB12                                     | I/O      | FT            | -     | TIM1_BKIN,<br>TIM1_BKIN_COMP2,<br>I2C2_SMBA, SPI2_NSS,<br>USART3_CK,<br>LPUART1_RTS_DE,<br>TSC_G1_IO1,<br>SWPMI1_IO,<br>SAI1_FS_A,<br>TIM15_BKIN,<br>EVENTOUT | -                    |  |  |

| -               | 26     | 26              | E2      | G2      | 34     | G8      | 52      | K12      | PB13                                     | I/O      | FT_f          | -     | TIM1_CH1N, I2C2_SCL,<br>SPI2_SCK,<br>USART3_CTS,<br>LPUART1_CTS,<br>TSC_G1_IO2,<br>SWPMI1_TX,<br>SAI1_SCK_A,<br>TIM15_CH1N,<br>EVENTOUT                       | -                    |  |  |

Table 14. STM32L431xx pin definitions (continued)

| Bus  | STM32L431xx memory map and per<br>Boundary address | Size(bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Peripheral      |

|------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

|      | 0x5006 0800 - 0x5006 0BFF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RNG             |

|      | 0x5004 0400 - 0x5006 07FF                          | 158 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reserved        |

|      | 0x5004 0000 - 0x5004 03FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ADC             |

|      | 0x5000 0000 - 0x5003 FFFF                          | 16 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reserved        |

|      | 0x4800 2000 - 0x4FFF FFFF                          | ~127 MB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reserved        |

| AHB2 | 0x4800 1C00 - 0x4800 1FFF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GPIOH           |

| ANDZ | 0x4800 1400 - 0x4800 1BFF                          | 2 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reserved        |

|      | 0x4800 1000 - 0x4800 13FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GPIOE           |

|      | 0x4800 0C00 - 0x4800 0FFF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GPIOD           |

|      | 0x4800 0800 - 0x4800 0BFF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GPIOC           |

|      | 0x4800 0400 - 0x4800 07FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GPIOB           |

|      | 0x4800 0000 - 0x4800 03FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GPIOA           |

| -    | 0x4002 4400 - 0x47FF FFFF                          | ~127 MB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Reserved        |

|      | 0x4002 4000 - 0x4002 43FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TSC             |

|      | 0x4002 3400 - 0x4002 3FFF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reserved        |

|      | 0x4002 3000 - 0x4002 33FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | CRC             |

|      | 0x4002 2400 - 0x4002 2FFF                          | 3 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reserved        |

| AHB1 | 0x4002 2000 - 0x4002 23FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | FLASH registers |

| АПВТ | 0x4002 1400 - 0x4002 1FFF                          | 3 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reserved        |

|      | 0x4002 1000 - 0x4002 13FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RCC             |

|      | 0x4002 0800 - 0x4002 0FFF                          | 2 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reserved        |

|      | 0x4002 0400 - 0x4002 07FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DMA2            |

|      | 0x4002 0000 - 0x4002 03FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DMA1            |

|      | 0x4001 5800 - 0x4001 FFFF                          | 42 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Reserved        |

|      | 0x4001 5400 - 0x4000 57FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SAI1            |

|      | 0x4001 4800 - 0x4000 53FF                          | 3 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reserved        |

| APB2 | 0x4001 4400 - 0x4001 47FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TIM16           |

| APDZ | 0x4001 4000 - 0x4001 43FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TIM15           |

|      | 0x4001 3C00 - 0x4001 3FFF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reserved        |

|      | 0x4001 3800 - 0x4001 3BFF                          | 158 KB         Reserved           1 KB         ADC           16 KB         Reserved           ~127 MB         Reserved           1 KB         GPIOH           2 KB         Reserved           1 KB         GPIOE           1 KB         GPIOE           1 KB         GPIOD           1 KB         GPIOD           1 KB         GPIOA           1 KB         Reserved           1 KB         Reserved           1 KB         Reserved           1 KB         Reserved           1 KB         FLASH registers           3 KB         Reserved           1 KB         RCC           2 KB         Reserved           1 KB         DMA1           42 KB         Reserved           1 KB         SAI1           3 KB         Reserved           1 KB         SAI1 |                 |

|      | 0x4001 3400 - 0x4001 37FF                          | 1 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reserved        |

# Table 17. STM32L431xx memory map and peripheral register boundary addresses <sup>(1)</sup>

## 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 18: Current consumption measurement scheme*.

### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted with the minimum wait states number, depending on the f<sub>HCLK</sub> frequency (refer to the table "Number of wait states according to CPU clock (HCLK) frequency" available in the RM0392 reference manual).

- When the peripherals are enabled f<sub>PCLK</sub> = f<sub>HCLK</sub>

The parameters given in *Table 25* to *Table 38* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

|      | Peripheral                       | Peripheral Range 1 |     | Low-power run<br>and sleep | Unit     |  |

|------|----------------------------------|--------------------|-----|----------------------------|----------|--|

|      | RTCA                             | 1.7                | 1.1 | 2.1                        |          |  |

|      | CRS                              | 0.3                | 0.3 | 0.6                        |          |  |

|      | I2C1 independent clock domain    | 3.5                | 2.8 | 3.4                        |          |  |

|      | I2C1 clock domain                | 1.1                | 0.9 | 1.0                        |          |  |

|      | I2C2 independent clock domain    | 3.5                | 3.0 | 3.4                        |          |  |

|      | I2C2 clock domain                | 1.1                | 0.7 | 0.9                        |          |  |

|      | I2C3 independent clock domain    | 2.9                | 2.3 | 2.5                        |          |  |

|      | I2C3 clock domain                | 0.9                | 0.4 | 0.8                        |          |  |

|      | LPUART1 independent clock domain | 1.9                | 1.6 | 1.8                        |          |  |

|      | LPUART1 clock domain             | 0.6                | 0.6 | 0.6                        |          |  |

|      | LPTIM1 independent clock domain  | 2.9                | 2.4 | 2.8                        |          |  |

|      | LPTIM1 clock domain              | 0.8                | 0.4 | 0.7                        |          |  |

|      | LPTIM2 independent clock domain  | 3.1                | 2.7 | 3.9                        |          |  |

|      | LPTIM2 clock domain              | 0.8                | 0.7 | 0.8                        |          |  |

| APB1 | OPAMP                            | 0.4                | 0.2 | 0.4                        | µA/MH:   |  |

|      | PWR                              | 0.4                | 0.1 | 0.4                        | μονινιιι |  |

|      | SPI2                             | 1.8                | 1.6 | 1.6                        |          |  |

|      | SPI3                             | 1.7                | 1.3 | 1.6                        |          |  |

|      | SWPMI1 independent clock domain  | 1.9                | 1.6 | 1.9                        |          |  |

|      | SWPMI1 clock domain              | 0.9                | 0.7 | 0.8                        |          |  |

|      | TIM2                             | 6.2                | 5.0 | 5.9                        |          |  |

|      | TIM6                             | 1.0                | 0.6 | 0.9                        |          |  |

|      | TIM7                             | 1.0                | 0.6 | 0.6                        |          |  |

|      | USART2 independent clock domain  | 4.1                | 3.6 | 3.8                        |          |  |

|      | USART2 clock domain              | 1.3                | 0.9 | 1.1                        |          |  |

|      | USART3 independent clock domain  | 4.3                | 3.5 | 4.2                        |          |  |

|      | USART3 clock domain              | 1.5                | 1.1 | 1.3                        |          |  |

|      | WWDG                             | 0.5                | 0.5 | 0.5                        |          |  |

|      | All APB1 on                      | 45.4               | 35  | 47.8                       |          |  |

| APB2 | AHB to APB2 <sup>(4)</sup>       | 1.0                | 0.9 | 0.9                        |          |  |

| Table 39. Peripheral current | nt consumption (continued) |

|------------------------------|----------------------------|

|------------------------------|----------------------------|

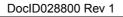

### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.14. However, the recommended clock input waveform is shown in *Figure 21*.

| Symbol                                       | Parameter                             | Conditions | Min                    | Тур    | Max                    | Unit |

|----------------------------------------------|---------------------------------------|------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -          | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | -          | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage  | -          | V <sub>SS</sub>        | -      | 0.3 V <sub>DDIOx</sub> |      |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | -          | 250                    | -      | -                      | ns   |

Table 44. Low-speed external user clock characteristics<sup>(1)</sup>

1. Guaranteed by design.

## High-speed internal 48 MHz (HSI48) RC oscillator

| Symbol                   | Parameter                                                                    | Conditions                                                    | Min               | Тур                    | Max                 | Unit |

|--------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------|------------------------|---------------------|------|

| f <sub>HSI48</sub>       | HSI48 Frequency                                                              | V <sub>DD</sub> =3.0V, T <sub>A</sub> =30°C                   | -                 | 48                     | -                   | MHz  |

| TRIM                     | HSI48 user trimming step                                                     | -                                                             | -                 | 0.11 <sup>(2)</sup>    | 0.18 <sup>(2)</sup> | %    |

| USER TRIM<br>COVERAGE    | HSI48 user trimming coverage                                                 | ±32 steps                                                     | ±3 <sup>(3)</sup> | ±3.5 <sup>(3)</sup>    | -                   | %    |

| DuCy(HSI48)              | Duty Cycle                                                                   | -                                                             | 45 <sup>(2)</sup> | -                      | 55 <sup>(2)</sup>   | %    |

| ACC <sub>HSI48_REL</sub> | Accuracy of the HSI48 oscillator<br>over temperature (factory<br>calibrated) | $V_{DD}$ = 3.0 V to 3.6 V,<br>T <sub>A</sub> = -15 to 85 °C   | -                 | -                      | ±3 <sup>(3)</sup>   | %    |

|                          |                                                                              | $V_{DD}$ = 1.65 V to 3.6 V,<br>T <sub>A</sub> = -40 to 125 °C | -                 | -                      | ±4.5 <sup>(3)</sup> |      |

|                          | HSI48 oscillator frequency drift with $V_{DD}$                               | V <sub>DD</sub> = 3 V to 3.6 V                                | -                 | 0.025 <sup>(3)</sup>   | 0.05 <sup>(3)</sup> | - %  |

| D <sub>VDD</sub> (HSI48) |                                                                              | V <sub>DD</sub> = 1.65 V to 3.6 V                             | -                 | 0.05 <sup>(3)</sup>    | 0.1 <sup>(3)</sup>  |      |

| t <sub>su</sub> (HSI48)  | HSI48 oscillator start-up time                                               | -                                                             | -                 | 2.5 <sup>(2)</sup>     | 6 <sup>(2)</sup>    | μs   |

| I <sub>DD</sub> (HSI48)  | HSI48 oscillator power<br>consumption                                        | -                                                             | -                 | 340 <sup>(2)</sup>     | 380 <sup>(2)</sup>  | μA   |

| N <sub>T</sub> jitter    | Next transition jitter<br>Accumulated jitter on 28 cycles <sup>(4)</sup>     | -                                                             | -                 | +/-0.15 <sup>(2)</sup> | -                   | ns   |

| P <sub>T</sub> jitter    | Paired transition jitter<br>Accumulated jitter on 56 cycles <sup>(4)</sup>   | -                                                             | -                 | +/-0.25 <sup>(2)</sup> | -                   | ns   |

## Table 49. HSI48 oscillator characteristics<sup>(1)</sup>

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 125°C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Jitter measurement are performed without clock source activated in parallel.

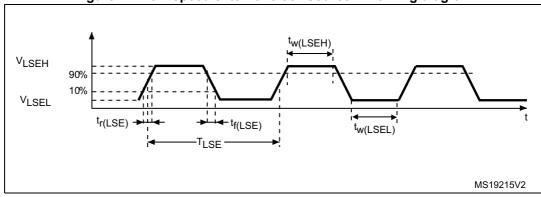

1. Refer to Table 61: I/O AC characteristics.

## 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

| Symbol                 | Parameter                                          | Conditions                        | Min                                 | Тур | Мах                                 | Unit |

|------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------|-----|-------------------------------------|------|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                       | -                                 | -                                   | -   | 0.3 <sub>x</sub> V <sub>DDIOx</sub> | v    |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                      | -                                 | 0.7 <sub>x</sub> V <sub>DDIOx</sub> | -   | -                                   | v    |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis            | -                                 | -                                   | 200 | -                                   | mV   |

| R <sub>PU</sub>        | Weak pull-up<br>equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                  | 40  | 55                                  | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered<br>pulse                       | -                                 | -                                   | -   | 70                                  | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                      | 1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V  | 350                                 | -   | -                                   | ns   |

Table 62. NRST pin characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

| Sym-<br>bol       | Parameter                          | Conditions <sup>(4)</sup>                                                                                                         |                 |                          | Min  | Тур  | Max | Unit                                |

|-------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------|------|------|-----|-------------------------------------|

|                   |                                    |                                                                                                                                   | Single          |                          |      | 4    | 5   |                                     |

| Total<br>ET unadi |                                    |                                                                                                                                   | ended           | Slow channel (max speed) | -    | 4    | 5   |                                     |

|                   | unadjusted<br>error                |                                                                                                                                   | Differential -  | Fast channel (max speed) | -    | 3.5  | 4.5 |                                     |

|                   |                                    |                                                                                                                                   |                 | Slow channel (max speed) | -    | 3.5  | 4.5 |                                     |

|                   |                                    |                                                                                                                                   | Single          | Fast channel (max speed) | -    | 1    | 2.5 |                                     |

| EO                | Offset                             |                                                                                                                                   | ended           | Slow channel (max speed) | -    | 1    | 2.5 |                                     |

| EU                | error                              |                                                                                                                                   | Differential    | Fast channel (max speed) | -    | 1.5  | 2.5 |                                     |

|                   |                                    |                                                                                                                                   | Dillerential    | Slow channel (max speed) | -    | 1.5  | 2.5 |                                     |

|                   |                                    |                                                                                                                                   | Single          | Fast channel (max speed) | -    | 2.5  | 4.5 |                                     |

| EG                | Coin orror                         |                                                                                                                                   | ended           | Slow channel (max speed) | -    | 2.5  | 4.5 |                                     |

| EG                | Gainenor                           | ain error                                                                                                                         | Differential    | Fast channel (max speed) | -    | 2.5  | 3.5 | - LSB<br>-<br>-<br>-<br>-<br>-<br>- |

|                   |                                    |                                                                                                                                   | Differential    | Slow channel (max speed) | -    | 2.5  | 3.5 |                                     |