Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 80MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, QSPI, SAI, SPI, SWPMI, UART/USART |

| Peripherals                | Brown-out Detect/Reset, DMA, PWM, WDT                                     |

| Number of I/O              | 39                                                                        |

| Program Memory Size        | 256KB (256K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                              |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l431ccu6     |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 3.17  | Voltage reference buffer (VREFBUF)                                   |

|-------|----------------------------------------------------------------------|

| 3.18  | Comparators (COMP)                                                   |

| 3.19  | Operational amplifier (OPAMP)                                        |

| 3.20  | Touch sensing controller (TSC)                                       |

| 3.21  | Random number generator (RNG)                                        |

| 3.22  | Timers and watchdogs                                                 |

|       | 3.22.1 Advanced-control timer (TIM1)                                 |

|       | 3.22.2 General-purpose timers (TIM2, TIM15, TIM16)                   |

|       | 3.22.3 Basic timers (TIM6 and TIM7)                                  |

|       | 3.22.4 Low-power timer (LPTIM1 and LPTIM2)                           |

|       | 3.22.5 Infrared interface (IRTIM)                                    |

|       | 3.22.6 Independent watchdog (IWDG) 39                                |

|       | 3.22.7 System window watchdog (WWDG)                                 |

|       | 3.22.8 SysTick timer                                                 |

| 3.23  | Real-time clock (RTC) and backup registers                           |

| 3.24  | Inter-integrated circuit interface (I <sup>2</sup> C) 41             |

| 3.25  | Universal synchronous/asynchronous receiver transmitter (USART) 42   |

| 3.26  | Low-power universal asynchronous receiver transmitter (LPUART) 43    |

| 3.27  | Serial peripheral interface (SPI) 44                                 |

| 3.28  | Serial audio interfaces (SAI) 44                                     |

| 3.29  | Single wire protocol master interface (SWPMI)                        |

| 3.30  | Controller area network (CAN)                                        |

| 3.31  | Secure digital input/output and MultiMediaCards Interface (SDMMC) 46 |

| 3.32  | Clock recovery system (CRS)                                          |

| 3.33  | Quad SPI memory interface (QUADSPI)                                  |

| 3.34  | Development support                                                  |

|       | 3.34.1 Serial wire JTAG debug port (SWJ-DP)                          |

|       | 3.34.2 Embedded Trace Macrocell™                                     |

| Pino  | uts and pin description                                              |

| Mem   | ory mapping                                                          |

| Elect | rical characteristics                                                |

| 6.1   | Parameter conditions                                                 |

|       |                                                                      |

DocID028800 Rev 1

4

5

6

RC, the HSI16 RC and the HSE crystal oscillators are disabled. The LSE or LSI is still running.

The RTC can remain active (Stop mode with RTC, Stop mode without RTC).

Some peripherals with wakeup capability can enable the HSI16 RC during Stop mode to detect their wakeup condition.

Three Stop modes are available: Stop 0, Stop 1 and Stop 2 modes. In Stop 2 mode, most of the VCORE domain is put in a lower leakage mode.

Stop 1 offers the largest number of active peripherals and wakeup sources, a smaller wakeup time but a higher consumption than Stop 2. In Stop 0 mode, the main regulator remains ON, allowing a very fast wakeup time but with much higher consumption.

The system clock when exiting from Stop 0, Stop1 or Stop2 modes can be either MSI up to 48 MHz or HSI16, depending on software configuration.

### • Standby mode

The Standby mode is used to achieve the lowest power consumption with BOR. The internal regulator is switched off so that the VCORE domain is powered off. The PLL, the MSI RC, the HSI16 RC and the HSE crystal oscillators are also switched off.

The RTC can remain active (Standby mode with RTC, Standby mode without RTC).

The brown-out reset (BOR) always remains active in Standby mode.

The state of each I/O during standby mode can be selected by software: I/O with internal pull-up, internal pull-down or floating.

After entering Standby mode, SRAM1 and register contents are lost except for registers in the Backup domain and Standby circuitry. Optionally, SRAM2 can be retained in Standby mode, supplied by the low-power Regulator (Standby with RAM2 retention mode).

The device exits Standby mode when an external reset (NRST pin), an IWDG reset, WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper) or a failure is detected on LSE (CSS on LSE).

The system clock after wakeup is MSI up to 8 MHz.

#### Shutdown mode

The Shutdown mode allows to achieve the lowest power consumption. The internal regulator is switched off so that the VCORE domain is powered off. The PLL, the HSI16, the MSI, the LSI and the HSE oscillators are also switched off.

The RTC can remain active (Shutdown mode with RTC, Shutdown mode without RTC).

The BOR is not available in Shutdown mode. No power voltage monitoring is possible in this mode, therefore the switch to Backup domain is not supported.

SRAM1, SRAM2 and register contents are lost except for registers in the Backup domain.

The device exits Shutdown mode when an external reset (NRST pin), a WKUP pin event (configurable rising or falling edge), or an RTC event occurs (alarm, periodic wakeup, timestamp, tamper).

The system clock after wakeup is MSI at 4 MHz.

|                 |        |                 | Pi      | n Nu    | mbe    | ər      |         |          |                                          | _        | 0             |       | Pin functions                                                                                                                     |                                                     |  |  |

|-----------------|--------|-----------------|---------|---------|--------|---------|---------|----------|------------------------------------------|----------|---------------|-------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|

| <b>UFQFPN32</b> | LQFP48 | <b>UFQFPN48</b> | WLCSP49 | WLCSP64 | LQFP64 | UFBGA64 | LQFP100 | UFBGA100 | Pin name<br>(function<br>after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                               | Additional functions                                |  |  |

| 8               | 12     | 12              | E5      | F6      | 16     | F3      | 25      | K3       | PA2                                      | I/O      | FT_a          | -     | TIM2_CH3, USART2_TX,<br>LPUART1_TX,<br>QUADSPI_BK1_NCS,<br>COMP2_OUT,<br>TIM15_CH1, EVENTOUT                                      | COMP2_INM,<br>ADC1_IN7,<br>WKUP4,<br>LSCO           |  |  |

| 9               | 13     | 13              | E4      | G6      | 17     | G3      | 26      | L3       | PA3                                      | I/O      | TT_a          | -     | TIM2_CH4, USART2_RX,<br>LPUART1_RX,<br>QUADSPI_CLK,<br>SAI1_MCLK_A,<br>TIM15_CH2, EVENTOUT                                        | OPAMP1_<br>VOUT,<br>COMP2_INP,<br>ADC1_IN8          |  |  |

| -               | -      | -               | -       | H8      | 18     | C2      | 27      | E3       | VSS                                      | S        | -             | -     | -                                                                                                                                 | -                                                   |  |  |

| -               | -      | -               | -       | H7      | 19     | D2      | 28      | H3       | VDD                                      | S        | -             | -     | -                                                                                                                                 | -                                                   |  |  |

| 10              | 14     | 14              | G6      | E5      | 20     | H3      | 29      | М3       | PA4                                      | I/O      | TT_a          | -     | SPI1_NSS, SPI3_NSS,<br>USART2_CK,<br>SAI1_FS_B,<br>LPTIM2_OUT,<br>EVENTOUT                                                        | COMP1_INM,<br>COMP2_INM,<br>ADC1_IN9,<br>DAC1_OUT1  |  |  |

| 11              | 15     | 15              | F5      | F5      | 21     | F4      | 30      | K4       | PA5                                      | I/O      | TT_a          | -     | TIM2_CH1, TIM2_ETR,<br>SPI1_SCK,<br>LPTIM2_ETR,<br>EVENTOUT                                                                       | COMP1_INM,<br>COMP2_INM,<br>ADC1_IN10,<br>DAC1_OUT2 |  |  |

| 12              | 16     | 16              | F4      | G5      | 22     | G4      | 31      | L4       | PA6                                      | I/O      | FT_a          | -     | TIM1_BKIN, SPI1_MISO,<br>COMP1_OUT,<br>USART3_CTS,<br>LPUART1_CTS,<br>QUADSPI_BK1_IO3,<br>TIM1_BKIN_COMP2,<br>TIM16_CH1, EVENTOUT | ADC1_IN11                                           |  |  |

| 13              | 17     | 17              | F3      | H6      | 23     | H4      | 32      | M4       | PA7                                      | I/O      | FT_fa         | -     | TIM1_CH1N, I2C3_SCL,<br>SPI1_MOSI,<br>QUADSPI_BK1_IO2,<br>COMP2_OUT,<br>EVENTOUT                                                  | ADC1_IN12                                           |  |  |

| -               | -      | -               | -       | D4      | 24     | H5      | 33      | K5       | PC4                                      | I/O      | FT_a          | -     | USART3_TX,<br>EVENTOUT                                                                                                            | COMP1_INM,<br>ADC1_IN13                             |  |  |

| -               | -      | -               | -       | E4      | 25     | H6      | 34      | L5       | PC5                                      | I/O      | FT_a          | -     | USART3_RX,<br>EVENTOUT                                                                                                            | COMP1_INP,<br>ADC1_IN14,<br>WKUP5                   |  |  |

Table 14. STM32L431xx pin definitions (continued)

STM32L431xx

Pinouts and pin description

|        |      | Tab    | le 15. Alternate     | function AF0 t | o AF7 (for AF8 | 8 to AF15 see <mark>Ta</mark> | ble 16) (contir | nued) |                              |  |

|--------|------|--------|----------------------|----------------|----------------|-------------------------------|-----------------|-------|------------------------------|--|

|        |      | AF0    | AF1                  | AF2            | AF3            | AF4                           | AF5             | AF6   | AF7                          |  |

| P      | ort  | SYS_AF | TIM1/TIM2/<br>LPTIM1 | TIM1/TIM2      | USART2         | 12C1/12C2/12C3                | SPI1/SPI2       | SPI3  | USART1/<br>USART2/<br>USART3 |  |

|        | PD0  | -      | -                    | -              | -              | -                             | SPI2_NSS        | -     | -                            |  |

|        | PD1  | -      | -                    | -              | -              | -                             | SPI2_SCK        | -     | -                            |  |

|        | PD2  | -      | -                    | -              | -              | -                             | -               | -     | USART3_RTS_<br>DE            |  |

|        | PD3  | -      | -                    | -              | -              | -                             | SPI2_MISO       | -     | USART2_CTS                   |  |

|        | PD4  | -      | -                    | -              | -              | -                             | SPI2_MOSI       | -     | USART2_RTS_<br>DE            |  |

|        | PD5  | -      | -                    | -              | -              | -                             | -               | -     | USART2_TX                    |  |

|        | PD6  | -      | -                    | -              | -              | -                             | -               | -     | USART2_RX                    |  |

| Port D | PD7  | -      | -                    | -              | -              | -                             | -               | -     | USART2_CK                    |  |

|        | PD8  | -      | -                    | -              | -              | -                             | -               | -     | USART3_TX                    |  |

|        | PD9  | -      | -                    | -              | -              | -                             | -               | -     | USART3_RX                    |  |

|        | PD10 | -      | -                    | -              | -              | -                             | -               | -     | USART3_CK                    |  |

|        | PD11 | -      | -                    | -              | -              | -                             | -               | -     | USART3_CTS                   |  |

|        | PD12 | -      | -                    | -              | -              | -                             | -               | -     | USART3_RTS_<br>DE            |  |

|        | PD13 | -      | -                    | -              | -              | -                             | -               | -     | -                            |  |

|        | PD14 | -      | -                    | -              | -              | -                             | -               | -     | -                            |  |

|        | PD15 | -      | -                    | -              | -              | -                             | -               | -     | -                            |  |

| Port E | PE0  | -      | -                    | -              | -              | -                             | -               | -     | -                            |  |

DocID028800 Rev 1

5

67/200

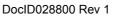

# 6.1.6 Power supply scheme

Figure 17. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

# 6.3 **Operating conditions**

# 6.3.1 General operating conditions

| Table 21 | . General | operating | conditions |

|----------|-----------|-----------|------------|

|----------|-----------|-----------|------------|

| Symbol             | Parameter                                           | Conditions                                 | Min         | Мах                                                                                | Unit |  |  |

|--------------------|-----------------------------------------------------|--------------------------------------------|-------------|------------------------------------------------------------------------------------|------|--|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                        | -                                          | 0           | 80                                                                                 |      |  |  |

| f <sub>PCLK1</sub> | Internal APB1 clock frequency                       | -                                          | 0           | 80                                                                                 | MHz  |  |  |

| f <sub>PCLK2</sub> | Internal APB2 clock frequency                       | -                                          | 0           | 80                                                                                 |      |  |  |

| V <sub>DD</sub>    | Standard operating voltage                          | -                                          | 1.71<br>(1) | 3.6                                                                                | V    |  |  |

|                    |                                                     | ADC or COMP used                           | 1.62        |                                                                                    |      |  |  |

|                    |                                                     | DAC or OPAMP used                          | 1.8         |                                                                                    |      |  |  |

| $V_{DDA}$          | Analog supply voltage                               | VREFBUF used                               | 2.4         | 3.6                                                                                | V    |  |  |

|                    |                                                     | ADC, DAC, OPAMP, COMP,<br>VREFBUF not used | 0           |                                                                                    |      |  |  |

| V <sub>BAT</sub>   | Backup operating voltage                            | -                                          | 1.55        | 3.6                                                                                | V    |  |  |

|                    | V <sub>IN</sub> I/O input voltage                   | TT_xx I/O                                  | -0.3        | V <sub>DDIOx</sub> +0.3                                                            |      |  |  |

| V <sub>IN</sub>    |                                                     | All I/O except TT_xx                       | -0.3        | MIN(MIN(V <sub>DD</sub> ,<br>V <sub>DDA</sub> )+3.6 V,<br>5.5 V) <sup>(2)(3)</sup> | V    |  |  |

|                    |                                                     | LQFP100                                    | -           | 476                                                                                |      |  |  |

|                    |                                                     | LQFP64                                     | -           | 444                                                                                |      |  |  |

|                    |                                                     | LQFP48                                     | -           | 350                                                                                |      |  |  |

|                    | Power dissipation at                                | UFBGA100                                   | -           | 350                                                                                |      |  |  |

| P <sub>D</sub>     | T <sub>A</sub> = 85 °C for suffix 6<br>or           | UFBGA64                                    | -           | 307                                                                                | mW   |  |  |

|                    | $T_A = 105 \ ^{\circ}C$ for suffix 7 <sup>(4)</sup> | UFQFPN48                                   | -           | 606                                                                                |      |  |  |

|                    |                                                     | UFQFPN32                                   | -           | 523                                                                                |      |  |  |

|                    |                                                     | WLCSP64                                    | -           | 434                                                                                |      |  |  |

|                    |                                                     | WLCSP49                                    | -           | 416                                                                                |      |  |  |

|                    | Ambient temperature for the                         | Maximum power dissipation                  | -40         | 85                                                                                 |      |  |  |

|                    | suffix 6 version                                    | Low-power dissipation <sup>(5)</sup>       | -40         | 105                                                                                |      |  |  |

| Та                 | Ambient temperature for the                         | Maximum power dissipation                  | -40         | 105                                                                                | °C   |  |  |

| IA                 | suffix 7 version                                    | Low-power dissipation <sup>(5)</sup>       | -40         | 125                                                                                |      |  |  |

|                    | Ambient temperature for the                         | Maximum power dissipation                  | -40         | 125                                                                                |      |  |  |

|                    | suffix 3 version                                    | Low-power dissipation <sup>(5)</sup>       | -40         | 130                                                                                |      |  |  |

|                    |                                                     | Suffix 6 version                           | -40         | 105                                                                                |      |  |  |

| Т <sub>Ј</sub>     | Junction temperature range                          | Suffix 7 version                           | -40         | 125                                                                                | °C   |  |  |

|                    |                                                     | Suffix 3 version                           | -40         | 130                                                                                |      |  |  |

# 6.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 18: Current consumption measurement scheme*.

## Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in analog input mode

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted with the minimum wait states number, depending on the f<sub>HCLK</sub> frequency (refer to the table "Number of wait states according to CPU clock (HCLK) frequency" available in the RM0392 reference manual).

- When the peripherals are enabled f<sub>PCLK</sub> = f<sub>HCLK</sub>

The parameters given in *Table 25* to *Table 38* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

|      | Peripheral                       | Range 1 | Range 2 | Low-power run<br>and sleep | Unit     |

|------|----------------------------------|---------|---------|----------------------------|----------|

|      | RTCA                             | 1.7     | 1.1     | 2.1                        |          |

|      | CRS                              | 0.3     | 0.3     | 0.6                        |          |

|      | I2C1 independent clock domain    | 3.5     | 2.8     | 3.4                        |          |

|      | I2C1 clock domain                | 1.1     | 0.9     | 1.0                        |          |

|      | I2C2 independent clock domain    | 3.5     | 3.0     | 3.4                        |          |

|      | I2C2 clock domain                | 1.1     | 0.7     | 0.9                        |          |

|      | I2C3 independent clock domain    | 2.9     | 2.3     | 2.5                        |          |

|      | I2C3 clock domain                | 0.9     | 0.4     | 0.8                        |          |

|      | LPUART1 independent clock domain | 1.9     | 1.6     | 1.8                        |          |

|      | LPUART1 clock domain             | 0.6     | 0.6     | 0.6                        |          |

|      | LPTIM1 independent clock domain  | 2.9     | 2.4     | 2.8                        |          |

|      | LPTIM1 clock domain              | 0.8     | 0.4     | 0.7                        |          |

|      | LPTIM2 independent clock domain  | 3.1     | 2.7     | 3.9                        |          |

|      | LPTIM2 clock domain              | 0.8     | 0.7     | 0.8                        |          |

| APB1 | OPAMP                            | 0.4     | 0.2     | 0.4                        | µA/MHz   |

|      | PWR                              | 0.4     | 0.1     | 0.4                        | μονινιιι |

|      | SPI2                             | 1.8     | 1.6     | 1.6                        |          |

|      | SPI3                             | 1.7     | 1.3     | 1.6                        |          |

|      | SWPMI1 independent clock domain  | 1.9     | 1.6     | 1.9                        |          |

|      | SWPMI1 clock domain              | 0.9     | 0.7     | 0.8                        |          |

|      | TIM2                             | 6.2     | 5.0     | 5.9                        |          |

|      | TIM6                             | 1.0     | 0.6     | 0.9                        |          |

|      | TIM7                             | 1.0     | 0.6     | 0.6                        |          |

|      | USART2 independent clock domain  | 4.1     | 3.6     | 3.8                        |          |

|      | USART2 clock domain              | 1.3     | 0.9     | 1.1                        |          |

|      | USART3 independent clock domain  | 4.3     | 3.5     | 4.2                        |          |

|      | USART3 clock domain              | 1.5     | 1.1     | 1.3                        |          |

|      | WWDG                             | 0.5     | 0.5     | 0.5                        |          |

|      | All APB1 on                      | 45.4    | 35      | 47.8                       |          |

| APB2 | AHB to APB2 <sup>(4)</sup>       | 1.0     | 0.9     | 0.9                        |          |

| Table 39. Peripheral current | nt consumption (continued) |

|------------------------------|----------------------------|

|------------------------------|----------------------------|

|      | Peripheral                      | Range 1 | Range 2 | Low-power run<br>and sleep | Unit   |

|------|---------------------------------|---------|---------|----------------------------|--------|

|      | FW                              | 0.2     | 0.2     | 0.2                        |        |

|      | SAI1 independent clock domain   | 2.3     | 1.8     | 1.9                        |        |

|      | SAI1 clock domain               | 2.1     | 1.8     | 2.0                        |        |

|      | SDMMC1 independent clock domain | 4.7     | 3.9     | 3.9                        |        |

|      | SDMMC1 clock domain             | 2.5     | 1.9     | 1.9                        |        |

|      | SPI1                            | 1.8     | 1.6     | 1.7                        |        |

| APB2 | SYSCFG/VREFBUF/COMP             | 0.6     | 0.5     | 0.6                        |        |

|      | TIM1                            | 8.1     | 6.5     | 7.6                        | µA/MHz |

|      | TIM15                           | 3.7     | 3.0     | 3.4                        |        |

|      | TIM16                           | 2.7     | 2.1     | 2.6                        |        |

|      | USART1 independent clock domain | 4.8     | 4.2     | 4.6                        |        |

|      | USART1 clock domain             | 1.5     | 1.3     | 1.7                        |        |

|      | All APB2 on                     | 24.2    | 19.9    | 22.6                       |        |

|      | ALL                             | 94.8    | 76.5    | 94.0                       |        |

| Table 39. Peri | pheral current | consumption | (continued) |

|----------------|----------------|-------------|-------------|

|                |                |             |             |

1. The BusMatrix is automatically active when at least one master is ON (CPU, DMA).

2. The GPIOx (x= A...H) dynamic current consumption is approximately divided by a factor two versus this table values when the GPIO port is locked thanks to LCKK and LCKy bits in the GPIOx\_LCKR register. In order to save the full GPIOx current consumption, the GPIOx clock should be disabled in the RCC when all port I/Os are used in alternate function or analog mode (clock is only required to read or write into GPIO registers, and is not used in AF or analog modes).

3. The AHB to APB1 Bridge is automatically active when at least one peripheral is ON on the APB1.

4. The AHB to APB2 Bridge is automatically active when at least one peripheral is ON on the APB2.

# 6.3.6 Wakeup time from low-power modes and voltage scaling transition times

The wakeup times given in *Table 40* are the latency between the event and the execution of the first user instruction.

The device goes in low-power mode after the WFE (Wait For Event) instruction.

| Symbol               | Parameter                                                           | Conditions                                                                                                                      | Тур | Max | Unit          |

|----------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----|-----|---------------|

| t <sub>WUSLEEP</sub> | Wakeup time from Sleep mode to Run mode                             | -                                                                                                                               | 6   | 6   | Nb of         |

| twulpsleep           | Wakeup time from Low-<br>power sleep mode to Low-<br>power run mode | Wakeup in Flash with Flash in power-down<br>during low-power sleep mode (SLEEP_PD=1 in<br>FLASH_ACR) and with clock MSI = 2 MHz | 6   | 8.3 | CPU<br>cycles |

Table 40. Low-power mode wakeup timings<sup>(1)</sup>

| Symbol              | Parameter                                                |         | Conditions                  | Тур   | Max   | Unit |  |

|---------------------|----------------------------------------------------------|---------|-----------------------------|-------|-------|------|--|

|                     |                                                          | Dongo 1 | Wakeup clock MSI = 48 MHz   | 8.02  | 9.24  |      |  |

|                     | Wake up time from Stop 2                                 | Range 1 | Wakeup clock HSI16 = 16 MHz | 7.66  | 8.95  |      |  |

|                     | mode to Run mode in                                      |         | Wakeup clock MSI = 24 MHz   | 8.5   | 9.54  |      |  |

| twustop2            | Flash                                                    | Range 2 | Wakeup clock HSI16 = 16 MHz | 7.75  | 8.95  |      |  |

|                     |                                                          |         | Wakeup clock MSI = 4 MHz    | 12.06 | 13.16 |      |  |

|                     | Wake up time from Stop 2<br>mode to Run mode in<br>SRAM1 | Range 1 | Wakeup clock MSI = 48 MHz   | 5.45  | 6.79  | μs   |  |

|                     |                                                          | Range   | Wakeup clock HSI16 = 16 MHz | 6.9   | 7.98  |      |  |

|                     |                                                          | Range 2 | Wakeup clock MSI = 24 MHz   | 6.3   | 7.36  |      |  |

|                     |                                                          |         | Wakeup clock HSI16 = 16 MHz | 6.9   | 7.9   |      |  |

|                     |                                                          |         | Wakeup clock MSI = 4 MHz    | 13.1  | 13.31 |      |  |

| +                   | Wakeup time from Standby                                 | Damas 4 | Wakeup clock MSI = 8 MHz    | 12.2  | 18.35 |      |  |

| <sup>t</sup> WUSTBY | mode to Run mode                                         | Range 1 | Wakeup clock MSI = 4 MHz    | 19.14 | 25.8  | μs   |  |

| t <sub>WUSTBY</sub> | Wakeup time from Standby                                 | Range 1 | Wakeup clock MSI = 8 MHz    | 12.1  | 18.3  |      |  |

| SRAM2               | with SRAM2 to Run mode                                   | Range   | Wakeup clock MSI = 4 MHz    | 19.2  | 25.87 | μs   |  |

| twushdn             | Wakeup time from<br>Shutdown mode to Run<br>mode         | Range 1 | Wakeup clock MSI = 4 MHz    | 261.5 | 315.7 | μs   |  |

Table 40. Low-power mode wakeup timings<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

## Table 41. Regulator modes transition times<sup>(1)</sup>

| Symbol               | Parameter                                                                                 | Conditions               | Тур | Max | Unit |

|----------------------|-------------------------------------------------------------------------------------------|--------------------------|-----|-----|------|

| t <sub>WULPRUN</sub> | Wakeup time from Low-power run mode to Run mode $^{(2)}$                                  | Code run with MSI 2 MHz  | 5   | 7   | 110  |

| t <sub>VOST</sub>    | Regulator transition time from Range 2 to<br>Range 1 or Range 1 to Range 2 <sup>(3)</sup> | Code run with MSI 24 MHz | 20  | 40  | μs   |

1. Guaranteed by characterization results.

2. Time until REGLPF flag is cleared in PWR\_SR2.

3. Time until VOSF flag is cleared in PWR\_SR2.

# Table 42. Wakeup time using USART/LPUART<sup>(1)</sup>

| Symbol                                        | Parameter                                                                                                         | Conditions    | Тур | Max | Unit |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------|-----|-----|------|

|                                               | Wakeup time needed to calculate the                                                                               | Stop mode 0   | -   | 1.7 |      |

| t <sub>WUUSART</sub><br>t <sub>WULPUART</sub> | maximum USART/LPUART baudrate<br>allowing to wakeup up from stop mode<br>when USART/LPUART clock source is<br>HSI | Stop mode 1/2 | -   | 8.5 | μs   |

1. Guaranteed by design.

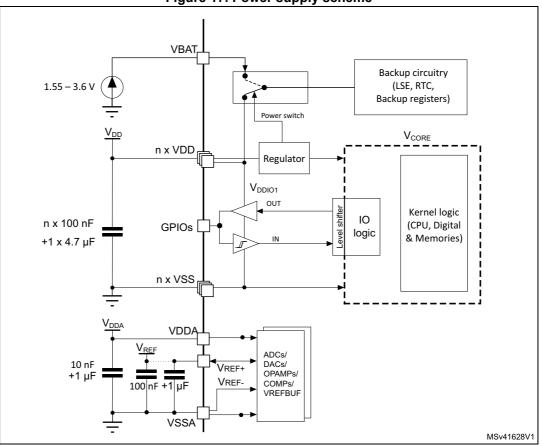

| Speed | Symbol       | Parameter                       | Conditions                                 | Min | Max                | Unit |  |  |  |

|-------|--------------|---------------------------------|--------------------------------------------|-----|--------------------|------|--|--|--|

|       |              |                                 | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 50                 |      |  |  |  |

|       |              |                                 | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 25                 |      |  |  |  |

|       | Fmax         | Maximum fraguanay               | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 5                  | MHz  |  |  |  |

|       | гшах         | Maximum frequency               | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 100 <sup>(3)</sup> |      |  |  |  |

|       |              |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 37.5               |      |  |  |  |

| 10    |              |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 5                  |      |  |  |  |

| 10    |              |                                 | C=50 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 5.8                |      |  |  |  |

|       |              |                                 | C=50 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 11                 |      |  |  |  |

|       | Tr/Tf        | Output rise and fall time       | C=50 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 28                 | ns   |  |  |  |

|       | 11/11        |                                 | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 2.5                |      |  |  |  |

|       |              |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 5                  |      |  |  |  |

|       |              |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 12                 |      |  |  |  |

|       |              |                                 | C=30 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 120 <sup>(3)</sup> |      |  |  |  |

|       |              |                                 | C=30 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 50                 |      |  |  |  |

|       | <b>F</b> max |                                 | C=30 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 10                 |      |  |  |  |

|       | Fmax         | Maximum frequency               | C=10 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 180 <sup>(3)</sup> | MHz  |  |  |  |

| 11    |              |                                 | C=10 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 75                 |      |  |  |  |

|       |              |                                 | C=10 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 10                 |      |  |  |  |

|       |              |                                 | C=30 pF, 2.7 V≤V <sub>DDIOx</sub> ≤3.6 V   | -   | 3.3                |      |  |  |  |

|       | Tr/Tf        | Output rise and fall time       | C=30 pF, 1.62 V≤V <sub>DDIOx</sub> ≤2.7 V  | -   | 6                  | ns   |  |  |  |

|       |              |                                 | C=30 pF, 1.08 V≤V <sub>DDIOx</sub> ≤1.62 V | -   | 16                 |      |  |  |  |

| Fm+   | Fmax         | Maximum frequency               | C = 50  pE = 1.6  V/s/V = -53.6  V/s       | -   | 1                  | MHz  |  |  |  |

| LU14  | Tf           | Output fall time <sup>(4)</sup> | -C=50 pF, 1.6 V≤V <sub>DDIOx</sub> ≤3.6 V  | -   | 5                  | ns   |  |  |  |

Table 61. I/O AC characteristics<sup>(1)(2)</sup> (continued)

The I/O speed is configured using the OSPEEDRy[1:0] bits. The Fm+ mode is configured in the SYSCFG\_CFGR1 register. Refer to the RM0392 reference manual for a description of GPIO Port configuration register.

2. Guaranteed by design.

3. This value represents the I/O capability but the maximum system frequency is limited to 80 MHz.

4. The fall time is defined between 70% and 30% of the output waveform accordingly to I<sup>2</sup>C specification.

1. Refer to Table 61: I/O AC characteristics.

# 6.3.15 NRST pin characteristics

The NRST pin input driver uses the CMOS technology. It is connected to a permanent pull-up resistor,  $\mathsf{R}_{\mathsf{PU}}.$

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 21: General operating conditions*.

| Symbol                 | Parameter                                          | Conditions                        | Min                                 | Тур | Мах                                 | Unit |

|------------------------|----------------------------------------------------|-----------------------------------|-------------------------------------|-----|-------------------------------------|------|

| V <sub>IL(NRST)</sub>  | NRST input low level voltage                       | -                                 | -                                   | -   | 0.3 <sub>x</sub> V <sub>DDIOx</sub> | v    |

| V <sub>IH(NRST)</sub>  | NRST input high level voltage                      | -                                 | 0.7 <sub>x</sub> V <sub>DDIOx</sub> | -   | -                                   | v    |

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage hysteresis            | -                                 | -                                   | 200 | -                                   | mV   |

| R <sub>PU</sub>        | Weak pull-up<br>equivalent resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                                  | 40  | 55                                  | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered<br>pulse                       | -                                 | -                                   | -   | 70                                  | ns   |

| V <sub>NF(NRST)</sub>  | NRST input not filtered pulse                      | 1.71 V ≤ V <sub>DD</sub> ≤ 3.6 V  | 350                                 | -   | -                                   | ns   |

Table 62. NRST pin characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

#### 3. Refer to Table 59: I/O static characteristics.

4. Ton is the Refresh phase duration. Toff is the Hold phase duration. Refer to RM0392 reference manual for more details.

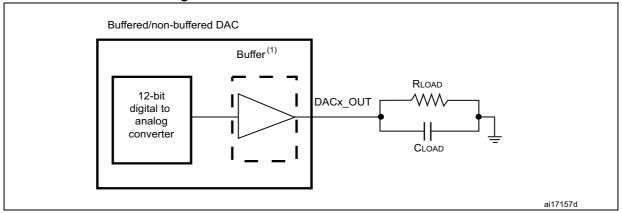

## Figure 32. 12-bit buffered / non-buffered DAC

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

| Symbol                                       | Parameter                                 | Conditio                                      | Min                       | Тур | Max       | Unit |     |

|----------------------------------------------|-------------------------------------------|-----------------------------------------------|---------------------------|-----|-----------|------|-----|

| DNL                                          | Differential non                          | DAC output buffer ON                          | DAC output buffer ON      |     | -         | ±2   |     |

| DINL                                         | linearity <sup>(2)</sup>                  | DAC output buffer OFF                         |                           | -   | -         | ±2   |     |

| -                                            | monotonicity                              | 10 bits                                       |                           | ç   | guarantee | d    |     |

| INL Integral non<br>linearity <sup>(3)</sup> |                                           | DAC output buffer ON<br>CL ≤ 50 pF, RL ≥ 5 kΩ |                           | -   | -         | ±4   |     |

|                                              |                                           | DAC output buffer OFF<br>CL ≤ 50 pF, no RL    |                           | -   | -         | ±4   |     |

|                                              |                                           | DAC output buffer ON                          | V <sub>REF+</sub> = 3.6 V | -   | -         | ±12  |     |

| Offset                                       | Offset error at code 0x800 <sup>(3)</sup> | CL ≤ 50 pF, RL ≥ 5 kΩ                         | V <sub>REF+</sub> = 1.8 V | -   | -         | ±25  | LSB |

|                                              |                                           | DAC output buffer OFF<br>CL ≤ 50 pF, no RL    |                           | -   | -         | ±8   |     |

| Offset1                                      | Offset error at code 0x001 <sup>(4)</sup> | DAC output buffer OFF<br>CL ≤ 50 pF, no RL    |                           | -   | -         | ±5   |     |

| OffsetCal                                    | Offset Error at                           | DAC output butter ()N                         | V <sub>REF+</sub> = 3.6 V | -   | -         | ±5   |     |

| Unserval                                     | code 0x800<br>after calibration           | CL ≤ 50 pF, RL ≥ 5 kΩ                         | V <sub>REF+</sub> = 1.8 V | -   | -         | ±7   |     |

# Table 71. DAC accuracy<sup>(1)</sup>

#### Voltage reference buffer characteristics 6.3.19

| Table 72. VREFBUF characteristics <sup>(1)</sup> |                                                                                                 |                                        |                            |                          |       |                                         |         |  |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------|----------------------------|--------------------------|-------|-----------------------------------------|---------|--|

| Symbol                                           | Parameter                                                                                       | Conditio                               | ons                        | Min                      | Тур   | Max                                     | Unit    |  |

|                                                  |                                                                                                 | Normal made                            | V <sub>RS</sub> = 0        | 2.4                      | -     | 3.6                                     |         |  |

| M                                                | Analog supply                                                                                   | Normal mode                            | V <sub>RS</sub> = 1        | 2.8                      | -     | 3.6                                     | 1       |  |

| V <sub>DDA</sub>                                 | voltage                                                                                         | Degraded mode <sup>(2)</sup>           | V <sub>RS</sub> = 0        | 1.65                     | -     | 2.4                                     |         |  |

|                                                  |                                                                                                 |                                        | V <sub>RS</sub> = 1        | 1.65                     | -     | 2.8                                     | V       |  |

|                                                  |                                                                                                 | Normal mode                            | V <sub>RS</sub> = 0        | 2.046 <sup>(3)</sup>     | 2.048 | 2.049 <sup>(3)</sup>                    | v       |  |

| V <sub>REFBUF</sub> _                            | Voltage reference                                                                               | Normai mode                            | V <sub>RS</sub> = 1        | 2.498 <sup>(3)</sup>     | 2.5   | 2.502 <sup>(3)</sup>                    |         |  |

| OUT                                              | output                                                                                          | Degraded mode <sup>(2)</sup>           | V <sub>RS</sub> = 0        | V <sub>DDA</sub> -150 mV | -     | V <sub>DDA</sub>                        |         |  |

|                                                  |                                                                                                 | Degraded mode                          | V <sub>RS</sub> = 1        | V <sub>DDA</sub> -150 mV | -     | V <sub>DDA</sub>                        |         |  |

| TRIM                                             | Trim step resolution                                                                            | -                                      | -                          | -                        | ±0.05 | ±0.1                                    | %       |  |

| CL                                               | Load capacitor                                                                                  | -                                      | -                          | 0.5                      | 1     | 1.5                                     | μF      |  |

| esr                                              | Equivalent<br>Serial Resistor<br>of Cload                                                       | -                                      | -                          | -                        | -     | 2                                       | Ω       |  |

| I <sub>load</sub>                                | Static load current                                                                             | -                                      | -                          | -                        | -     | 4                                       | mA      |  |

| 1                                                | Line regulation                                                                                 | 281/51/5361/                           | I <sub>load</sub> = 500 μA | -                        | 200   | 1000                                    | ppm/V   |  |

| I <sub>line_reg</sub>                            |                                                                                                 | $2.0 V \leq V_{\text{DDA}} \leq 3.0 V$ | I <sub>load</sub> = 4 mA   | -                        | 100   | 500                                     | ppm/v   |  |

| l <sub>load_reg</sub>                            | Load<br>regulation                                                                              | 500 µA ≤ I <sub>load</sub> ≤4 mA       | Normal mode                | -                        | 50    | 500                                     | ppm/mA  |  |

| T                                                | Temperature                                                                                     | -40 °C < T <sub>J</sub> < +125 °C      |                            | -                        | -     | T <sub>coeff</sub> _<br>vrefint +<br>50 | ppm/ °C |  |

| T <sub>Coeff</sub>                               | coefficient                                                                                     | 0 °C < T <sub>J</sub> < +50 °C         |                            | -                        | -     | T <sub>coeff</sub><br>vrefint +<br>50   |         |  |

| PSRR                                             | Power supply                                                                                    | DC                                     |                            | 40                       | 60    | -                                       | dB      |  |

| FORK                                             | rejection                                                                                       | 100 kHz                                |                            | 25                       | 40    | -                                       | uБ      |  |

|                                                  |                                                                                                 | $CL = 0.5 \ \mu F^{(4)}$               |                            | -                        | 300   | 350                                     |         |  |

| t <sub>START</sub> Start-up time                 |                                                                                                 | $CL = 1.1 \ \mu F^{(4)}$               |                            | -                        | 500   | 650                                     | μs      |  |

|                                                  |                                                                                                 | $CL = 1.5 \ \mu F^{(4)}$               |                            | -                        | 650   | 800                                     |         |  |

| I <sub>INRUSH</sub>                              | Control of<br>maximum DC<br>current drive<br>on VREFBUF_<br>OUT during<br>start-up phase<br>(5) | -                                      | -                          | -                        | 8     | -                                       | mA      |  |

# (1)

Г

Т

٦

Т

## **SPI characteristics**

Unless otherwise specified, the parameters given in *Table 82* for SPI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and supply voltage conditions summarized in *Table 21: General operating conditions*.

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI).

| Symbol                                       | Parameter                | Conditions                                                                              | Min                              | Тур               | Max                  | Unit |

|----------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------|----------------------------------|-------------------|----------------------|------|

|                                              |                          | Master mode receiver/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1    |                                  |                   | 40                   |      |

|                                              |                          | Master mode receiver/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1   |                                  |                   | 16                   |      |

|                                              |                          | Master mode transmitter<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1            |                                  |                   | 40                   |      |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency      | Slave mode receiver<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1                | -                                | -                 | 40                   | MHz  |

|                                              |                          | Slave mode transmitter/full duplex<br>2.7 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1  |                                  |                   | 37 <sup>(2)</sup>    |      |

|                                              |                          | Slave mode transmitter/full duplex<br>1.71 < V <sub>DD</sub> < 3.6 V<br>Voltage Range 1 |                                  |                   | 20 <sup>(2)</sup>    |      |

|                                              |                          | Voltage Range 2                                                                         |                                  |                   | 13                   |      |

| t <sub>su(NSS)</sub>                         | NSS setup time           | Slave mode, SPI prescaler = 2                                                           | 4 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |

| t <sub>h(NSS)</sub>                          | NSS hold time            | Slave mode, SPI prescaler = 2                                                           | 2 <sub>x</sub> T <sub>PCLK</sub> | -                 | -                    | ns   |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time    | Master mode                                                                             | T <sub>PCLK</sub> -2             | T <sub>PCLK</sub> | T <sub>PCLK</sub> +2 | ns   |

| t <sub>su(MI)</sub>                          | Data input satur timo    | Master mode                                                                             | 4                                | -                 | -                    | ns   |

| t <sub>su(SI)</sub>                          |                          | ata input setup time<br>Slave mode                                                      |                                  | -                 | -                    | 115  |

| t <sub>h(MI)</sub>                           | Data input hold time     | t hold time                                                                             |                                  | -                 | -                    | ns   |

| t <sub>h(SI)</sub>                           |                          | Slave mode                                                                              | 1.5                              | -                 | -                    | 115  |

| t <sub>a(SO)</sub>                           | Data output access time  | Slave mode                                                                              | 9                                | -                 | 36                   | ns   |

| t <sub>dis(SO)</sub>                         | Data output disable time | Slave mode                                                                              | 9                                | -                 | 16                   | ns   |

| Table | 82. | SPI | characteristics <sup>(</sup> | 1) |

|-------|-----|-----|------------------------------|----|

|-------|-----|-----|------------------------------|----|

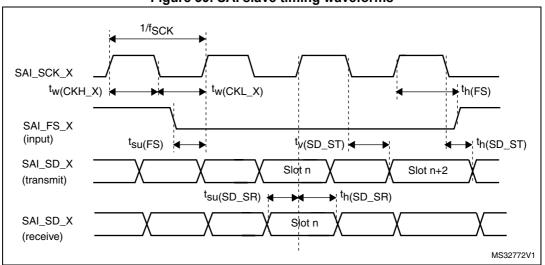

Figure 39. SAI slave timing waveforms

## **SDMMC** characteristics

Unless otherwise specified, the parameters given in *Table 86* for SDIO are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and V<sub>DD</sub> supply voltage conditions summarized in *Table 21: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output characteristics.

| Symbol                                              | Parameter                             | Conditions               | Min | Тур | Max | Unit |  |  |

|-----------------------------------------------------|---------------------------------------|--------------------------|-----|-----|-----|------|--|--|

| f <sub>PP</sub>                                     | Clock frequency in data transfer mode | -                        | 0   | -   | 50  | MHz  |  |  |

| -                                                   | SDIO_CK/fPCLK2 frequency ratio        | -                        | -   | -   | 4/3 | -    |  |  |

| t <sub>W(CKL)</sub>                                 | Clock low time                        | f <sub>PP</sub> = 50 MHz | 8   | 10  | -   | ns   |  |  |

| t <sub>W(CKH)</sub>                                 | Clock high time                       | f <sub>PP</sub> = 50 MHz | 8   | 10  | -   | ns   |  |  |

| CMD, D inpu                                         | ts (referenced to CK) in MMC and SD H | S mode                   |     |     |     |      |  |  |

| t <sub>ISU</sub>                                    | Input setup time HS                   | f <sub>PP</sub> = 50 MHz | 3.5 | -   | -   | ns   |  |  |

| t <sub>IH</sub>                                     | Input hold time HS                    | f <sub>PP</sub> = 50 MHz | 2.5 | -   | -   | ns   |  |  |

| CMD, D outp                                         | uts (referenced to CK) in MMC and SD  | HS mode                  |     |     |     |      |  |  |

| t <sub>OV</sub>                                     | Output valid time HS                  | f <sub>PP</sub> = 50 MHz | -   | 12  | 13  | ns   |  |  |

| t <sub>OH</sub>                                     | Output hold time HS                   | f <sub>PP</sub> = 50 MHz | 10  | -   | -   | ns   |  |  |

| CMD, D inputs (referenced to CK) in SD default mode |                                       |                          |     |     |     |      |  |  |

| t <sub>ISUD</sub>                                   | Input setup time SD                   | f <sub>PP</sub> = 50 MHz | 3.5 | -   | -   | ns   |  |  |

| t <sub>IHD</sub>                                    | Input hold time SD                    | f <sub>PP</sub> = 50 MHz | 3   | -   | -   | ns   |  |  |

Table 86. SD / MMC dynamic characteristics,  $V_{DD}$ =2.7 V to 3.6 V<sup>(1)</sup>

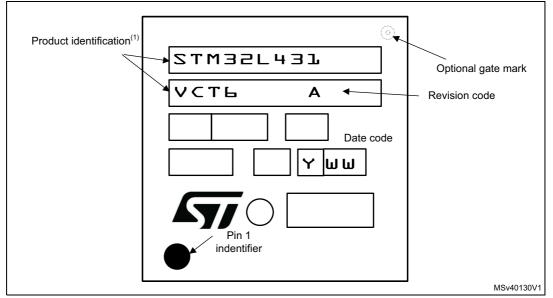

## **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

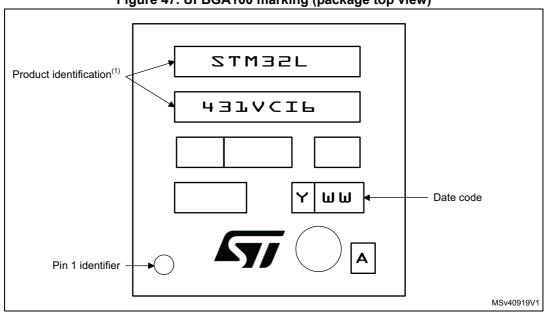

Figure 47. UFBGA100 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

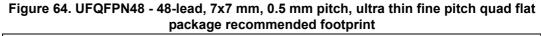

| package mechanical data |             |       |       |                       |        |        |  |  |  |

|-------------------------|-------------|-------|-------|-----------------------|--------|--------|--|--|--|

| Cumb al                 | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |  |  |

| Symbol                  | Min         | Тур   | Max   | Min                   | Тур    | Мах    |  |  |  |

| А                       | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |  |  |  |

| A1                      | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |  |  |  |

| D                       | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |  |  |  |

| Е                       | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |  |  |  |

| D2                      | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |  |  |

| E2                      | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |  |  |  |

| L                       | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |  |  |  |

| Т                       | -           | 0.152 | -     | -                     | 0.0060 | -      |  |  |  |

| b                       | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |  |  |  |

| е                       | -           | 0.500 | -     | -                     | 0.0197 | -      |  |  |  |

| ddd                     | -           | -     | 0.080 | -                     | -      | 0.0031 |  |  |  |

# Table 100. UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flatpackage mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

# **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID028800 Rev 1